### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

# ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Ανάπτυξη Μεθοδολογίας Δυναμικής Διαχείρισης Συχνότητας σε FPGAs μέσω Ελέγχου των Μονοπατιών Δεδομένων σε Πραγματικό Χρόνο

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Πέτρος Α. Σουσούρης

Επιβλέπων: Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

#### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

## ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Ανάπτυξη Μεθοδολογίας Δυναμικής Διαχείρισης Συχνότητας σε FPGAs μέσω Ελέγχου των Μονοπατιών Δεδομένων σε Πραγματικό Χρόνο

### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

# Πέτρος Α. Σουσούρης

Επιβλέπων: Δημήτριος Ι. Σούντρης

Αναπληρωτής Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 29<sup>η</sup> Φεβρουαρίου 2016

.....

Δημήτριος Ι. Σούντρης Κιαμάλ Πεκμεστζή Γεώργιος Οικονομάκος

Αν. Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π. Επ. Καθηγητής Ε.Μ.Π.

Αθήνα, Φεβρουάριος 2016

.....

Πέτρος Α. Σουσούρης

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright © Πέτρος Α. Σουσούρης, 2016

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# Πεοιεχόμενα

| Ευρετή | ήριο Εικόνων                               | 7  |

|--------|--------------------------------------------|----|

| Ευρετή | ήριο Πινάκων                               | 9  |

| Σύντομ | ιη περίληψη                                | 10 |

| Abstra | act                                        | 11 |

| 1. Ev  | νσωματωμένα Συστήματα                      | 12 |

| 1.1    | Ενσωματωμένη υπολογιστική – προκλήσεις     | 13 |

| 1.2    | FPGA - ιστορική εξέλιξη                    | 14 |

| 1.3    | Πλεονεκτήματα χρήσης των FPGA              | 16 |

| 1.4    | Δομή του FPGA                              | 18 |

| 1.5    | Έτοιμες βιβλιοθήκες                        | 20 |

| 1.8    | Εργαλεία που χρησιμοποιήθηκαν              | 21 |

| 2. In  | ntroduction                                | 24 |

| 2.1    | Embedded systems                           | 24 |

| 2.2    | $Embedded\ computing-challenges$           | 24 |

| 2.3    | FPGA - evolution                           | 26 |

| 2.4    | Benefits of FPGA technology                | 27 |

| 2.5    | FPGA structure                             | 29 |

| 2.6    | Software libraries                         | 31 |

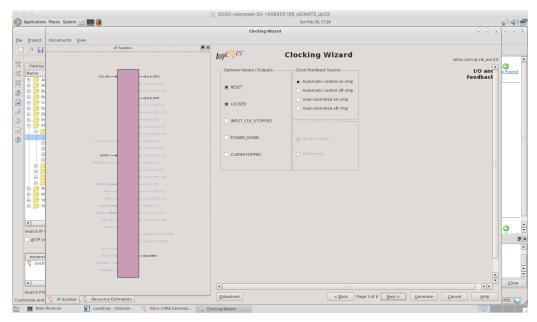

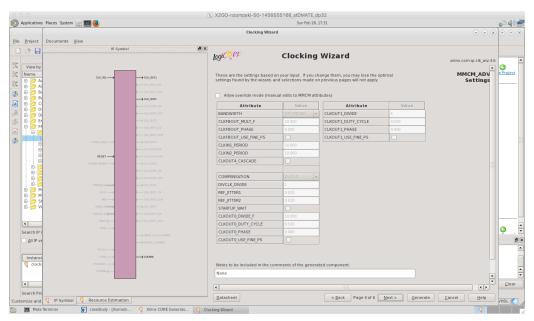

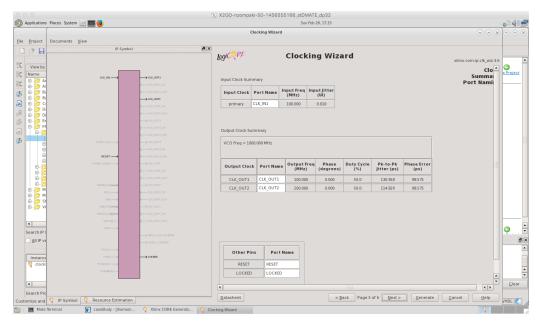

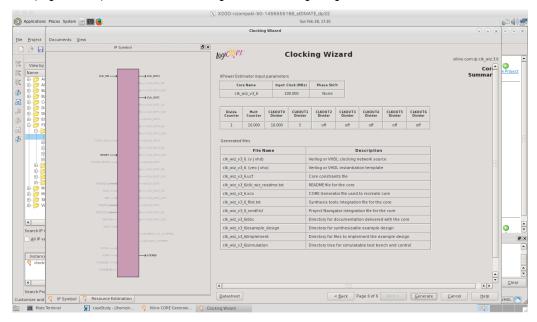

| 2.7    | Tools used                                 | 31 |

| 3. D   | ata path control path,                     | 35 |

| 3.1    | General                                    | 35 |

| 3.2    | Data path                                  | 36 |

| 3.3    | Control path (control unit)                | 37 |

| 3.4    | Combinational design                       | 40 |

| 3.5    | Sequential design                          | 41 |

| 3.6    | Paths                                      | 43 |

| 3.7    | FPGA timing                                | 45 |

| 3.8    | Timing in Xilinx designs                   | 48 |

| 3.9    | Methodology                                | 50 |

| 3.     | .10.1 Manual retouch of file               | 50 |

| 3.     | .10.2 Generating VHDL Code                 | 52 |

| 3.     | .10.3 Creating digital clock manager (DCM) | 52 |

| 3.1     | 10.4 Schematic of the enhanced circuit         | 53 |

|---------|------------------------------------------------|----|

| Appen   | dix A – Detailed Tutorial                      | 55 |

| A.1     | From VHDL to implementation                    | 55 |

| A.2     | Analyzing the circuit using Planahead Expander | 63 |

| A.3     | Inserting Selector into the project            | 67 |

| A.4     | Building the digital clock manager             | 67 |

| A.5     | Inserting the digital clock manager            | 72 |

| A.6     | Connecting internal signals using FPGA Editor  | 74 |

| A.7     | Simulating the new design                      | 75 |

| Appen   | dix B                                          | 77 |

| B.1     | Edf file explanation                           | 77 |

| B.2     | Twr file explanation                           | 82 |

| Βιβλιογ | γαφία                                          | 85 |

# Ευρετήριο Εικόνων

| 1: Σύγχοονα Ενσωματωμένα Συστήματα                           | 12          |

|--------------------------------------------------------------|-------------|

| 2: FPGA πάνω σε τυπωμένα κυκλώματα                           | 15          |

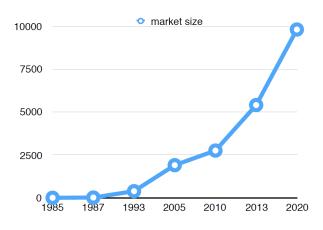

| 3: Εξέλιξη της αγοράς σε εκατομμύρια                         | 16          |

| 4: Αρχιτεκτονική τύπου νησίδων με διασυνδέσεις block και swi | tch boxes19 |

| 5: Διαδικασία κατασκευής κυκλώματος πάνω σε FPGA             | 23          |

| 6: Control and Data Path                                     | 35          |

| 7: Basic components of Control and Data Path                 | 36          |

| 8: MIPS Data Path                                            |             |

| 9: MIPS                                                      | 40          |

| 10: Combinational circuit                                    | 41          |

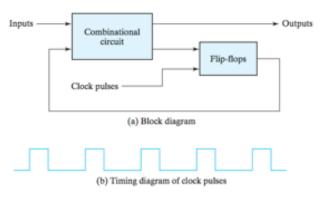

| 11: Block Diagram and Timing Diagram of Clock Pulses         | 43          |

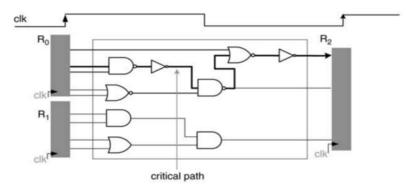

| 12: Critical Path                                            | 44          |

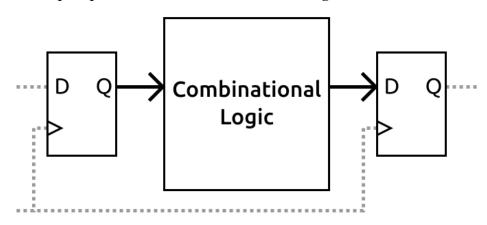

| 13: Combinational Circuit                                    | 45          |

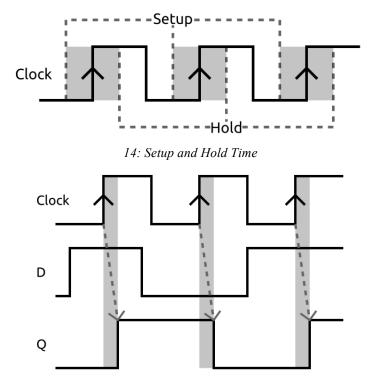

| 14: Setup and Hold Time                                      | 46          |

| 15: Propagation Time                                         | 46          |

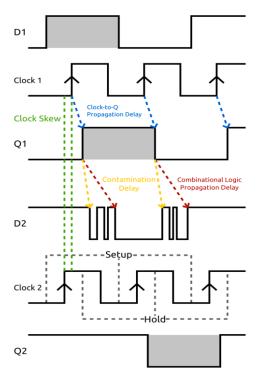

| 16: Timing Issues                                            | 48          |

| 17: Combinational Logic                                      | 48          |

| 18: Xilinx Timing Design                                     | 49          |

| 19: Interconnections                                         | 49          |

| 20: Interconnection Detail                                   | 49          |

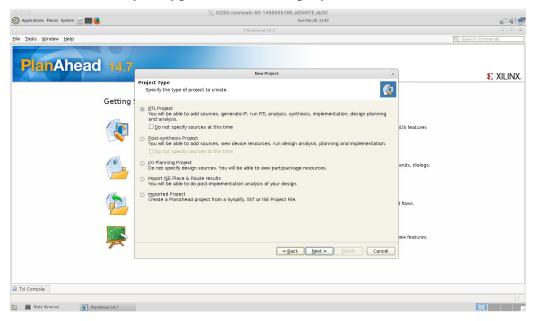

| 21: Opening Screen of Planahead                              | 55          |

| 22: New Project Screen                                       | 55          |

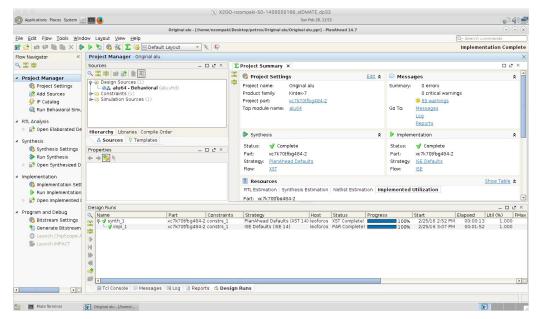

| 23: Main screen of Planahead                                 | 56          |

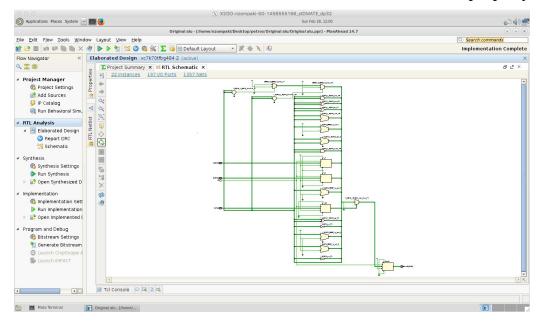

| 24: RTL Schematic                                            | 56          |

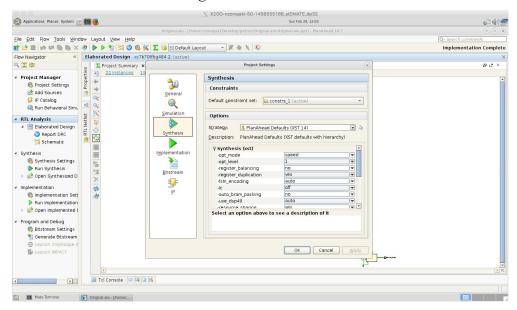

| 25: Synthesis Settings                                       | 57          |

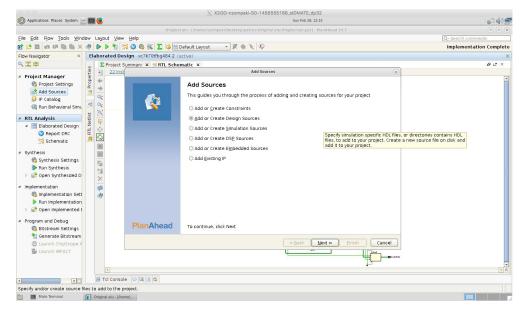

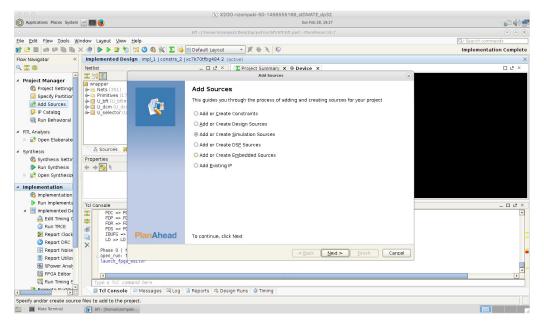

| 26: Add Sources Screen                                       | 58          |

| 27: New File                                                 | 58          |

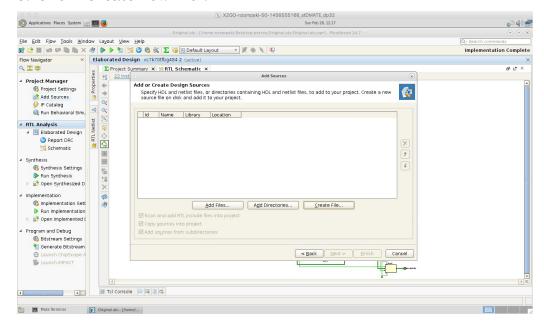

| 28: Hierarchical Code Structure                              | 59          |

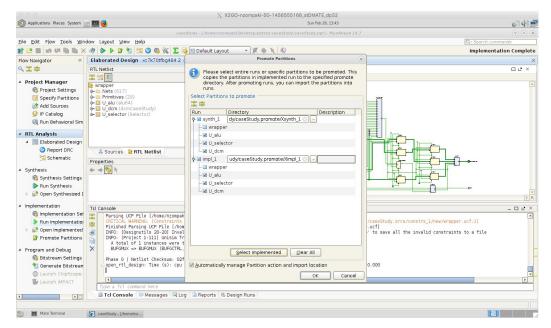

| 29: Partitions Overview                                      | 59          |

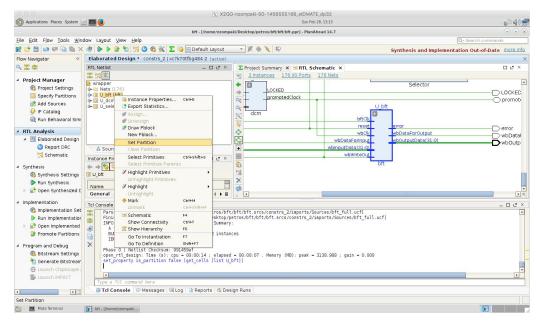

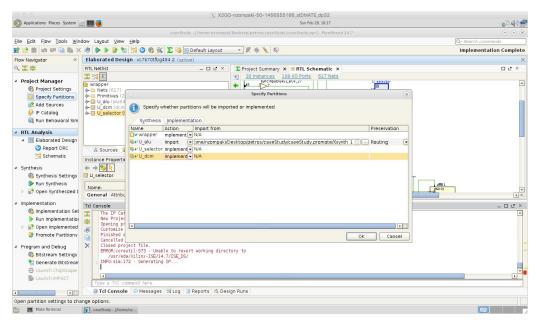

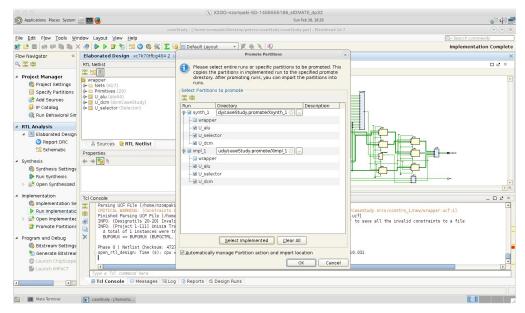

| 30: Setting a Partition                                      | 60          |

| 31: Heing Partitions                                         | 60          |

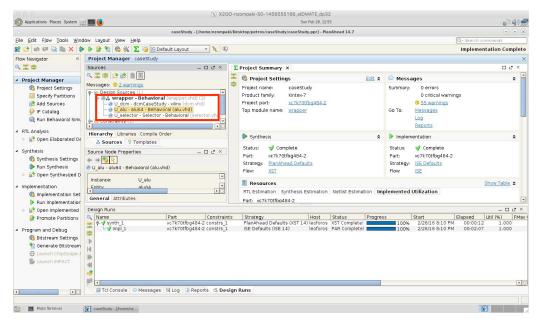

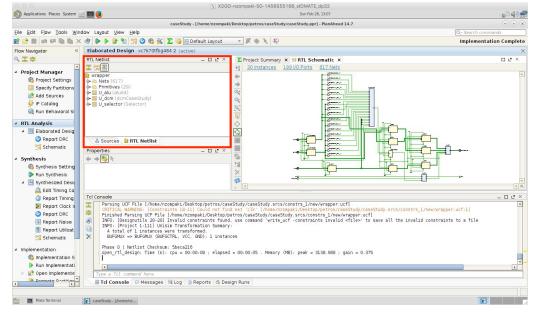

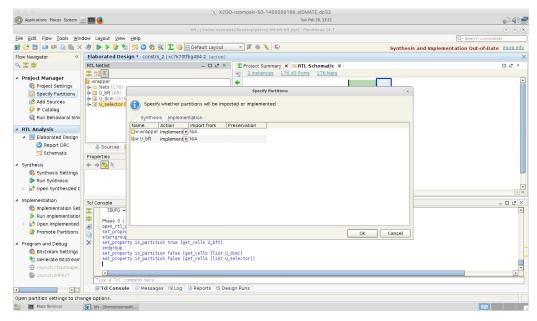

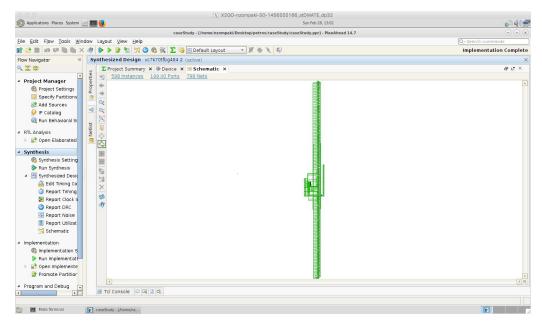

| 32: Synthesis schematic                   | 61 |

|-------------------------------------------|----|

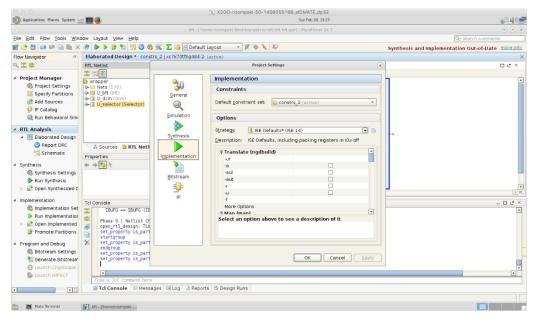

| 33: Implementation Settings               | 61 |

| 34: Promoting Partitions                  | 62 |

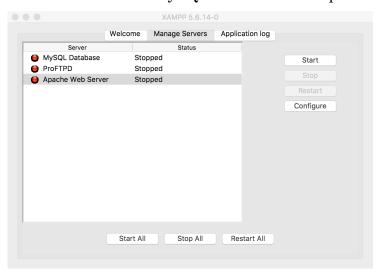

| 35: Xampp main window                     | 63 |

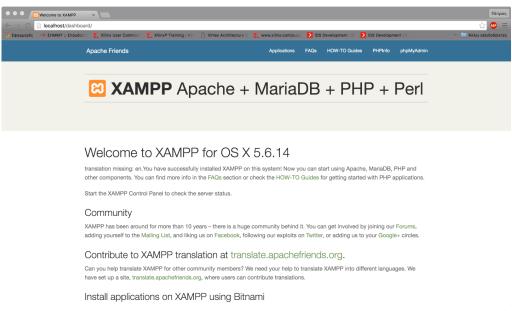

| 36: localhost main screen                 | 63 |

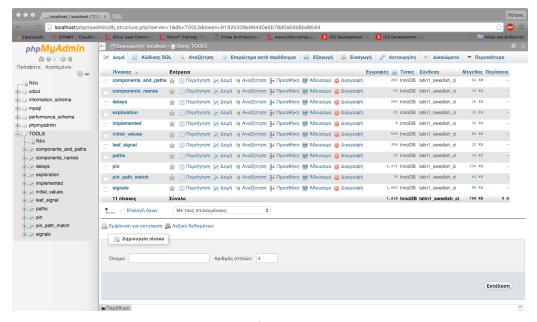

| 37: Database overview                     | 64 |

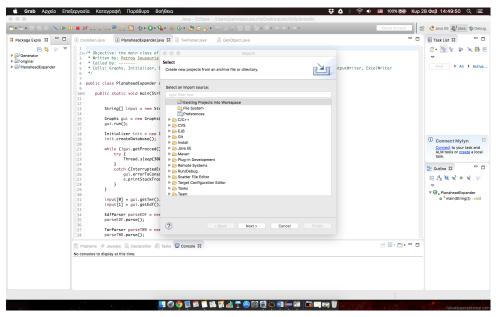

| 38: Importing Expander in Eclipse (1)     | 64 |

| 39: Importing Expander in Eclipse (2)     | 65 |

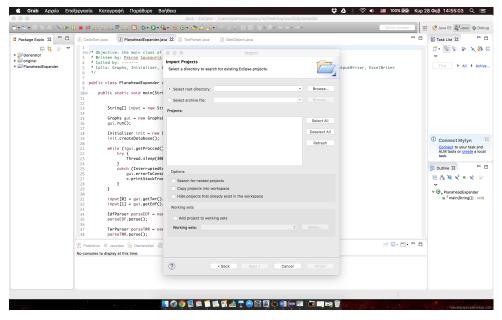

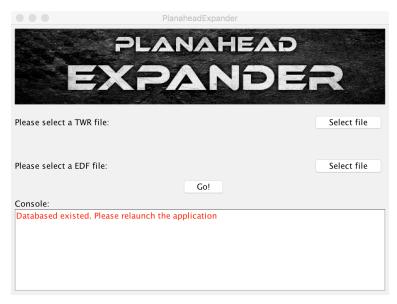

| 40: Expander main window                  | 66 |

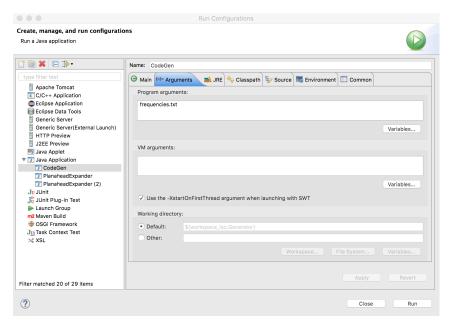

| 41: Setting Input Arguments               | 67 |

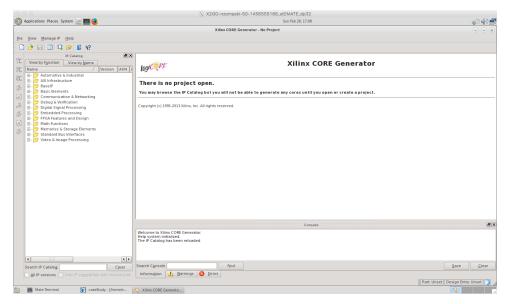

| 42: Opening Screen of Core Generator      | 68 |

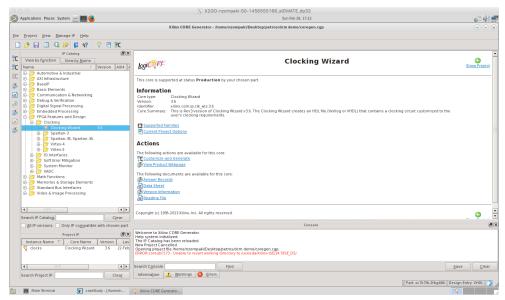

| 43: Locating Clocking Wizard              | 68 |

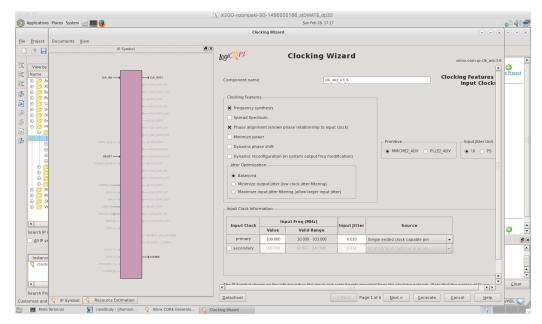

| 44: Defining input frequency              | 69 |

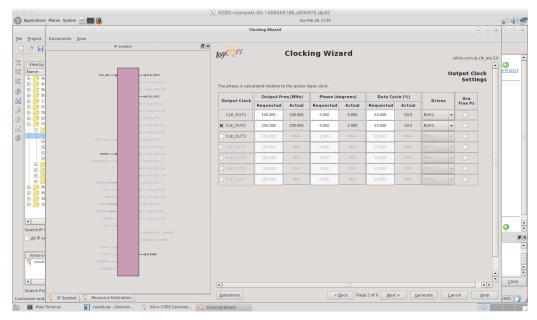

| 45: Defining output frequencies           | 69 |

| 46: Optional pins                         | 70 |

| 47: Other options                         | 70 |

| 48: Renaming options                      | 71 |

| 49: Settings check                        | 71 |

| 50: Importing and implementing partitions | 73 |

| 51: Promoting partitions                  | 73 |

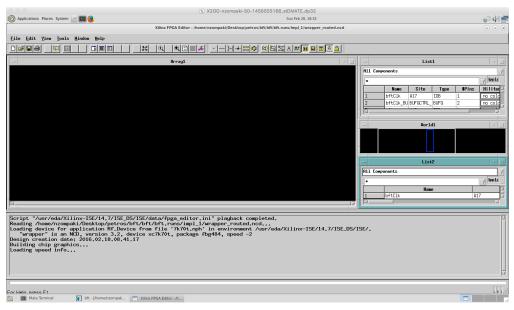

| 52: FPGA Editor main screen               | 74 |

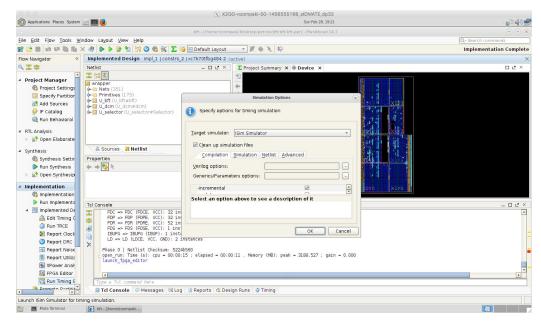

| 53: Add simulation sources                | 75 |

| 54: Simulator settings                    | 76 |

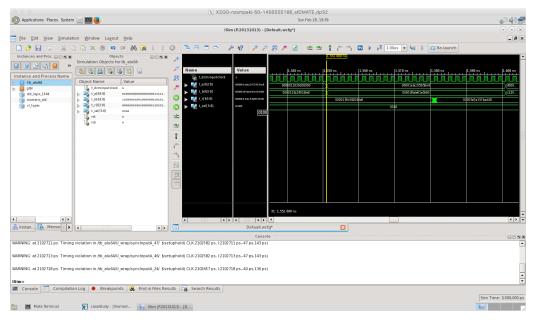

| 55: Simulator window                      | 76 |

# Ευρετήριο Πινάκων

| 1: Εξέλιξη του αριθμού πυλών στα FPGA | 16 |

|---------------------------------------|----|

| 2: Timing Comparison                  | 50 |

| 3: Example of Expander Output         | 51 |

| 4: Sorted Generator Input             | 51 |

| 5: Switching between Clocks           | 53 |

# Σύντομη περίληψη

Τα δεδομένα που παράγονται μέσα σε ένα κύκλωμα απαιτείται σχεδόν πάντοτε να μετακινηθούν από το σημείο δημιουργίας τους σε ένα άλλο σημείο, ώστε να συνεχιστεί η επεξεργασία τους ή να αποθηκευτούν για μελλοντική χρήση. Η μετακίνηση αυτή δεν πραγματοποιείται ακαριαία, αλλά απαιτεί ένα χρονικό διάστημα το οποίο εισάγει περιορισμούς σχετικά με τον χρονισμό και την απόδοση του κυκλώματος. Συγκεκριμένα, η μέγιστη επιτρεπόμενη συχνότητα λειτουργίας ενός κυκλώματος εξαρτάται άμεσα από την μέγιστη καθυστέρηση κατά μήκος των διαδρομών, που ονομάζονται μονοπάτια δεδομένων (data paths) και ακολουθούνται για την μετακίνηση των δεδομένων.

Στη συγκεκριμένη διπλωματική εργασία αναπτύσσεται μια μεθοδολογία και τα αντίστοιχα εργαλεία λογισμικού που είναι απαραίτητα για την ανάλυση και μελέτη των μονοπατιών δεδομένων (data paths) ενός κυκλώματος. Τελικός στόχος είναι η βελτίωση της απόδοσης (performance) του υπό εξέταση κυκλώματος κάνοντας χρήση της συγκεκριμένης μεθοδολογίας.

Κατά συνέπεια, η παρούσα διπλωματική κινείται πάνω σε δύο άξονες. Πρώτον, τη συστηματική διατύπωση της μεθοδολογίας που θα οδηγήσει στην βελτίωση της απόδοσης ενός κυκλώματος και την αποφυγή διάφορων τεχνικών και σχεδιαστικών προβλημάτων που ενδεχομένως να προκύψουν κατά τη διάρκεια μιας αντίστοιχης διαδικασίας. Δεύτερον, την ανάπτυξη εργαλείων λογισμικού, που σε συνδυασμό με εμπορικά εργαλεία συμβάλλουν στην επίτευξη καλύτερης απόδοσης και ταχύτερης ανάπτυξης και επαλήθευσης (verification) του κυκλώματος. Τέλος, η βελτίωση της απόδοσης που επιτυγχάνεται συγκρίνεται με την απόδοση του αρχικού κυκλώματος.

**Λέξεις κλειδιά:** κρίσιμο μονοπάτι, μονοπάτια δεδομένων, μέγιστη καθυστέρηση, μέγιστη συχνότητα λειτουργίας, δυναμική διαχείριση ρολογιών, σήματα ελέγχου, Planahead

## **Abstract**

Data created in a circuit is often needed to be transmitted to a part of the design other than their creation place in order to be further processed or stored for future utilization. These transmissions cannot take place in zero time, but a short amount of time is required, which results in many timing constrains regarding the timing and the performance of the circuit. In particular, the maximum allowed frequency for operating a circuit highly depends on the maximum delay met during data transmissions.

In this diploma thesis a methodology is developed and described along with the software tools required for studying and analyzing the data paths of a circuit. This methodology aims to improve the performance of the circuit under examination.

To conclude, this diploma thesis has two main goals. First, explicitly define and describe the methodology which will guide a system designer to improve the performance of his/her circuit. The detailed description of the methodology will help the designer to avoid some of the technical problems which occur during the design process. Second, the development of some software tools, in collaboration with some commercial software applications provided by Xilinx, will help the designed accomplish even better performance in the system and accelerate the process of developing and verifying the circuit. The performance improvement is compared to the original circuit.

**Key words:** data paths, critical path, maximum delay, maximum frequency, control signals

# 1. Ενσωματωμένα Συστήματα

Ένας απλός ορισμός του ενσωματωμένου συστήματος είναι οποιαδήποτε συσκευή η οποία περιλαμβάνει έναν υπολογιστή που είναι αφοσιωμένος σε μία συγκεκριμένη λειτουργία και δεν είναι γενικού σκοπού. Συχνά, το σύστημα πρέπει να ανταποκρίνεται σε υπολογιστικούς περιορισμούς πραγματικού χρόνου (real time computing constrains) και είναι ενσωματωμένο ως μέρος μιας ολοκληρωμένης συσκευής που πολλές φορές περιλαμβάνει υλικό (hardware) και μηχανικά μέρη.

Τα ενσωματωμένα συστήματα ποικίλουν από φορητές συσκευές όπως ψηφιακά ρολόγια και συσκευές μουσικής, έως εφαρμογές μεγάλης κλίμακας, όπως φανάρια και ελεγκτές εργοστασίων, και συστήματα ιδιαίτερα μεγάλης πολυπλοκότητας όπως είναι τα αυτοκίνητα. Η πολυπλοκότητα των ενσωματωμένων συστημάτων μπορεί να είναι μικρή, όπως σε έναν απλό μικροελεγκτή (micro controller), έως υψηλή σε συστήματα με πολλές μονάδες, περιφερειακές συσκευές ή συσκευές διαχείρισης δικτύων. Στην εικόνα 1 είναι ορατά διάφορα σύγχρονα ενσωματωμένα συστήματα διαφορετικής πολυπλοκότητας σχεδίασης από πολλά και διαφορετικά πεδία εφαρμογών.

1: Σύγχρονα Ενσωματωμένα Συστήματα. Πηγή: es.informatik.uni-kl.de

Τα σύγχρονα συστήματα συχνά βασίζονται σε μικροελεγκτές, δηλαδή επεξεργαστές με ενσωματωμένη μνήμη ή άλλες περιφερειακές συσκευές, αλλά κανονικοί μικροεπεξεργαστές συναντώνται ακόμα ειδικά σε πολύπλοκα συστήματα. Οι επεξεργαστές μπορούν να είναι γενικού σκοπού είτε ειδικά σχεδιασμένοι (custom designed) για μία πολύ συγκεκριμένη εφαρμογή. Ένα χαρακτηριστικό παράδειγμα εξειδικευμένου επεξεργαστή είναι ο επεξεργαστής ψηφιακού σήματος (digital signal processor - DSP).

Για ποιον όμως λόγο χρησιμοποιούνται μικροεπεξεργαστές; Στην ερώτηση αυτή, υπάρχουν δύο απαντήσεις:

• Οι μικροεπεξεργαστές είναι ένας πολύ αποδοτικός τρόπος υλοποίησης ψηφιακών συστημάτων, καθώς προσφέρουν την δυνατότητα επαναχρησιμοποίησης της σχεδίασης του υλικού απλά με μία αλλαγή λογισμικού. Αυτό είναι ιδιαίτερα σημαντικό, καθώς η ολοκληρωμένων κυκλωμάτων παραμένει μία ακριβή και χρονοβόρα διαδικασία.

Οι μικροεπεξεργαστές καθιστούν ευκολότερη την σχεδίαση οικογενειών προϊόντων τα οποία μπορούν να κατασκευαστούν για να παρέχουν διαφορετικά σύνολα χαρακτηριστικών σε διαφορετικές τιμές και μπορούν να επεκταθούν για να παρέχουν νέα χαρακτηριστικά, ώστε να συμβαδίζουν με τις ραγδαία μεταβαλλόμενες αγορές.

## 1.1 Ενσωματωμένη υπολογιστική – προκλήσεις

Η ενσωματωμένη υπολογιστική (embedded computing) είναι από πολλές απόψεις περισσότερο απαιτητική από τα προγράμματα που γράφονται για προσωπικούς υπολογιστές. Η λειτουργικότητα είναι σημαντική τόσο στην υπολογιστική γενικού σκοπού όσο και την ενσωματωμένη υπολογιστική, αλλά οι ενσωματωμένες εφαρμογές πρέπει να ικανοποιούν πολλούς επιπλέον περιορισμούς.

- Πολύπλοκοι αλγόριθμοι: Οι λειτουργίες που εκτελούνται από τον μικροεπεξεργαστή μπορεί να είναι ιδιαίτερα σύνθετες (για παράδειγμα, έλεγχος της ροής καύσιμου στο αυτοκίνητο)

- Διασύνδεση με τον χρήστη: Οι μικροεπεξεργαστές χρησιμοποιούνται συχνά για τον έλεγχο πολύπλοκων διασυνδέσεων με τον χρήστη οι οποίες μπορούν να περιλαμβάνουν πολλά μενού και επιλογές (για παράδειγμα, σε ένα σύστημα εντοπισμού θέσης (global positioning system GPS)

Για να γίνουν τα πράγματα ακόμα δυσκολότερα, πολλές λειτουργίες των ενσωματωμένων συστημάτων πρέπει να πραγματοποιούνται μέσα σε συγκεκριμένες προθεσμίες (deadlines).

- Πραγματικός χρόνος (real time): Πολλά ενσωματωμένα υπολογιστικά συστήματα πρέπει να λειτουργούν σε πραγματικό χρόνο. Αν τα δεδομένα δεν είναι έτοιμα μέχρι μια συγκεκριμένη προθεσμία, το σύστημα κινδυνεύει με κατάρρευση. Η μη τήρηση των περιορισμών χρόνου μπορεί να δημιουργήσει δυσαρεστημένους πελάτες ή να κοστίσει ακόμα και ανθρώπινες ζωές.

- Λειτουργίες πολλαπλών ρυθμών (multirate): Οι λειτουργίες των ενσωματωμένων συστημάτων όχι μόνο πρέπει να ανταποκρίνονται σε συγκεκριμένες προθεσμίες, αλλά πιθανόν πολλές λειτουργίες πραγματικού χρόνου μπορεί να εξελίσσονται παράλληλα. Είναι πιθανό κάποιες λειτουργίες να εκτελούνται με αργό ρυθμό και άλλες με γρήγορο. Οι εφαρμογές πολυμέσων (multimedia) είναι το κύριο παράδειγμα συμπεριφοράς πολλαπλών ρυθμών, καθώς τα τμήματα ήχου και εικόνας εκτελούνται με πολύ διαφορετικούς ρυθμούς αλλά πρέπει να παραμένουν συγχρονισμένα.

- Κόστος κατασκευής: Το συνολικό κόστος κατασκευής ενός συστήματος είναι πολύ σημαντικό σε πολλές εφαρμογές και προσδιορίζεται από πολλούς παράγοντες, όπως ο τύπος του επεξεργαστή, η ποσότητα της μνήμης και το πλήθος των εξωτερικών συσκευών.

- Ισχύς (power): Η κατανάλωση ισχύος επηρεάζει την διάρκεια ζωής της μπαταρίας των φορητών συστημάτων, που σε πολλές εφαρμογές είναι κρίσιμη, αλλά και την παραγωγή θερμότητας που μπορεί να οδηγήσει σε προσωρινή αδυναμία χρήσης του συστήματος.

• Περιορισμένοι πόροι συστήματος: Σε αντίθεση με τους προσωπικούς υπολογιστές, τα περισσότερα ενσωματωμένα συστήματα διαθέτουν περιορισμένους πόρους προς αξιοποίηση (για παράδειγμα, τροφοδοσία από μπαταρία, περιορισμένη ποσότητα κύριας μνήμης, λίγες ή καθόλου συσκευές εισόδου/εξόδου). Επομένως, είναι απαραίτητη η προσεκτική αξιοποίηση τους, ώστε η εφαρμογή που θα τρέξει στο συγκεκριμένο σύστημα να μπορεί να λειτουργεί σωστά.

Οι εξωτερικοί περιορισμοί είναι μια σημαντική πηγή δυσκολίας στην σχεδίαση ενσωματωμένων συστημάτων. Κατά την σχεδίαση, τους πρέπει να ληφθούν υπόψη τα παρακάτω σημαντικά προβλήματα.

Πόσο υλικό χρειάζεται; Υπάρχει τρόπος για σημαντικό έλεγχο της ποσότητας της υπολογιστικής ισχύος που εφαρμόζεται στο πρόβλημα μέσω της επιλογής του τύπου του μικροεπεξεργαστή, την ποσότητα της μνήμης, τις συσκευές εισόδου και εξόδου και πολλά άλλα. Εφόσον πρέπει συχνά να ικανοποιούνται τέτοιοι περιορισμοί απόδοσης και κόστους κατασκευής, η επιλογή του υλικού είναι σημαντική. Αν το υλικό είναι λίγο, το σύστημα δεν θα μπορεί να ανταποκριθεί στις προθεσμίες. Αν το υλικό είναι υπερβολικό, το κόστος του συστήματος αυξάνεται χωρίς ανάλογη βελτίωση της απόδοσης.

Πως ικανοποιούνται οι προθεσμίες; Ο ωμός τρόπος ικανοποίησης μίας προθεσμίας είναι η επιτάχυνση του υλικού, ώστε το πρόγραμμα να εκτελείται γρηγορότερα. Η επιλογή αυτή όμως αυξάνει το κόστος του συστήματος, όπως αναφέρθηκε. Είναι επίσης πιθανό η αύξηση του χρονισμού του επεξεργαστή να μην βελτιώσει τον χρόνο εκτέλεσης, εφόσον η ταχύτητα του προγράμματος μπορεί να περιορίζεται από το σύστημα μνήμης.

Πως ελαχιστοποιείται η κατανάλωση ισχύος; Σε όλα τα συστήματα, η κατανάλωση ισχύος είναι κρίσιμο ζήτημα. Απαιτείται προσεκτική σχεδίαση για την επιβράδυνση μη κρίσιμων τμημάτων του συστήματος για τον περιορισμό της κατανάλωσης ενώ ικανοποιούνται ακόμη οι απαραίτητοι στόχοι απόδοσης.

Σχεδίαση με δυνατότητα αναβάθμισης. Η πλατφόρμα υλικού μπορεί να χρησιμοποιηθεί για αρκετές γενιές προϊόντων με ελάχιστες ή καθόλου αλλαγές. Ωστόσο, είναι επιθυμητή η προσθήκη δυνατοτήτων μέσω του λογισμικού. Είναι επομένως σημαντική η σωστή σχεδίαση του υλικού ώστε να προβλεφθεί η απόδοση λογισμικού που ακόμα δεν έχει σχεδιαστεί.

Αζιοπιστία. Η αξιοπιστία είναι σημαντική κατά την δημιουργία προϊόντων αλλά και σε ορισμένες εφαρμογές, όπως τα κρίσιμα από πλευράς ασφάλειας συστήματα (safety critical systems).

# 1.2 FPGA - ιστορική εξέλιξη

Το FPGA (Field Programmable Gate Array - συστοιχία επιτόπια προγραμματιζόμενων πυλών) είναι τύπος προγραμματιζόμενου ολοκληρωμένου κυκλώματος γενικής χρήσης το οποίο διαθέτει μεγάλο αριθμό τυποποιημένων πυλών και άλλων ψηφιακών λειτουργιών όπως απαριθμητές, καταχωρητές μνήμης, γεννήτριες PLL και πολλά άλλα. Μερικά FPGA ενσωματώνουν επίσης αναλογικές λειτουργίες. Κατά τον προγραμματισμό του FPGA, ο οποίος γίνεται πάντοτε ενώ αυτό είναι τοποθετημένο πάνω σε ένα τυπωμένο κύκλωμα, ενεργοποιούνται οι

επιθυμητές λειτουργίες και διασυνδέονται μεταξύ τους ώστε να συμπεριφέρεται ως ολοκληρωμένο κύκλωμα με συγκεκριμένη λειτουργία.

Ο κώδικας με τον οποίο προγραμματίζεται το FPGA γράφεται σε κάποια γλώσσα περιγραφής υλικού όπως η VHDL και η Verilog. Έχει παρόμοιο πεδίο εφαρμογών με άλλα προγραμματιζόμενα ολοκληρωμένα ψηφιακά συστήματα όπως τα PLD και τα ASIC. Όμως το FPGA διαθέτει κάποια ιδιαίτερα χαρακτηριστικά που περιγράφονται παρακάτω:

- Το FPGA χάνει τον προγραμματισμό του κάθε φορά που χάνει την τάση τροφοδοσίας του. Επομένως, απαιτεί εξωτερικό μικροεπεξεργαστή ή μνήμη με μόνιμη συγκράτηση δεδομένων (non volatile memory) από τα οποία θα προγραμματίζεται, κάθε φορά που επανέρχεται η τάση τροφοδοσίας.

- Ο προγραμματισμός του FPGA μπορεί να αλλάζει κάθε φορά που τροποποιείται το λογισμικό του μικροεπεξεργαστή ή τα δεδομένα της μνήμης που το ελέγχει.

- Δεν υπάρχει κάποιο όριο στον αριθμό των φορών που μπορεί να προγραμματιστεί.

- Η κατανάλωση ισχύος είναι σημαντικά αυξημένη σε σχέση με τα ASIC.

Το FPGA είναι ιδιαίτερα κατάλληλο εκεί που οι παράμετροι λειτουργίας πρέπει να αλλάζουν συχνά ή σε μικρές ποσότητες παραγωγής, ενώ το ASIC, λόγω μαζικής παραγωγής, είναι φθηνότερο εκεί που απαιτούνται μεγάλες ποσότητες και η επιθυμητή λειτουργία είναι αυστηρά προκαθορισμένη, χωρίς σφάλματα (τα ASIC δεν μπορούν να προγραμματιστούν ξανά).

Βασική δομική μονάδα του FPGA είναι το λογικό μπλοκ, με την χρήση του οποίου υλοποιούνται οι λογικές συναρτήσεις που εκφράζουν τις λειτουργίες ενός ψηφιακού κυκλώματος. Ανάλογα με το μέγεθος του κυκλώματος, πολλά λογικά μπλοκ συνδέονται για να υλοποιήσουν το πλήθος των απαραίτητων λογικών συναρτήσεων. Στις εικόνες 2 και 3 φαίνονται μερικά FPGAs.

2: FPGA πάνω σε τυπωμένα κυκλώματα Πηγή: en.wikipedia.com, codehackcreate.com

Η βιομηχανία των FPGA προέκυψε από τις προγραμματιζόμενες μνήμες μόνο ανάγνωσης (programmable read only memory - PROM) και τις προγραμματιζόμενες λογικές συσκευές (programmable logic device - PLD). Και οι δύο προηγούμενες

συσκευές έχουν την δυνατότητα προγραμματισμού σε ομάδες (banches). Ωστόσο, ο προγραμματισμός τους στηρίζονταν σε καλωδιωμένη λογική ανάμεσα στις πύλες.

Η δεκαετία του 1990 ήταν εκρηκτική για τα FPGA τόσο από άποψη πολυπλοκότητας της σχεδίασης τους όσο και όγκου παραγωγής. Την ίδια περίοδο τα FPGA χρησιμοποιούνταν σε τηλεπικοινωνιακές εφαρμογές και στα δίκτυα. Προς το τέλος της δεκαετίας, τα FPGA βρήκαν τον δρόμο τους σε πιο εμπορικές εφαρμογές, την αυτοκινητοβιομηχανία και βιομηχανικές εφαρμογές.

Μία πρόσφατη τάση είναι η υβριδική αρχιτεκτονική, δηλαδή ο συνδυασμός των λογικών μπλοκ των παραδοσιακών FPGA με ενσωματωμένους επεξεργαστές και τα σχετικά περιφερειακά για να σχηματίσουν ένα ολοκληρωμένο σύστημα πάνω σε ένα προγραμματιζόμενο chip (system on a programmable chip). Η συγκεκριμένη αρχιτεκτονική περιορίζει την κατανάλωση ισχύος, δημιουργεί ένα μικρότερο σε μέγεθος σύστημα και σε μεγαλύτερη αξιοπιστία των συνδέσεων των δύο ξεχωριστών συστημάτων. (Wolf, 2008)

Στον πίνακα και το γράφημα που ακολουθούν υπάρχουν συγκεντρωμένα διάφορα στοιχεία που φανερώνουν την ιστορική εξέλιξη των FPGA (πηγή: en.wikipedia.com).

| Year            | 1982  | 1987  | 1992    | 2000     |

|-----------------|-------|-------|---------|----------|

| Number of Gates | 8.192 | 9.000 | 600.000 | millions |

1: Εξέλιζη του αριθμού πυλών στα FPGA

3: Εξέλιζη της αγοράς σε εκατομμύρια

## 1.3 Πλεονεκτήματα χρήσης των FPGA

Η ικανότητα των FPGAs να συνδυάζουν τα καλύτερα στοιχεία από τους δυο κόσμους (ASICs και συστήματα βασισμένα σε επεξεργαστή) οδήγησε στην ευρεία υιοθέτηση τους από όλες τις βιομηχανίες. Τα FPGA παρέχουν ταχύτητα και αξιοπιστία, ενώ δεν απαιτούν το μεγάλο προκαταβολικό κόστος που παρουσιάζει μια σχεδίαση βασισμένη στα ASIC. Το επαναπρογραμματιζόμενο πυρίτιο έχει τα ίδια πλεονεκτήματα και ευελιξία με ένα λογισμικό που τρέχει σε ένα σύστημα βασισμένο σε επεξεργαστή, αλλά δεν περιορίζεται από τον αριθμό των διαθέσιμων υπολογιστικών πυρήνων. Σε αντίθεση με τους επεξεργαστές, τα FPGA είναι παράλληλα από την κατασκευή τους κι έτσι διαφορετικές διεργασίες δεν χρειάζεται να ανταγωνίζονται για τους ίδιους πόρους. Κάθε ανεξάρτητη υπολογιστική διεργασία

ανατίθεται σε ένα διαφορετικό τμήμα του chip και μπορεί να λειτουργεί αυτόνομα χωρίς επιρροή από άλλες διεργασίες. Συνεπώς, η απόδοση ενός τμήματος μιας εφαρμογής δεν επηρεάζεται όταν περισσότερες διεργασίες προστεθούν στο σύστημα. (The Linley Group, 2009)

Τα κύρια πλεονεκτήματα της χρήσης των FPGA συνοψίζονται παρακάτω:

- Απόδοση. Εκμεταλλευόμενα την παραλληλία στο υλικό, τα FPGA υπερέχουν ως προς την υπολογιστική ισχύ των ψηφιακών επεξεργαστών σήματος (digital signal processors DSP) εγκαταλείποντας την λογική της ακολουθιακής εκτέλεσης και επιτυγχάνοντας περισσότερα ανά κύκλο ρολογιού. Η BDTI, μια εταιρεία benchmarking, σε μελέτη της έδειξε ότι τα FPGA μπορούν να παραδώσουν πολλές φορές παραπάνω απόδοση ανά δολάριο σε μερικές εφαρμογές σε σχέση με ένα DSP (BDTI Industry Report, 2006). Ο έλεγχος εισόδων και εξόδων στο επίπεδο του υλικού παρέχει καλύτερους χρόνους απόκρισης και εξειδικευμένη λειτουργικότητα για να ικανοποιήσει τις ανάγκες μιας εφαρμογής.

- Χρόνος στην αγορά (time to market). Η τεχνολογία των FPGA προσφέρει ευελιξία και ικανότητες ταχείας προτυποποίησης. Μια ιδέα και μια σχεδίαση μπορούν να δοκιμαστούν στο υλικό χωρίς να μεσολαβήσει η χρονοβόρα διαδικασία της κατασκευής ενός ASIC (Thompson, 2004). Οι συνέχεις αλλαγές και βελτιώσεις της σχεδίασης μπορούν να επιτευχθούν σε ώρες αντί για εβδομάδες. Στο εμπόριο υπάρχουν πολλές επιλογές υλικού με διαφορετικούς τύπους I/O ήδη συνδεδεμένες πάνω σε ένα επαναπρογραμματιζόμενο chip. Επίσης, η συνεχώς αυξανόμενη διαθεσιμότητα εργαλείων λογισμικού υψηλού επιπέδου μειώνουν τον χρόνο εκμάθησης εισάγοντας πολλαπλά επίπεδα αφαίρεσης και προσφέροντας έτοιμες υλοποιήσεις για προηγμένο έλεγχο και επεξεργασία σήματος.

- Κόστος. Το προκαταβολικό κόστος σχεδίασης ενός ASIC ξεπερνά κατά πολύ τις αντίστοιχες λύσεις βασισμένες σε FPGA. Η μεγάλη αρχική επένδυση των ASIC μπορεί να δικαιολογηθεί από για κατασκευαστές που παράγουν και πουλούν μαζικά chip. Η φύση του επαναπρογραμματιζόμενου πυριτίου ελαττώνει το κόστος ανάπτυξης και την χρονοβόρα διαδικασία κατασκευής. Επειδή συχνά στην πράξη οι προδιαγραφές ενός συστήματος αλλάζουν με τον χρόνο, το κόστος των συνεχών αλλαγών σε σχεδιάσεις FPGA είναι αμεληταίο όταν συγκριθεί με το μεγάλο κόστος επανασχεδίασης ενός ASIC.

- Αξιοπιστία. Ενώ τα εργαλεία λογισμικού παρέχουν το προγραμματιστικό περιβάλλον, τα κυκλώματα των FPGA είναι μια υλοποίηση της εκτέλεσης του προγράμματος στο υλικό. Τα συστήματα βασισμένα σε επεξεργαστή συχνά παρέχουν πολλά επίπεδα αφαίρεσης για βοήθεια στην δρομολόγηση διεργασιών και τον διαμοιρασμό πόρων ανάμεσα σε διεργασίες. Το επίπεδο "οδηγός" ελέγχει τους πόρους του υλικού και το λειτουργικό σύστημα διαχειρίζεται την μνήμη και τον επεξεργαστή. Σε κάθε διαθέσιμο υπολογιστικό πυρήνα μόνο μία εντολή μπορεί να εκτελεστεί κάθε χρονική στιγμή και τα συστήματα βασισμένα σε επεξεργαστή κινδυνεύουν χρονικά κρίσιμες διεργασίες συνεχώς να διακόπτουν η μία την άλλη. Τα FPGA, τα οποία δεν διαθέτουν λειτουργικό σύστημα, ελαχιστοποιούν τους κινδύνους αξιοπιστίας με πραγματικά παράλληλη εκτέλεση εντολών και ντετερμινιστικό υλικό αφιερωμένο σε κάθε διεργασία που υπάρχει στο σύστημα.

• Μακροχρόνια συντήρηση. Όπως αναφέρθηκε προηγουμένως, τα FPGA είναι αναβαθμίσιμα και δεν απαιτούν το κόστος και τον χρόνο επαναδιαμόρφωσης όπως ένα ASIC. Τα ψηφιακά πρωτόκολλα επικοινωνιών, για παράδειγμα, έχουν προδιαγραφές που μπορεί να αλλάξουν με τον καιρό και οι διεπαφές που βασίζονται σε ASIC ενδεχομένως να προκαλέσουν προβλήματα συντήρησης και συμβατότητας. Με τις δυνατότητες επαναδιαμόρφωσης τα FPGA μπορούν να ανταπεξέλθουν σε μελλοντικές τροποποιήσεις που θα χρειαστούν. Καθώς ένα προιόν ή ένα σύστημα ωριμάζει, λειτουργικές ενισχύσεις μπορούν να γίνουν σε αυτό χωρίς τον χρόνο που απαιτείται για σχεδίαση υλικού από την αρχή. (National Instruments, 2012)

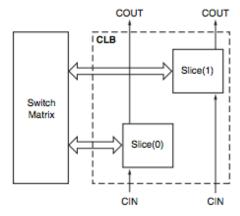

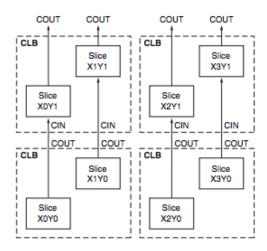

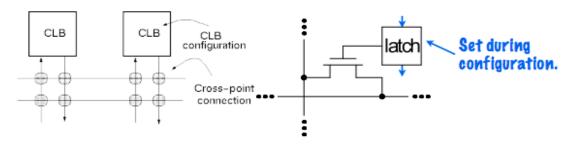

## 1.4 Δομή του FPGA

Τα FPGA αποτελούνται από τρία βασικά στοιχεία: logic boards, θύρες εισόδου και εξόδου και προγραμματιζόμενη δρομολόγηση. Ο τύπος της logic board που χρησιμοποιείται επηρεάζει την ταχύτητα και την επιφάνεια του FPGA. Ένας κοινός τύπος logic board που χρησιμοποιείται στα σύγχρονα FPGA βασίζεται στα lookup tables (LUT), τα οποία αποτελούνται από έναν N:1 πολυπλέκτη και μια μνήμη N bit. Όσον αφορά την ψηφιακή λογική, ένα LUT απλά απαριθμεί έναν πίνακα αλήθειας, δίνοντας την δυνατότητα στο FPGA να υλοποιεί περίπλοκη ψηφιακή λογική. (Brown & Rose)

#### **LUT**

Ένα LUT είναι ένας πίνακας που αντικαθιστά υπολογισμούς την ώρα της εκτέλεσης με μία πιο απλή και γρήγορη λειτουργία indexing. Αν και τα LUT έχουν επιλεγεί ως η κύρια υπολογιστική μονάδα στα εμπορικά FPGA, το μέγεθος τους σε κάθε logic board πρέπει να προσδιοριστεί προσεκτικά. Τα μεγάλα LUT μπορούν να χειριστούν πιο πολύπλοκους υπολογισμούς και συνεπώς να μειώσουν τις καθυστερήσεις πάνω στην καλωδίωση ανάμεσα στις διάφορες μονάδες. Ωστόσο, αυτό οδηγεί σε πιο αργές υλοποιήσεις των LUT εξαιτίας της χρήσης μεγαλύτερων πολυπλεκτών. Από την άλλη πλευρά, μικρότερα LUT έχουν ως αποτέλεσμα την χρησιμοποίηση μεγαλύτερου αριθμού logic blocks, κάτι που αυξάνει τις καθυστερήσεις καλωδίωσης στην σχεδίαση. Επιπλέον, υπάρχει μια μονάδα αποθήκευσης ενός bit που είναι ένα D flip flop. Ο πολυπλέκτης εξόδου επιλέγει ένα αποτέλεσμα είτε από την συνάρτηση που είναι υλοποιημένη μέσα στο LUT είτε από το bit που είναι αποθηκευμένο στο flip flop.

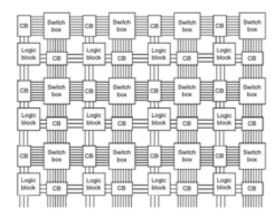

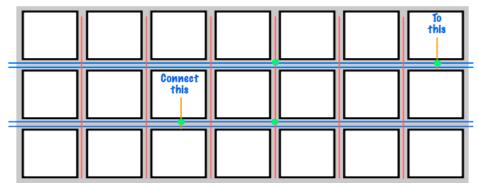

#### Διασύνδεση

Τα σύγχρονα FPGA είναι σχεδιασμένα χρησιμοποιώντας την αρχιτεκτονική "νησίδων". Σύμφωνα με αυτήν, οι δομικές μονάδες τοποθετούνται σε ένα δισδιάστατο πλέγμα και διασυνδέονται με ένα συγκεκριμένο μοτίβο. Αυτές οι δομικές μονάδες σχηματίζουν τις νησίδες οι οποίες επιπλέουν στον ωκεανό των διασυνδέσεων. Αυτή η αρχιτεκτονική επιτρέπει στους υπολογισμούς να πραγματοποιηθούν τοπικά στο FPGA, ενώ μεγαλύτεροι υπολογισμοί σπάνε σε κομμάτια και αντιστοιχίζονται σε φυσικά logic blocks μέσα στο πλέγμα.

4: Αρχιτεκτονική τύπου νησίδων με διασυνδέσεις block και switch boxes

Το κάθε block έχει πρόσβαση στους γείτονες του μέσω του block διασύνδεσης, το οποίο συνδέει τις εισόδους και εξόδους του λογικού block στους πόρους δρομολόγησης μέσω προγραμματιζόμενων διακοπτών ή πολυπλεκτών. Το block διασύνδεσης επιτρέπει στην είσοδο και την έξοδο του λογικού block να αποδοθούν σε οριζόντιες και κάθετες διαδρομές, βελτιώνοντας κατά πολύ την ευελεξία δρομολόγησης.

Κάθε διαμορφώμενο στοιχείο του FPGA απαιτεί ένα bit πληροφορίας για να διατηρήσει μία διαμόρφωση καθορισμένη από τον χρήστη. Για ένα FPGA βασιζόμενο σε LUT, αυτές οι προγραμματιζόμενες τοποθεσίες περιλαμβάνουν τα περιεχόμενα του λογικού block και την συνδεσιμότητα. Η διαμόρφωση επιτυγχάνεται μέσω προγραμματισμού των bits που συνδέονται με αυτές τις προγραμματιζόμενες τοποθεσίες, σύμφωνα με την είσοδο του χρήστη. Υπάρχουν πολλοί τρόποι για την αποθήκευση ενός bit δυαδικής πληροφορίας με την πιο δημοφιλή να είναι η SRAM, η antifuse και η flash μνήμη. (Kuon, Tessier, & Rose, 2008)

Η πιο ευρεία χρησιμοποιούμενη μέθοδος για την αποθήκευση πληροφορίας διαμόρφωσης στα εμπορικά FPGA είναι η πτητική στατική RAM, περισσότερο γνωστή ως SRAM. Αυτή η τεχνική έγινε δημοφιλής επειδή παρέχει δυνατότητες γρήγορης και απεριόριστης επαναδιαμόρφωσης σε μια ήδη γνωστή τεχνολογία. Μεινεκτήματα της SRAM είναι η υψηλή κατανάλωση ενέργειας και η πτητικότητα των δεδομένων. Συγκρινόμενη με άλλες τεχνολογίες μνήμης, ένα στοιχείο της SRAM είναι μεγαλύτερο (απαιτεί 6 έως 12 transistor) και παρουσιάζει σημαντική στατική κατανάλωση εξαιτίας ρευμάτων διαρροής. Ένα ακόμα σημαντικό μειονέκτημα είναι ότι η SRAM δεν διατηρεί τα δεδομένα της χωρίς ενέργεια, που σημαίνει ότι κατά την εκκίνηση το FPGA δεν έχει διαμόρφωση και πρέπει να προγραμματιστεί χρησιμοποιώντας λογική και αποθήκευση εκτός chip. Αυτό επιτυγχάνεται χρησιμοποιώντας μη πτητική μνήμη για διατήρηση της διαμόρφωσης και έναν μικροελεγκτή για να πραγματοποιήσει την διαδικασία του προγραμματισμού κατά την εκκίνηση του FPGA.

Αν και λιγότερο δημοφιλής, πολλές οικογένειες συσκευών χρησιμοποιούν μνήμη flash για να αποθηκεύσουν την πληροφορία διαμόρφωσης. Η μνήμη flash είναι διαφορετική από την SRAM επειδή είναι μη πτητική και μπορεί να εγγραφεί περιορισμένο αριθμό φορών. Η μη πτητικότητα της μνήμης flash σημαίνει ότι τα δεδομένα μπορούν να εγγραφούν και να παραμείνουν αποθηκευμένα ακόμα και χωρίς την παροχή ρεύματος. Σε αντίθεση με τα FPGA που βασίζονται σε SRAM, αυτά που βασίζονται σε μνήμη flash παραμένουν διαμορφωμένα από τον χρήστη και δεν

χρειάζονται επιπλέον υλικό για να προγραμματιστούν κατά την εκκίνηση, που σημαίνει ότι είναι έτοιμα να λειτουργήσουν αμέσως. Επιπλέον, ένα κύτταρο flash μνήμης κατασκευάζεται από λιγότερα transistors και συνεπώς έχει μικρότερες απώλειες λόγω ρευμάτων διαρροής. Ωστόσο, οι συγκεκριμένες μνήμες έχουν περιορισμένο κύκλο αναγνώσεων/εγγραφών και συχνά χαμηλότερες ταχύτητες εγγραφής συγκριτικά με τις SRAM. Ο αριθμός των κύκλων εγγραφής εξαρτάται από την τεχνολογία αλλά τυπικά κυμαίνεται σε μερικά εκατομμύρια φορές. Επιπρόσθετα, οι περισσότερες τεχνικές εγγραφής σε flash απαιτούν υψηλότερη τάση συγκριτικά με τα άλλα κυκλώματα. Επομένως, χρειάζονται βοηθητικά κυκλώματα εκτός chip ή δομές όπως αντλίες τάσης για να πραγματοποιήσουν εγγραφές.

Μια τρίτη προσέγγιση για προγραμματισμό είναι η τεχνολογία μνήμης antifuse. Όπως υποδηλώνει και το όνομα, πρόκειται για έναν μεταλλικό σύνδεσμο που συμπεριφέρεται το αντίθετο από μία ασφάλεια. Ο σύνδεσμος antifuse είναι κανονικά ανοιχτός (μη συνδεδεμένος). Μια προγραμματιστική διαδικασία που περιλαμβάνει είτε έναν προγραμματιστή υψηλού ρεύματος είτε μία ακτίνα laser λιώνουν τον σύνδεσμο για να σχηματιστεί μία ηλεκτρική σύνδεση σαν να υπήρχε καλώδιο ανάμεσα στις άκρες του antifuse. Παρουσιάζει αρκετά πλεονεκτήματα αλλά δεν είναι επαναπρογραμματίσιμο. Μόλις ένας σύνδεσμος λιώσει, έχει υποστεί έναν μη αντιστρεπτό μετασχηματισμό. Τα FPGA που βασίζονται σε αυτή την τεχνολογία θεωρούνται προγραμματιζόμενα μόνο μία φορά. Το γεγονός αυτό περιορίζει την ευελιξία και καθιστά ακατάλληλη την τεχνολογία για προτυποποίηση. Ωστόσο, η χρήση της τεχνολογίας συνοδεύεται από μερικά πλεονεκτήματα. Ο σύνδεσμος έχει πολύ μικρό μέγεθος συγκριτικά με τα κύτταρα των άλλων τεχνολογιών που αποτελούνται από αρκετά transistor. Αυτό οδηγεί σε μικρές καθυστερήσεις διάδοσης και μηδενική στατική κατανάλωση ενέργειας επειδή δεν υπάρχουν πλέον ρεύματα διαφυγής. Επίσης οι σύνδεσμοι είναι ιδιαίτερα ανθεκτικοί στην ακτινοβολία, γεγονός που καθιστά την τεχνολογία κατάλληλη για στρατιωτικές και διαστημικές εφαρμογές.

## 1.5 Έτοιμες βιβλιοθήκες

Πολλά εμπορικά εργαλεία παρέχουν ένα γενικό σετ από τμήματα FPGA, δηλαδή συμβολικές αναπαραστάσεις έτοιμων blocks λειτουργιών που ο χρήστης επιθυμεί να ενσωματώσει στο δικό του FPGA design. Αυτά τα τμήματα παρουσιάζονται στον χρήστη των εργαλείων ως σύμβολα έτοιμα προς χρήση πάνω σε μια πλακέτα.

Τα τμήματα πριν την σύνθεση (pre synthesized components) παρέχονται ως ενότητες κώδικα αντικειμένων (object code) χωρίς να είναι απαραίτητο να αποκαλύψουν τον πηγαίο κώδικα επιπέδου RTL ή netlist. Το σύστημα περιλαμβάνει πολλαπλές βιβλιοθήκες παρέχοντας ένα ολοκληρωμένο σετ τμημάτων προ σύνθεσης, με εύρος από απλές λογικές πύλες μέχρι λειτουργίες υλικού υψηλού επιπέδου, όπως πολλαπλασιαστές και διαμορφωτές παλμών ή ακόμα και επεξεργαστές και περιφερειακά επικοινωνίας.

Αυτά τα έτοιμα τμήματα μπορούν να εισαχθούν σε σχέδια από τον χρήστη του εργαλείου και έπειτα ολόκληρο το design να μεταφερθεί σε μία κατάλληλη φυσική συσκευή. Τα πλεονεκτήματα χρήσης έτοιμων τμημάτων είναι πολλά. Μερικά αναφέρονται ενδεικτικά παρακάτω:

• Μείωση του χρόνου που απαιτείται για την ολοκλήρωση του design καθώς πολλά συχνά χρησιμοποιούμενα τμήματα παρέχονται έτοιμα.

- Ευκολότερος έλεγχος της σωστής λειτουργίας του σχεδίου, αφού τα έτοιμα τμήματα παρέχουν εγγυημένα σωστή λειτουργία.

- Δυνατότητα επαναχρησιμοποίησης τμημάτων πολλές φορές.

- Αποδοτικότερα κυκλώματα, καθώς τα προσφερόμενα τμήματα είναι βελτιστοποιημένα για την λειτουργία που προορίζονται.

## 1.8 Εργαλεία που χρησιμοποιήθηκαν

Στην παρούσα διπλωματική εργασία χρησιμοποιήθηκε το εργαλείο Planahead της εταιρείας Xilinx. Επιτρέπει στον χρήστη να συνθέσει το σχέδιο του, να πραγματοποιήσει ανάλυση του χρονισμού, να ελέγξει την απόκριση του κυκλώματος σε διάφορες εισόδους και καταστάσεις και να προγραμματίσει το design του πάνω σε μία πλακέτα για πραγματική λειτουργία. Με το εργαλείο αυτό, είναι δυνατή η μελέτη των αποτελεσμάτων υλοποίησης πάνω στο FPGA (implementation) και του χρονισμού (timing) με στόχο την ανάλυση της κρίσιμης λογικής. Επιπλέον, βοηθά στην βελτίωση της απόδοσης του design του χρήστη μέσω floor planning, τροποποίησης των περιορισμών και πολλών διαφορετικών ρυθμίσεων σε επίπεδο σύνθεσης και υλοποίησης.

Κάθε design που υλοποιείται με την βοήθεια του Planahead περνάει από τα στάδια του placement, του mapping και του routing. Ακολουθεί μία σύντομη ανάλυση για κάθε ένα από αυτά τα στάδια:

- Placement: είναι ένα απαραίτητο βήμα στην ηλεκτρονική σχεδίαση και αναφέρεται στην ανάθεση τοποθεσιών με ακρίβεια διαφόρων τμημάτων του κυκλώματος μέσα στην περιοχή του chip. Ένα κατώτερης ποιότητας placement όχι μόνο επηρεάζει την απόδοση του chip, αλλά πιθανόν να οδηγήσει στην αδυναμία κατασκευής του παράγοντας καλωδιώσεις μεγάλου μήκους που ξεπερνούν τους διαθέσιμους πόρους για routing. Κατά συνέπεια, η διαδικασία αυτή πρέπει να κάνει τις αναθέσεις ενώπαράλληλα βελτιστοποιεί ένα πλήθος στόχων, ώστε να επιτευχθούν οι προδιαγραφές απόδοσης. Χαρακτηριστικοί στόχοι του placement περιλαμβάνουν:

- Συνολικό μήκος καλωδιώσεων: η ελαχιστοποίηση του μήκους των καλωδιώσεων αποτελεί τον πρωταρχικό στόχο του λογισμικού που υλοποιεί το placement. Αυτό όχι μόνο συντελεί στην μείωση του μεγέθους του chip, αλλά ταυτόχρονα μειώνει την κατανάλωση ισχύος και την καθυστέρηση διάδοσης των σημάτων που είναι ανάλογη του μήκους καλωδίωσης.

- Χρονισμός: ο κύκλος ρολογιού ενός chip καθορίζεται από την καθυστέρηση του μακρύτερου μονοπατιού του, που συχνά αναφέρεται ως κρίσιμο μονοπάτι. Έχοντας καθορισμένες προδιαγραφές απόδοσης, το λογισμικό πρέπει να είναι σίγουρο ότι δεν υπάρχει μονοπάτι που να ξεπερνά την μέγιστη καθορισμένη καθυστέρηση.

- Συμφόρηση: Ενώ είναι απαραίτητο να μειωθεί το μήκος των καλωδιώσεων ώστε να επαρκούν οι πόροι του routing, είναι επίσης αναγκαίο οι πόροι αυτοί να ικανοποιούν προδιαγραφές τοπικότητας πάνω στο chip. Μια περιοχή με συμφόρηση ίσως οδηγήσει σε παρακάμψεις διαδρομών αυξάνοντας τις καλωδιώσεις.

- Ισχύς: η μείωση της ισχύος συνήθως περιλαμβάνει την σωστή κατανομή των τμημάτων για την μείωση της κατανάλωσης και την εξομάλυνση της θερμοκρασίας του chip.

- Ένας δευτερεύων στόχος του λογισμικού είναι η μείωση του χρόνου που απαιτεί για την ολοκλήρωση του το placement.

- Μapping: είναι μία μέθοδος με την οποία το design μπορεί να αντιστοιχιστεί στα φυσικά pins του FPGA στο οποίο θα προγραμματιστεί, δηλαδή πύλες ή διάφορα στοιχεία επιλέγονται από τις βιβλιοθήκες για να υλοποιήσουν τα κυκλώματα του design. Διαφορετικά, είναι το μέσο με το οποίο το design μπορεί να αλληλεπιδράσει με τον "έξω κόσμο". Χαρτογραφώντας εσωτερικά ψηφιακά σήματα σε pins κάποιας συσκευής, η λογική του design μπορεί να επικοινωνήσει με άλλα τμήματα του chip. Ως μέρος του mapping, καθορίζονται και αναλογικά χαρακτηριστικά στα pins, όπως IO standards, δυνάμεις οδήγησης (drive strengths) και slew rates. Σε επίπεδο λογισμικού, το mapping επιτυγχάνεται με χρήση διαμορφώσεων και αρχείων περιορισμών. Ένα FPGA design μπορεί να έχει πολλαπλές καθορισμένες διαμορφώσεις, με κάθε μία να περιέχει το αρχείο περιορισμών (χαρτογράφηση pins, περιορισμοί τοποθέτησης και δρομολόγησης, περιορισμοί ρολογιού και χρονισμού) που απαιτείται για να στοχεύσει σε υλοποίηση πάνω σε διαφορετικές φυσικές συσκευές.

- Routing: είναι μία διαδικασία που στηρίζεται στο placement, που καθορίζει την τοποθεσία κάθε ενεργού στοιχείου που χρησιμοποιείται από το κύκλωμα. Μετά το placement, το routing τοποθετεί καλώδια που απαιτούνται για την σύνδεση των τοποθετημένων εξαρτημάτων ενώ διατηρεί όλους τους κανόνες του design. Στο λογισμικό δίνονται κάποια προϋπάρχοντα πολύγωνα που αποτελούνται από pins και προαιρετικά κάποιες προϋπάρχουσες καλωδιώσεις. Κάθε ένα από αυτά τα πολύγωνα συσγετίζεται με ένα net, βάσει ονόματος ή ενός αριθμού. Η κύρια εργασία του router είναι να δημιουργήσει γεωμετρίες ώστε όλα τα pins του ίδιου net να είναι συνδεδεμένα, κανένα pin συσχετισμένο με άλλο net να μην συνδέεται και όλοι οι κανόνες του design να ισχύουν. Ένας router μπορεί να αποτύχει μην συνδέοντας δύο pins που έπρεπε να συνδεθούν (open), συνδέοντας δύο pins που δεν έπρεπε (short) ή παραβιάζοντας κάποιον κανόνα. Επιπλέον, για να συνδεθούν σωστά τα nets, οι routers πρέπει να τηρήσουν τον χρονισμό, να μην δημιουργήσουν προβλήματα crosstalk, να τηρήσουν τις απαιτήσεις πυκνότητας και πολλά άλλα. Από τα παραπάνω είναι εμφανές ότι το routing είναι μία ιδιαίτερα δύσκολη διαδικασία.

Σχεδόν κάθε πρόβλημα που σχετίζεται με το routing είναι δυσεπίλυτο. Το απλούστερο πρόβλημα δρομολόγησης, γνωστό ως δέντρο του Steiner, εύρεσης του συντομότερου δρόμου για ένα net χωρίς εμπόδια και κανόνες του design είναι NP-δύσκολο αν όλες οι γωνίες επιτρέπονται και NP-πλήρες αν μόνο οριζόντια και κάθετα καλώδια επιτρέπονται. Κατά συνέπεια, οι routers σπάνια προσπαθούν να βρουν μία βέλτιστη λύση. Αντίθετα, σχεδόν ολόκληρη η δρομολόγηση βασίζεται σε ευριστικές λύσεις που προσπαθούν να βρουν απλά μία ικανοποιητική λύση.

5: Διαδικασία κατασκευής κυκλώματος πάνω σε FPGA

Το **Planahead** θα χρησιμοποιηθεί επίσης για την σύνδεση των τριών μερών (κύριο κύκλωμα, κύκλωμα Selector που παρακολουθεί τα σήματα ελέγχου και το digital clock manager που επιλέγει την κατάλληλη συχνότητα λειτουργίας) που συνθέτουν το τελικό κύκλωμα.

Το δεύτερο εργαλείο που θα χρησιμοποιηθεί είναι μία εφαρμογή που αναπτύχθηκε στο πλαίσιο της διπλωματικής και ονομάζεται Planahead Expander. Αναλύει τα αποτελέσματα της χρονικής ανάλυσης του κύριου κυκλώματος (τα αποτελέσματα αυτά παρέχονται από το Planahead) και βγάζει σαν έξοδο τα σήματα ελέγχου καθώς και τις αντίστοιχες συχνότητες λειτουργίας. Η εφαρμογή είναι γραμμένη σε Java για να μπορεί να εκτελεστεί σε οποιοδήποτε λειτουργικό σύστημα. Μαζί με τον Expander έρχεται μία ακόμα εφαρμογή γραμμένη σε Java που ονομάζεται Generator. Η εφαρμογή αυτή διαβάζει το αρχείο που δημιουργήθηκε από τον Expander και δημιουργεί ένα αρχείο με κώδικα VHDL που υλοποιεί το κύκλωμα που παρακολουθεί τα σήματα ελέγχου όπως προσδιορίστηκαν από το προηγούμενο εργαλείο.

Το **ISE** της ΧΙΙ πα χρησιμοποιείται για την κατασκευή της μονάδας digital clock manager. Η μονάδα αυτή μετατρέπει μία συχνότητα εισόδου σε μέχρι έξι (εξαρτάται από τον τύπο του FPGA που χρησιμοποιείται) συχνότητες εξόδου καθορισμένες από τον χρήστη. Στην παρούσα εργασία, μόνο το IP Core Generator του ISE χρησιμοποιείται. Όλες οι άλλες λειτουργίες επιτυγχάνονται μέσα από το Planahead. Η κατασκευή του digital clock manager είναι εύκολη και πραγματοποιείται μέσα από γραφικό περιβάλλον.

Το FPGA Editor από την Xilinx χρησιμοποιείται (εφόσον χρειάζεται) για να συνδέσει τα εσωτερικά σήματα του κύριου κυκλώματος με τις εισόδους του κυκλώματος Selector. Αν δεν υπαρχουν εσωτερικά σήματα, σύνδεση μπορεί να πραγματοποιηθεί μέσω κώδικα VHDL και το FPGA Editor δεν χρειάζεται. Επιπλέον, αυτή η εφαρμογή μπορεί να χρησιμοποιηθεί για πληροφορίες σχετικές με την καθυστέρηση σε συγκεκριμένα δρομολογημένα καλώδια που θα βοηθήσουν τον χρήστη να επιταχύνει ακόμα περισσότερο το κύριο κύκλωμα.

Το **Isim** από την Xilinx είναι ένας προσομοιωτής που χρησιμοποιείται για να ελεγχεί η λειτουργία του νέου και βελτιωμένου κυκλώματος. Ο προσομοιωτής δίνει την δυνατότητα ελέγχου των κυματομορφών εισόδου και εξόδου του κυκλώματος.

## 2. Introduction

## 2.1 Embedded systems

A simple definition of an embedded system is whatever device which contains a task specific central possessing unit (CPU) and not a general purpose one. Usually, the system must meet real time computing constrains and it is embedded as a part of a whole device that often includes hardware and mechanical parts.

Embedded systems range from mobile devices, such as digital watches and portable music players, to large scale application devices, such as traffic lights and factories controllers, to highly complicated systems like cars. The complexity of the embedded systems may vary from small like a simple micro-controller, to large multi-unit systems, peripheral devices and network controllers.

Modern systems often rely on micro-controllers, which are processors with embedded memory or other peripheral devices. Micro-processors are quite common too, especially on highly complicated systems. Processors vary from general purpose to custom designed for a highly specialised application. A typical example of a specialised processor is a digital signal processor or DSP for short.

Why are micro-processors currently in use? There a two major answers to that question:

- Micro-processor is a very efficient way of implementing digital systems because they offer the ability of reusing many hardware designs with a simple software update. This is very important and the main reason is that designing integrated circuits remains an expensive and time consuming process.

- Micro-processors facilitate designing of families of products which can be made in order to provide different specifications in various price levels. They may also be expandable so that they keep up with the rapidly changing market needs.

## 2.2 Embedded computing - challenges

Embedded computing is, according to many opinions, a more demanding process than writing software for personal computers. Proper functionality remains important for both personal and embedded computing, but embedded applications must meet many more constrains.

- *Complicated algorithms:* Functions executed by a micro-processor may be highly complicated. For instance, controlling the fuel flow in a car.

- *User interface:* micro computers are usually used for controlling complicated user interfaces which contain a lot of lists and buttons.

For example, a global positioning system (GPS) uses a very expressive user interface.

Furthermore, many tasks of embedded systems must be completed within strict deadlines, which adds more constrains and complexity into designing embedded software. Some of these extra demands are mentioned below.

- *Real time:* many embedded systems must operate in real time. If data is not ready until a specific deadline, the whole system may collapse. Not meeting all timing constrains in a system, may result in dissatisfied customers or even deaths (please consider a system used in surgeries or an airplane controller).

- *Multirate functions:* Many functions in embedded systems must meet all timing constrains but also many real time processes may take place in parallel. It is highly likely that some of these processes have a slow pace and others have a faster one. Multimedia applications are a good example of multirate functions, because audio and video segments are executed in the system with different rates but they must always be synchronised in order to be presented to the user.

- *Manufacturing costs:* The total manufacturing cost is a critical part in many applications and it is defined by many factors such as the type of processor used, the amount of on board memory and the number of peripherals.

- *Power:* Power consumption affects the battery life of all mobile devices, which is crucial in many applications. It also affects the heat production of the device which may lead to temporal malfunction.

- *Limited hardware resources:* Unlike personal computers, most embedded systems possess limited hardware resources to take advantage of (for example, power coming from a battery, limited ram onboard, few or even none peripheral I/O devices). Therefore, it is necessary that all resources are used efficiently and the user application will function correctly.

External limitations are an important source of difficulties in designing embedded systems. During designing process, all important problems mentioned below must be taken into serious consideration.

How much hardware is needed? There is a way of controlling the quantity of processing power given to a problem by carefully choosing the type of micro processor, the amount of RAM, the I/O devices and so on. The choice of the hardware components is very important if we recall that many timing, cost and performance constrains must be met. If the system lacks hardware, it will miss its deadlines and it will not meet its user's expectations. If the system possesses too much hardware, the total cost of the system will rise without any noticeable performance improvements.

How are deadlines satisfied? The absolutely raw way of satisfying a deadline is by accelerating the hardware, so that commands execute faster. However, this may lead to a more expensive system. Moreover, it is

likely that the overclock of the processor won't benefit the execution time due to memory limitations.

How is power consumption minimised? Power consumption is a major problem almost on every embedded system. By slowing down non crucial datapaths, the system achieves better power consumption and at the same time it meets all deadlines. However, the designing process requires a lot of attention and it is time consuming because of its complexity.

Upgradable design. The hardware platform of a system can be used for many generations of products with zero or few modifications. However, adding new capabilities is still desirable and it can be achieved through software updates. Therefore, the correct and future proof design of the hardware is very important, so that software which is not yet designed will be executed without any problems on the platform.

*Reliability*. Reliability is an important feature of both hardware and software. It is also desirable in some applications such as safety critical systems. Careful planning and design are needed in order reliable products to be built.

#### 2.3 FPGA - evolution

FPGA (stands for Field Programmable Gate Array) is a type of general purpose programmable integrated circuit which possesses a large number of standardized gates and other digital components, such as counters, registers, PLL generators and so on. Some FPGAs embody analog functions as well. During the programming process of a FPGA, that always takes place when the FPGA is on the printed circuit, all desired functions are activated and interconnected. The final result is that the FPGA behaves as an integrated circuit with a specific function.

The source code, which the FPGA is programmed with, is usually written in a hardware description language like VHDL or Verilog. Its application field is quite similar to other programmable integrated circuits, such as PLDs and ASIC. However, FPGAs have some unique features:

- FPGA forgets its programming every time it is unplugged. Therefore, it requires an external micro processor or a non volatile memory unit, which will program the main FPGA unit when needed.

- FPGA programming may change every time that the software located in the micro processor or the memory unit is modified.

- There is no upper limit on how many times a FPGA unit can be programmed.

- Power consumption is significantly increased compared to ASIC.

FPGAs are very suitable in applications where their parameters change often or in small production rates, while ASICs, due to mass production, is cheaper in large quantities and the desired function is

strictly predefined with no errors (ASICs cannot be reprogrammed. The can be programmed once).

The basic structural unit of the FPGA is a logical block, the combinations of which implement boolean functions that express functions of a digital circuit. Depending on the size of the circuit, many logical blocks can be combined to implement all necessary boolean functions.

FPGA industry resulted from programmable read only memories (PROM) and programmable logic devices (PLD). Both of them are capable of banch programming. However, their programming was depending on wired logic between gates.

FPGAs were skyrocketed during the 90s as long as design complexity and production rates are concerned. During the same era, FPGAs were only used in telecommunications and networks. However, during the late 90s, they were used in more consumer applications, such as car industry and various industrial applications.

A resent trend is a hybrid architecture, which means combining the logical blocks of the traditional FPGAs with embedded processors and the required peripheral units to form a complete system on a programmable chip. This hybrid architecture limits the power consumption, creates a system with smaller size but more reliable. (Wolf, 2008)

## 2.4 Benefits of FPGA technology

FPGA chip adoption across all industries is driven by the fact that they combine the best parts of ASICs and processor based systems. FPGAs provide hardware timed speed and reliability, but they do not require high volumes to justify the large upfront expense of custom ASIC design. Reprogrammable silicon also has the same flexibility of software running on a processor based system, but it is not limited by the number of processing cores available. Unlike processors, FPGAs are truly parallel in nature, so different processing operations do not have to compete for the same resources. Each independent processing task is assigned to a dedicated section of the chip and can function autonomously without any influence from other logic blocks. As a result, the performance of one part of the application is not affected when more processing is added. (The Linley Group, 2009)

The main benefits of using FPGAs can be listed as follows:

• **Performance**. Taking advantage of hardware parallelism, FPGAs exceed the computing power of digital signal processors (DSPs) by breaking the paradigm of sequential execution and accomplishing more per clock cycle. BDTI, a noted analyst and benchmarking firm, released benchmarks showing how FPGAs can deliver many times the processing power per dollar of a DSP (BDTI Industry Report, 2006) solution in some applications. Controlling inputs and outputs

- at the hardware level provides faster response times and specialized functionality to closely match application requirements.

- Time to market. FPGA technology offers flexibility and rapid prototyping capabilities in the face of increased time to market concerns. An idea or a concept can be tested and verified in hardware without going through the long fabrication process of custom ASIC (Thompson, 2004) design. Incremental changes and iterations on an FPGA design can be implemented within hours instead of weeks. Commercial off the shelf hardware is also available with different types of I/O already connected to a user programmable chip. The growing availability of high level software tools decreases the learning curve with layers of abstraction and often offers valuable IP cores (prebuilt functions) for advanced control and signal processing.

- **Cost**. The nonrecurring engineering expense of custom ASIC design far exceeds that of FPGA based hardware solutions. The large initial investment in ASIC is easy to justify for OEMs shipping thousands of chips per year, but many end users need custom hardware functionality for the tens to hundreds of systems in development. The very nature of programmable silicon means that fabrication costs or long lead time for assembly are absent. Because system requirements often change over time, the cost of making incremental changes to FPGA designs is negligible when compared to the large expenses of respinning an ASIC.

- Reliability. While software tools provide the programming environment, FPGA circuitry is truly a "hard" implementation of program execution. Processor based systems often involve several layers of abstraction to help schedule tasks and share resources among multiple processes. The driver layer controls hardware resources and the operating system manages memory and processor bandwidth. For any given processor core, only one instruction can be executed at a time and processor based systems are continually at risk of time critical tasks preempting one another. FPGAs, which do not use an operating system, minimize reliability concerns with true parallel execution and deterministic hardware dedicated to every task.

- Long term maintenance. As mentioned earlier, FPGA chips are field upgradable and do not require the time and expense involved with ASIC redesign. Digital communication protocols, for example, have specifications that can change over time and ASIC based interfaces may cause maintenance and forward compatibility challenges. Being reconfigurable, FPGA chips can keep up with future modifications that might be necessary. As a product or system matures, functional enhancements can be made without spending time redesigning hardware or modifying the board layout. (National Instruments, 2012)

#### 2.5 FPGA structure

FPGAs consist of three fundamental components: logic boards, input and output ports and programmable routing. The type of logic board used affects the speed and area efficiency of the FPGA. A common type of logic board found in modern FPGAs is based on look up tables (LUT), which consists of an N:1 multiplexer and an N-bit memory. As far as digital logic is concerned, a LUT simply enumerates a truth table, giving the ability to the FPGA to implement arbitrary digital logic. (Brown & Rose)

#### LUT

A LUT is an array that replaces runtime computations with a simpler and faster array indexing operation. Although the LUT has been selected as the core computational unit in commercial FPGAs, its size in each logic board has been carefully considered. Larger lookup tables can handle more complex logic functions, thus reducing the wiring delay between blocks. However, this results in slower LUTs due to the usage of larger multiplexers. On the other hand, smaller lookup tables result in larger number of logic blocks used which increases wiring delays in the design. In addition, there is a single-bit storage element in the base logic block which is a D flip flop. The output multiplexer selects a result either from the function implemented in the LUT or from the stored bit in the flip flop.

#### Interconnection

Modern FPGAs are designed using the island styled architecture. According to this, logic blocks are tiled in a two dimensional array and interconnected with a pattern. The logic blocks form the "islands" which float in the ocean of interconnections. This architecture allow computations to be performed spatially in the fabric of FPGA and large computations are broken into pieces and mapped into physical logic blocks in the array.

The logic block accesses its neighbors through the connection block, which connects logic block input and output terminals to routing resources through programmable switches or multiplexers. The connection block allows logic block inputs and outputs to be assigned to arbitrary horizontal and vertical tracks, increasing routing flexibility.

Each configurable element of the FPGA requires 1 bit of storage to maintain a user defined configuration. For a LUT based FPGA, these programmable locations generally include the contents of the logic block and the connectivity of the routing fabric. Configuration is accomplished through programming of storage bits connected to these programmable locations according to user's input. There are many methods for storing a single bit of binary information, the most popular being SRAM, antifuse and flash memory. (Kuon, Tessier, & Rose, 2008)

The most widely used method for storing configuration information in commercially available FPGAs is volatile **static RAM**, better known as SRAM. This method was made popular because it provides fast and

unlimited reconfiguration in a well known technology. Drawbacks of SRAM are the high power consumption and data volatility. Compared to other memory technologies, the SRAM cell is larger (requires 6 to 12 transistors) and dissipates significant static power because of current leakage. Another major disadvantage is that SRAM does not maintain its contents without power, which means that during power up the FPGA is not configured and must be programmed using off chip logic and storage. This can be achieved by using a non volatile memory to hold the configuration and a micro controller to perform the programming procedure.

Although less popular than SRAM, many families of devices use **flash memory** to store configuration information. Flash memory is different from SRAM because it is non volatile and can be written a limited number of times. The non volatility of flash memory means that data can be written to it and remains stored when power is removed. In contrast with SRAM based FPGA, a flash based one remains configured by user defined logic and does not require extra hardware to be programmed during boot up, which means that a flash based FPGA can be ready immediately. Moreover, a flash cell is made by less transistors compared to SRAM cells, thus there are fewer transistors to contribute to current leakage. However, flash memory has a limited read/write cycle lifetime and often offers less write speeds compared to SRAM. The number of write cycles varies depending on technology, but is typically some million times. Additionally, most flash write techniques require higher voltage compared to normal circuits; they require additional off chip circuitry or structures like charge pumps on chip to be able to perform writes.

A third approach to achieving programmability is antifuse technology. Antifuse, as its name suggests, is a metal based link that behaves oppositely of a fuse. The antifuse link is normally open (unconnected). A programming procedure that involves either a high current programmer or a laser melts the link to form an electrical connection across it, like creating a wire between the antifuse endpoints. Antifuse has several advantages but it is not reprogrammable. Once a link is fused, it has undergone a physical transformation that cannot be reversed. FPGAs based on this technology are generally considered one time programmable. This severely limits their flexibility in terms of reconfigurable computing and nearly eliminates this technology for use in prototyping environments. However, there are some distinct advantages of using antifuse in an FPGA platform. First of all, the antifuse link can be made very small compared to the large multi transistor SRAM cell and does not require any transistors in order to be formed. This results in very low propagation delays across links and zero static power consumption, because there is no longer current leakage due to transistors. Antifuse links are also not susceptible to high energy radiation particles that induce errors known as single event upsets making them more likely candidates for space and military applications.

#### 2.6 Software libraries

Many commercial tools provide a generic set of FPGA macro components – symbolic representations of blocks of functionality that a user desires to add to an FPGA design. These components are presented to the user as FPGA-ready schematic symbols (or graphical representations) that can be instantiated into a design. FPGA-ready schematic components are like traditional PCB-ready components, except instead of the symbol being linked to a PCB footprint, each is linked to a pre-synthesized EDIF model.

The pre-synthesized components are supplied as object code entities without having to expose underlying RTL- or netlist-level source code. The system includes multiple libraries providing a comprehensive set of presynthesized components, ranging from simple gate-level functional blocks, up through high-level hardware functions, such as multipliers and pulsewidth modulators, to high-level functions, such as processors and communications peripherals. These components can be instantiated into designs by the system user and then the whole design can be targeted to a suitable physical device. There are many advantages of using pre built components. Some of them are referred below:

- The time needed to complete a design is reduces because many of the most commonly used components are already built by the tool.

- Debugging the hardware design is easier because the components provided are functioning correctly and are error free.

- A segment can be used many times.

- More efficient circuits are created because the provided segments are already optimized for a specific function.

- The result is a design environment that offers true device vendor independence, with the ability to quickly retarget the FPGA design to a different device with relative ease.

#### 2.7 Tools used

In the present diploma thesis the main software tool used was the Xilinx **Planahead**. It allows the user to synthesize his design, to perform a timing analysis, to check the performance of the circuit in many different inputs and to program that design onto a physical device. With that tool it is possible to study the implementation and the timing results in order to analyse the critical logic. Moreover, it helps improving the performance of the user's design through floor planning, constrains modification and many more synthesis and implementation settings.

Every single design which is implemented with Planahead goes through placement, mapping and routing. All three stages are explained in detail just below:

**Placement** is an essential step in electronic design automation - the portion of the physical design flow that assigns exact locations for various

circuit components within the chip's core area. An inferior placement assignment will not only affect the chip's performance but might also make it non manufacturable by producing excessive wire length, which is beyond available routing resources. Consequently, a placer must perform the assignment while optimizing a number of objectives to ensure that a circuit meets its performance demands. Typical placement objectives include:

- *Total wire length*: Minimizing the total wire length, or the sum of the length of all the wires in the design, is the primary objective of most existing placers. This not only helps minimize chip size, and hence cost, but also minimizes power and delay, which are proportional to the wire length (This assumes long wires have additional buffering inserted; all modern design flows do this.)

- *Timing*: The clock cycle of a chip is determined by the delay of its longest path, usually referred to as the critical path. Given a performance specification, a placer must ensure that no path exists with delay exceeding the maximum specified delay.

- Congestion: While it is necessary to minimize the total wire length to

meet the total routing resources, it is also necessary to meet the

routing resources within various local regions of the chip's core area.

A congested region might lead to excessive routing detours, or make

it impossible to complete all routes.

- *Power*: Power minimization typically involves distributing the locations of cell components so as to reduce the overall power consumption, alleviate hot spots, and smooth temperature gradients.

- A secondary objective is placement runtime minimization.

**Mapping:** is a method by which the design can be interfaced to the physical pins of the FPGA device in which it is programmed. Put another way, it is the means by which the design can interact with the 'outside world'. By mapping internal digital signals to the device pins, the logic is able to communicate to other areas of your product. As part of this mapping, you would also define analog characteristics of the pins, such as IO standards, drive strengths and slew rates.

This mapping is achieved using ports (or port components), configurations and constraint files. An FPGA design can have multiple defined configurations, with each configuration containing the constraint files (pin mappings, clock constraints, place and route constraints) required to target a different physical device.

Routing: In electronic design, wire routing, commonly called simply routing, is a step in the design of printed circuit boards (PCBs) and integrated circuits (ICs). It builds on a preceding step, called placement, which determines the location of each active element of an IC or component on a PCB. After placement, the routing step adds wires needed to properly connect the placed components while obeying all design rules for the IC.

The task of all routers is the same. They are given some pre-existing polygons consisting of pins (also called terminals) on cells, and optionally some pre-existing wiring called pre routes. Each of these polygons are associated with a net, usually by name or number. The primary task of the router is to create geometries such that all terminals assigned to the same net are connected, no terminals assigned to different nets are connected, and all design rules are obeyed. A router can fail by not connecting terminals that should be connected (an open), by mistakenly connecting two terminals that should not be connected (a short), or by creating a design rule violation. In addition, to correctly connect the nets, routers may also be expected to make sure the design meets timing, has no crosstalk problems, meets any metal density requirements, does not suffer from antenna effects, and so on. This long list of often conflicting objectives is what makes routing extremely difficult.

Almost every problem associated with routing is known to be intractable. The simplest routing problem, called the Steiner tree problem, of finding the shortest route for one net in one layer with no obstacles and no design rules is NP-hard if all angles are allowed and NP-complete if only horizontal and vertical wires are allowed. Variants of channel routing have also been shown to be NP-complete, as well as routing which reduces crosstalk, number of vias, and so on. Routers therefore seldom attempt to find an optimum result. Instead, almost all routing is based on heuristics which try to find a solution that is good enough.

Design rules sometimes vary considerably from layer to layer. For example, the allowed width and spacing on the lower layers may be four or more times smaller than the allowed widths and spacings on the upper layers. This introduces many additional complications not faced by routers for other applications such as printed circuit board or Multi-Chip Module design. Particular difficulties ensue if the rules are not simple multiples of each other, and when vias must traverse between layers with different rules.

**Planahead** will also be used to connect the three components (master circuit, Selector which monitors controls signals, and the dcm which chooses the appropriate clock frequency) that compose the final circuit.

The second tool used is a custom made application called **Planahead Expander** which analyzes the timing results of the master circuit (provided by Planahead) and outputs the control signals as well as the operational frequency of each one. This application is written in Java in order to be executed under every operating system. Along with Expander, there is another Java application called **Generator**, which parses the file generated by Expander and creates a file with VHDL code that implements the circuit that monitors the control signals determined by Expander.

**ISE** by Xilinx is also used to create the dcm unit. The dcm unit converts an input frequency into up to six (depending on the type of FPGA

used) output clocks with user controlled frequencies. In this thesis, only the IP Core Generator of the ISE tool will be used. All the other operations will be performed by Planahead instead. The building of the dcm is easy and it is performed by a graphical user interface.

**FPGA editor** by Xilinx is used (if necessary) in order to connect the internal signals of the master circuit with the input pins of the selector circuit. If no internal signals exist, the connection can be done by VHDL code and FPGA editor will not be needed. Furthermore, this application can be used in order to extract delays on specific routed wires which will help user accelerate even more the master circuit.

**ISim** by Xilinx is the simulator that will be used in order to verify that the new and enhanced circuit performs better than the original. The simulator can be used to check the input and output waveforms of the circuits.

# 3. Data path control path,

#### 3.1 General

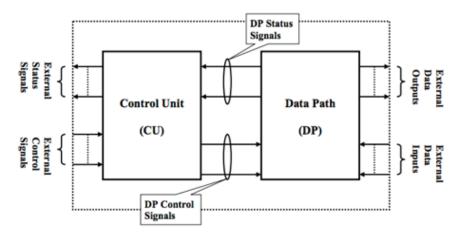

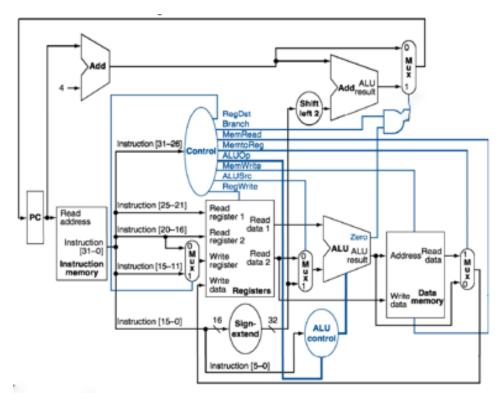

Most processors and other complicated hardware circuits are typically divided into two major components: **data path** and a control unit or **control path**. The data path contains all the hardware necessary to perform all operations supported by the system and holds data in memory. In many cases, these hardware modules are parallel to one another and the final result is determined by multiplexing all the partial results. The control unit determines the operation of the data path, by activating switches and passing control signals to the various multiplexers according to the instructions of the memory. In this way, the control unit can specify how the data flows through the data path. (Digital System Design Using Data Path and Control Unit, 2013)

The general structure of a modern digital system that performs a specific task is as follows:

6: Control and Data Path

- External control signals: they specify the task required by the circuit (for example calculation of the average of some integers)

- **External status signals**: indicate the status of the circuit (such as finished processing, error or overflow detected)

- External data inputs/outputs: data going into the circuit or out of it (the integers to be averaged and their average)

- **Data path control signals**: signals generated by the control unit to control different blocks in the data path (like shift registers, counters, multiplexers)

- **Data path status signals**: signals that indicate the status of some blocks in the data path (for instance when an adder produces a carry or an overflow, when the sign bit of the result is negative)

## 3.2 Data path

The data path contains blocks that only deal with data; they do not provide control to any other blocks and themselves need to be controlled (possibly by the control unit). Data path blocks can be viewed as the workers that perform certain tasks on the data who need to be managed by someone else (in this case the control unit is the manager that tells every "worker" in the data path what to do). Some examples of data path blocks are:

- **Registers**: parallel load registers to read data in parallel, shift registers to read data serially one bit at a time, digit serial registers that read data serially one digit at a time, where the digit size could be 4 bits, 8 bits and so on.

- Arithmetic circuits: adders, subtractors, multipliers

- Multiplexers: to route one out of many data signals to one or more destinations

- **Counters**: As timers and counters (for example to count how many times a certain event occurred, or how much data was read)

- Comparators and logic circuits: logic operations like AND, OR, XOR and so on

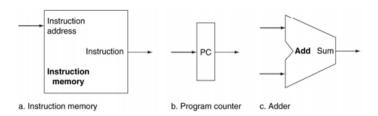

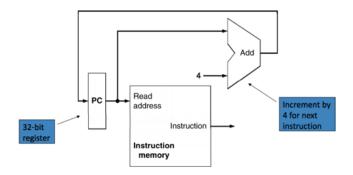

As an example, we will build a simple MIPS data path incrementally considering only a subset of the supported instructions. In order to build the instruction fetch block, we need the following three components:

7: Basic components of Control and Data Path

An adder is required to increment the PC (program counter) to the address of the next instruction. It can be implemented as an ALU permanently wired to perform only addition. As a result, no extra control signal is required. A memory unit is needed to store instructions of a program and supply instructions given an address. It needs to provide only read access once the program is loaded so no control signal is required. Finally, program counter or instruction address register is a register that holds the address of the current instruction. A new value is written to it every clock cycle. No control signal is required to enable write. By combining those three components, we create a data path portion for instruction fetch:

8: MIPS Data Path

Another example of a datapath is the following. Let us consider addition as an arithmetic operation. Data will be retrieved from memory in detail and contents from registers reg1 and reg2 are added and the result is stored in reg3. The sequence of operations is:

- reg1out, Xin

- reg2out, choose X, addition, Yin

- Yout, reg3in

The control signals written in one line are executed in the same clock cycle. All other signals remain untouched. So, in the first step the contents of reg1 are written into the register X through the bus. Then, the content of reg2 is placed onto the bus and the multiplexer is made to choose input X as the contents of reg1 are stored in register X. The ALU then adds the contents in the register X and reg2 and stores the result of the addition in the special temporary register Y. In the final step the result stored in Y is sent over to reg3 over the internal processor bus. Only one register can output its data onto bus in a single step, hence steps 2 and 3 cannot be combined. (Processor: Datapath and Control, 2014)

## 3.3 Control path (control unit)

The control unit (CU) handles all processor control signals. It directs all input and output flow, fetches code for instructions from microprograms and directs other units and models by providing control and timing signals. A control unit component is considered as the brain because it issues orders to just about everything and ensures correct instruction execution. John von Neumann included the control unit as part of his architecture. In modern computer designs, the control unit is typically an internal part of the CPU with its overall role and operation unchanged since its introduction. (Englander, 2009)