### ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΥΠΟΛΟΓΙΣΤΙΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Τεχνικές χρονοδρομολόγησης εφαρμογών για δίκαιη κατανομή πόρων σε πολυπύρηνες αρχιτεκτονικές

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ του

Θεόδωρου Ι. Μαρινάκη

**Επιβλέπων**: Νεκτάριος Κοζύρης Καθηγητής Ε.Μ.Π.

# Τεχνικές χρονοδρομολόγησης εφαρμογών για δίκαιη κατανομή πόρων σε πολυπύρηνες αρχιτεκτονικές

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ του

## Θεόδωρου Ι. Μαρινάκη

**Επιβλέπων**: Νεκτάριος Κοζύρης Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 1<sup>η</sup> Ιουλίου 2016.

| (Υπογραφή)        | (Υπογραφή)       | (Υπογραφή)           |

|-------------------|------------------|----------------------|

|                   |                  |                      |

| Νεκτάριος Κοζύρης | Γεώργιος Γκούμας | Δημήτριος Τσουμάκος  |

| Καθηγητής Ε.Μ.Π.  | Λέκτορας Ε.Μ.Π.  | Επιίκουρος Καθηγητής |

|                   |                  | Ιονίου Πανεπιστημίου |

| (Υπογραφή) | ) |

|------------|---|

|------------|---|

## ΜΑΡΙΝΑΚΗΣ ΘΕΟΔΩΡΟΣ

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright © Θεόδωρος Ι. Μαρινάκης, 2016 Με επιφύλαξη παντός δικαιώματος. All rights reserved

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

## Περίληψη

Η χρονοδρομολόγηση είναι μια διαδικασία, η οποία αφορά το διαμοιρασμό πόρων σε εργασίες ανά τακτά χρονικά διαστήματα, με σκοπό τη βελτιστοποίηση ορισμένων στόχων. Ένας τομέας, στον οποίο χρησιμοποιείται κυρίως, είναι τα υπολογιστικά συστήματα. Όσον αφορά μονοπύρηνες αρχιτεκτονικές έχουν αναπτυχθεί τεχνικές χρονοδρομολόγησης, οι οποίες ανταπεξέρχονται αποδοτικά στο διαμοιρασμό του χρόνου του πυρήνα ανάμεσα στις διεργασίες του συστήματος. Η ανάγκη όμως για εξυπηρέτηση μεγαλύτερου φόρτου εργασίας οδήγησε τους κατασκευαστές στη δημιουργία πολυπύρηνων αρχιτεκτονικών ενσωματώνοντας πολλούς πυρήνες μέσα σε ένα ολοκληρωμένο κύκλωμα (CMP). Αντίθετα με τα συμμετρικά πολυπύρηνα συστήματα (SMP), οι πυρήνες των CMPs δεν θεωρούνται ανεξάρτητες μονάδες εφόσον μοιράζονται στοιχεία της αρχιτεκτονικής, όπως το τελευταίο επίπεδο κρυφής μνήνης και το δίαυλο μνήμης.

Στα πολυπύρηνα συστήματα αυτά (CMP) ενσωματώθηκαν, αυτούσιες ή με λίγες αλλαγές, οι τεχνικές χρονοδρομολόγησης, που είχαν υλοποιηθεί στις συμμετρικές (SMP) αρχιτεκτονικές. Εκτελώντας προγράμματα παράλληλα σε πυρήνες που μοιράζονται στοιχεία υπάρχει πιθανότητα να παρατηρήσουμε μείωση στην απόδοσή τους λόγω ανταγωνισμού μεταξύ τους. Υιοθετώντας τεχνικές που δε λαμβάνουν υπόψιν τους τον ανταγωνισμό αυτόν, θεωρώντας τους πυρήνες απομονωμένες μονάδες που δεν μοιράζονται στοιχεία, οδηγούμαστε σε αποτελέσματα που δεν πληρούν τις αρχές της χρονοδρομολόγησης. Μερικά προβλήματα που δημιουργούνται είναι τα εξής: πολύ χαμηλή απόδοση των εφαρμογών, άνισος διαμοιρασμός των πυρήνων μεταξύ τους και συνεπώς απρόβλεπτη και ασταθής συμπεριφορά του συστήματος.

Ο σκοπός αυτής της διπλωματικής είναι να παρουσιάσουμε τεχνικές που βελτιώνουν την άνιση κατανομή των πόρων, λαμβάνοντας υπόψιν την διαμάχη των διεργασιών για τα μοιραζόμενα στοιχεία του τσιπ και τις καταστροφικές συνέπειες που αυτή αποφέρει στην αξιοπιστία του συστήματος. Επικεντρωνόμαστε σε τεχνικές που προσφέρουν δικαιοσύνη στις εφαρμογές με τους παρακάτω τρόπους. Στην πρώτη προσέγγιση σχεδιάζουμε έναν χρονοδρομολογητή που προταιρεότητα του είναι να αποφύγει τον ανταγωνισμό των διεργασιών, βασισμένοι σε ένα σχήμα ταξινόμησης και σε ένα μοντέλο που προβλέπει πως οι διάφορες κατηγορίες διεργασιών αλληλεπιδρούν. Η επόμενη μέθοδος προσπαθεί να διαχειριστεί τον ανταγωνισμό των διεργασιών. Λαμβάνει υπόψιν τη μείωση της απόδοσης των διεργασιών και τις ευνοεί αναλόγως. Αυτο το επιτυγχάνει δίνοντας ευκαιρία συχνότερης εκτέλεσης σε εκείνες που υποφέρουν περισσότερο, σε βάρος εκείνων που εκτελούνται με υψηλότερη απόδοση. Τέλος επεκτείναμε την δεύτερη τεχνική μας, έτσι ώστε να αποφεύγει μέρος του ανταγωνισμού και να διαχειρίζεται το υπόλοιπο.

Δοκιμάζοντας τις τεχνικές μας σε μια ποικιλία πειραμάτων και συγκρίνοντας τα αποτελέσματα με χρονοδρομολογητή που χρησιμοποιείται σε εμπορικά πολυπύρηνα συστήματα (Linux scheduler), καταλήξαμε στο εξής συμπέρασμα. Οι προτεινόμενες εναλλακτικές είναι ικανές να βελτιώσουν σε μεγάλο βαθμό την άνιση κατανομή των πόρων και να προσφέρουν αξιοπιστία στην απόδοση του συστήματος.

**Λέξεις Κλειδιά:** Χρονοδρομολόγηση, ανταγωνισμός, μοιραζόμενοι πόροι, πολυπύρηνες αρχιτεκτονικές, δικαιοσύνη

### **Abstract**

Scheduling is a decision-making process that deals with the assignment of resources to tasks over given periods, aiming to optimize one or more objectives. Responsible for efficient distribution of the CPU time among the processes, scheduler has become an essential part of computer systems. OS schedulers for single processor architectures have become so optimized that need for further improvements dramatically subsided. The scheduling problem was considered solved until the arrival of chip multiprocessors (CMP). Driven by the critical problems of transistor shrinking, heat generation, power consumption and poor performance improvement, manufacturers abandoned single core architectures and turned to chips with multiple cooler-running, energy-efficient processing cores. In order to provide a cost-effective solution, they integrated the cores into a single circuit die, sharing architectural components, such as the last level cache and the memory bus.

Scheduling policies developed for symmetric multiprocessors (SMP) have been integrated without modifications into CMPs. While applications run on neighboring cores of a CMP, they contend with each other for the shared resources. This contention can result in great performance degradation for the applications that are concurrently executed. For this reason, treating the cores of a CMP as isolated and independent units is a very optimistic abstraction and can cause great problems to the objectives a scheduler tries to optimize. First and foremost, it cannot be assured that applications would make adequate progress. In addition, it is observed that resources cannot be fairly distributed among the applications of the system. As a result, poor fairness enforcement can lead to unstable and unpredictable performance of the system.

In this paper, we develop 3 scheduling techniques aiming to improve the unequal sharing of the resources, taking into consideration the destructive effects of applications interference, when contending for the shared resources. On our first approach, we attempt to avoid pairing applications that interfere destructively. We build a contention-aware scheduler, based on a classification scheme and an interference prediction model. On the next approach, we manage the results of the interference, boosting the performance of applications based on their IPC reduction. Applications that are heavily impacted have the opportunity to increase their running time at the expense of the well-performed. Finally, we extend our previous technique, aiming to avoid a part of the contention and manage the rest of it.

Evaluating our proposed scheduling policies on a variety of workloads and comparing them with the Linux scheduler, we come to the following conclusions. All of them manage to overcome the problem of unfair distribution, creating an environment where Quality of Service (QoS) guarantees are possible to be provided and Service Level of Agreements (SLAs) can be enforced.

**Key words:** Scheduling, contention, shared resources, chip multiprocessor, fairness

## Ευχαριστίες

Σε αυτό το σημείο θα ήθελα να ευχαριστήσω τον επιβλέποντα καθηγητή μου κ. Ν. Κοζύρη που μου έδωσε την ευκαιρία να ασχοληθώ με αυτό το θέμα. Επίσης θα ήθελα να ευχαριστήσω το κ. Γ. Γκούμα για τις συμβουλές του και τον Αλέξανδρο Χαριτάτο, που με βοήθησε στην περάτωση της εργασίας.

Τέλος θα ήθελα να ευχαριστήσω τον πατέρα και την μητέρα μου που με υποστήριξαν σε όλη μου τη προσπάθεια και με ενθάρρυναν διαρκώς με την αγάπη τους. Ευχαριστώ ιδιαιτέρως τη Φλώρα που στάθηκε στο πλευρό μου τις πιο δύσκολες στιγμές μου και τους φίλους μου που με άκουγαν υπομονετικά.

# Κεφάλαιο 1 Εισαγωγή

#### 1.1 Χρονοδρομολόγηση και Εφαρμογές

Η χρονοδρομολόγηση είναι μια διαδικασία, κατά την οποία λαμβάνονται αποφάσεις για το διαμοιρασμό πόρων σε εργασίες, με τέτοιο τρόπο ώστε να επιτυγχάνονται συγκεκριμένοι στόχοι. Παίζει πολύ σημαντικό ρόλο σε διάφορους τομείς και έχει εφαρμογές σε εργοστάστια παραγωγής, σε υπηρεσίες μεταφορών και σε υπολογιστικά συστήματα. Σε κάθε τομέα οι πόροι, οι εργασίες και οι προς εκπλήρωση στόχοι παίρνουν ποικίλες μορφές.

Ας εξετάσουμε, αρχικά, ένα εργοστάσιο που παράγει χάρτινες συσκευασίες για σκυλοτροφές, κάρβουνα και τσιμέντο. Η διαδικασία παραγωγής αποτελείται απο διάφορα στάδια, όπως τύπωμα λογοτύπου ή ράψιμο των πλευρών της συσκευασίας. Σε κάθε στάδιο τα μηχανήματα διαφέρουν ως προς τα χαρακτηριστικά τους και τις λειτουργίες που εξυπηρετούν. Τα μηχανήματα αυτά αποτελούν τους πόρους του εργοστασίου. Ανάλογα με το είδος της παραγγελίας, κάποιες εργασίες πρέπει να πραγματοποιηθούν στα μηχανήματα. Οι παραγγελίες δεν αφορούν μόνο ένα προϊόν, άρα και οι λειτουργίες των μηχανημάτων διαφέρουν απο παραγγελία σε παραγγελία. Ένας στόχος θα μπορούσε να είναι η ελαχιστοποίηση του χρόνου παραγωγής μιας συγκεκριμένης παραγγελίας, αν υποθέσουμε ότι ένας υψίστης σημασίας πελάτης απαιτεί γρήγορη παράδοση. Ένας άλλος στόχος μπορεί να είναι η αποδοτική λειτουργία των μηχανημάτων για εξοικονόμηση ενέργειας και κόστους. Σε κάθε περίπτωση βλέπουμε ότι είναι αναγκαία η εφαρμογή μίας πολιτικής, που θα μοιράζει τους πόρους στις εργασίες με τέτοιο τρόπο, ώστε συγκεκριμένοι στόχοι να εξυπηρετούνται.

Η χρονοδρομολόγηση συναντάται, επίσης, στα υπολογιστικά συστήματα. Αποτελεί αναπόσπαστο κομμάτι του λειτουργικού συστήματος και η κύρια αρμοδιότητα της είναι να παρέχει ένα περιβάλλον, στο οποίο πολλά προγράμματα μπορούν να τρέχουν παράλληλα. Μια διεργασία δεν μπορεί να κρατάει τον επεξεργαστή απασχολημένο όλη την ώρα. Το λειτουργικό σύστημα οφείλει να προσφέρει τμήμα του χρόνου του επεξεργαστή σε όλες τις διεργασίες και να διαβεβαιώνει ότι αυτές κάνουν πρόοδο. Ο δρομολογητής αποτελεί απαραίτητο κομμάτι του λειτουργικού, διότι εκτός από το να προσφέρει ένα πολυπρογραμματιστικό περιβάλλον, παίζει βαρίνουσας σημασίας ρόλο στη συνολική απόδοση του συστήματος, καθώς οι στόχοι που προσπαθεί να ικανοποιήσει σχετίζονται με την απόδοσή του. Μερικοί απο τους στόχους είναι οι εξής: να κρατάμε τον επεξεργαστή όσο περισσότερο απασχολημένο γίνεται, να εκτελούμε όσο το δυνατόν περισσότερες διεργασίες ανα μονάδα χρόνου ή να ελαχιστοποιύμε το χρόνο των διεργασιών που μένουν εκτός επεξεργαστή. Ανεξαρτήτως στόχου, ο δρομολογητής εφαρμόζει δύο πολιτικές. Στην μία μοιράζει τον επεξεργαστή χρονικά και στην άλλη τοπικά, δηλαδή πως σε μία χρονική στιγμή θα μοιραστούν οι πυρήνες στις διεργασίες. Όταν πρόκειται για μονοπύρηνες αρχιτεκτονικές η μόνη πολιτική που μπορεί να εφαρμοστεί είναι η κατανομή του χρόνου, ενώ σε πολυπύρηνες αρχιτεκτονικές μπορούν να εφαρμοστούν και οι δύο.

#### 1.2 Πολυπύρηνα Συστήματα (CMPs)

Οι κατασκευαστές για χρόνια επιδίωκαν την αύξηση της απόδοσης του επεξεργαστή, αυξάνωντας τον αριθμό των τρανζίστορ και συρρικνώνοντας τα ώστε να μειώσουν το συνολικό μέγεθος του τσιπ. Αυτή η τάση, όμως, δεν μπορεί να συνεχιστεί για πάντα, καθώς οι δυνατότητες συρρίκνωσης των τρανζίστορ περιορίζονται και προβήματα κατανάλωσης και θερμότητας συνεχώς αυξάνονται. Έτσι η βελτίωση της απόδοσης του επεξεργαστή άρχισε να μειώνεται. Στη δεκαετία του 90 η απόδοση αυξανόταν κατά 60 % κάθε χρόνο, ενώ απο το 2000 έως το 2004 η αύξηση έπεσε στο 40% κάθε χρόνο. Η κατασκευή ενός ελάχιστα, κατά 20% γρηγορότερου τσιπ με διπλάσιο μέγεθος δεν ανταποκρίνεται στις προσδοκίες μας για βελτιωμένη απόδοση, αποδοτική κατανάλωση και μειωμένο κόστος.

Για αυτούς τους λόγους, στραφήκαμε στην κατασκευή πολυπύρηνων συστημάτων. Σε αντίθεση με τις μονοπύρηνες αρχιτεκτονικές, ενσωματώνουμε στο ίδιο τσιπ πολλούς πυρήνες, οι οποίοι λειτουργούν σε ελαφρώς χαμηλότερες ταχύτητες και μοιράζονται στοιχεία αρχιτεκτονικής (CMPs). Ο διαμοιρασμός του φόρτου σε πολλές μονάδες επεξεργασίας, οι οποίες μπορούν να εκτελούν προγράμματα παράλληλα αποφέρει σημαντική αύξηση στην συνολική απόδοση. Από την άλλη, το κόστος για την κατασκευή και τη λειτουργία τους (κατανάλωση) είναι χαμηλότερο συγκριτικά με τα συμμετρικά πολυπύρηνα συστήματα, καθώς οι επεξεργαστές μοιράζονται στοιχεία και η επικοινωνία τους γίνεται γρηγορότερα.

Λόγω των πλεονεκτημάτων που προσφέρουν, αυτές οι αρχιτεκτονικές έχουν κυρίαρχη θέση στα υπολογιστικά συστήματα. Χρησιμοποιούνται ευρέως σε πολλούς τομείς, απο ενσωματωμένα σε συστήματα επεξεργασίας ψηφιακών σημάτων. Όσον αφορά την βιομηχανία, η ΑΜD, η Fujitsu, η IBM, η Intel και η Sun Microsystems κατασκευάζουν ήδη πολυπύρηνα συστήματα και σκοπεύουν να σχεδιάσουν νέα μοντέλα στο μέλλον.

#### 1.3 Ο χρονοδρομολογητής του λειτουργικού συστήματος Linux

Όπως αναφέραμε νωρίτερα, ο ρόλος των δρομολογητών στα CMPs είναι να μοιράζει τους επεξεργαστές όχι μόνο χρονικά αλλά και τοπικά. Δηλαδή να αποφασίζουν σε κάθε χρονική στιγμή ποιες διεργασίες θα ανατεθούν στους πυρήνες. Ο κύριος σκοπός τους είναι να μοιράζουν το φόρτο εργασίας ίσα μεταξύ των πυρήνων. Ας εξετάσουμε έναν δρομολογητή που χρησιμοποιείται στο λειτουργικό σύστημα του Linux, ώστε να καταλάβουμε καλύτερα πως το σύνολο των διεργασιών διαχειρίζεται στα CMPs.

Η χρονοδρομολόγηση γίνεται σε δύο επίπεδα. Στο πρώτο επίπεδο χρησιμοποιούνται ξεχωριστές ουρές διεργασιών για κάθε πυρήνα και πολιτικές για την διαχείριση τους. Στο δεύτερο επίπεδο υπάρχει ο load balancer που μοιράζει τις διεργασίες στους πυρήνες. Με αυτόν τον τρόπο επιτυγχάνουμε κατανομή στο χρόνο (πρώτο επίπεδο) και στο χώρο (δεύτερο επίπεδο).

Η ουρά διεργασιών σε κάθε πυρήνα αντιπροσωπεύει το σύνολο των προγραμμάτων που έχει αναλάβει να εκτελέσει αυτός ο πυρήνας. Η πολιτική που χρησιμοποιείται για την διαχείρηση κάθε ουράς βασίζεται στην εξής αρχή. Η διεργασία που έχει την μεγαλύτερη ανάγκη για υπολογιστικό χρόνο θα είναι η επόμενη που θα δρομολογηθεί. Σκοπός αυτής της πολιτκής είναι να προσφέρει δίκαιη κατανομή του χρόνου μεταξύ των διεργασιών και για αυτό το λόγο ονομάζεται CFS (Completely Fair Scheduler). Για να το πετύχει αυτό, λαμβάνει

υπ'όψιν του το χρόνο που οι διεργασίες βρίσκονται εκτός πυρήνα και επιλέγει κάθε φορά αυτήν με τον μεγαλύτερο. Με αυτόν τον τρόπο διαβεβαιώνει ότι καμία διεργασία δεν θα μένει εκτός πυρήνα για περισσότερο χρόνο, μοιράζοντας τους πόρους δίκαια μεταξύ των. Η ουρά διεργασιών υλοποιείται με ένα time-ordered red black tree για κάθε πυρήνα

Στις CMP αρχιτεκτονικές κάθε πυρήνας έχει τη δικιά του ουρά διεργασιών. Εφ'όσον οι χρόνοι εκτέλεσης των διεργασιών διαφέρουν, είναι πιθανό μερικοί επεξεργαστές να διαχειρίζονται λιγότερο αριθμό διεργασιών. Αυτήν την άνιση κατανομή φόρτου προσπαθεί να μετριάσει ο load balancer, ο οποίος εφαρμόζεται περιοδικά και σκοπός του είναι να ισορροπεί το μήκος των ουρών σε όλους τους πυρήνες. Αυτό το επιτυγχάνει μετακινόντας διεργασίες απο το πιο απασχολημένο πυρήνα σε εκείνο με το λιγότερο φόρτο. Η εξισορρόπηση του φόρτου γίνεται ιεραρχικά, ξεκινώντας απο επίπεδο που αφορά διαφορετικά NUMA domains καταλήγοντας στο επίπεδο των SMT contexts. Η συχνόντητα και ο αριθμός των μετακινήσεων διαφέρει απο επίπεδο σε επίπεδο.

#### 1.4 Περιγραφή Κεφαλαίων

Στο δέυτερο κεφάλαιο παρουσιάζουμε την επίδραση των εφαρμογών στην απόδοση τους, όταν εκείνες ανταγωνίζονται για τους μοιραζόμενους πόρους. Επιπλέον μελετάμε πως η αντιμετώπιση των πόρων απο σύγχρονο χρονοδρομολογητή, επηρεάζει την απόδοση του συστήματος.

Στο τρίτο κεφάλαιο προτείνουμε 3 τεχνικές χρονοδρομολόγησης, με σκοπό να βελτιώσουμε τη σταθερότητα του συστήματος και να προσφέρουμε δικαιη κατανομή των πόρων

Στο τέταρτο κεφάλαιο, ελέγχουμε τις τεχνικές μας σε μία ποικιλία φόρτων εργασίας και συγκρίνουμε τα αποτελέσματα μας με το Linux scheduler.

Στο πέμπτο κεφάλαιο, παρουσιάζουμε τα συμπεράσματα μας και πιθανές ιδέες για βελτίωση, ενώ στο τελευταίο κεφάλαιο αναφέρουμε διάφορες προσεγγίσεις που έχουν γίνει από την επιστημονική κοινότητα.

## Κεφάλαιο 2 Ορισμός του Προβλήματος και Κίνητρο

#### 2.1 Δημιουργική και καταστροφική συμπεριφορά

Όπως αναφέραμε προηγουμένως, οι πυρήνες των CMP είναι ενσωματομένοι σε ένα τσιπ και μοιράζονται στοιχεία της αρχιτεκτονικής, όπως την κρυφή μνήμη τελευταίου επιπέδου και το δίαυλο μνήμης. Όταν εκτελούνται εφαρμογές παράλληλα στους πυρήνες οι μοιραζόμενοι πόροι μπορεί να έχουν είτε θετικό είτε αρνητικό ανίκτυπο στην απόδοσή τους.

Στην περίπτωση που συνεισφέρουν δημιουργικά, οι εφαρμογές μπορούν να γνωρίσουν τρομερή βελτίωση στην απόδοση τους. Αυτό μπορεί να επιτευχθεί όταν νήματα μιας εφαρμογής κάνουν αναφορά στα ίδια ή σε τοπικά δεδομένα ταυτόχρονα (fine-grained sharing). Με αυτό το τρόπο μερικά νήματα φέρνουν δεδομένα στην κρυφή μνήμη και εξυπηρετούν και τα γειτονικά νήματα που χρησιμοποιούν τα ίδια, χωρίς να χρειάζεται να κάνουν εκ νέου

αναφορά στην μνήμη.

Από την άλλη μεριά, οι μοιραζόμενοι πόροι μπορεί να έχουν καταστροφικές συνέπειες για τις εφαρμογές. Αυτό συμβαίνει όταν τρέχουν παράλληλα νήματα διαφορετικών διεργασιών, που δεν έχουν καμία επικοινωνία μεταξύ τους. Επίσης νήματα των ίδιων διεργασιών είναι δυνατό να έχουν ένα μοτίβο αναφοράς στα δεδομένα που να μην εξυπηρετούν τα γειτονικά τους. Για παράδειγμα μπορεί ένα νήμα να αναφέρεται σε ένα τμήμα δεδομένων για κάποιο χρονικό διάστημα και το γειτονικό του να αναφερθεί σε αυτό αφού τελειώσει την αναφορά το αρχικό(coarse-grained sharing). Συνεπώς δεν μπορεί το ένα να βοηθήσει το άλλο και συμπεριφέρονται σαν νήματα ξεχωριστών διεργασιών. Σε όλες τις περιπτώσεις τα νήματα προσπαθούν να ικανοποιήσουν τις απαιτήσεις τους, χρησιμοποιώντας τους μοιραζόμενους πόρους για δικό τους λογαριασμό αποκλειστικά και ανταγωνίζονται μεταξύ τους για την ικανοποίηση των αναγκών τους. Αυτή η διαμάχη για τη χρήση των μοιραζόμενων πόρων έχει σημαντικές αρνητικές συνέπειες στην απόδοσή των εφαρμογών, καθώς παρατηρείται καθυστέρηση στην εκτέλεση τους συγκριτικά με τον όταν τρέχουν μόνες τους.

Μελετάμε παρακάτω την σύγκρουση σε δύο μοιραζόμενους πόρους, τη LLC και το Memory Bandwidth

#### 2.2 Ανταγωνισμός για τη κρυφή μνήμη

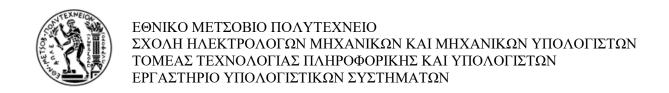

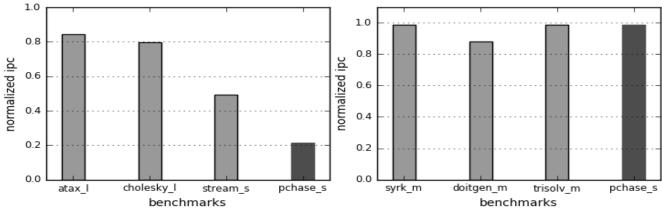

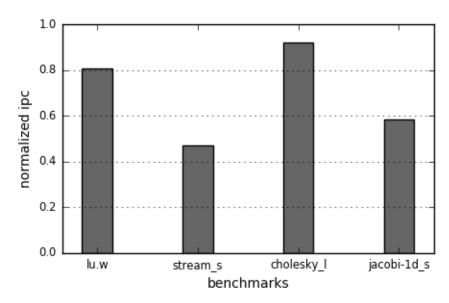

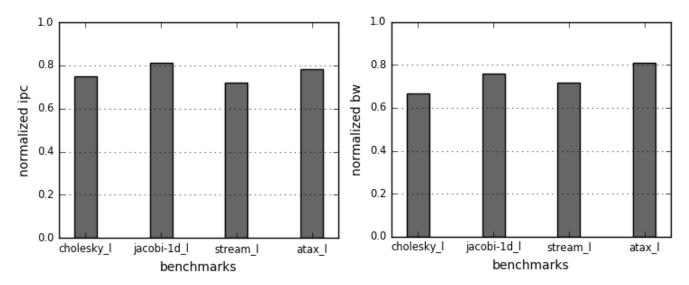

Όταν οι διεργασίες τρέχουν παράλληλα ο πρώτος πόρος, για τον οποίο έρχονται σε σύγκρουση είναι η κρυφή μνήμη. Διεργασίες φέρνουν δεδομένα στη κρυφή μνήμη με σκοπό να ικανοποιήσουν τις απαιτήσεις τους. Στην περίπτωση που τρέχει μία διεργγασία η κρυφή μνήμη περιέχει τα δεδομένα της. Όταν όμως τρέξει παράλληλα μία άλλη στον γειτονικό πυρήνα, φέρνει τα δικά της δεδομένα, διώχνοντας απο τη κρυφή μνήμη τα δεδομένα της άλλης. Αυτό έχει σαν αποτέλεσμα την αύξηση των αποτυχιών και συνεπώς μεγαλύτερες καθυστερήσεις στην εκτέλεση της διεργασίας. Τρέχοντας σε ένα τετραπύρηνο σύστημα με κοινή LLC (θα αναλύσουμε λεπτομερώς παρακάτω) 4 εφαρμογές παρατηρούμε τις καταστροφικές συνέπειες που έχει αυτή η διαμάχη στην απόδοση τους. (Figure 1.1-1)

Figure 1.1-1: Επίπτωση της αύξησης των MPI στο IPC 4 διεργασιών που τρέχουν παράλληλα

Παρατηρούμε, λοιπόν, ότι ο ανταγωνισμός για την κρυφή μνήμη προκαλεί αύξηση στα

ΜΡΙ των εφαρμογών. Βλέπουμε, επίσης, ότι η εφαρμογές δεν επηρεάζονται το ίδιο, μερικές επωφελούνται περισσότερο από τη κρυφή μνήμη ενώ άλλες όχι.

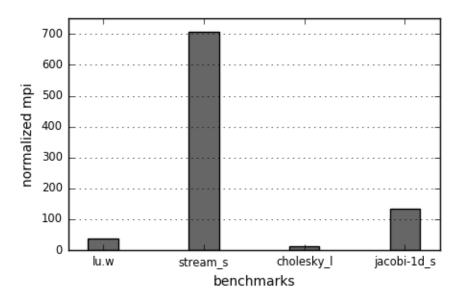

#### 2.2 Ανταγωνισμός για το Memory Bandwidth

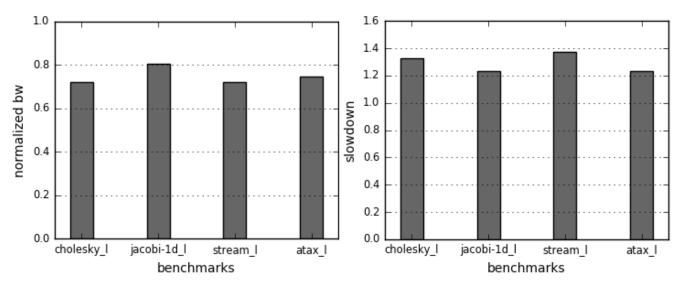

Ένα άλλο σημείο σύγκρουσης είναι ο δίαυλος της μνήμης. Ο ρυθμός, με τον οποίο τα δεδομένα διαβάζονται ή γράφονται από και προς τη μνήμη, ονομάζεται Memory Bandwidth. Όταν τρέχουν παράλληλα διεργασίες, μολύνουν το δίαυλο μνήμης με δεδομένα. Το σύστημα της μνήμης, όπως είναι φυσικό, έχει ένα όριο στο ρυθμό εξυπηρέτησης των δεδομένων. Αυτό σημαίνει ότι υπάρχει ένα σημείο στο οποίο το Bandwidth δεν μπορεί να ικανοποιήσει όλες τις διεργασίες. Σε αυτή τη περίπτωση το Bandwidth μοιράζεται μεταξύ των διεργασιών και κάθε μία παίρνει ένα τμήμα του αρχικού εύρους που θα έπαιρνε, όταν έτρεχε μόνη της. Χρησιμοποιώντας streaming εφαρμογές, δηλαδή εφαρμογές που χρησιμοποιούν δεδομένα από την μνήμη έως τον επεξεργαστή χωρίς να επωφελούνται απο τις κρυφές μνήμες, παρατηρούμε πώς η διαμάχη για το Memory Bandwidth επηρεάζει την απόδοσή τους.

Figure 1.1-2: Η μείωση του Bandwidth έχει άμεσο αντίκτυπο στο IPC 4 streaming εφαρμογών

Παρατηρούμε ότι η σύγκρουση στο δίαυλο της μνήμης προκαλεί μείωση του Bandwidth και μία ανάλογη μείωση στο IPC. Από αυτό καταλαβαίνουμε ότι το Bandwidth είναι ένας σημαντικός παράγοντας που επηρεάζει την απόδοση των διεργασιών.

#### 2.3 Κίνητρο

Με την άφιξη των CMPs οι περισσότερες τεχνικές υλικού και λογισμικού που είχαν υλοποιηθεί στις μονοπύρηνες αρχιτεκτονικές ή στα SMPs εφαρμόσθηκαν χωρίς μετατροπές. Οι χρονοδρομολογητές θεωρούν ότι οι πυρήνες είναι ανεξάρτητοι και απομονωμένοι. Αυτό, όμως, δεν ισχύει, καθώς μοιράζονται στοιχεία για τα οποία υπάρχει διαμάχη μεταξύ των εφαρμογών που τρέχουν μαζί. Η αντιμέτωπιση αυτή όμως δημιουργεί πολλά προβλήματα στους στόχους που ένας χρονοδρομολογητής προσπαθεί να ικανοποιήσει.

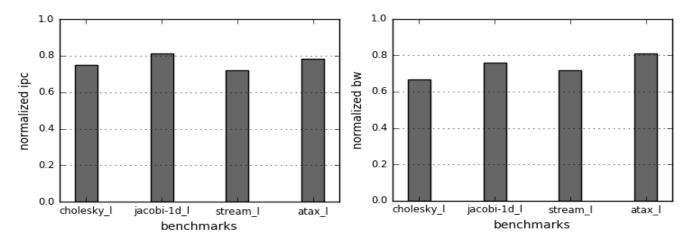

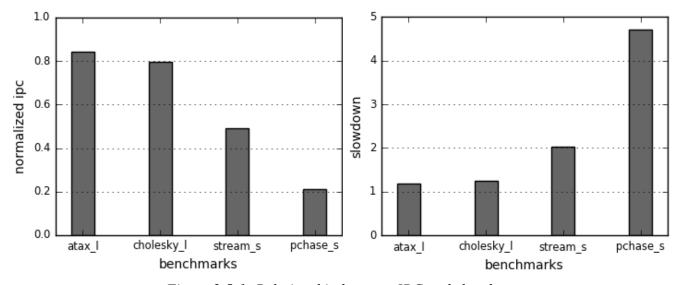

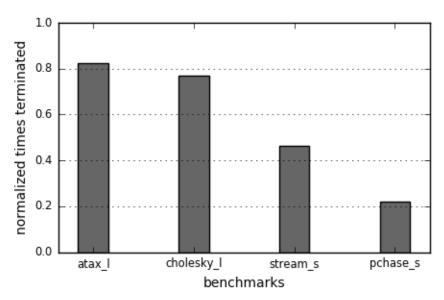

Τρέχοντας 4 εφαργμογές στο σύστημα που αναφέραμε προηγουμένως για 5 λεπτά με τον Linux scheduler (Figure 1.1-3) παρατηρούμε πως ο ρόλος του χρονοδρομολογητή

υποβαθμίζεται.

Figure 1.1-3: Φορές τερματισμού 4 διεργασιών κανονικοποιημένες στην περίπτωση που εκτελούνται μόνες τους

Αρχικά είναι προφανές ότι ο πρωταρχικός σκοπός του να προσφέρει ένα περιβάλλον, στο οποίο όλες οι διεργασίες κάνουν πρόοδο δεν μπορεί να επιτευχθεί, καθώς υπάρχουν εφαρμογές σαν την pchase\_s οι οποίες εκτελούνται με πολύ χαμηλή απόδοση.

Το γεγονός αυτό σε ευρύτερη κλίμακα έχει μεγάλη επίπτωση στον αριθμό των διεργασιών που το σύστημα μπορεί να εκτελέσει ανά μονάδα χρόνου (throughput). Σε χρονικό διάστημα 5 λεπτών οι διεργασίες stream\_s και pchase\_s έχουν εκτελεστεί 50% και 80% λιγότερες φορές.

Επίσης είναι αδύνατο να εφαρμοσθεί μία πολιτική με προτεραίοτητες. Δίνοντας σε μία διεργασία υψηλότερη προτεραιότητα σημαίνει ότι επιθυμούμε αυτή να κάνει μεγαλύτερη πρόοδο. Αυτό στο παράδειγμά μας δεν μπορεί να επιτευχθεί βλέποντας την πολύ χαμηλή απόδοση της pchase\_s.

Ένας απο τους κυριότερους ρόλους του χρονοδρομολογητή είναι να κατανέμει δίκαια τους πόρους μεταξύ των διεργασιών. Αυτό πλέον δεν μπορεί να γίνει εφικτό, καθώς βλέπουμε ότι μερικές διεργασίες έχουν υψηλή και άλλες πολύ χαμηλή απόδοση. Είναι εμφανές ότι οι επιπτώσεις της σύγκρουσης δεν μπορούν να μοιραστούν ομοιόμορφα στις εφαρμογές και συνεπώς δικαιοσύνη δεν μπορεί να επέλθει.

Figure 1.1-4: Μεταβλητή απόδοση της εφαρμογής pchase\_s

Τέλος παρατηρώντας το σχήμα 1.1-4 καταλήγουμε στο εξής συμπέρασμα. Η απόδοση μιας εφαρμογής εξαρτάται απο τις εφαρμογές που θα τρέξουν στους γειτουνικούς πυρήνες. Στη μία τετράδα η απόδοσή της είναι πολύ χαμηλή ενώ στην άλλη πολύ υψηλή. Αυτό σημαίνει ότι η απόδοση του συστήματος είναι ασταθής και απρόβλεπτη και ο χρονοδρομολογητής δεν μπορεί να εγγυηθεί αξιοπιστία στην εκτέλεση των διεργασιών.

# Κεφάλαιο 3

## Προτεινόμενες τεχνικές χρονοδρομολόγησης

Σε αυτό το κεφάλαιο παρουσιάζουμε τρεις τεχνικές χρονοδρομολόγησης, βάσει των οποίων επιδιώκουμε να ξεπεράσουμε τα προβλήματα σταθερότητας και αξιοπιστίας που δημιουργούν οι χρονοδρομολογητές που δεν λαμβάνουν υπ'όψιν τους την σύγκρουση στους μοιραζόμενου πόρους.

Στην πρώτη προσέγγισή μας, σχεδιάζουμε έναν χρονοδρομολογητή, ο οποίος προσπαθεί να αποφύγει τη σύγκρουση των διεργασιών. Το επιτυγχάνει χωρίζοντας τις διεργασίες σε κατηγορίες και εξετάζοντας πως αυτές οι κατηγορίες αλληλεπιδρούν μεταξύ τους όταν τρέχουν παράλληλα. Εφ'όσον υπάρχει μία πρόβλεψη για το πως αυτές οι κατηγορίες συγκρούονται, είναι έτοιμος να πάρει αποφάσεις για το πως θα τις διαχωρίσει με σκοπό να πετύχει δίκαιη κατανομή των πόρων.

Στην δεύτερη προσέγγιση, διαχειριζόμαστε εκ των υστέρων τα αποτελέσματα της σύγκρουσης των διεργασιών. Ευνοούμε τις διεργασίες που έχουν πληγεί περισσότερο, δίνοντας τους την ευκαιρία να τρέξουν για περισσότερο χρόνο και να αυξήσουν την πρόοδο τους σε βάρος αυτών που τρέχουν με καλύτερη απόδοση. Με αυτό τον τρόπο θέλουμε να εξισορροπήσουμε την απόδοση τους.

Η τρίτη προσέγγιση είναι επέκταση της δεύτερης. Ξέροντας ότι μερικά ζευγάρια όταν τρέξουν μαζί, προκαλούν καταστροφικές συνέπειες. Για αυτό το λόγο αποφεύγουμε την εκτέλεσή τους και εξακολουθούμε να εφαρμόζουμε την πολιτική της δεύτερης τεχνικής, αποφεύγοντας έτσι ένα μέρος της σύγκρουσης και διαχειρίζοντας το υπόλοιπο. Με αυτήν την τεχνική θέλουμε να πετύχουμε μεγαλύτερη βελτίωση στη πρόοδο των διεργασιών και συνεπώς στο throughput.

#### 3.1 Πρώτη Προσέγγιση (Αποφεύγοντας τη σύγκρουση)

Κύριο χαρακτηριστικό αυτής της τεχνικής είναι η εύρεση του κατάλληλου συνδιασμού διεργασιών η οποία οδηγεί στην επιθυμητή απόδοση. Όπως παρατηρήσαμε προηγουμένως, οι διεργασίες δεν αποδίδουν το ίδιο όταν εκτελούνται παράλληλα με άλλες στους γειτονικούς πυρήνες. Μερικοί συνδιασμοί συγκρούονται σε πολύ χαμηλό βαθμό και αποδίδουν αρκετά καλά, ενώ άλλοι σε έντονο και επηρεάζονται καταστροφικά. Όμως δεν είναι εφικτό να δοκιμάσουμε δυναμικά όλους τους συνδιασμούς ώστε να καταλήξουμε στον πιο αποδοτικό. Για αυτό το λόγο η χρονοδρομολόγησή μας γίνεται σε τρία επίπεδα. Στο πρώτο ταζινομούμε τις εφαρμογές σε κατηγορίες. Στο δεύτερο βρίσκουμε ένα μοντέλο που προβλέπει πως αλληλεπιδρούν οι κατηγορίες αυτές μεταξύ τους. Τέλος παίρνουμε την απόφαση να

τοποθετήσουμε τις εφαρμογές στους πυρήνες με τέτοιο τρόπο ώστε να αποφύγουμε τη σύγκρουσή τους και να πετύχουμε τα επιθυμητά αποτελέσματα. Πριν αναλύσουμε τα στάδια, θα αναφέρουμε την πλατφόρμα στην οποία θα εκτελέσουμε τα πειράματά μας και τις δυνατότητες που μας προσφέρει.

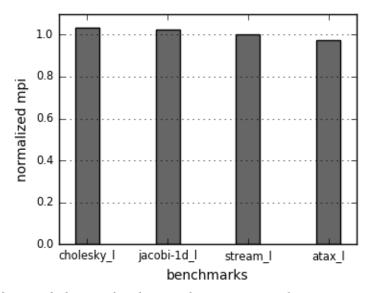

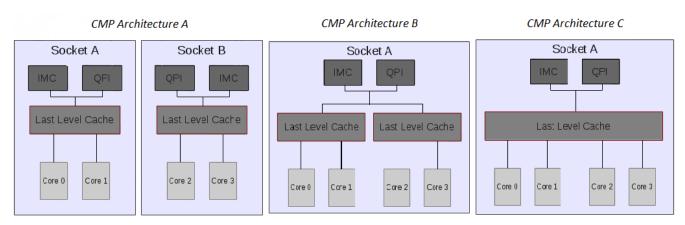

#### 3.1.1 Πλατφόρμα Εκτέλεσης

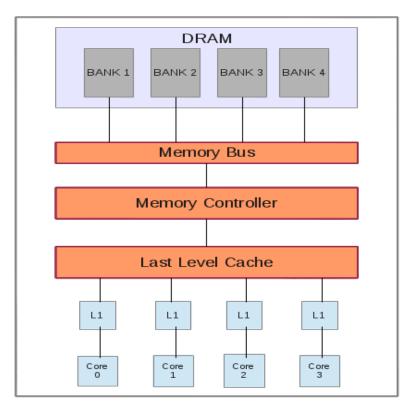

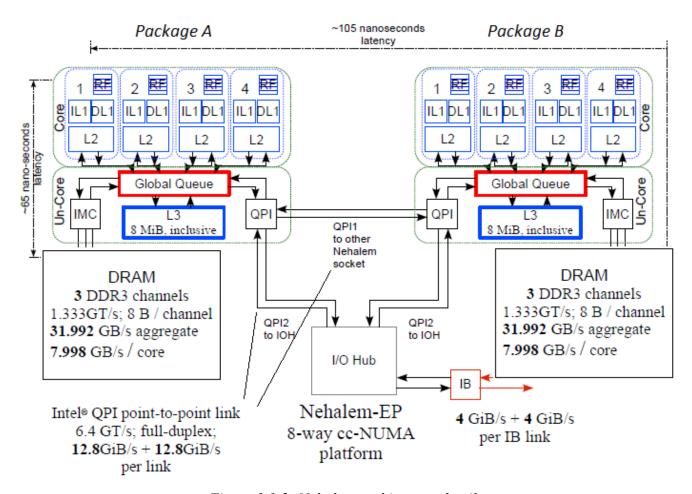

Στην εργασία αυτή, για την αξιολόγηση των χρονοδρομολογητών μας, χρησιμοποιήσαμε τον επεξεργαστή Intel® Xeon® Processor X5560 Nehalem αρχιτεκτονικής. Αποτελείται απο δύο τσιπ (sockets) τα οποία αναφέρονται σε ξεχωριστό μέρος μνήμης (NUMA) και αποτελούνται απο τα εξής.

Τεσσερις πυρήνες 2,8 GHz συχνότητας, L1 ιδιωτική κρυφή μνήμη, που χωρίζεται σε 32 KB δεδομένων και 32 KB εντολών, L2 ιδιωτική κρυφή μνήμη 256 KB και L3 κοινή κρυφή μνήμη 8 MB. Κάθε τσιπ επικοινωνεί με την μνήμη μέσω τριών 8-byte καναλιών που λειτουργούν στο 1,333 GT/s. Δηλαδή το μέγιστο θεωρητικό Bandwidth μπορεί να φτάσει την τιμή 31,992 GB/s. Η επικοινωνία μεταξύ των 2 τσιπ επιτυγχάνεται μέσω του QPI συνδέσμου που φτάνει Bandwidth 12,8 GB/s. Επίσης κάθε τσιπ υποστηρίζει Hardware Prefetching Logic, για να φέρνει δεδομένα που τα νήματα θα χρησιμοποιήσουν στο κοντινό μέλλον, Simultaneous Multi-Threading" (SMT), επιτρέποντας παραπάνω νήματα να εκτελούνται στον ίδιο πυρήνα και Turbo Boost Technology για εξοικονόμηση ενέργειας.

Για τα πειράματα μας χρησιμοποιήσαμε μόνο το ένα τσιπ με ενεργοποιημένη τη λειτουργία του hardware prefetching logic και απενεργοποιημένες τις SMT και TBT.

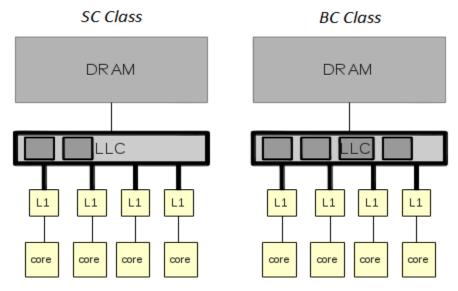

Η αρχιτεκτονική διαδραματίζει πολύ σημαντικό ρόλο στην τοποθέτηση των διεργασιών στους πυρήνες και καθορίζει τις διαφορετικές ομάδες που μπορούν να δημιουργηθούν συνδιάζοντας τις διεργασίες. Παίρνοντας για παράδειγμα 4 εφαρμογές Α, Β, Γ, Δ, στην δική μας αρχιτεκτονική παράγεται ένας μοναδικός συνδιασμός εκτέλεσης τους στους πυρήνες. Αν είχαμε μια αρχιτεκτονική που οι πυρήνες ανα 2 μοιραζόντουσαν μια LLC, τότε τα πράγματα θα ήταν διαφορετικά. Σε αυτή την περίπτωση οι πιθανές τετράδες εκτέλεσης αυξάνονται στις 3. Παρατηρούμε λοιπόν ότι η δυνατότητα αποφυγής της σύγκρουσης αυξάνεται καθώς μειώνεται ο αριθμός των πυρήνων που μοιράζονται τη LLC. Αυτό συμβαίνει, επειδή μας δίνεται επιπλέον η δυνατότητα να μοιράσουμε τις διεργασίες στο χώρο (space-sharing). Στη δική μας περίπτωση, ο μόνος τρόπος να μοιράσουμε τις εφαρμογές είναι χρονικά (time-sharing) και αυτό περιορίζει τις επιλογές μας για αποφυγή της σύγκρουσης.

#### 3.1.2 Μέθοδος Ταξινόμησης

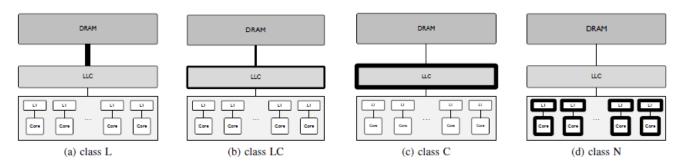

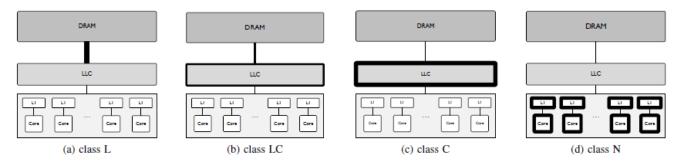

Ξεκινάμε με το πρώτο στάδιο της ταξινόμησης. Βασισμένοι στο σχήμα που προτάθηκε απο τη δουλειά του Haritatos et al [1] κατηγοριοποιούμε τις εφαρμογές σε τέσσερις κλάσεις, την L, LC, C και N.

Στην L κατηγορία ανήκουν εκείνες, οι οποίες παρουσιάζουν μία σημαντική και σταθερή ροή δεδομένων από την μνήμη έως το πυρήνα. Αυτές οι εφαρμογές δεν επωφελούνται απο τη LLC και μολύνουν με μεγάλο αριθμό δεδομένων το δίαυλο μνήμης κάνοντας χρήση μεγάλου ποσοστού του Memory Bandwidth.

Στην LC κατηγορία ταξινομούνται εφαρμογές, οι οποίες χρησιμοποιούν σε μέτριο βαθμό το δίαυλο της μνήμης και επωφελούνται ελαφρά απο τη LLC, επαναχρησιμοποιώντας την σε μικρό βαθμό.

Στην C κλάση κατατάσσονται οι εφαρμογές με τα εξής χαρακτηριστικά. Χρησιμοποιούν σε πολύ μικρό βαθμό το δίαυλο μνήμης, καταναλώνοντας μικρό ποσοστό του Bandwidth, αλλά παρουσιάζουν μεγάλη εξάρτηση απο τη LLC. Αυτό σημαίνει ότι φέρνουν δεδομένα σε αυτή και πραγματοποιούν αναφορές σε αυτά για αρκετό χρονικό διάστημα πριν φέρουν τα επόμενα. Με αυτό τον τρόπο περιορίζονται μόνο σε αυτό το μοιραζόμενο πόρο, πραγματοποιώντας πολύ μεγάλη επαναχρησιμοποίηση.

Τέλος η Ν κατηγορία αποτελείται απο εφαρμογές οι οποίες δεν δείχνουν σημαντική δραστηριότητα στους μοιραζόμενους πόρους, αλλά περιορίζονται στις ιδιωτικές κρυφές μνήμες και στον επεξεργαστή. Οι κατηγορίες παρουσιάζονται στο σχήμα 1.1-5.

Figure 1.1-5: Δραστηριότητα στις 4 κατηγορίες

Για να ταξινομήσουμε τις εφαρμογές στις παραπάνω κατηγορίες, είναι απαραίτητο να καταγράψουμε τη συμπεριφορά τους. Αυτό το επιτυγχάνουμε χρησιμοποιώντας κάποιες απλές μετρικές, τις οποίες μπορούμε να αποκτήσουμε κατά το χρόνο εκτέλεσης απο τους hardware performance counters που παρέγουν οι σύγχρονοι επεξεργαστές.

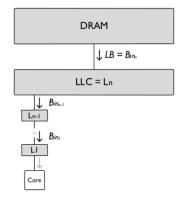

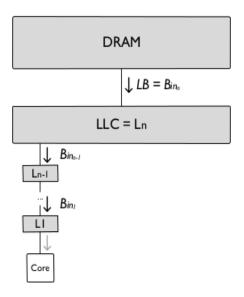

Figure 1.1-6: Ροή δεδομένων

Για κάθε εφαρμογή είναι απαραίτητο να μετρήσουμε τη ροή των δεδομένων απο τή κύρια μνήμη έως τον επεξεργαστή, χρησιμοποιώντας το Bandwidth σαν μετρική και να βρούμε σε ποιό μέρος της ιεραρχίας της μνήμης υπάρχει μεγάλη δραστηριότητα, χρησιμοποιώντας το

$$CR_i = \frac{Bin_{i-1}}{Bin_i}$$

(σχήμα 1.1-6).

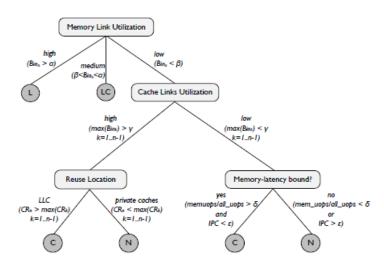

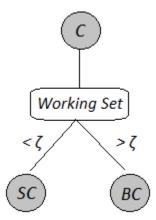

Αν το LB (Memory Bandwidth) είναι μεγάλο και το  $CR_n=1$  τότε η εφαρμογή είναι L. Αν η δραστηριότητα μεταξύ μνήμης και LLC είναι μέτρια και  $CR_n>1$ , τότε είναι LC. Διαφορετικά εφαρμογές με πολύ χαμηλο LB δραστηριοποιούνται στο υπόλοιπο τμήμα της ιεραρχίας.

Αν υπάρχει μεγάλη επαναχρησιμοποίηση της LLC αναφερόμαστε σε C αλλιώς σε N.

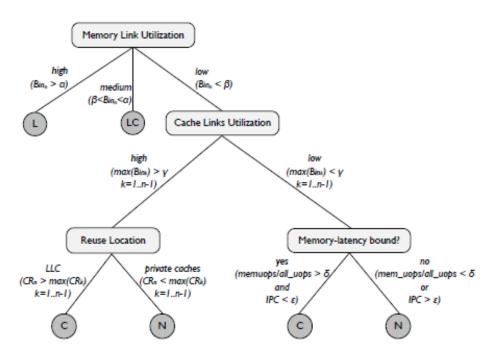

Η μέθοδος ταξινόμησης μας παρουσιάζεται στο δέντρο του σχήματος 1.1-7. Σε κάθε πλατφόρμα πρέπει να θέσουμε 5 όρια, α, β, γ, δ και ε. Σε αυτή τη πλατφόρμα έχουμε  $\alpha=0.12\times B_{max},\ \beta=0.045\times B_{max},\ \gamma=0.068\times B_{max},\ \delta=0.25,\ \varepsilon=0.25\times IPC_{max}.$  Η μέγιστη τιμή του Memory Bandwidth όπως μετρήθηκε απο τη stream εφαρμογή [2] είναι  $B_{max}=13.20\ GB/sec$  και  $IPC_{max}=4$

Figure 1.1-7: Δέντρο ταξινόμησης

#### Διαχωρισμός της C κατηγορίας

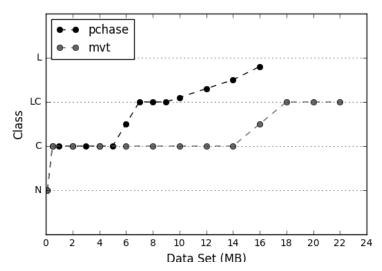

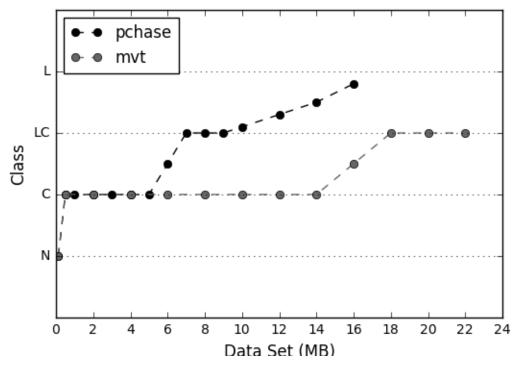

Οι εφαρμογές μπορεί να παρουσιάσουν διαφορετικά χαρακτηριστικά ανάλογα το μέγεθος του data set τους. Εξετάζοντας δύο εφαρμογές με διάφορα μεγέθη για το data set τους παρατηρούμε τα εξής .

Αρχικά βλέπουμε ότι όταν το σύνολο των δεδομένων είναι αρκετά μικρό ώστε να ικανοποιείται απο τα χαμηλότερα τμήματα της μνήμης (ιδιωτικές κρυφές μνήμες) η δραστηριότητα περιορίζεται σε αυτό το κομμάτι και οι εφαρμογές παρουσιάζουν συμπεριφορά Ν κλάσης.

Αυξάνουμε το data set και παρατηρούμε ότι αυτό μπορεί να ικανοποιηθεί πλέον απο τη LLC, οπότε και οι εφαρμογές γίνονται C.

Αξίζει να σημειώσουμε, ότι η μετάβαση απο τη C στη LC κατηγορία πραγματοποιείται σε διαφορετικό data set για κάθε εφαρμογή. Στην pchase γίνεται στο σημείο στο οποίο αρχίζουν να μην χωράνε τα δεδομένα στη LLC, ενώ στην mvt πολύ αργότερα. Αυτό σημαίνει

ότι η πρώτη εφαρμογή όταν βρίσκεται στα όρια της LLC ευνοείται από όλο το χώρο που αυτή προσφέρει και όταν το data set ξεπερνάει το μέγεθος της αρχίζει να κάνει συχνή αναφορά στην κύρια μνήμη, δείχνοντας μηδενική ανοχή. Από την άλλη, η δεύτερη εφαρμογή δείχνει να μην επηρεάζεται απο τον περιορισμό και να εξακολουθεί να εξυπηρετείται απο τη LLC ακόμα και για 14 MB data set.

Figure 1.1-8: Συμπεριφορά δύο εφαρμογών για διάφορα data sets

Βασισμένοι στην προηγούμενη παρατήρησή μας, μπορούμε να συμπεράνουμε τα εξής. Εάν στη πλατφόρμα μας (8 MB LLC, 4 πυρήνες) τρέξουμε παράλληλα δύο εφαρμογές με 6 MB data set, που παρουσιάζουν ίδια συμπεριφορά με τη pchase, η LLC δεν μπορεί να εξυπηρετήσει και τις δύο. Θα μοιράσει το χώρο της και αναγκαστικά θα πάρουν ένα υποσύνολο του data set τους. Ο περιορισμός αυτός θα τους οδηγήσει σε αύξηση των misses, συχνότερη αναφορά στη μνήμη (αυξημένο Bandwidth) και μείωση στην απόδοση τους. Αν οι εφαρμογές είχαν την συμπεριφορά της mvt θα ήταν ανεκτικές στον περιορισμό και δεν θα παρουσίαζαν προβλήματα στην απόδοσή τους.

Κρίνεται αναγκαίο λοιπόν να διαχωρίσουμε περαιτέρω την C κατηγορία στις υποκατηγορίες SC και BC.

Στη SC ανήκουν εκείνες με working set μικρότερο των 2 MB, καθώς στην περίπτωση 4 πυρήνων μπορούν να συνυπάρχουν στη 8 MB LLC. Πιάνουν μικρό χώρο και δεν επηρεάζονται σημαντικά απο την παρεμβολή.

Στη BC κατηγορία κατατάσσονται εκείνες με working set μεγαλύτερο των 2 MB, οι οποίες χρειάζονται αρκετό χώρο της LLC για να τρέξουν αποδοτικά και όταν περιορίζονται παρουσιάζουν μεγάλες καθυστερήσεις στην εκτέλεσή τους.

Ο τρόπος διαχωρισμού της C κατηγορίας γίνεται στατικά. Για να πραγματοποιηθεί δυναμικά χρειάζονται πολύπλοκες τεχνικές (cache partitioning) που είναι εκτός του πεδίου μελέτης αυτής της εργασίας. Ενδεικτικά παρουριάζουμε στον παρακάτω πίνακα μερικές εφαρμογές (single-threaded and single execution phase) και σε ποιες κατηγορίες ταξινομούνται βάσει του δέντρου που περιγράψαμε.

| Name        | Source    | DataSet (MB) | $B_{in3=LLC}(MB/s)$ | CR3      | CR2     | IPC   | Class |

|-------------|-----------|--------------|---------------------|----------|---------|-------|-------|

| stream      | [2]       | 366          | 6618.432            | 0.994    | 1.003   | 0.721 | L     |

| atax        | polybench | 72           | 4401.339            | 1.029    | 1.759   | 0.380 |       |

| gemver      | polybench | 125          | 1173.694            | 4.299    | 1.315   | 0.402 | LC    |

| mvt         | polybench | 125          | 996.640             | 5.597    | 1.171   | 0.279 |       |

| pchase      | [3]       | 6            | 491.220             | 9.920    | 1.000   | 0.081 | BC    |

| stream      | [2]       | 5            | 99.691              | 51.732   | 1.000   | 0.921 |       |

| correlation | polybench | 2            | 0.706               | 1275.893 | 15.874  | 1.334 | SC    |

| covariance  | polybench | 2            | 0.714               | 1255.327 | 15.960  | 1.332 |       |

| 3mm         | polybench | 0.064        | 0.760               | 1.983    | 72.710  | 2.250 | N     |

| bicg        | polybench | 0.064        | 0.670               | 2.194    | 504.134 | 1.180 |       |

Table 1.1-1: Ταξινόμηση εφαρμογών στις κατηγορίες

#### 3.1.3 Μοντέλο Πρόβλεψης

Περνάμε στο επόμενο στάδιο μετά την ταξινόμηση, την πρόβλεψη της σύγκρουσης μεταξύ των κατηγοριών. Έχοντας μία καλή εκτίμηση για το πως οι κατηγορίες αλληλεπιδρούν μεταξύ τους όταν τρέχουν παράλληλα, μπορούμε να πάρουμε μία έγκυρη απόφαση για το πως θα τοποθετήσουμε τις εφαρμογές ώστε να πάρουμε το επιθυμητό αποτέλεσμα. Παραθέτουμε παρακάτω πως περιμένουμε να επηρεαστούν οι κατηγορίες, όταν τρέξουν παράλληλα με τις υπόλοιπες.

Η Ν κατηγορία περιορίζεται στα χαμηλότερα επίπεδα της ιεραρχίας της μνήμης (ιδιωτικές κρυφές μνήμες) και δεν αλληλεπιδρά με καμία άλλη κατηγορία.

Η L κατηγορία καταναλώνει μεγάλο μέρος του Memory Bandwidth και εξαρτάται απο αυτό. Όταν πολλές L εφαρμογές τρέξουν παράλληλα το συνολικό τους Bandwidth μπορεί να ξεπεράσει αυτό που το σύστημα μπορεί να ικανοποιήσει. Αυτή η σύγκρουση προκαλεί μείωση στην απόδοσή τους που είναι ανάλογη της μείωσης του Bandwidth. Άρα αυτή η κατηγορία επηρεάζεται από τον εαυτό της.

Για την LC κλάση περιμένουμε μικρές καθυστερήσεις όταν εκτελούνται μαζί με τις L. Αυτό μπορεί να συμβεί λόγω της διαμάχης στο Memory Bandwidth και της μόλυνσης της LLC με δεδομένα των L.

Όσον αφορά την SC ομάδα, οι εφαρμογές της επωφελούνται απο τη LLC καθώς φέρνουν σε αυτή ένα μικρό όγκο δεδομένων και κάνουν έντονη επαναχρησιμοποίηση σε αυτά. Περιμένουμε να επηρεάζονται σε ικανοποιητικό βαθμό απο την L κατηγορία, διότι οι εφαρμογές της μολύνουν διαρκώς με δεδομένα τη LLC προκαλώντας καταστροφική παρεμβολή.

Τέλος εξετάζουμε τη BC κλάση, η οποία είναι η πιο ευαίσθητη απο όλες. Λόγω του ότι χρειάζεται το μεγαλύτερο μέρος της LLC για να τρέξει με καλή απόδοση, οποιαδήποτε παρεμβολή σε αυτόν τον πόρο θα προκαλέσει πολύ σοβαρή ζημιά. Επομένως προβλέπεται ότι η L και η LC κατηγορία, οι οποίες μολύνουν με μεγάλη συχνότητα την LLC, να επηρεάζουν την ομαλή εκτέλεση της BC. Επίσης οι εφαρμογές της ίδιας κατηγορίας περιμένουμε να προκαλέσουν μεγάλη διαμάχη στη LLC.

|    | L      | LC     | SC     | BC     | N      |

|----|--------|--------|--------|--------|--------|

| L  | 1.3014 | 1.1273 | 1.6744 | 2.4278 | 1.0821 |

| LC | 1.1184 | 1.0714 | 1.1192 | 2.2216 | 1.0549 |

| sc | 1.0564 | 1.0436 | 1.0783 | 1.4609 | 1.0384 |

| ВС | 1.1438 | 1.0761 | 1.1608 | 2.3253 | 1.0093 |

| N  | 1.0189 | 1.0063 | 1.0008 | 1.0644 | 1.0017 |

Figure 1.1-9: Μέση καθυστέρηση των εφαρμογών όταν εκτελούνται παράλληλα σε επίπεδο κλάσεων

Στο σχήμα 1.1-9 παρουσιάζουμε τη μέση καθυστέρηση που υποφέρει κάθε κατηγορία όταν εκτελείται με μία άλλη. Στον άξονα χ παρουσιάζουμε την καθυστέρηση που επιβάλουν οι κλάσεις, ενώ στον y την καθυστέρηση που υποφέρουν.

Τα αποτελέσματα δείχνουν ότι οι προβλέψεις μας είναι έγκυρες. Η πιο ευάλωτη κλάση είναι η BC, που επηρεάζεται από τις L, LC και BC. Η L και SC βλέπουμε ότι επηρεάζονται σε μικρότερο βαθμό απο την L. Η N και η LC δεν φαίνονται να παρουσιάζουν καθυστερήσεις, όταν τρέχουν με τις άλλες κατηγορίες.

#### 3.1.4 Απόφαση

Στο τελευταίο αυτό στάδιο εφαρμόζουμε την πολιτική μας, αποφασίζοντας με ποιο τρόπο θα συνδιάσουμε τις εφαρμογές, ώστε να αποφύγουμε τη σύγκρουση για τους μοιραζόμενους πόρους. Με αυτό το τρόπο επιδιώκουμε να προσφέρουμε ένα περιβάλλον, στο οποίο οι διεργασίες θα εκτελούνται με υψηλή απόδοση (κοντά στην απόδοση που βιώνουν όταν εκτελούνται μόνες τους) και κατ'επέκταση η κατανομή των πόρων θα γινεται δίκαια.

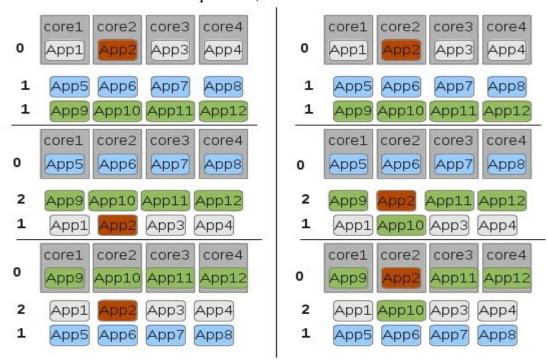

Ο χρονοδρομολογητής μας λαμβάνει υπ'όψιν του τη διαμάχη για τη LLC και το Memory Bandwidth και ονομάζεται CMB (Cache and Memory Bandwidth contention-aware scheduler). Υπενθυμίζουμε ότι επειδή δουλεύουμε στο ένα τσιπ, στο οποίο 4 πυρήνες μοιράζονται μια LLC, έχουμε τη δυνατότητα να χωρίσουμε τις εφαρμογές στο χρόνο μόνο (time-sharing). Έτσι συνδιάζουμε τις εφαρμογές σε τετράδες που εκτελούνται σε διαφορετικά κβάντα χρόνου, με σκοπό να αποφύγουμε τη μεταξύ τους σύγκρουση.

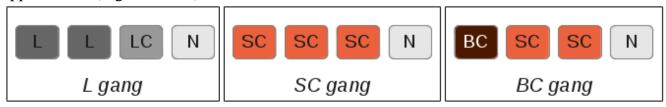

Βασισμένοι στο μοντέλο πρόβλεψης και στα αποτέλεσμα της συνεκτέλεσης των κατηγοριών, δημιουργούμε μία πολιτική με προτεραιότητες. Η πρώτη μας προτεραιότητα είναι να απομονώσουμε την BC κατηγορία που είναι πιο ευάλωτη. Επίσης θέλουμε να προστατέψουμε τη SC κατηγορία και τέλος να μετριάσουμε τη διαμάχη των L για το Memory Bandwidth. Για αυτό το λόγο δημιουργούμε τρεις πιθανές τετράδες.

Στην μία (BC) επιτρέπεται να είναι μαζί BC με SC με N εφαρμογές, καθώς βλέπουμε απο τον παραπάνω πίνακα ότι σε αυτήν την περίπτωση δεν επιβάλλονται μεγάλες

καθυστερήσεις. Το ιδανικό θα ήταν αυτή η τετράδα απο μόνο μία BC εφαρμογή καθώς όπως ξέρουμε η συνεκτέλεση τους προκαλεί καταστροφική παρεμβολή, αλλά αυτό είναι εφικτό όταν ο αριθμός των BC είναι μικρός και μπορούν να απομονωθούν πλήρως στις τετράδες.

Στην δεύτερη τετράδα (SC) μπορούν να βρίσκονται πολλές SC μαζί με N εφαρμογές. Με αυτό τον τρόπο επιτυγχάνουμε αποφυγή σύγκρουσης SC με L.

Η τρίτη τετράδα (L) αποτελείται απο L, LC ή N εφαρμογές.

Τα βήματα που ακολουθεί ο χρονοδρομολογητής για τον σχηματισμό αυτών των τετράδων παρουσίαζονται στον παρακάτω πίνακα 1.1-2. Παράλληλα παραθέτουμε και το σκοπό που κάθε βήμα εξυπηρετεί.

| Βήματα                                                                                         | Στόχοι                                          |  |

|------------------------------------------------------------------------------------------------|-------------------------------------------------|--|

| 1) μεγιστοποίησε της BC τετράδες και άπλωσε τις BC εφαρμογές                                   | Απέφυγε τη παρεμβολή των ΒC με τις ΒC και τις L |  |

| 2)συγκέντρωσε τις SC εφαρμογές ώστε να ελαχιστοποιήσεις τις SC τετράδες                        | Απέφυγε τη παρεμβολή των SC με τις L            |  |

| 3) Ταξινόμησε τις L εφαρμογές ως προς το Bandwidth και μοίρασε τες στις τετράδες που απομένουν | Ισορρόπησε τη χρήση του Memory Bandwidth        |  |

Table 1.1-2: Βήματα και στόχοι του CMB χρονοδρομολογητή

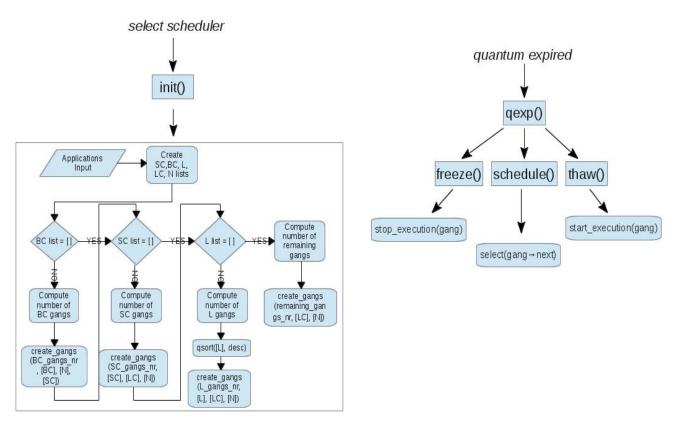

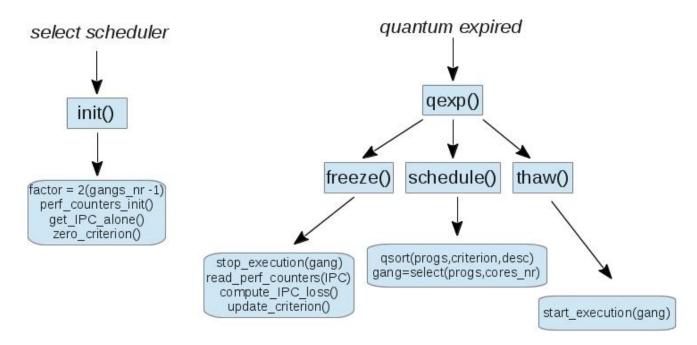

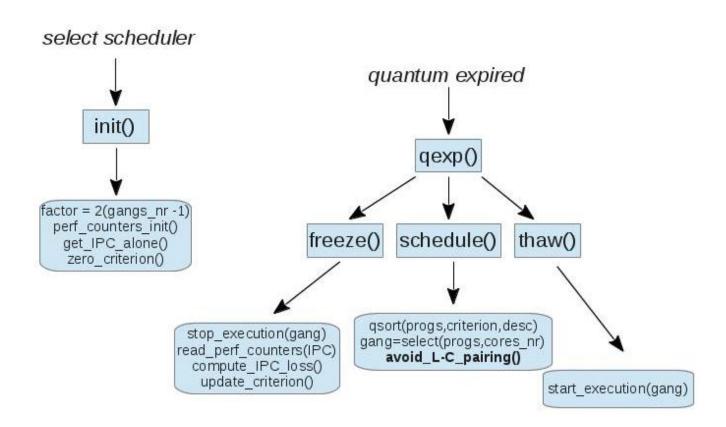

Ο χρονοδρομολογητής μας υλοποιείται σε 5 συναρτήσεις, init(), qex(), thaw(), freeze(), schedule(). Η qex() καλείται μετά το τέλος του κβάντου χρόνου και καλεί με τη συγκεκριμένη σειρά τις freeze(), schedule() και thaw(). Στη freeze() σταματάμε την τετράδα που έτρεχε, στη schedule() επιλέγουμε την επόμενη τετράδα, στην περίπτωση μας οι τετράδες εκτελούνται κυκλικά, και στη thaw() ξεκινάμε την εκτέλεση της τετράδας που επιλέχθηκε προηγουμένως. Στην init() γίνεται ο σχηματισμός των τετράδων, όπως περιγράφηκε.

Οι τετράδες και οι κλάσεις υλοποιούνται σε λίστες. Οι εφαρμογές έχουν ταξινομηθεί offline. Ο αλγόριθμος έχει πολυπλοκότητα O(n + L log L), O(n) για τον διαχωρισμό των εφαρμογών στις διαφορετικές ομάδες και O(L log L) για την ταξινόμηση των L εφαρμογών (code 1.1-1), και O(1) για την απόφαση. Μετά το σχηματισμό των τετράδων οι τετράδες εκτελούνται κυκλικά σε κάθε κβάντο χρόνου.

```

void create_gangs (gangs_nr, apps_l){

list_t

gangs[gangs_nr];

for_each_app_in_list(apps_l){

remove from top (apps 1);

add_to_tail (gangs[i++]);

void form_gangs(apps){

move_to_lists(apps);

gangs_nr = (apps_nr / cores_nr);

minimum_L = (L_nr / cores_nr);

BC_gangs_nr = 0;

SC gangs nr = 0;

if (BC_list != []){

maximum BC = (gangs nr - minimum L);

BC_gangs_nr = ((BC_nr < maximum_BC) ?

BC_nr : maximum_BC);

create_gangs(BC_gangs_nr, [BC, N, SC]);

if (SC_list != []){

SC_gangs_nr = (SC_nr / cores_nr);

create_gangs(SC_gangs_nr, [SC, LC, N]);

remaining_gangs_nr = gangs_nr - (BC_gangs_nr +

SC gangs nr);

if (L_list == []) create_gangs(remaining_gangs_nr, [LC, N]);

else{

quicksort(L list);

create_gangs(remaining_gangs_nr, [L, LC, N]);

```

Code 1.1-1: Αλγοριθμος του CMB χρονοδρομολογητή

#### 3.2 Δεύτερη Προσέγγιση (Διαχειρίζοντας τη σύγκρουση)

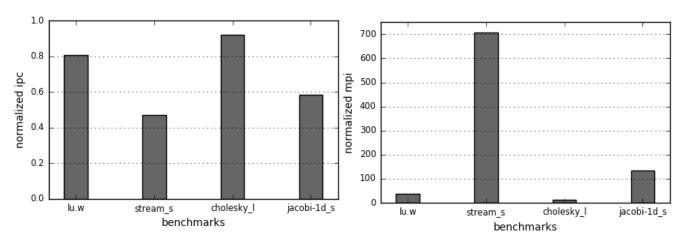

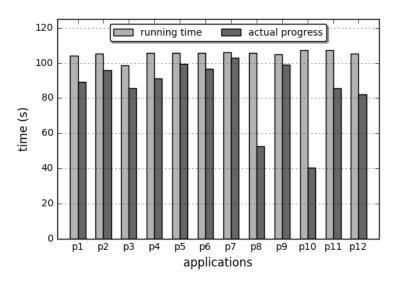

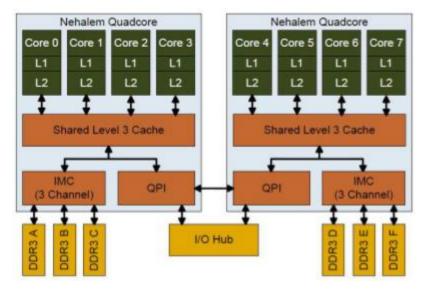

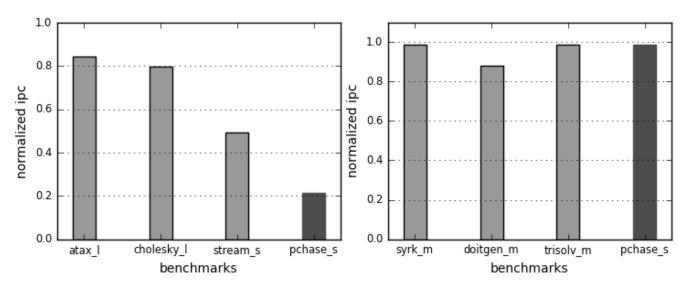

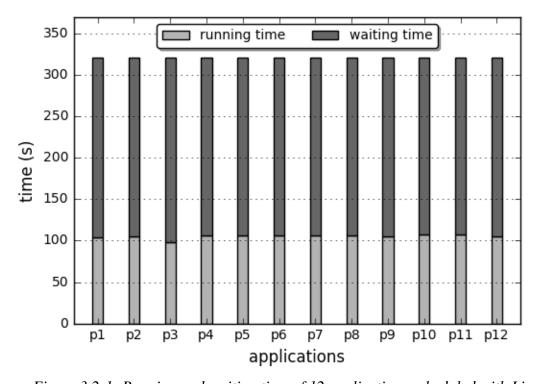

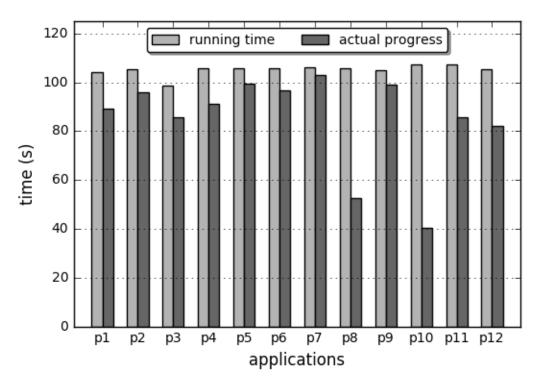

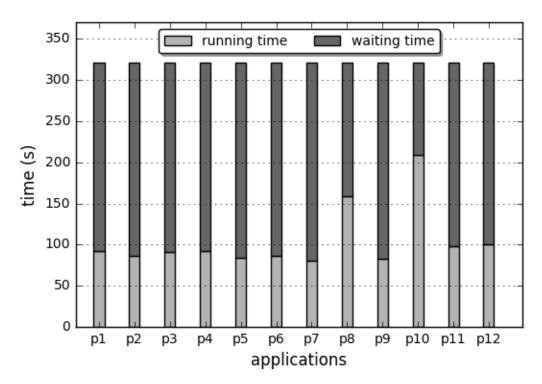

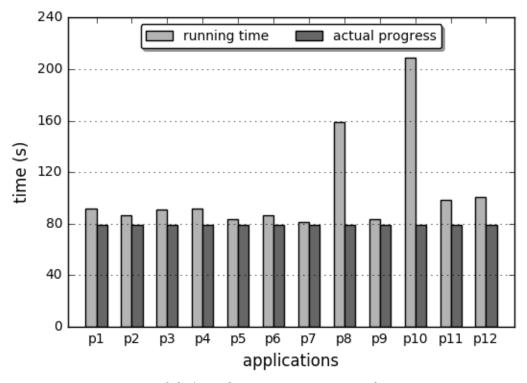

Σε αυτή τη τεχνική σκοπός μας είναι να διαχειριστούμε τα αποτελέσματα της σύγκρουσης των εφαρμογών. Όπως είδαμε σε προηγούμενο κεφάλαιο οι διεργασίες δεν επηρεάζονται το ίδιο απο τη μεταξύ τους και η επίπτωση στην πρόοδο τους είναι διαφορετική. Αυτό έχει ως αποτέλεσμα την άνιση κατανομή των πόρων σε αυτές. Τρέχουμε 12 εφαρμογές με το Linux scheduler για 320 δευτερόλεπτα και παρατηρούμε ότι δίνει ίδια ευκαιρία στις εφαρμογές να εκτελεστούν, αλλά δεν κατανέμει την πρόοδο τους δίκαια. Η πρόοδος υπολογίζεται ως το γινόμενο των φορών που εκτελέστηκε η κάθε εφαρμογή επί το χρόνο που χρειάζεται για να εκτελεστεί όταν τρέχει μόνη της.

Αυτό που επιδιώκουμε εμείς είναι οι διεργασίες να κάνουν την ίδια πρόοδο στη χρονική περίοδο που τους δίνεται να τρέξουν. Λαμβάνοντας υπ'όψιν ότι η πρόοδος τους καθορίζεται απο το κλάσμα  $IPC_{co-running}/IPC_{alone}$  και από το χρόνο που τρέχουν στον πυρήνα, μια

Figure 1.1-10: Δικαιη κατανομή χρόνου αλλά όχι προόδου

εφαρμογή A με χαμηλότερο IPC από αυτό μιάς άλλης B πρέπει να τρέξει περισσότερο χρόνο απο την B ώστε οι πραγματικοί χρόνοι που αυτές έτρεξαν να έρθουν στα ίδια επίπεδα.

Οδηγούμενοι απο αυτήν την παρατήρηση, σχεδιάζουμε έναν χρονοδρομολογητή, ο οποίος λαμβάνει υπ'όψιν του την μείωση του IPC που κάθε διεργασία έχει υποστεί μετά το τέλος της εκτέλεσής της και τις ευνοεί αναλόγως. Επιδιώκει να αυξήσει το χρόνο εκτέλεσης αυτών που έχουν μεγάλη μείωση στο IPC, με σκοπό να αυξήσει την πραγματική τους πρόοδο, μειώνοντας το χρόνο και συνεπώς πρόοδο εκείνων που τρέχουν με μεγαλύτερο IPC. Με αυτόν τον τρόπο μπορεί να κατανέμουμε άνισα το χρόνο του επεξεργαστή ανάμεσα στις διεργασίες, διαβεβαιώνουμε όμως ότι όλες θα κάνουν την ίδια πρόοδο.

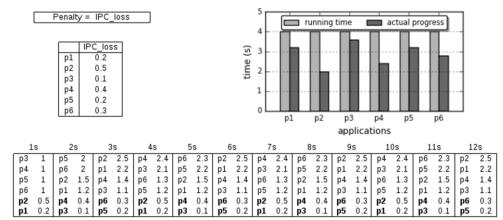

Στην υλοποίησή μας χρησιμοποιούμε μία ουρά διεργασιών για όλους τους πυρήνες. Μετά από κάθε κβάντο χρόνου η ουρά αυτή ταξινομείται σε φθίνουσα σειρά με βάση ένα κριτήριο, που έχουμε επιλέξει και θα εξηγήσουμε παρακάτω, και οι τέσσερις πρώτες διεργασίες επιλέγονται για να τρέξουν στους πυρήνες.

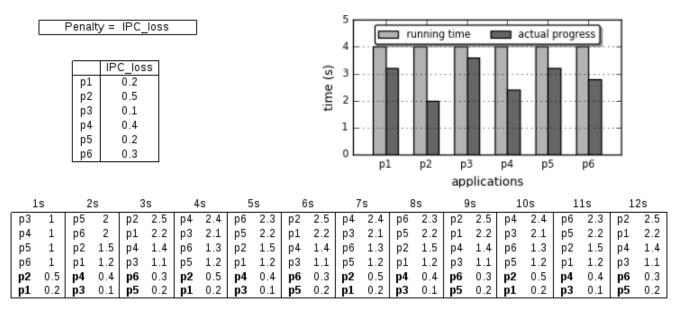

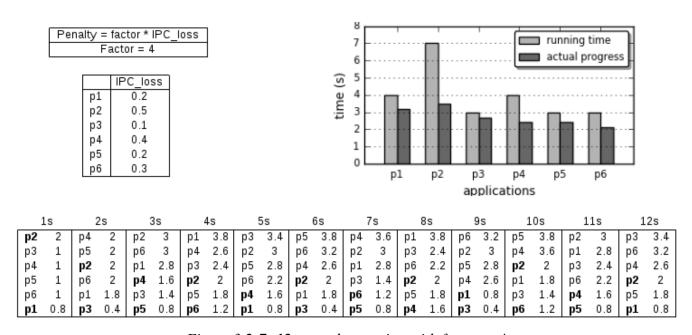

Η βασική ιδέα είναι να ευνοούμε τις διεργασίες ανάλογα με το πόσο IPC έχασαν την τελευταία φορά που ήταν στον πυρήνα. Αυτό το επιτυγχάνουμε προωθώντας αυτές τις διεργασίες ψηλότερα στην ουρά, έτσι ώστε να έχουν την ευκαιρία να εκτελεστούν συχνότερα, αυξάνοντας την πρόοδο τους. Για αυτό το λόγο ταξινομούμε τις διεργασίες με βάση το παρακάτω κριτήριο criterion = waiting time + factor \* IPC\_loss .Στην περίπτωση που είχαμε μόνο το waiting time οι διεργασίες θα επιλέγονταν κυκλικά και θα είχαν ίση κατανομή χρόνου. Τώρα όμως αυτές που μόλις έτρεξαν με μεγάλο IPC\_loss μπορούν να ξεπεράσουν μερικές άλλες στη ουρά και να τοποθετηθούν στον επεξεργαστή νωρίτερα, καθυστερώντας εκείνες που έτρεξαν με καλύτερο IPC. Το IPC\_loss υπολογίζεται πολύ εύκολα, μετά το τέλος του κβάντου χρόνου για τις διεργασίες που ήταν στον πυρήνα, από τη σχέση IPC\_loss =  $\left(1-\frac{\text{IPC}_{\text{co-running}}}{\text{IPC}_{\text{alone}}}\right)$ . Το  $\text{IPC}_{alone}$  το υπολογίζουμε offline για κάθε διεργασία, ενώ το  $\text{IPC}_{\text{co-running}}$  το αποκτούμε μετά από κάθε κβάντο χρόνου από τους hardware performance

counters που παρέχει ο επεξεργαστής μας.

Figure 1.1-11: Εκτέλεση 12 δευτερολεπτων χωρίς factor σε 2-πύρηνο σύστημα

Το IPC\_loss από μόνο του δεν είναι ικανό να προωθήσει σωστά τις διεργασίες. Για αυτό το λόγο χρειάζεται να πολλαπλασιαστεί με τον παράγοντα factor. Αυτό γίνεται εμφανές στο παράδειγμα του σχήματος 1.1-11. Παρατηρούμε ότι καθώς το IPC\_loss κυμαίνεται μεταξύ 0 και 1, είναι αδύνατο να ξεπεράσει τις διεργασίες που περιμένουν στην ουρά με waiting time 1 και 2 δευτερόλεπτα (κβάντο χρόνου = 1 δευτερόλεπτο).

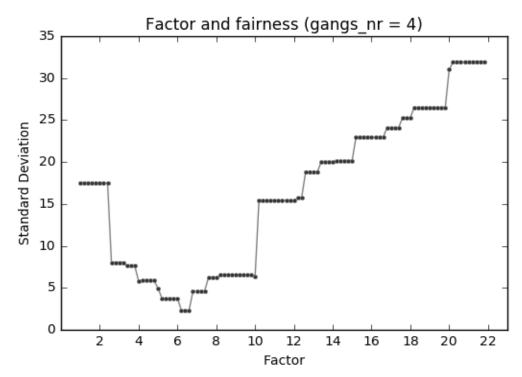

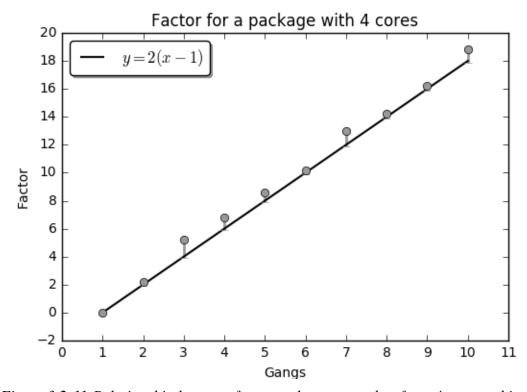

Figure 1.1-12: Σχέση μεταζύ παράγοντα και αριθμό τετράδων

Ο παράγοντας factor είναι ένας ακέραιος που εξαρτάται απο το κβάντο χρόνου και τις ομάδες των διεργασιών και καθορίζει τη σωστή προώθηση των διεργασιών στην ουρά. Στο παράδειγμά μας αν ο παράγοντας 4 ικανοποιούσε τις απαιτήσεις μας και αλλάζαμε τον φόρτο εργασίας προσθέτοντας μερικές διεργασίες τότε οι ομάδες που θα περίμεναν να τρέξουν στους πυρήνες θα αυξάνονταν. Αυτό σημαίνει ότι και το waiting time θα αυξανόταν συνολικά. Σε

αυτή την περίπτωση η προηγούμενη τιμή δεν θα ήταν αρκετή για να μας ανεβάσει τις διεργασίες στην ουρά. Το ίδιο ισχύει και για μια πιθανή αλλαγή του κβάντου χρόνου

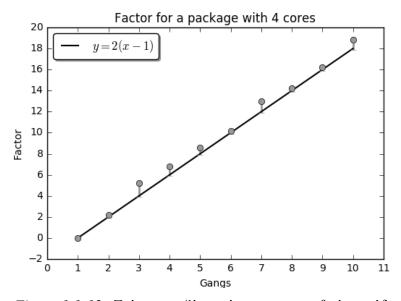

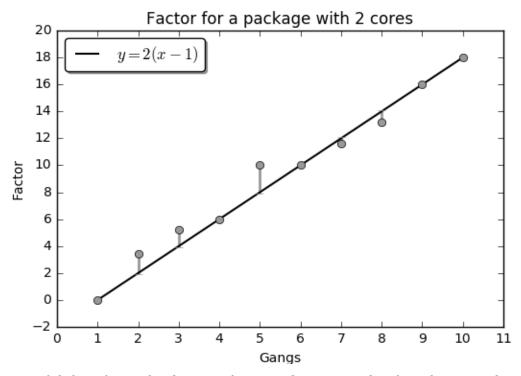

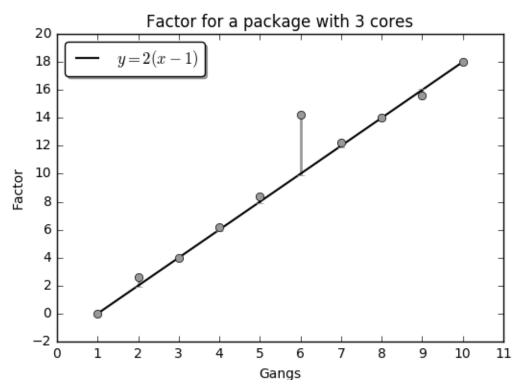

Σκοπός μας είναι να βγάλουμε μία σχέση με την οποία θα καθορίσουμε τον factor μια για πάντα για οποιοδήποτε σύστημα. Με κβάντο χρόνο ίσο με 1 δευτερόλεπτο βρίσκουμε για διάφορες ομάδες διεργασιών τον παράγοντα που οδηγεί στην καλύτερη απόδοση, δηλαδή ίση κατανομή της προόδου. Επειδή είναι πολυ χρονοβόρο και σχεδόν ανέφικτο να κάνουμε δοκιμές για όλες τις πιθανές ομάδες σε πραγματικό σύστημα, προσωμοιόνουμε την πολιτική μας. Δημιουργούμε όλες τις πιθανές ομάδες για τα συστήματα δύο, τριών και τεσσάρων πυρήνων και για κάθε ομάδα ελέγχουμε επαναληπτικά ένα εύρος από παράγοντες. Κρατάμε εκείνον που οδηγεί στην μικρότερη τυπική απόκλιση της προόδου των διεργασιών. Ενδεικτικά παραθέτουμε τα αποτελέσματα τις προσομοίωσης για ένα 4-πύρηνο σύστημα για το διαφορετικό αριθμό τετράδων. Η ίδια εικόνα παρουσιάζεται και για τα υπόλοιπα συστήματα που εξετάσαμε (δύο, τριών πυρήνων).

Βλέπουμε λοιπόν ότι η σχέση μεταξύ παράγοντα και αριθμού ομάδων με κβάντο χρόνου ίσο με 1 δευτερόλεπτο είναι η εξής :

$$Factor = 2 \cdot (gangs\_nr - 1)$$

$$gangs\_nr = \frac{progs\_nr}{cores\ nr}$$

Είμαστε έτοιμοι λοιπόν να υλοποιήσουμε το χρονοδρομολογητή μας, σκοπός του οποίου είναι να προσφέρει δίκαιη κατανομή τής προόδου μεταξύ των διεργασιών (FOP-Fairness over Progress scheduler).

Όπως στην προηγούμενη προσέγγιση μας, ο χρονοδρομολογητής υλοποιείται σε 5 συναρτήσεις όπως φαίνεται στον κώδικα 1.1-2.

Στην init() ενεργοποιούμε τους performance counters, λαμβάνουμε το IPCalone για κάθε εφαρμογή, υπολογίζουμε το σύνολο των τετράδων που θα τρέξουν και εν συνεχεία τον παράγοντα. Η quantum\_expired() καλείται μετά το τέλος του κβάντου και καλεί με τη σειρά τις freeze(), schedule() και thaw(). Στη freeze σταματάμε την τετράδα που ήταν στους πυρήνες, λαμβάνουμε το IPCco-running, βρίσκουμε το IPCloss και υπολογίζουμε το penalty. Ανανεώνουμε επίσης το waiting time και συνεπώς το criterion για όλες τις εφαρμογές. Στη schedule() ταξινομούμε τις εφαρμογές σε φθίνουσα σειρά με βάση το criterion και επιλέγουμε τις 4 πρώτες προς εκτέλεση. Στη thaw() εκτελούμε τις επιλεγμένες εφαρμογές. Η πολυπλοκότητα του FOP scheduler για την απόφαση είναι O(n log n) (πολυπλοκότητα της quicksort), η ουρά υλοποιείται σαν λίστα.

```

void init (){

gangs_nr = progs_nr/cores_nr;

factor = 2 (gangs_nr - 1);

counters = perf counters init(selected events);

for_each_application_in_list(progs_all_list){

application->criterion = 0;

application->IPC alone = get IPC parameter();

void schedule(){

quicksort(progs_all_list, criterion, DESCENDING);

while (number(progs_schedule_list) < cores_nr){

remove_from_top(progs_all_list);

add_to_tail(progs_schedule_list);

void thaw(){

for_each_application_in_list(progs_schedule_list){

start_running(application);

perf_counters_zero(counters);

perf_counters_start(counters);

void freeze(){

perf_counters_stop(counters);

for_each_application_in_list(progs_schedule_list){

stop running(application);

value = perf_counters_read(counters);

IPC_co-running = get_IPC(value);

IPC\_loss = (1 - IPC\_co-running/application > IPC\_alone);

application->waiting time = 0;

application->penalty = factor * IPC loss;

remove from top(progs schedule list);

add_to_tail(progs_all_list);

for_each_application_in_list(progs_all_list){

update waiting time(application);

application->criterion = waiting_time + penalty;

void quantum_expired(){

freeze();

if (current_tics < RUN_TICS){

schedule();

thaw();

}else{

stop execution();

print_results();

```

Code 1.1-2: Αλγόριθμος του FOP scheduler

#### 3.2 Τρίτη Προσέγγιση (Αποφεύγοντας και διαχειρίζοντας τη σύγκρουση)

Σε αυτή τη προσέγγιση μας επεκτείνουμε τον προηγούμενο χρονοδρομολογητή έτσι ώστε να αποφεύγει τη σύγκρουση ορισμένων εφαρμογών. Από το μοντέλο πρόβλεψης της σύγκρουσης των διαφορετικών κατηγοριών βλέπουμε ότι η απόδοση των C (SC, BC) εφαρμογών μειώνεται σημαντικά όταν εκτελούνται μαζί με L (x1.67 καθυστέρηση για τη SC, x2.43 καθυστέρηση για τη BC). Θέλοντας να παρέχουμε ένα περιβάλλον, στο οποίο οι διεργασίες θα εκτελούνται πιο αποδοτικά, μετασχηματίζουμε την προηγούμενη τεχνική ώστε να αποφεύγει την εκτέλεση των L με τις C. Με αυτό τον τρόπο οι C έχουν τη δυνατότητα να κάνουν μεγαλύτερη πρόοδο. Σε ευρύτερη κλίμακα αυτό σημαίνει βελτιωμένο throughput σε σχέση με τον FOP scheduler. Τους 'κακούς' συνδιασμούς που δεν μπορούμε να αποφύγουμε τους διαχειριζόμαστε, εφαρμόζωντας την ίδια πολιτική με τον FOP.

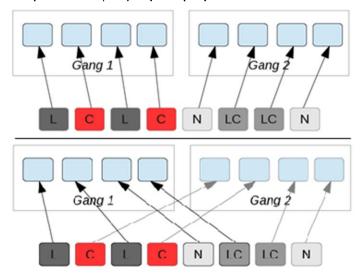

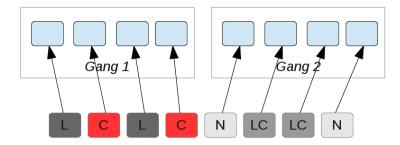

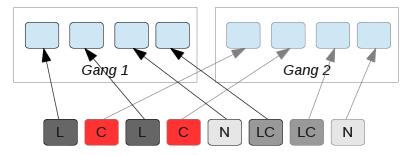

Ο FOP-LCI (Fairness over Progress with L-C Isolation) scheduler μετά την ταξινόμηση της ουράς διαμοιράζει τις εφαρμογές όπως φαίνεται στο σχήμα 1.1-13. Όπως παρατηρούμε είναι πιθανό μερικές εφαρμογές που δεν ήταν η σειρά τους να τρέξουν, να τοποθετηθούν στον πυρήνα νωρίτερα, 'κλέβοντας' τη σειρά αυτών που έπρεπε να τρέξουν. Εφ'όσον έμειναν εκτός πυρήνα για άλλο ένα κβάντο χρόνου το waiting time τους θα αυξηθεί και επομένως το κριτήριο τους. Θα φτάσουν, λοιπόν, να είναι στην αρχή της ουράς και να εκτελεστούν με τις επιθυμητές εφαρμογές. Με αυτό τον τρόπο αποφεύγουμε τη λιμοκτονία.

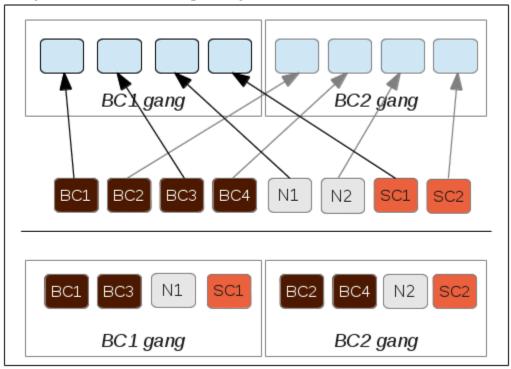

Figure 1.1-13: Επιλογή τετράδων με τον FOP(πάνω) και με τον FOP-LCI (κάτω)

Ο FOP-LCΙ διαφοροποιείται σε σχέση με τον FOP μόνο στη συνάρτηση schedule(). Ο κώδικάς της φαίνεται δίπλα (Code 1.1-3). Οι εφαρμογές ταξινομούνται με βάση το σχήμα του πρώτου CMB scheduler. Η πολυπλοκότητα για την απόφαση είναι όπως και πριν O(n log n) (πολυπλοκότητα της quicksort).

```

void schedule()

L_ON = 0;

C_ON = 0;

allowed = 1;

quicksort(progs_all_list, criterion, DESCENDING);

for_each_app_in_list(progs_all_list)

switch (app->class)

case L_CLASS:

if (C_ON) allowed = 0;

else L_ON = 1;

case C_CLASS:

if (L_ON) allowed = 0;

else C_ON = 1;

if (allowed)

if (number(progs_schedule_list) != cores_nr)

remove_app_from_list(progs_all_list);

add_to_tail(progs_schedule_list);

```

Code 1.1-3: Schedule() συνάρτηση του FOP-LCI scheduler

# Κεφάλαιο 4 Αξιολόγηση

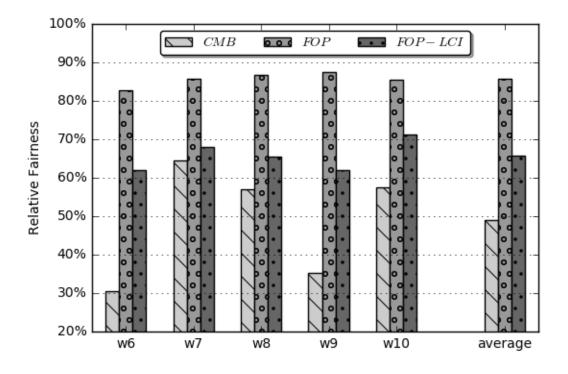

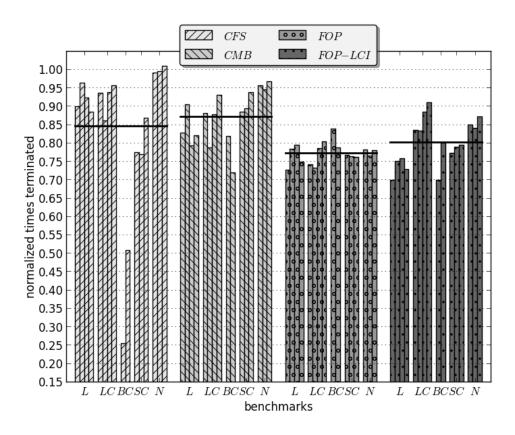

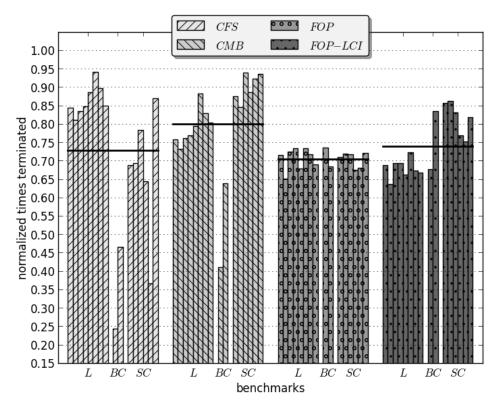

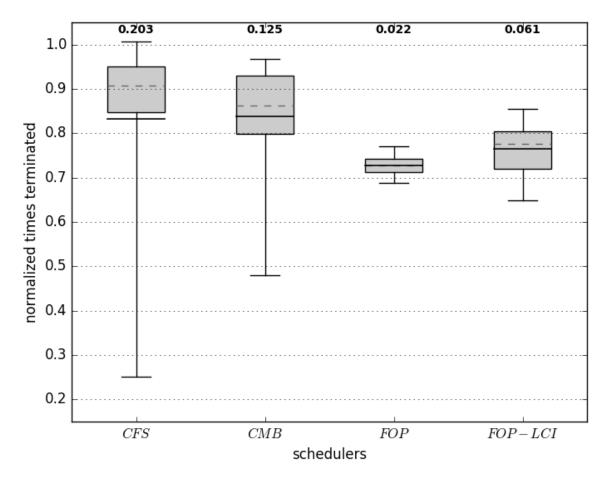

Για την αξιολόγηση των πολιτικών μας δημιουργούμε 3 ομάδες πειραμάτων, με 5 φόρτους εργασιών σε κάθε ομάδα. Στην πρώτη ομάδα δημιουργούμε φόρτους εργασιών συνδιάζοντας όλες τις κατηγορίες εφαρμογών εκτός της BC. Η δεύτερη αποτελέιται απο εφαρμογές όλων των κατηγοριών και από αριθμό BC εφαρμογών, οι οποίες μπορούν να απομονωθούν πλήρως σε διαφορετικές τετράδες. Στην τελευταία ομάδα ο αριθμός των BC εφαρμογών είναι τέτοιος και η πλήρης απομόνωση τους δεν είναι εφικτή. Κάθε φόρτος εργασιών αποτελείται από 16 εφαρμογές. Οι εφαρμογές έχουν ταξινομηθεί offline. Σε κάθε εκτέλεση επιθυμούμε ο φόρτος διεργασιών να είναι σταθερός, έτσι επανεκτελούμε κάθε εφαρμογή που τερματίζει. Η πλατφόρμα που χρησιμοποιήσαμε είναι αυτή που περιγράψαμε σε προηγούμενο κεφάλαιο και ασχοληθήκαμε με το ένα τσιπ, ώστε να δοκιμάσουμε τις τεχνικές μας σε περιβάλλον που μας δίνει τη δυνατότητα να μοιράσουμε τις εφαρμογές μόνο χρονικά.

Ενδιαφερόμαστε να μετρήσουμε το κατά πόσο δίκαια κατανέμονται οι πόροι (fairness) και πόσες διεργασίες εκτελούνται ανα μονάδα χρόνου (throughput). Γιαυτό το λόγο χρησιμοποιούμε δύο μετρικές, την τυπική απόκλιση (2) και τον μέσο (1). Τις μετρικές αυτές τις εφαρμόζουμε στο σύνολο των εφαρμογών, στο κλάσμα των φορών που τερματίστηκαν με την κάθε τεχνική προς τον ιδανικό αριθμό που θα τερματιζόντουσαν αν δεν υπήρχε σύγκρουση (3).

$$T(s) = average(N(s,i)), for all applications i$$

(1)

$F(s) = \sigma(N(s,i)), for all applications i$  (2)

$$N(s,i) = \frac{times\_terminated(s,i)}{ideal\_times\_terminated(i)}, \qquad s = scheduler, i = application (3)$$

$$ideal\_times\_terminated(i) = \frac{execution\_time}{time(i)_{alone-execution}}, i = application(4)$$

$$execution\_time = total\_execution\_time \cdot \frac{cores\_nr}{apps\_nr}$$

(5)

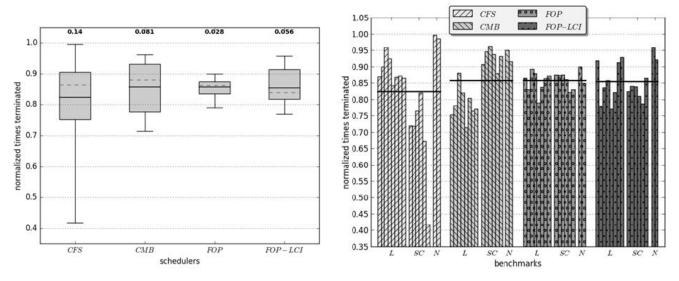

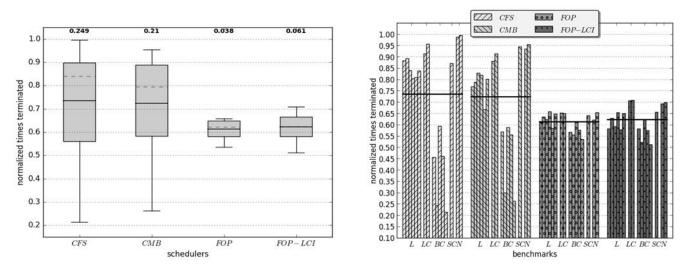

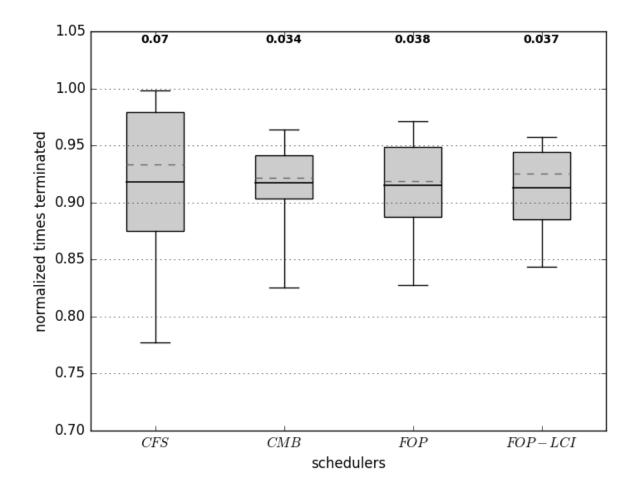

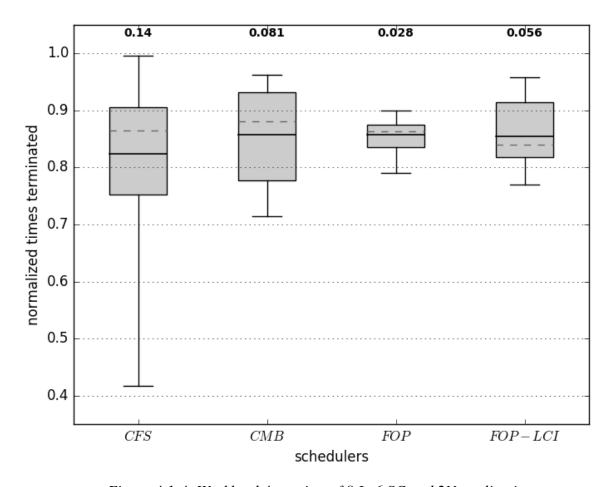

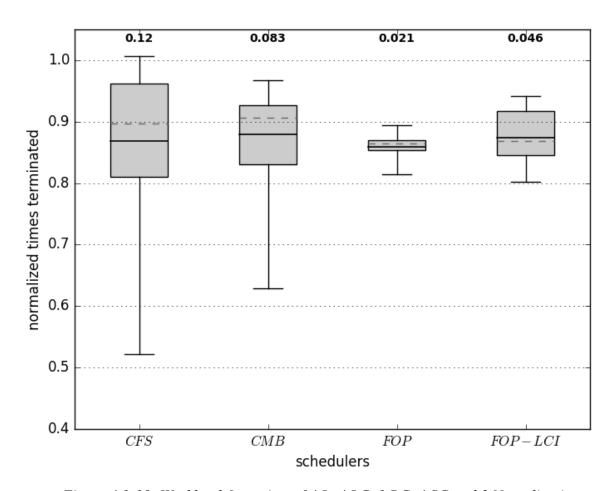

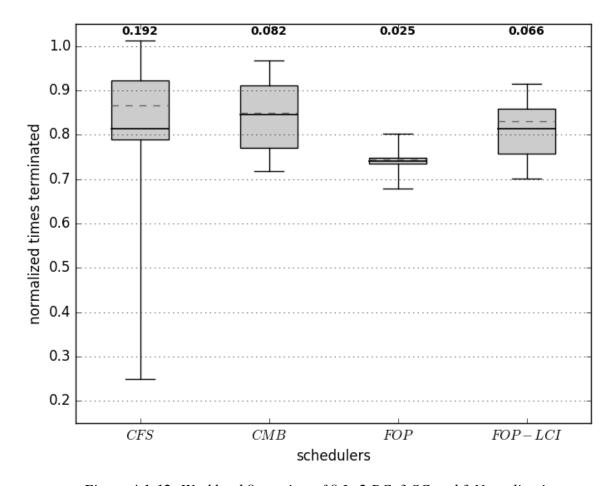

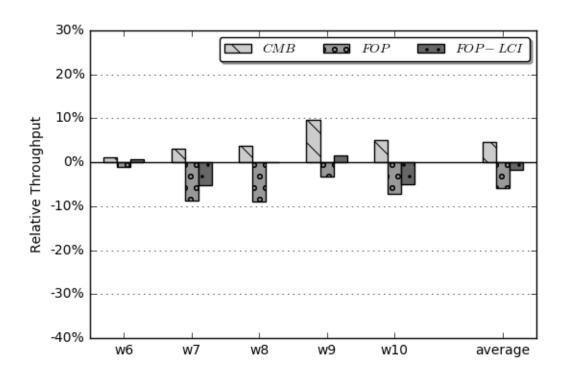

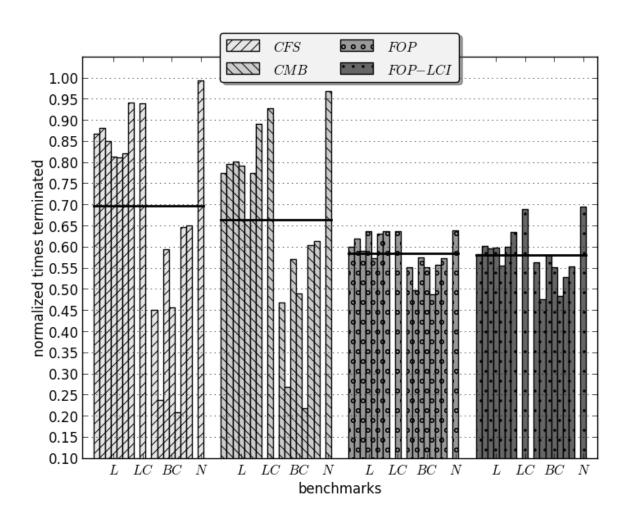

Παραθέτουμε μία ενδεικτική μέτρηση για κάθε ομάδα πειραμάτων. Χρησιμοποιούμε boxplots για να δείξουμε την γενική εικόνα μεταξύ των τεχνικών μας και barcharts για να δείξουμε πιο αναλυτικά την απόδοση κάθε εφαρμογής. Σε κάθε ομάδα συγκρίνουμε τις τεχνικές μας με το Linux scheduler όσον αφορά το throughput και το fairness.

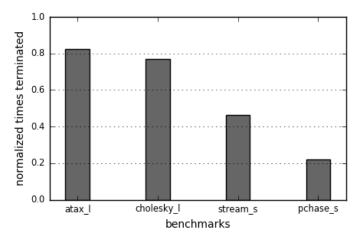

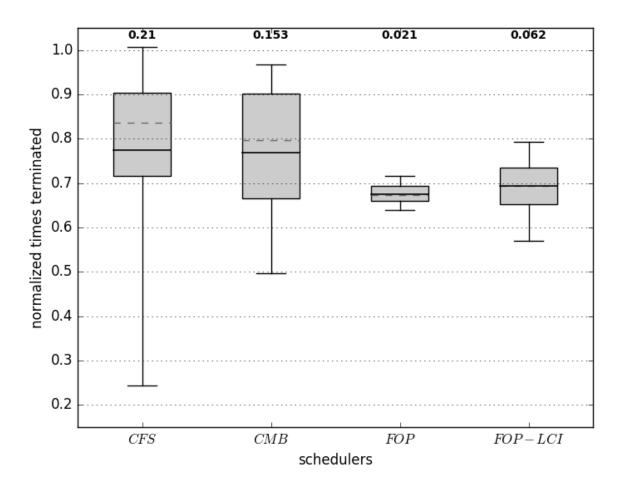

#### Πρώτη Ομάδα Πειραμάτων

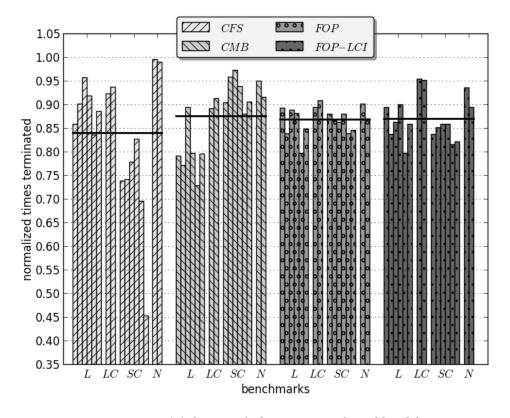

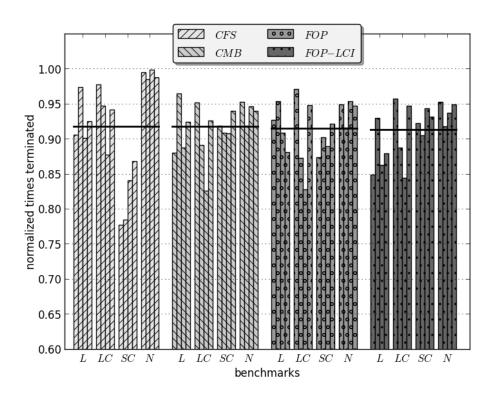

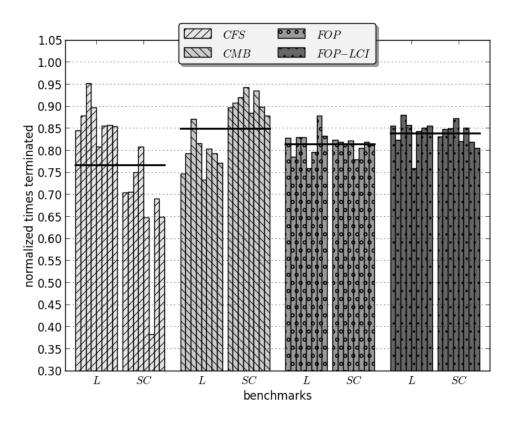

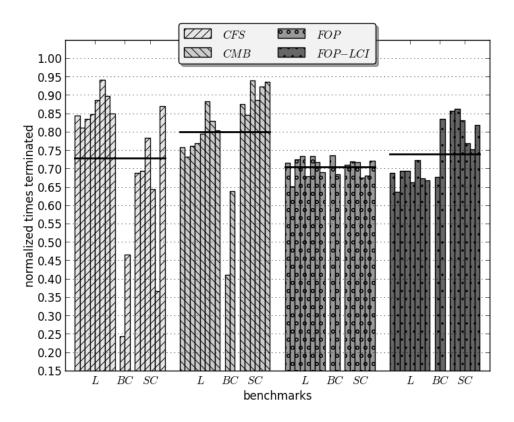

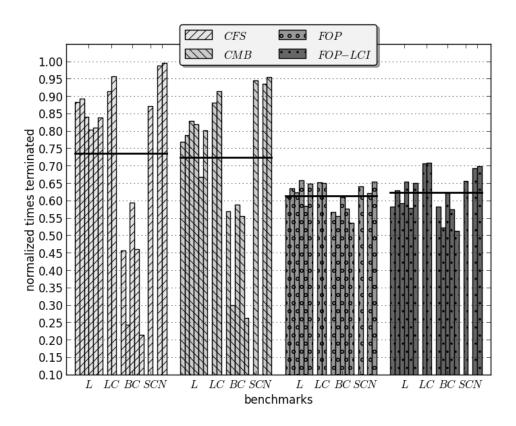

Παραθέτουμε παρακάτω ένα φόρτο διεργασιών με 8 L, 6 SC και 2 N. (σχήμα 1.1-14)

Figure 1.1-14 : Φόρτος διεργασιών με 8 L, 6 SC και 2 N διεργασίες

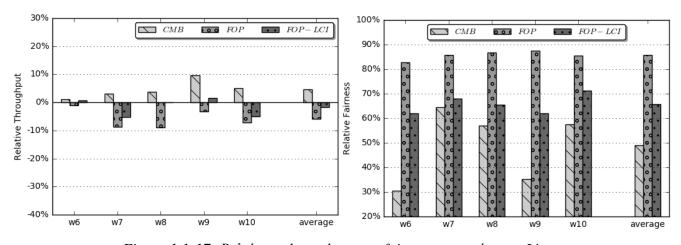

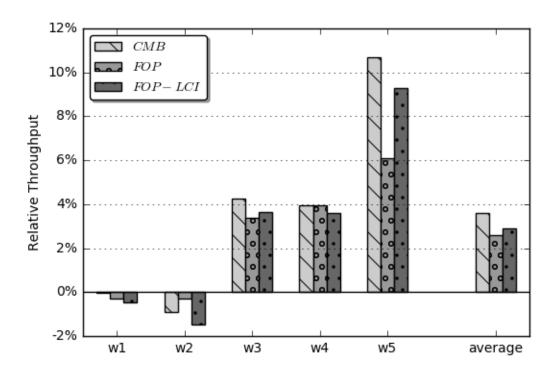

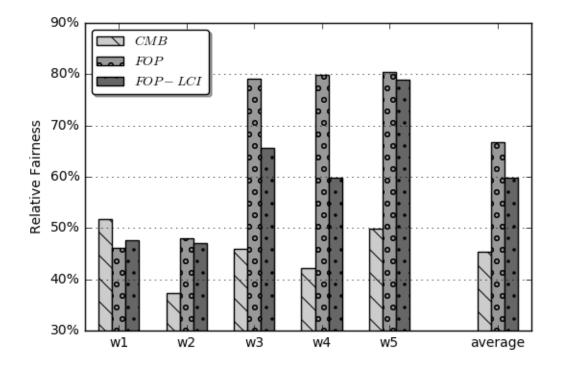

Παρατηρούμε ότι όλες οι τεχνικές που προτείναμε υπερτερούν και σε throughput και σε fairness τον Linux scheduler. Την καλύτερη απόδοση όσον αφορά το throughput επιδεικνύει ο FOP, φέρνοντας την πρόοδο των διεργασιών σχεδόν στην ίδια ευθεία. Ο CMB παρουσιάζει το μεγαλύτερο throughput, δίνοντας μία σημαντική ώθηση στις SC εφαρμογές και μειώνοντας ελαφρά τις L (λόγω πακεταρίσματος). Για το FOP-LCI, παρατηρούμε παρόμοια συμπεριφορά με το FOP. Βλέπουμε ότι ευνοεί τις N εφαρμογές αντι των SC και αυτό δικαιολογείται απο το γεγονός ότι οι N είναι ουδέτερες, δηλαδή μπορούν να τρέξουν και με τις L και με τις C.

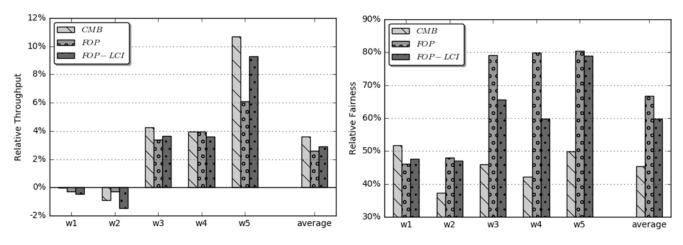

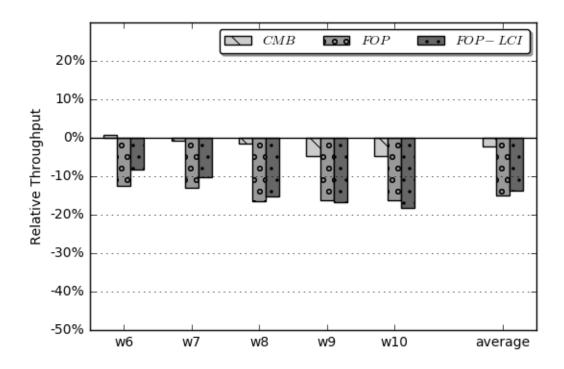

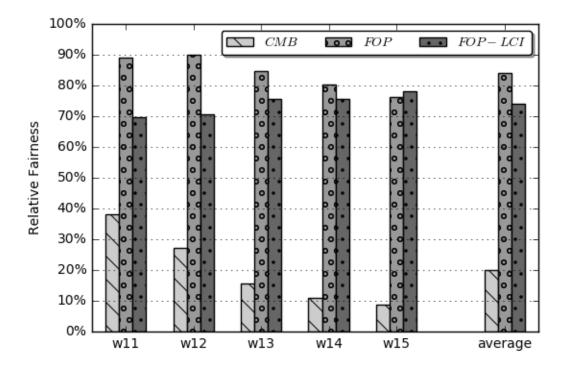

Figure 1.1-15: Βελτίωση throughput και fairness σχετικά με το Linux

Στο σχήμα 1.1-15 παρουσιάζουμε τα αποτελέσματα σύγκρισης με το Linux scheduler των φόρτων της πρώτης ομάδας. Όσον αφορα το throughput, ο CMB δείχνει τα καλύτερα αποτελέσματα, ενώ σχετικά με το fairness, πρώτος έρχεται ο FOP.

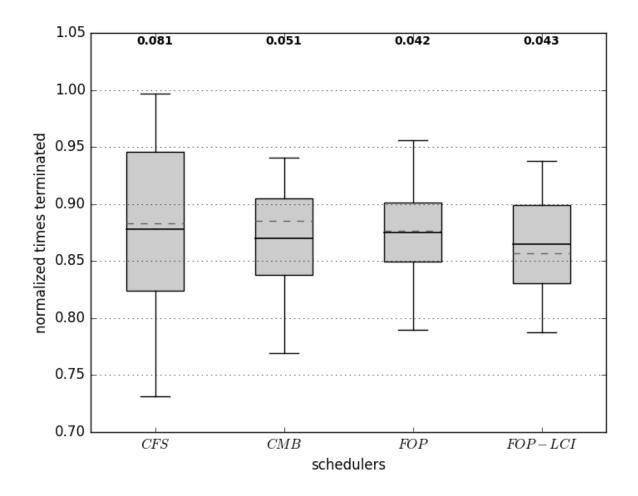

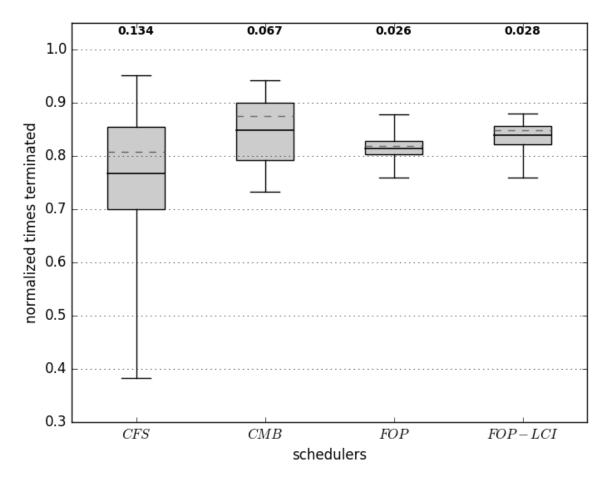

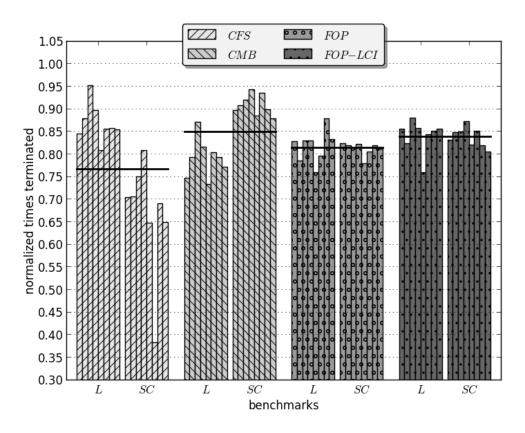

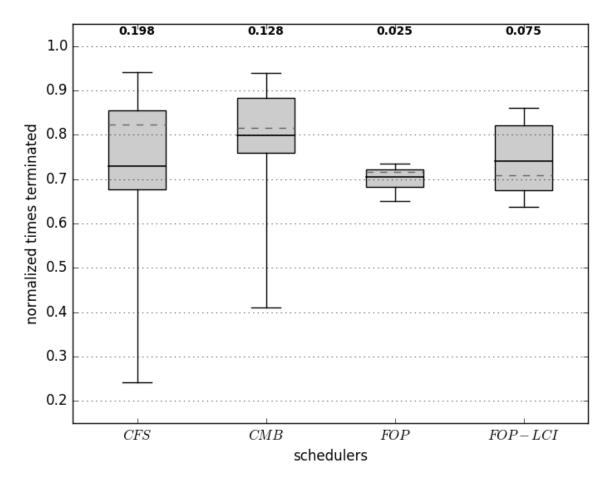

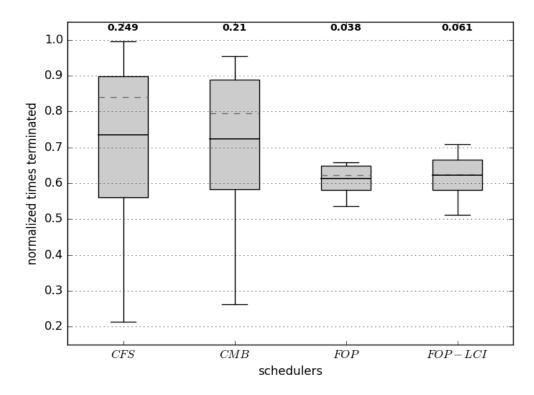

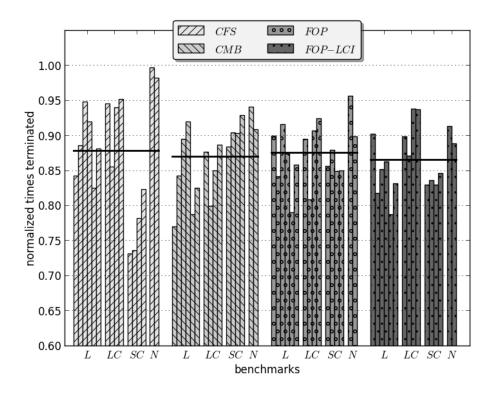

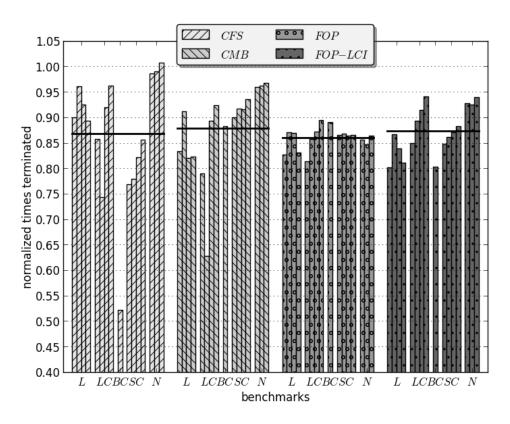

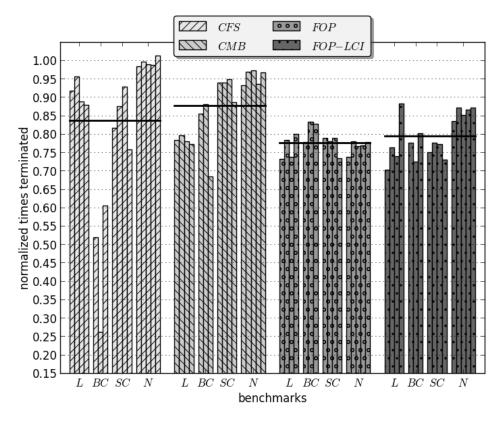

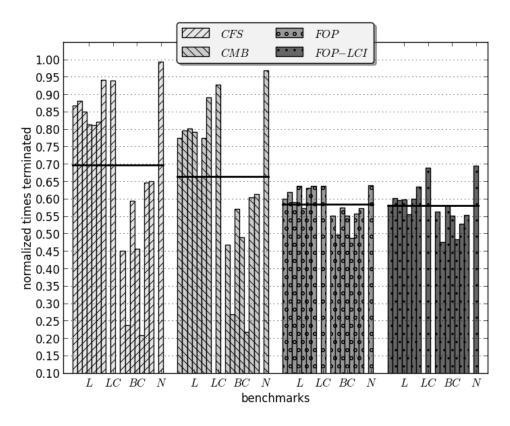

#### Δεύτερη Ομάδα Πειραμάτων

Figure 1.1-16: Φόρτος διεργασιών με 4 L, 3 BC, 4 SC και 5 N διεργασίες

Σε αυτό το φόρτο παρατηρούμε τα εξής. Ο CMB πετυχαίνει το καλύτερο throughput, καθώς καταφέρνει να απομονώσει πλήρως τις BC εφαρμογές στις τετράδες και να αυξήσει σημαντικά την απόδοσή τους, όπως επίσης κάνει και με τις SC. Μειώνει την πρόοδο των L όπως πριν, καθώς τις πακετάρει μαζί. Ο FOP, όπως πριν, έχει την καλύτερη απόδοση ως προς το fairness, ισορροπώντας σχεδόν τέλεια τις εφαρμογές, αλλά μειώνει το throughput, διότι τρέχει συχνότερα εφαρμογές που δεν κάνουν πρόοδο. Ο FOP-LCI φαίνεται, πάλι, να ευνοεί τις Ν εφαρμογές αντί των SC.

Figure 1.1-17: Βελτίωση throughput και fairness σχετικά με το Linux

Στο σχήμα 1.1-17 συγκρίνουμε τις τεχνικές μας με το Linux για τους φόρτους της δεύτερης ομάδας. Καταλήγουμε στα εξής. Ο CMB είναι ικανός να μοιράσει τις BC εφαρμογές και να προσφέρει το καλύτερο throughput. Από την άλλη ο FOP μειώνει ελαφρώς το throughput, αλλά πετυχαίνει το καλύτερο fairness. Ο FOP-LCI βρίσκεται σε μια ενδιάμεση κατάσταση

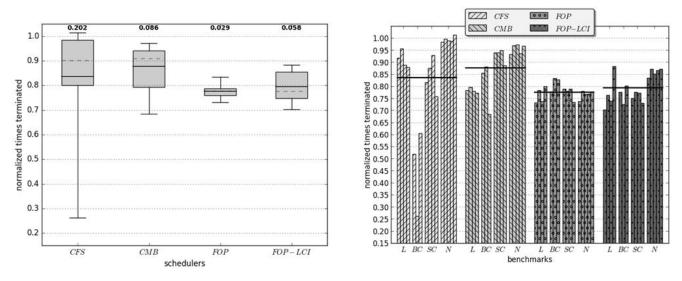

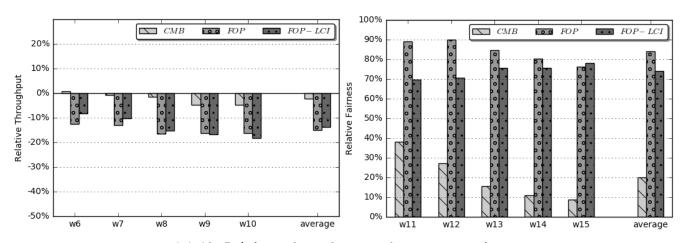

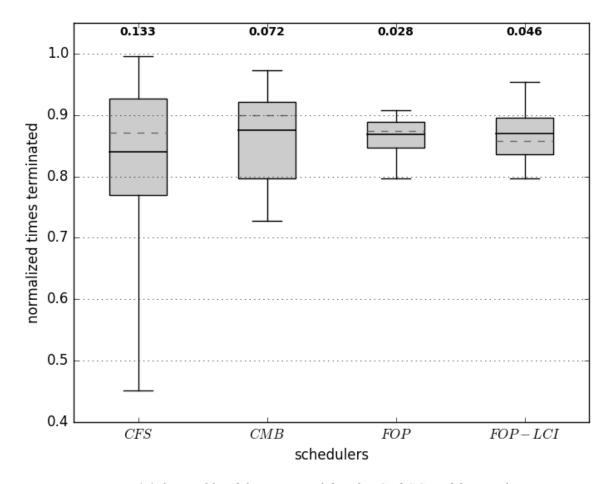

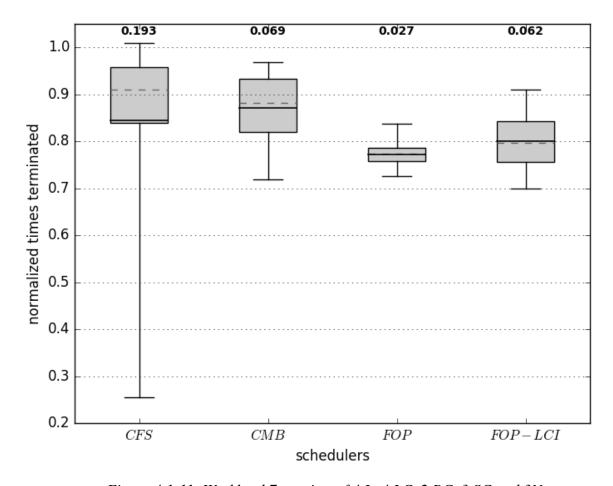

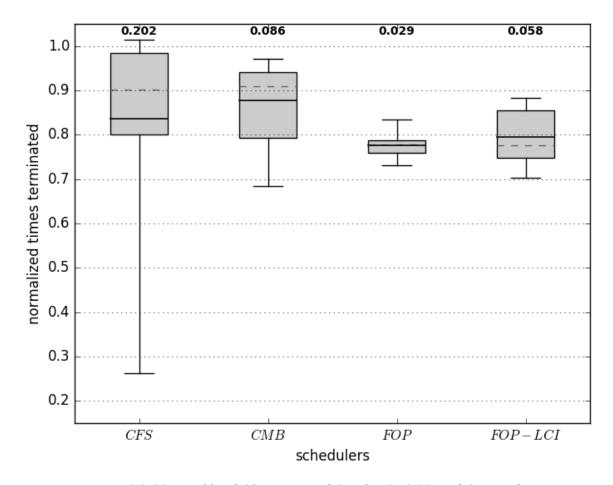

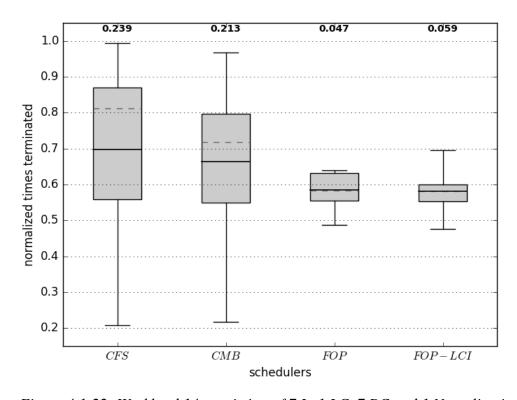

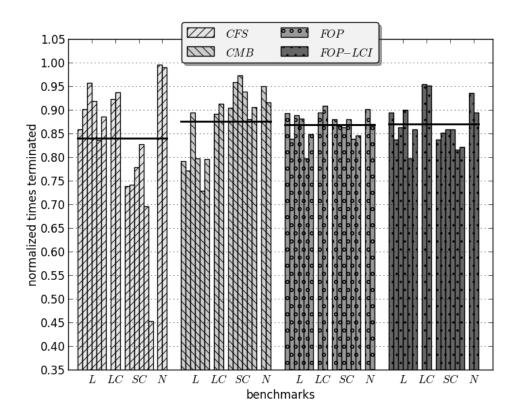

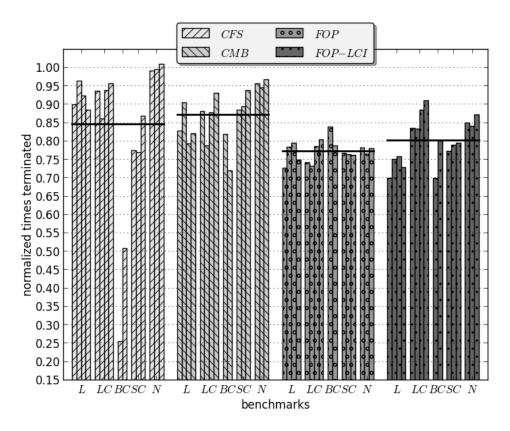

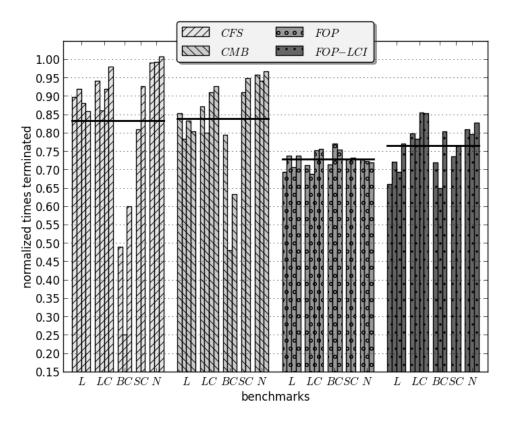

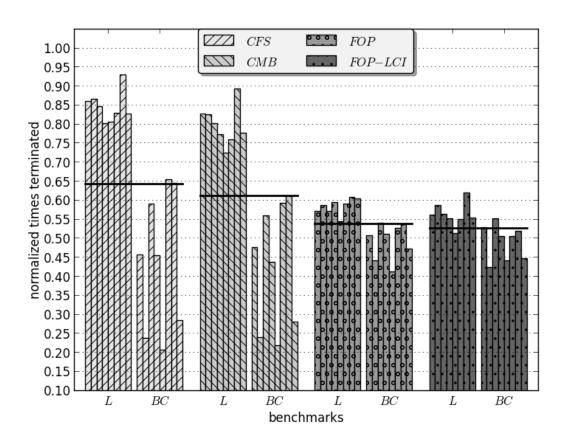

#### Τρίτη Ομάδα Πειραμάτων

Figure 1.1-18: Φόρτος διεργασιών με 6 L, 2 LC, 5 BC, 1 SC και 2 N διεργασίες

Σε αυτή την περίπτωση (σχήμα 1.1-18) καταλαβαίνουμε ότι ο CMB δεν μπορεί να απομονώσει τις BC εφαρμογές και αναγκαστικά τις τρέχει μαζί. Λαμβάνοντας υπόψιν ότι πακετάρει και τις L, αυτό οδηγεί σε ελαφρώς μειωμένη απόδοση συγκριτικά με το Linux. Γενικά ακολουθεί τη συμπεριφορά του Linux. Απο την άλλη, οι άλλες δυο τεχνικές αποδίδουν όπως περιμέναμε, με χαμηλότερο throughput σχετικά με τις άλλες ομάδες πειραμάτων, διότι ο αριθμός των εφαρμογών που δεν εκτελούνται αποδοτικά (BC) είναι αυξημένος.

Figure 1.1-19: Βελτίωση throughput και fairness σχετικά με το Linux

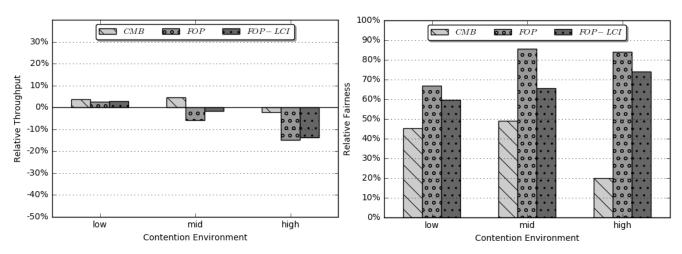

Συγκεντρωτικά για όλους τους φόρτους διεργασιών έχουμε τα εξής. Ο CMB παρουσίαζει την μικρότερη μείωση στο throughput και την μικρότερη αύξηση στο fairness. Οι άλλες δύο τεχνικές έχουν παρόμοια συμπεριφορά, με τον FOP να είναι ελαφρώς χειρότερος στο throughput και ελαφρώς καλύτερος στο fairness από τον FOP-LCI.

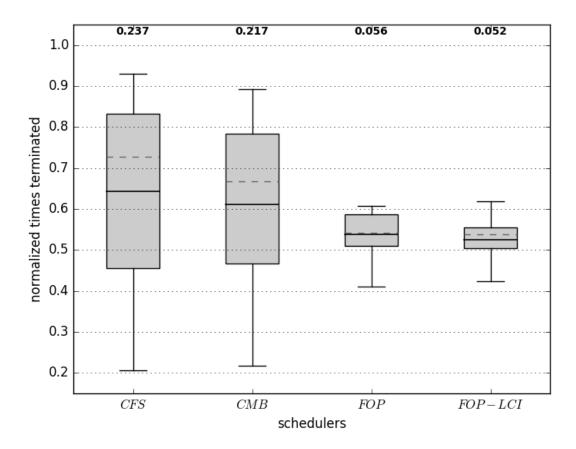

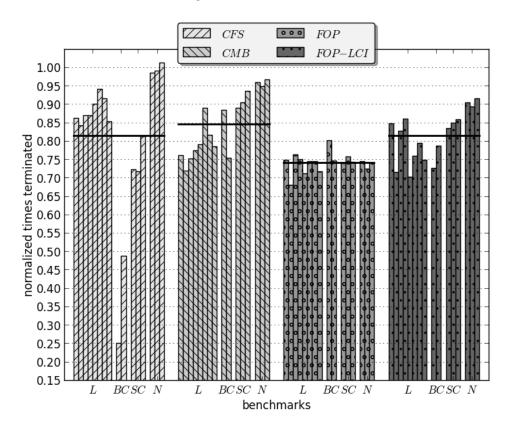

# Κεφάλαιο 4 Συμπεράσματα

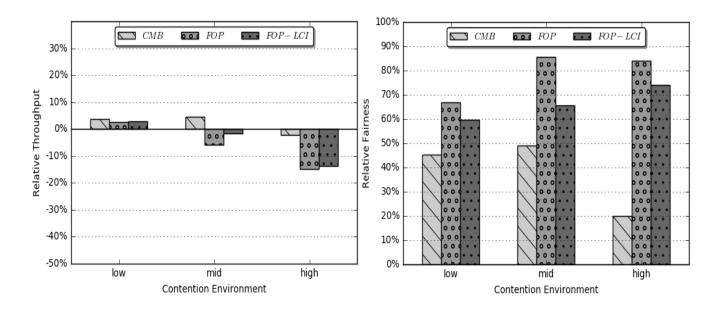

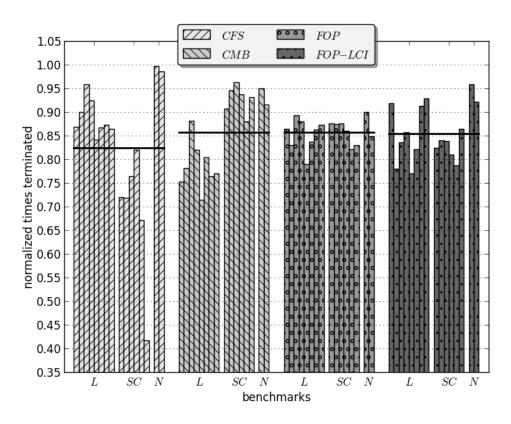

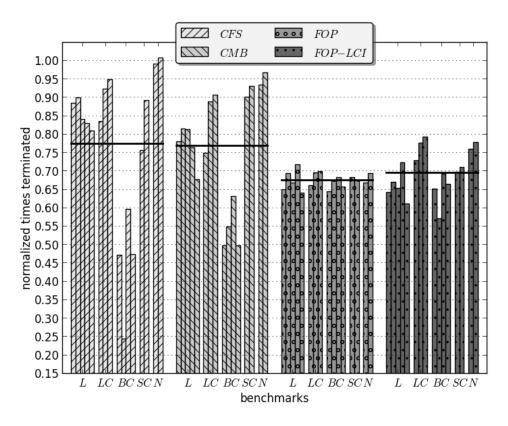

Figure 1.1-20: Βελτίωση throughput και fairness για κάθε ομάδα σχετικά με το Linux

Βλέποντας τα αποτελέσματα της σύγκρισης καταλήγουμε στο εξής. Όλες οι τεχνικές που προτείναμε κατανέμουν πιο δίκαια τους πόρους του συστήματος στις διεργασίες. Εκπληκτικά αποτελέσματα παρουσιάζει η δεύτερη και η τρίτη προσέγγιση καθώς φέρνει σε σχεδόν απόλυτη ισορροπία ην πρόοδο τους. Στην πρώτη προσέγγιση έχουμε τον περιορισμό ότι ο διαχωρισμός των εφαρμογών που υποφέρουν περισσότερο μπορεί να γίνει μόνο χρονικά. Αυτό σημαίνει ότι όταν ο αριθμός τους ξεπεράσει τις πιθανές τετράδες, τότε ο χρονοδρομολογητής μας δεν μπορεί να ανταποκριθεί σε αποδοτική αύξηση throughput και fairness.

Αναφορικά με την μείωση του throughput για τους FOP και FOP-LCI, αυτό συμβαίνει επειδή τον επεξεργαστή κρατάνε απασχολημένο κυρίως διεργασίες που δεν κάνουν πρόοδο. Παρ'όλα αυτά είναι σπουδαίο το αποτέλεσμα που προσφέρουν και αξίζει να θυσιάσουμε throughput ώστε να πετύχουμε σχεδόν την απόλυτη ισορροπία.

Σχετικά με τον FOP-LCI, επιδιώκαμε να αυξήσουμε την πρόοδο των C με την απομόνωση τους. Καταλαβαίνουμε όμως ότι με αυτό το τρόπο, συσσωρεύαμε τις L ή τρέχαμε τις BC μαζί, κάτι που δεν οδηγεί σε καλύτερα αποτελέσματα. Αυτό που παρατηρήσαμε είναι αύξηση του throughput απο την ευνοική εκτέλεση των 'ουδέτερων' εφαρμογών.

Συνοψίζοντας, βλέπουμε ότι οι σύγχρονοι χρονοδρομολογητές δεν λαμβάνουν υπόψιν τους τις ιδιαιτερότητες των πολυπήρνων συστημάτων και δεν παρέχουν σταθερότητα. Οι τεχνικές που προτείναμε μπορούν να εγγυηθούν αξιοπιστία και δικαιοσύνη στην κατανομή των πόρων.

# **Table of Contents**

| 1 | Intro | ductionduction                                                             | 40 |

|---|-------|----------------------------------------------------------------------------|----|

|   | 1.1   | Definition of scheduling                                                   | 40 |

|   | 1.2   | Chip Multiprocessor                                                        | 41 |

|   | 1.3   | Operating System Services                                                  | 42 |

|   | 1.4   | Process Scheduling                                                         | 43 |

|   | 1.5   | The Linux Scheduler                                                        | 44 |

|   | 1.6   | Chapter Description                                                        | 46 |

| 2 | Prob  | lem Definition and Motivation                                              | 48 |

|   | 2.1   | Resource sharing utilization                                               | 48 |

|   | 2.1.  | 1 Constructive behavior of resource sharing                                | 49 |

|   | 2.1.  | 2 Destructive behavior of resource sharing                                 | 49 |

|   | 2.2   | Last Level Cache Contention                                                | 50 |

|   | 2.3   | Memory Bandwidth Contention                                                | 52 |

|   | 2.4   | NUMA Architecture                                                          | 54 |

|   | 2.5   | Motivation                                                                 | 55 |

|   | 2.5.  | 1 Low progress                                                             | 55 |

|   | 2.5.  | 2 Poor fairness                                                            | 57 |

|   | 2.5.  | 3 Co-runner Dependent Performance                                          | 58 |

| 3 | Prop  | osed Scheduling Policies                                                   | 60 |

|   | 3.1   | First approach (Avoiding contention)                                       | 60 |

|   | 3.1.  | 1 CMP architecture and thread placement                                    | 61 |

|   | 3.1.  | 2 Experimental CMP Platform                                                | 63 |

|   | 3.1.  | The Classification Method                                                  | 65 |

|   | 3.1.  | 4 The Prediction Model                                                     | 76 |

|   | 3.1.  | The Decision - CMB (Cache and Memory Bandwidth contention-aware) Scheduler | 79 |

|   | 3.2   | Second Approach (Managing Contention)                                      | 84 |

|   | 3.2.  | 1 Fairness over running time                                               | 84 |

|   | 3.2.  | 2 Fairness over progress                                                   | 86 |

|   | 3.2.  | The FOP (Fairness over Progress) Scheduler                                 | 88 |

|   | 3.3   | Third Approach (Avoiding and Managing Contention)                          | 98 |

|   | 3.3.  | The FOP-LCI (Fairness over Progress with L-C class Isolation) Scheduler    | 98 |

|   | 3.4    | Imp   | lementation tool               | 101 |

|---|--------|-------|--------------------------------|-----|

|   | 3.4.2  | 1     | The scaff                      | 101 |

|   | 3.4.2  | 2     | System tools and mechanisms    | 102 |

| 4 | Expe   | rime  | ntal Evaluation                | 105 |

|   | 4.1    | Eval  | luation of scheduling policies | 108 |

|   | 4.1.3  | 1     | Low contention environment     | 108 |

|   | 4.1.2  | 2     | Medium contention environment  | 116 |

|   | 4.1.3  | 3     | High contention environment    | 124 |

| 5 | Conc   | lusio | n and Future Work              | 132 |

|   | 5.1    | Res   | ults Evaluation                | 132 |

|   | 5.2    | Futu  | ure work                       | 134 |

| 6 | Relat  | ted V | Vork                           | 136 |

| 7 | Biblio | ograp | ohy                            | 140 |

| 8 | Арре   | endix |                                | 143 |

# Chapter 1

## Introduction

## 1.1 Definition of scheduling

Scheduling is a process concerning the decision of allocating resources to tasks. It occurs over given time periods and is responsible for optimizing several objectives [4]. The resources, tasks and objectives vary between different organizations. In the examples below we illustrate the possible forms they may take.

Taking industry for example, we examine a factory that produces paper bags used for dog food or cement. Regardless of the type of bags we want to produce, the process remains the same and follows three stages, the printing, the gluing and the sewing. In each stage, there are machines of different characteristics, which execute different operations at various speeds. So we recognize here that the resources and the tasks coincide with the machines and the clients' orders respectively. The size of the order affects the completion time. In addition, the setup of a machine should be changed when a switch from one type of bag to another occurs. Another thing that should be taken into consideration is the impact a late delivery would have on the relationship between the factory and the clients. For these reasons, it is necessary to schedule the operation of the machines aiming to satisfy some of the following objectives, minimize the penalties a late delivery would impose or minimize the time wasted on different setups.

As far as transportation services are concerned, we examine a terminal at an airport. Each day hundreds of planes arrive to and depart from numerous gates. Some gates have plenty of space and are easily accessible by large planes, while others are in a location where it is difficult for a plane to reach in. Planes follow a certain schedule for their arrival and their departure. However unforeseen circumstances, like bad weather conditions, require changes to the main schedule. When a plane arrives to the airport, it occupies its gate. The arriving passengers disembark, the plane remains at the gate in order to be serviced and the departing passengers are boarded. However the flight could be postponed, because the destination airport could be busy enough to accommodate another plane. On this occasion, the plane may have to remain at the gate for a long period, preventing others from using it. In this example, the gates are the resources and the servicing of planes are the tasks. It is made clear that a scheduling policy should be adopted in order to optimize several objectives. In the first place, we need to assure that the arriving planes would be assigned to an unoccupied gate. Another objective may be the minimization of personnel's work or the minimization of delays.

Scheduling is widely used in information processing environments. In such environments, we recognize the CPUs (Central Processing Units) as the resources and the executable programs (processes) as the tasks. Computing systems provide with the ability of multiprogramming, assigning, in other words, numerous processes in the CPUs in a given time period. The scheduler is responsible for this work. It slices the CPU time into pieces and devotes them to different processes. In that way it assures that all of the processes would take a fraction of the CPU time and that the CPU would not be kept busy by only a few. The

optimization of specific objectives has a great impact on the overall performance of the system. For example, keeping the CPUs busy all the time leads to maximization of throughput or minimizing the waiting time of applications provides with fair distribution of the resources. For these reasons, schedulers are an indispensable part of computing systems and it is essential to make efforts to improve them.

## 1.2 Chip Multiprocessor

Manufacturers adopt a simple rule to improve computer performance. They increase the number of transistors a CPU contain and decrease in parallel their size. In accordance with Moore's law this has caused speeds to climb and prices to fall. The computing industry followed this trend for years. However, it is impossible for transistors to continuously shrink. Despite the fact that transistors grow thinner, manufacturers have to face two critical problems, power usage and heat generation. Even approaches for performance enhancement, like running multiple instructions per thread (ILP) have reached a plateau.

For these reasons, potentials for improvement of the processor performance have been seriously restricted. Chip performance experienced a 60% increase per year in 90s but declined to 40% per year from 2000 to 2004. Apparently designing a chip with 20% speed increase, costing twice the die area would not be ideal for meeting our expectations for performance boost, energy efficiency and cost effectiveness [5].

In response, manufacturers are turning from single-core to multi-core architectures. Instead of one increasingly powerful core, they are building chips with multiple more energy-efficient processing cores. These cores run in lower speeds as compared to the single-core systems but they improve overall performance by executing more processes in parallel. Taking for example a dual-core chip running multiple processes simultaneously, we conclude that it is about 1.5 faster than a chip with just one core.

When a single-core chip runs multiple programs, it assigns a time slice to work on one program and then assigns different time slices for others. This can cause conflicts, errors, or slowdowns when the processor must perform multiple tasks simultaneously. When considering multi-core chips, on the opposite, it is feasible to execute multiple instructions at the same time, increasing overall speed for programs amenable to parallel computing. So if you have multiple tasks that all have to run at the same time, you will see a boost of performance with multi-core processors.

The improvement in performance gained by the use of a multi-core processor depends very much on the software algorithms used and their implementation. In particular, possible gains are limited by the fraction of the software that can be run in parallel simultaneously on multiple cores. Programmers must find good places to break up the applications, divide the work into roughly equal pieces that can run at the same time, and determine the best times for the threads to communicate with one another (thread-level parallelism (TLP)), a work that makes the parallelization of software a significant ongoing topic of research.

Manufacturers typically integrate the cores onto a single integrated circuit die (known as a chip multiprocessor or CMP), or onto multiple dies in a single chip package. Because the chips' cores are on the same die, they can share architectural components, such as memory

elements and memory management. They thus have fewer components and lower costs than systems running multiple chips (SMP). Also, the signaling between cores can be faster and use less electricity than on multichip systems.

The advantages a multi-core processor can offer, mentioned above, made them the dominant in the area of computing systems. Multi-core processors are widely used across many application domains including general-purpose, embedded, network, digital signal processing (DSP), and graphics. Multi-core technology, with its promise of improved power efficiency and increased hardware utilization, has been embraced by the industry: AMD, Fujitsu, IBM, Intel and Sun Microsystems are shipping multicore systems and have announced plans to release future models. Having become mainstream in both server and desktop processors, we expect to see processors with tens and even hundreds of cores on a chip, over the next decade.

## 1.3 Operating System Services

An operating system is a program that manages a computer's hardware. It also provides a basis for application programs and acts as an intermediary between the computer user and the computer hardware.

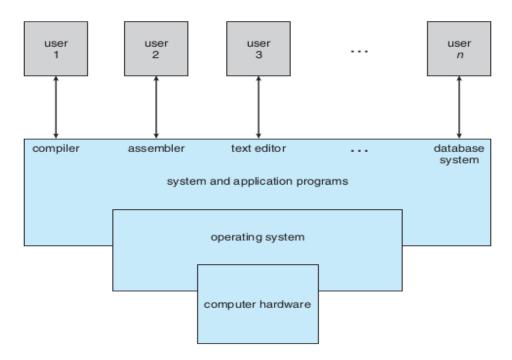

Figure 1.3-1: Abstract view of the components of a computer system

A computer system can be divided roughly into four components: the *hardware*, the *operating system*, the *application programs*, and the *users (Figure 1.3-1)*. The *hardware* consists of the central processing unit (CPU), the memory and the input/output (I/O) devices

and provides the resources for the system. The *application programs*, for example word processors, spreadsheets and browsers, define the ways in which these resources are used to solve *users*' computing problems. The *operating system* controls the hardware and coordinates its use among the various application programs for the various users [6].

The operating system is responsible for process, memory and storage management. Regarding process management, it schedules processes and threads on the CPUs, creates and deletes both user and system processes, suspends and resumes processes and provides mechanisms for process synchronization and communication.

Concerning the memory management, it keeps track of which parts of memory are currently being used and who is using them, decides which processes and data to move into and out of memory and (de)allocate memory space as needed.

Operating system abstracts the physical properties of the storage devices and creates a logical, uniform storage unit, the file. It accesses the storage devices via the files and takes charge of specific operations for managing the file-system. It creates and deletes files or directories, supports mechanisms for their manipulations, and maps files onto storage devices. I

In the case a program needs to communicate with a file or a device, the operating system provides I/O operations. The communication can be achieved via special functions that utilize the devices properly and offer efficiency and protection

Communication between users and their programs should be helpful and convenient. The operating system provides the user interface (UI), in order to make computer interactive. There are many form an interface could take. It may be a command line interface (CLI), which uses text commands. The other and most common form is the graphical user interface (GUI). It consists of a window system with a pointing device and a keyboard.

Protection and security are two aspects that an operating system should take into consideration. User and processes are not allowed to have access to the resources without regulation. Operating systems enforce some controlling mechanism in order to protect the execution of the processes. They ensure that files, memory and CPUs can be utilized by the processes that have gained proper authorization.

Operating systems should offer not only protection but also security. This means that they should be able to defend the system from external and internal attacks. Such attacks may include viruses, identity theft, denial-of-service and theft of service.

## 1.4 Process Scheduling

A process is considered as the task that should be completed in a computing system. A system consists of numerous processes, some of them are operating-system processes, meaning that they execute system code, and the others are user processes, meaning that they execute user code.

CPUs are considered as the main resources of a system. Operating systems assign these resources to the tasks aiming to optimize some objectives. Scheduler is the indispensable part of the operating systems that holds this responsibility. Its main role is to provide with the ability of multiprogramming. CPU cannot be kept busy by a single process all the time. It should be ensured that all processes take a slice of the CPU's time and make progress

However, multiprogramming is not the only reason that makes the scheduler so important. The way it manages the processes has a great impact on the system performance. The extent at which the various objectives are satisfied is reflected on the system, as these objectives consist the criteria for the performance measurement.

The main objectives that a scheduler tries to optimize are the following. First of all we want to maximize the *CPU utilization*, meaning that we try to keep the CPU as busy as possible. In addition we want to maximize the *throughput*, which is the measure of work done. It indicates the processes that are completed per time unit. Furthermore it is desirable to minimize the *turnaround time* of applications. This refers to the interval from the time of submission to the time of completion of a process. *Waiting time* is another criterion we try to minimize. It is the total time that an application spent waiting in the ready queue. We do not want waiting time to be gathered to one application only, but to be equally distributed among them. Another thing we should take into account is the *response time*, which is the time from the submission of a request until the first response is produced. In an interactive system, it is preferable to minimize response time

Regardless of the various scheduling algorithms proposed in order to achieve the optimization of the desirable objectives, the main abstract purpose of the scheduler is analyzed in the meaning of *time-sharing* and *space-sharing* the CPUs. *Time-sharing* the CPU means multiplexing a single processor in time and devotes every time-slice to different process, so that CPU executes multiple processes in a time interval. *Space-sharing* the CPUs is about deciding on which CPU each process chosen to run at a given time interval will be assigned to run.

For single processor architectures the scheduler enforces obviously time-sharing only. OS schedulers for these architectures had become so optimized that need for further improvements dramatically subsided, thereby diminishing interest in this research topic. In the late 90s, the scheduling problem was considered solved; at least it appeared that way until the advent and subsequent near ubiquitous proliferation of chip multiprocessors (CMP).