NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT OF COMPUTER SCIENCE

# Development of Design Methodologies and CAD tools for System-level evaluation of interconnect reliability issues in SoC designs

DIPLOMA THESIS

Christos A. Papameletis

Supervisor: Dimitrios Soudris, Assistant Professor

Athens, July 2010

NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING DEPARTMENT OF COMPUTER SCIENCE

# Development of Design Methodologies and CAD tools for System-level evaluation of interconnect reliability issues in SoC designs

DIPLOMA THESIS

Christos A. Papameletis

Supervisor: Dimitrios Soudris, Assistant Professor

Approved by the tripartite committee on July 13, 2010.

Dimitrios Soudris Assistant Professor Kiamal Pekmestzi Professor George Economakos Lecturer

Athens, July 2010

..... Christos A. Papameletis

Graduate of the N.T.U.A. School of Electrical and Computer Engineering

#### Copyright © Christos Papameletis, 2010

All rights reserved.

This work may not be copied, saved and distributed in whole or in part for commercial purposes. The reproduction and distribution is only allowed for non-profitable, scholarly purposes, under the condition that the original source is referenced and this message is preserved. Questions regarding the use of this work for financial gain are to be addressed to its author.

The opinions and conclusions recorded in this work express the author and they should not be held as official positions of the National Technical University of Athens.

### Abstract

The presented diploma thesis deals with interconnect reliability in VLSI systems from a system-level perspective. The dominant phenomena that are examined are Electromigration (EM) and Time-dependent Dielectric Breakdown (TDDB). The main goal of this work was the creation of a design flow that estimates the system's lifetime (MTTF) because of timing failures caused by the gradual degradation of the electrical characteristics of interconnects. The presented flow is based on a pre-existing work that was developed at IMEC, Belgium. A main feature of the project is the use of actual temperature data for each individual region of the system, which are derived from application-specific simulations. This results in rather accurate lifetime estimations as both reliability-threatening phenomena examined are heavily dependent on temperature. Another improvement that increases the accuracy of the predictions is the estimation of the interconnets' current density through Spice simulations. Other important features are the automation of the design flow as a tool as well as its compatibility with state-of-the-art EDA tools, such as the Cadence SoC Encounter Layout & Timing analysis system and the Synopsys front-end suite.

**Keywords:** << SoC, Electro-migration, Time-dependent dielectric breakdown, reliability, EM, TDDB, soft failure, timing, HotSpot, SoC Encounter >>

### Acknowledgements

I would like to acknowledge Prof. Dimitrios Soudris for assigning me this topic and supervising me in this work. Also, I would like to thank Prof. Kiamal Pekmestzi and Lect. George Economakos for their support in the Microcomputers and Digital Systems Laboratory.

I am particularly grateful to doctorate student Dimitrios Bekiaris for his guidance and the impeccable cooperation we had with each other. The completion of this work would not be possible without his help and technical support. I also am grateful to post-doctorate researcher Antonis Papanikolaou for providing the foundations for this work and for the fruitful discussion I had with him and Dimitrios Bekiaris which included valuable insightful remarks.

Finally, I deeply thank my family and friends for their long-term love and support. They all contributed indirectly to this work, either financially or psychologically.

# **Table of Contents**

| 1 | Intro | oduction                                                    | .17 |

|---|-------|-------------------------------------------------------------|-----|

|   | 1.1   | The importance of reliability                               | .17 |

|   | 1.2   | Reliability-threatening phenomena in general                | .18 |

|   | 1.3   | Motivation for studying interconnect reliability            | .19 |

|   | 1.4   | Choice and description of the examined phenomena            | .19 |

|   | 1.5   | The goals and main idea of the presented flow               | .20 |

|   | 1.6   | The test platforms                                          | .23 |

|   | 1.7   | Chapter outline                                             | .23 |

| 2 | Reli  | ability-threatening phenomena & models                      | .25 |

|   | 2.1   | Electro-migration                                           | .25 |

|   | 2.2   | Time-dependent Dielectric Breakdown                         | .30 |

| 3 | Des   | ign flow methodology                                        | .35 |

|   | 3.1   | Basic concepts                                              | .35 |

|   | 3.2   | Temperature estimation                                      | .38 |

|   | 3.3   | EM flow                                                     | .40 |

|   | 3.4   | TDDB flow                                                   | .42 |

|   | 3.5   | Combined impact methodology                                 | .45 |

| 4 | Des   | ign flow implementation & Automation                        | .47 |

|   | 4.1   | Flow implementation tools and components                    | .47 |

|   | 4.1.  | 1 Temperature estimation (HotSpot)                          | .47 |

|   | 4.1.  | 2 Path extraction and formatting                            | .49 |

|   | 4.1.  | 3 Layout geometric data extraction using Encounter DBAccess | .49 |

|   | 4.1.  | <i>4 Rise &amp; fall transition time estimation</i>         | .53 |

|   | 4.1.  | 5 Prerequisite files generation                             | .55 |

|   | 4.2   | EM flow                                                     | .56 |

|   | 4.2.  | 1 EM extraction script                                      | .56 |

|   | 4.2.  | 2 SPEF update script                                        | .63 |

|   | 4.2.  | 3 EM impact on system's timing                              | .65 |

|   | 4.3   | TDDB flow                                                   | .65 |

|   | 4.3.  | 1 TDDB extraction script                                    | .65 |

|   | 4.3.  | 2 TDDB delay library                                        | .68 |

|   | 4.    | 3.3    | SDF update script                                             | 70  |

|---|-------|--------|---------------------------------------------------------------|-----|

|   | 4.    | 3.4    | TDDB impact on system's timing                                | 72  |

|   | 4.4   | Au     | tomation of the flow                                          | 72  |

|   | 4.    | 4.1    | Summary of flow steps and of implementing scripts             | 72  |

|   | 4.    | 4.2    | Temperature estimation script                                 | 73  |

|   | 4.    | 4.3    | Flow configuration file                                       | 74  |

|   | 4.    | 4.4    | Flow core script                                              | 77  |

|   | 4.5   | Exe    | ecution time of the flow                                      | 78  |

| 5 | D     | esign  | platforms and implementation flows                            | 79  |

|   | 5.1   | Dig    | gital implementation flow of design platforms                 | 79  |

|   | 5.2   | Syı    | nthesis and Physical Implementation flow                      | 80  |

|   | 5.    | 2.1    | The Leon3 design platform                                     | 81  |

|   | 5.    | 2.2    | Synthesis of the Leon3 MP-SoC platform                        | 85  |

|   | 5.    | 2.3    | Physical Implementation of the Leon3 MP-SoC design            | 89  |

|   | 5.3   | Sin    | nulation and Software tools                                   | 100 |

| 6 | Е     | xperin | nental results & conclusions                                  |     |

|   | 6.1   | Ex     | perimental results                                            | 105 |

|   | 6.    | 1.1    | EM results                                                    | 106 |

|   | 6.    | 1.2    | TDDB results                                                  | 110 |

|   | 6.2   | Co     | nclusions, hints for future extensions and proposed solutions | 119 |

|   | 6.    | 2.1    | Conclusions                                                   | 119 |

|   | 6.2.2 |        | Future extensions of the analysis framework                   | 121 |

|   | 6.    | 2.3    | Proposed solutions to mitigate the reliability problems       | 122 |

| 7 | А     | ppend  | ix                                                            | 125 |

| 8 | R     | eferen | ces                                                           | 145 |

# **List of Figures**

| Figure 1.1. Delay rise in the interconnect of Path 2                             | 21    |

|----------------------------------------------------------------------------------|-------|

| Figure 1.2. Impact of delay rise on system's timing                              | 21    |

| Figure 2.1. Wire resistance change over time due to EM                           | 27    |

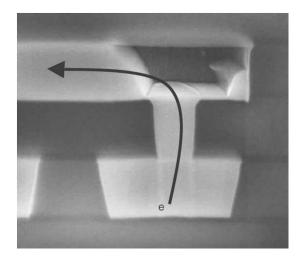

| Figure 2.2. EM-induced void above a via                                          | 27    |

| Figure 2.3. EM-induced extrusion near an adjacent wire.                          | 27    |

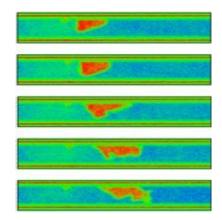

| Figure 2.4. Progressive void formation in a wire over time, due to EM.           | 28    |

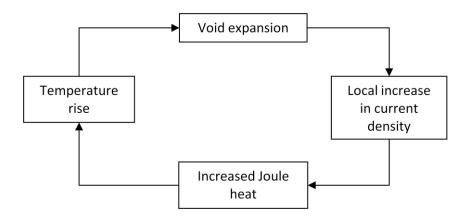

| Figure 2.5. Positive-feedback EM acceleration phenomenon.                        | 28    |

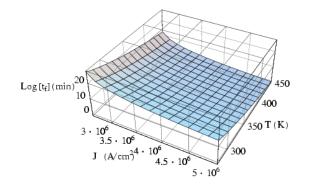

| Figure 2.6. Graphical representation of Black's equation.                        | 29    |

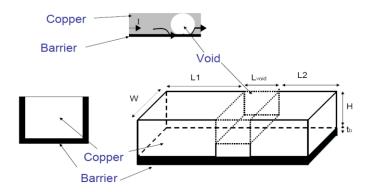

| Figure 2.7. Void demonstration in a copper wire.                                 | 30    |

| Figure 2.8. TDDB-induced leakage between adjacent wires of the same metal lay    | er.31 |

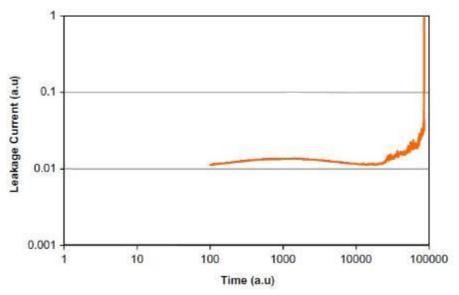

| Figure 2.9. Inter-metal leakage current versus time.                             | 32    |

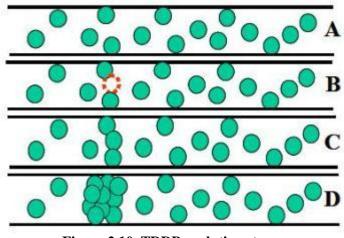

| Figure 2.10. TDDB evolution stages.                                              | 32    |

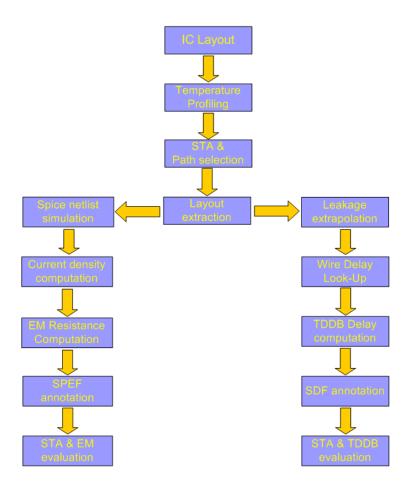

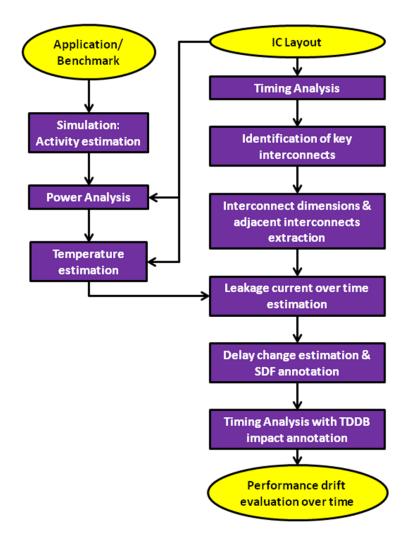

| Figure 3.1. The proposed interconnect reliability framework for EM and TDDB.     | 37    |

| Figure 3.2. The initial reliability analysis framework presented in [1] and [2]  | 38    |

| Figure 3.3. Temperature estimation flow                                          | 39    |

| Figure 3.4. The temperature-aware EM flow                                        | 42    |

| Figure 3.5. Delay impact on a wire due to TDDB, depending on wire length         | n and |

| distance.                                                                        | 44    |

| Figure 3.6. The TDDB flow with the temperature profile's annotation from Hot     | Spot. |

|                                                                                  | 45    |

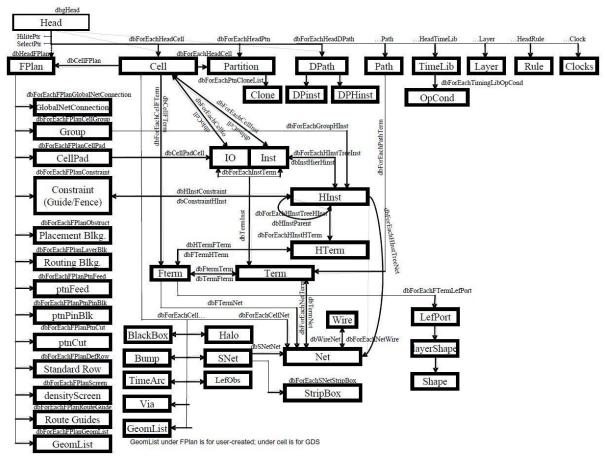

| Figure 4.1: DBAccess objects and commands relating them                          | 52    |

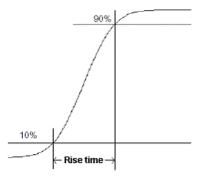

| Figure 4.2. Transition (rise) time, counted from the 10% to the 90% of the final |       |

|                                                                                  |       |

| Figure 4.3. Prerequisite files generation.                                       |       |

| Figure 4.4. Waveform demonstrating the delay shifting of a resistor node's trans |       |

| compared to the transition of the voltage source.                                |       |

| Figure 4.5. EM extraction script steps and results.                              |       |

| Figure 4.6. Adjacent wires - possible locations and filtering.                   |       |

| Figure 4.7. Possible locations of inter-metal adjacent wires.                    |       |

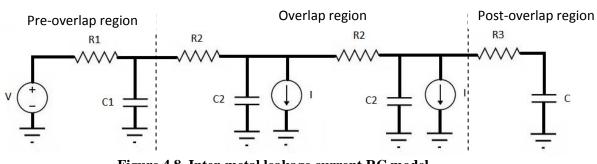

| Figure 4.8. Inter-metal leakage current RC model.                                |       |

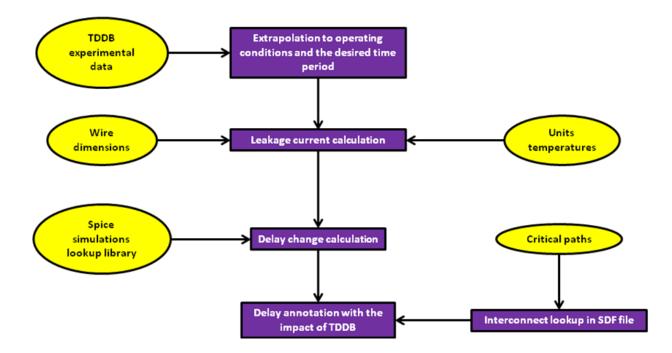

| Figure 4.9. Inter-metal leakage current extrapolation, delay estimation and imp  |       |

| annotation                                                                       |       |

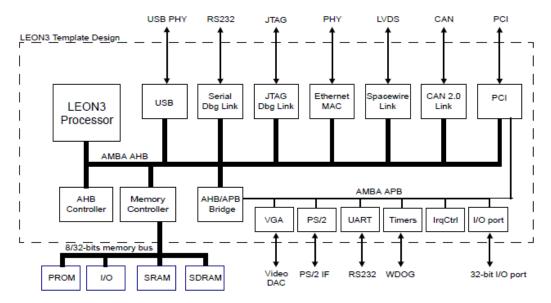

| Figure 5.1.A Leon3-based SoC with the core and peripherals on the AMBA bus.      |       |

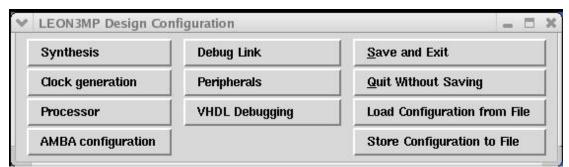

| Figure 5.2. The GUI for the configuration of the Leon3 MP-SoC platform.          |       |

| Figure 5.3. The option pane for the configuration of Leon3 processor.            |       |

| Figure 5.4. The Leon3 Data and Instruction cache configuration screenshot.       |       |

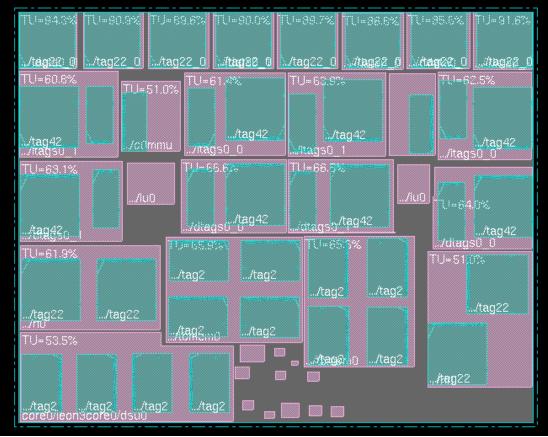

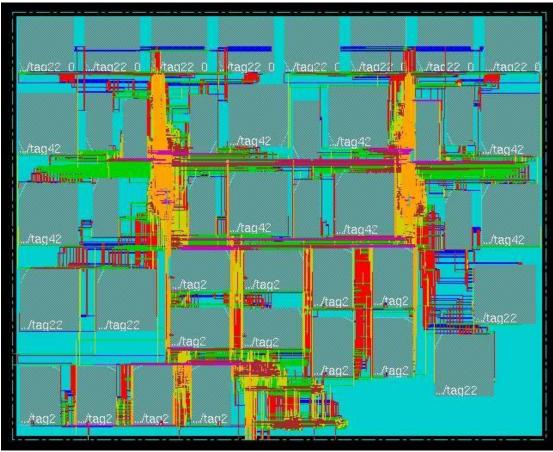

| Figure 5.5. The 2.32x1.85 mm2 Leon3 MP-SoC design's floorplan with two core      |       |

| Figure 5.6. Placement options of Encounter's Qplace placement tool.              |       |

| Figure 5.7. The general option pane of placement modes in Encounter              |       |

| Figure 5.8. The clock-tree synthesis main window in SoC Encounter                |       |

| Figure 5.9. The Nanoroute's main window with the most important options          | 97    |

| Figure 5.10. The timing and congestion optimization slide bar of Nanoroute           |

|--------------------------------------------------------------------------------------|

| Figure 5.11. The design's layout with timing-driven placement and normal routing. 99 |

| Figure 5.12. A simulation waveform sample of the design in ModelSim102               |

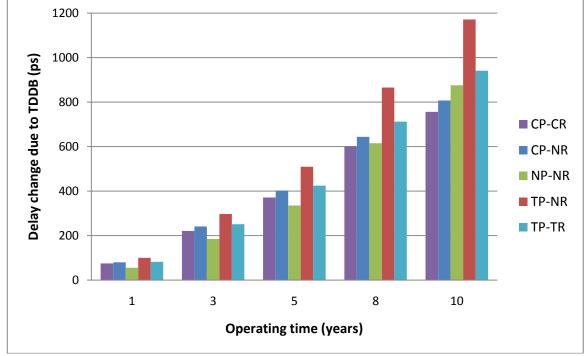

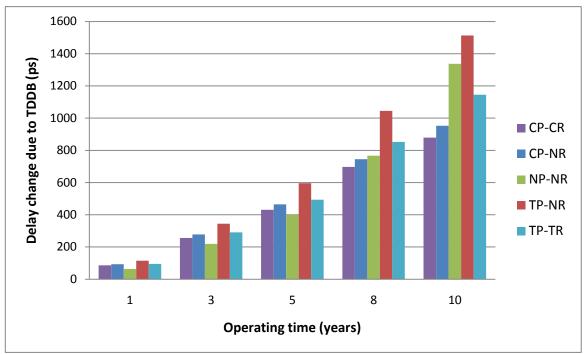

| Figure 6.1. Progressive impact of TDDB on timing (standard thermal conditions)113    |

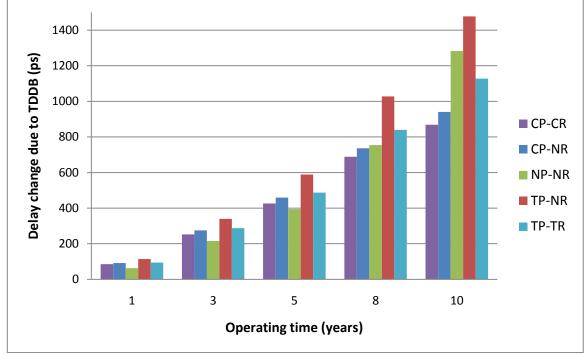

| Figure 6.2. Progressive impact of TDDB on timing (100°C constant and uniform). 116   |

| Figure 6.3. Delay impact on a wire due to TDDB, depending on temperature and         |

| operation time                                                                       |

| Figure 6.4. Progressive impact of TDDB on timing (military thermal conditions)119    |

# **List of Tables**

| Table 1.1. Feature comparison table between past and proposed version of the flow.22 |

|--------------------------------------------------------------------------------------|

| Table 4.1. Approximate execution time of the flow's core components for 50 paths. 78 |

| Table 6.1. NP-NR, standard thermal conditions                                        |

| Table 6.2. NP-NR, 100°C constant and uniform                                         |

| Table 6.3. NP-NR, military thermal conditions.    107                                |

| Table 6.4. CP-NR, standard thermal conditions.    107                                |

| Table 6.5. CP-NR, 100°C constant and uniform                                         |

| Table 6.6. CP-NR, military thermal conditions.    107                                |

| Table 6.7. CP-CR, standard thermal conditions.    108                                |

| Table 6.8. CP-CR, 100°C constant and uniform                                         |

| Table 6.9. CP-CR, military thermal conditions.    108                                |

| Table 6.10. TP-NR, standard thermal conditions.    109                               |

| Table 6.11. TP-NR, 100°C constant and uniform                                        |

| Table 6.12. TP-NR, military thermal conditions.    109                               |

| Table 6.13. TP-TR, standard thermal conditions.    109                               |

| Table 6.14. TP-TR, 100°C constant and uniform                                        |

| Table 6.15. TP-TR, military thermal conditions                                       |

| Table 6.16. CP-NR, standard thermal conditions.    111                               |

| Table 6.17. TP-NR, standard thermal conditions.    112                               |

| Table 6.18. NP-NR, standard thermal conditions.    112                               |

| Table 6.19. CP-CR, standard thermal conditions.    112                               |

| Table 6.20. TP-TR, standard thermal conditions.    113                               |

| Table 6.21. CP-NR, 100°C constant and uniform                                        |

| Table 6.22. TP-NR, 100°C constant and uniform.115                                    |

| Table 6.23. NP-NR, 100°C constant and uniform.115                                    |

| Table 6.24. CP-CR, 100°C constant and uniform.115                                    |

| Table 6.25. TP-TR, 100°C constant and uniform.116                                    |

| Table 6.26. CP-NR, military thermal conditions.    117                               |

| Table 6.27. TP-NR, military thermal conditions.    117                               |

| Table 6.28. NP-NR, military thermal conditions.    118                               |

| Table 6.29. CP-CR, military thermal conditions.    118                               |

| Table 6.30. TP-TR, military thermal conditions.    118                               |

|                                                                                      |

# 1

### Introduction

#### 1.1 The importance of reliability

The reliability of CMOS devices and interconnect structures has always been a great concern for their designers, as the desired lifetime of products should be guaranteed at the design and manufacturing phases, before entering the market. Reliable operation becomes even more important when human lives depend on the system.

This is also the case for VLSI systems used in embedded devices, as several of their applications include potentially life-critical situations, such as in cars or airplanes, as well as in medical devices. But even if no lives depend on them, the products' reliable operation for the desired lifetime and under the desired operational specifications is critical for both the producer and the consumer.

However, the trend of CMOS process scaling, which is likely to be continued towards sub-90nm technology nodes, reveals novel reliability phenomena, which affect the system's functionality either abruptly or progressively, leading to functional or parametric failures respectively. In this thesis, we focus on parametric or "soft" failures of two dominant interconnect reliability phenomena, namely of Electromigration and Time-Dependent Dielectric Breakdown, in a sub-micron technology context. However, the developed design flow presented in this work could estimate the impact of other phenomena with progressive impact on a system's timing behavior, presented in the following section, as well.

#### 1.2 Reliability-threatening phenomena in general

The most common and dominant reliability-threatening phenomena are the following:

- <u>Electro-migration (EM)</u>: EM is the transport of material caused by the gradual movement of the ions in a conductor due to the momentum transfer between conducting electrons and diffusing metal atoms. EM may progressively, and depending on the system's operation, lead to the destruction of the wire, as mass transfer caused by electrons eventually causes discontinuities in the wires by transporting also atoms of copper from the anode to the cathode, forming large voids at one end (anode) and extrusions at the other end (cathode). The underlying effect acts like a wear-out mechanism that affects the interconnects of digital and analog ICs and its impact gains in significance with CMOS technology scaling.

- <u>Time-Dependent Dielectric Breakdown (TDDB)</u>: TDDB is a progressive failure mechanism in device and interconnect structures where a capacitor is formed, leading to the gradual breakdown of the dielectric material as a result of long-time application of relatively low electric field (in contradiction to immediate breakdown, which is caused by strong electric field). The breakdown is caused by the gradual formation of conducting paths through the dielectric material eventually resulting in a short-circuit.

- <u>Hot Carrier Injection (HCI)</u>: HCI is the phenomenon in semiconductor electronic devices, where either an electron or a hole gains sufficient kinetic energy to overcome a potential barrier between different areas of the device and migrates from one area to another. The kinetic energy of microscopic particles is directly related to the temperature of the matter they constitute, so the higher the temperature, the higher the kinetic energy of the particles, hence the word hot. The injection of these high-energy carriers damages the dielectric material, gradually increasing its chance of failure.

- <u>Negative Bias Temperature Instability (NBTI)</u>: NBTI is a reliability issue of immediate concern in pMOS devices, stressed with negative gate voltages. NBTI manifests as an increase in the threshold voltage and consequent decrease in the drain current and transconductance, which can render a transistor useless.

From a device-component view, reliability issues in VLSI circuits can be divided in two categories, namely device-related and interconnect-related. As the size and complexity of ICs increase, the number of wires for the interconnection of the transistors in an IC grows very rapidly. So, the high ratio of interconnects in conjunction with newer fabrication technologies, shifts the attention greatly towards interconnect reliability. Newer fabrication technologies shrink the dimensions of ICs in order to make them faster and cheaper, while they also introduce new materials, such as low- $\kappa$  dielectrics, that make systems faster by reducing parasitic capacitances. However, these porous materials feature poorer electrical characteristics and are more vulnerable, thus making systems less reliable.

#### **1.3** Motivation for studying interconnect reliability

Reliability-aware design enables the location of vulnerable areas and components of the system and their re-design by certain criteria and techniques until the required specifications are met. As a result, ICs can function correctly for longer times and remain as unaffected as possible by random failures or fabrication defects. For most applications, the minimum target lifetime for individual transistors and interconnects is 10 years of continuous activity.

However, standards are not present solely for reliability, but also for yield, fabrication cost, area, power, performance and other parameters. Usually, these factors are connected to each other and influence each other negatively. This makes the tradeoff decisions very crucial as achieving the desired delicate balance is very hard. For instance, a higher performance standard for the system could lead to the upscaling of supply voltage, which in turn leads to increased currents, temperature and other parameters which shorten the IC's lifetime. Likewise, if a lower performance standard is set, the lifetime of the IC will rise, leading to a more reliable system.

Nevertheless, there is another reason because of which lower performance standards are likely to lead to increased reliability. This reason will be illustrated by an example. Newer fabrication technologies result in a transition from abrupt, hard failure mechanisms to gradual, soft failure mechanisms. Suppose there is an interconnect where EM starts to affect its internal structure by forming voids. At some point, a void in the wire is created because of the metal atom transfer. Electrical current still flows, but there is a significant rise in the wire's electrical resistance, resulting in increased delay for the interconnect.

The same principle can be applied to an interconnect where TDDB occurs. Before the dielectric leakage current flowing through the conductive path becomes large enough to cause a short circuit, the transition time of the interconnect rises because of it. Now, this rise in delay might cause a tightly timed, low slack system to stop functioning correctly because the delay in some register-to-register paths might exceed the clock period. If the system's clock and in general the design's timing constraints allowed for a higher slack, this delay increment might not influence the system, unless a hard failure occurs due to high peak currents leading to hotspots or disrupting the structure of certain, vulnerable wires due to metal atom transfer because of extremely high current density.

#### 1.4 Choice and description of the examined phenomena

In this work and tool flow only two reliability-threatening phenomena are examined, EM and TDDB as they have application in interconnect reliability and according to recent research these phenomena seem to dominate the reliability of newer technologies beyond the 90nm node. Actually, EM starts to gain in significance as manufacturing technology dimensions shrink – especially past the submicron node – as this raises the current density that greatly influences the intensity of the phenomenon. To be more precise, the scaling of a circuit's dimensions by a factor k, increases the power density proportionally to k and the current density increases by  $k^2$ . TDDB also becomes increasingly important because of the reduction of the inter-layer distance between adjacent wires, due to CMOS technology scaling, which comes

together with the introduction of low- $\kappa$  dielectric materials, leading to a rise in the inter-metal electric field and accelerating the breakdown process, as the porous nature of low- $\kappa$  dielectrics leads to the easier establishment of conducting paths, thus making them more susceptible to TDDB.

#### 1.5 The goals and main idea of the presented flow

The main goal of the presented work has been the incorporation of a realistic temperature profile in the calculation of the reliability models' parameters. This is important, because both phenomena presented above exhibit exponential dependence on temperature as the models presented in the next chapter show. Therefore, the use of imprecise temperature data can lead to either too optimistic or too pessimistic predictions regarding the lifetime of a system. In order to overcome this problem, a solution is proposed, involving the estimation of the temperature of each individual hierarchical unit on an architecture level, depending on its application-specific power consumption and its floorplan. This also introduces a further criterion for reliability-critical region location, namely that of high temperature, because of its exponential effect on reliability phenomena.

But still, the accurate estimation of temperature and consequently of the lifetime and degradation parameters of interconnects would not be of much significance, if there was no way to project the impact of these results on the system's timing. A methodology to interpret the quantitative effect of resistance rise in wires due to EM or leakage current rise in interconnects due to TDDB on system timing allows the exploitation of the results of predictive models in a tool, to assist reliability-aware design of systems. In other words, a methodology is presented in this work that allows the estimation of the degradation of a system's performance due to the gradual degradation of the electrical characteristics of its interconnects, caused by various reliability-threatening phenomena. Such a transition is important and has a lot of applications, some of which are mentioned below:

- It enhances the understanding of the designer as far as reliability is concerned, providing him with more information regarding the gradual impact of time on his design, thus enabling him to make a more effective tradeoff between performance and reliability.

- Through a set of incremental simulations over increasing time periods of circuit operation, the gradual reduction of the system's timing slack can be depicted in a diagram, giving a more detailed picture of the evolution of the phenomena, as the operating time progresses.

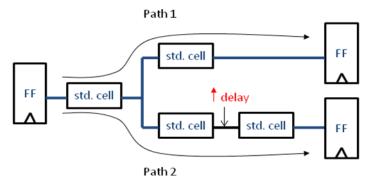

The concept of moving from the electrical and process characteristics' degradation of wires to the estimation of the system's performance drift over time due to the progressive impact of such degradation on the design's timing is explained graphically in Figure 1.2, which is the timing diagram of the register-to-register paths of Figure 1.1.

Figure 1.1. Delay rise in the interconnect of Path 2.

Figure 1.2. Impact of delay rise on system's timing.

If, as stated above, the system was loosely timed and left a larger slack, the delay rise in path 2 in the above example would not lead to the violation of the set timing constraint (clock period), as the output data of Path 2 would be produced before the beginning of the next clock cycle. Hence, the delay tolerance of a design due to the timing impact of such reliability phenomena is strongly dependent on its performance requirements.

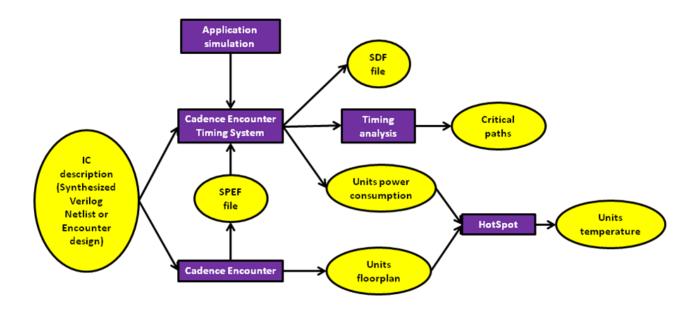

The transition described above is realized through an automated tool flow. This is based on state-of-the-art EDA tools such as the Cadence SoC Encounter physical implementation tool suite [22] and the Encounter Static Timing Analysis (Encounter Timing System-ETS) [19] engine. Standardized file formats such as the SPEF and the SDF are used as carriers of the effects of the reliability phenomena examined, as they include information that are important for the estimation of the system's timing. Therefore, either the SPEF or the SDF file of the target design should be read before any timing analysis, through which the design's performance is estimated.

Hence, the computations of the EM model regarding the resistance rise of the affected wires should be incorporated into the design's parasitic information file, so that the timing impact of the underlying wear-out is evaluated. In order to assess the impact of EM, the current density in each wire is first estimated. Next, the wires that are affected by EM are identified and using a model, their expected resistance rise over time is calculated. Finally, this resistance rise is incorporated in the design's SPEF file and the corresponding SDF file is also generated, based on the SPEF's parasitics, which are used for the required delay computations.

On the other hand, in order to assess the impact of TDDB, adjacent wires are located and the leakage current through the dielectric is estimated by performing extrapolation from stress to operating conditions, based on look-up table libraries of inter-metal leakage. The corresponding delay increment because of this leakage is computed by linear interpolation between the wire patterns of a constructed look-up table library and those extracted from the layout. The aforementioned library is constructed in order to estimate the delay increment of wires due to TDDB. Then, the increased delay of charging the wires of the examined interconnects is computed for each interconnect and it is incorporated into the design's SDF file. It should be noted that, the TDDB requires a different approach of annotating the induced delay compared to the EM, as there is no certain electrical characteristic directly affected and. So, the conducting paths through the dielectric are emulated by progressively increasing the delay of charging wires affected by TDDB, after a certain number of operating years. Although the most accurate method for the computation of the intermetal dielectric leakage is through Spice simulations using distributed RC models, this is a time-consuming solution. In order to overcome this obstacle, a Spice-based wire characterization library including the delay of adjacent wires due to TDDB is constructed instead and look-ups combined with interpolations are used to estimate the delay rise of the layout's real wire patterns. The computed delay increment for each wire of the examined net that belongs to a certain register-to-register path is annotated to the design's SDF file.

The comparison of the timing analysis reports based on the initial SDF file and each one of the other two SDFs, namely after the EM and TDDB models' computation and annotation, will reveal the impact of each phenomenon on the system's timing, considering a certain number of operating years. Also, assuming that the two phenomena are independent, if the delay overhead due to TDDB is annotated on the SDF file produced after the annotation of the EM impact, the resulting SDF file will reflect the combined impact of both phenomena. In order to make the model predictions much more accurate, an application-based power and then temperature estimation is performed, before the core of the interconnect reliability flow is executed.

The encapsulation of the design's temperature distribution across the layout comprises the main contribution of this work, as previous interconnect reliability frameworks [1][2] do not consider realistic temperature traces. However, apart from the temperature profiling, significant additions, corrections and improvements have been made to the initial framework of [1][2] during this thesis. These novel features, introduced by this work, are summarized in Table 1.1, shown below.

| Feature                           | Proposed version | Past version [1][2] |

|-----------------------------------|------------------|---------------------|

| Temperature-aware lifetime        |                  | ~                   |

| estimation                        | <b>V</b>         | •                   |

| Accurate current density          |                  | ~                   |

| calculation (through Spice)       | ×                | *                   |

| Accurate transition time          |                  |                     |

| computation (through EDA tool)    | ×                | *                   |

| Accurate look-up of TDDB-         |                  |                     |

| induced delay                     | ×                | *                   |

| Simultaneous analysis of multiple |                  |                     |

| paths                             | ×                | ×                   |

| Automated tool                    | ×                | ×                   |

| Combined EM&TDDB timing           |                  |                     |

| impact estimation                 | ×                | *                   |

Table 1.1. Feature comparison table between past and proposed version of the flow.

#### **1.6** The test platforms

The reliability tool flow has been tested using several designs, which are the testbenches, from which the wires of nets in the examined register-to-register timing paths are extracted. In order to thoroughly test our approach, we used several place&route scenarios, so that their impact on the evolution of the underlying phenomena can be explored. These scenarios were applied to an embedded Multi-processor System-on-Chip platform based on two LEON3 SPARC processors. The aforementioned design, implemented based on an Application-Specific Integrated Circuit (ASIC) flow with a 45nm standard-cell library, is large and complex enough and the implementing technology used is state-of-the-art, so that the impact of the examined interconnect wear-out mechanisms is significant enough. Especially the LEON3 design features buses with long wires, as well as computational-intensive ALUs, which may include timing paths with strict timing constraints and also long nets with wires susceptible to EM.

#### 1.7 Chapter outline

An overview of the chapters that follow is presented in this section, which can act as a guide to the reader. In Chapter 2, the examined reliability-threatening phenomena, as well as their models, are described. Chapter 3 provides a generic, high-level description of the presented reliability analysis flow in the form of steps, so that the reader can develop a general understanding of the origin of the data required at each step in order to calculate the desired parameters. The 4<sup>th</sup> Chapter elaborates further on the flow by getting a step closer to its implementation, describing the technical details of the individual scripts that comprise it. The physical designs (layouts) that were used as testbenches, together with the tools that generated them and their configuration details, are described in Chapter 5. In the first sections of Chapter 6 the produced experimental results and the conclusions derived from them are presented, whereas the next sections deal with the potential future extensions regarding the reliability analysis framework and attempt to provide solutions that could potentially mitigate the impact of the examined wear-out mechanisms. The 7<sup>th</sup> Chapter is the Appendix, where the code of the various developed scripts is listed, so that it is possible to delve deeper into the flow's implementation.

# 2

# Reliability-threatening phenomena &

models

#### 2.1 Electro-migration

Electro-migration (EM) is a physical phenomenon that may lead to major reliability problems regarding the structure and the electrical characteristics of copperbased interconnects, which are used in most modern VLSI systems. However, EM in general occurs when electrical current flows through a metal conductor and causes some metal atoms to drift along the wire due to momentum transfer from the electrons (electron wind). The transport of atoms progressively leads to the formation of voids, specifically near one end of the wire (anode). Because of the gradual void formation, the internal structure of the affected wire is not coherent any longer, as areas of void intercept those of copper. As the current cannot pass through voids, it has to come along the copper wire's barrier, which causes a significant increase in the time required for the current to pass through. Consequently, the progressive formation of voids due to EM leads to a gradual resistance rise of the wire, which in turn inserts a delay overhead to the signal's propagation. In recent years, research towards EM was focused mainly on the lines of the power and ground network, which may suffer from high voltage drop when the underlying phenomenon starts to develop.

Regarding data signals, EM has started to gain in significance as the geometric dimensions of interconnects tend to shrink, following the trend of CMOS technology scaling down to the nanometer regime. Technology scaling reduces the width and thickness of metal interconnects and consequently their cross-section area, as well as the wire pitch and spacing, while the operating voltage saturates around 1V in state-of-the-art deep sub-micron CMOS technologies. Therefore, the stressing of wires becomes more intense, as the current density tends to be increasing with scaling. Precisely, the scaling of a circuit's dimensions by a factor k, increases the power density proportionally to k and the current density increases by  $k^2$ . The dominant mechanisms that cause a circuit to malfunction due to the momentum metal atoms drift, caused by EM, are the following:

- The formation of voids along interconnects because of the displacement of material from some spots, leading to a resistance rise.

- The formation of extrusions near the anode because of material accumulation there, leading to higher risk of adjacent wire shorting.

The formation of a void usually starts from a spot of the wire, where some sort of defect in the crystal grid exists. The later results in higher collision rate between electrons and metal atoms and eventually to higher momentum transfer between them. At some point atoms detach from the grid and move. Then, because of the electrical forces that appear along the void in conjunction with the weakening of that spot's structure, the void begins to expand. Gradually, the void tends to occupy larger portions of the wire's width and height, reducing the conductor's cross-section at that spot.

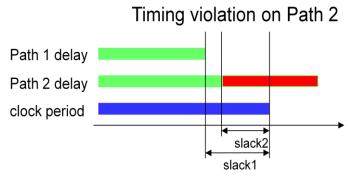

Such a phenomenon is located along a limited length of the wire, so the effect on its resistance is negligible. But at some time, the void fully occupies the crosssection of the wire. At that spot, the current is forced to flow through the diffusion barrier, which has much higher resistance than the metal conductor, due to its low conductivity and cross section. As a result, the wire resistance abruptly rises by several hundred Ohms (resistance step). Since then, strong electrical forces appear between the ends of the void which act as an anode and cathode respectively. Consequently, the void expands further along the length of the wire increasing the wire's resistance at an approximately linear rate (resistance slope).

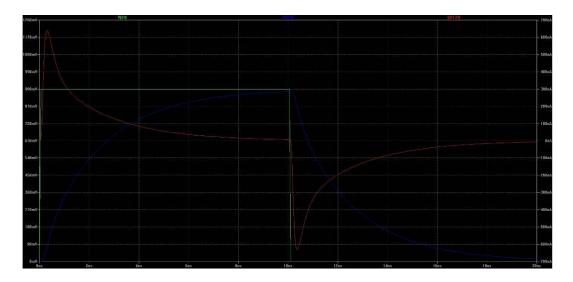

In the following graph, the stages of the resistance step and slope as EM progresses are demonstrated clearly:

Figure 2.1. Wire resistance change over time due to EM.

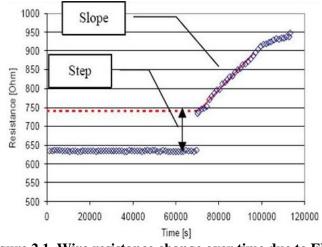

While a void forms at some spot in the wire, detached metal atoms are carried away by electrical forces and accumulate near the anode, forming extrusions through their diffusion in the dielectric material that surrounds the wire. If an adjacent wire exists in a close distance to the first one, it is possible that a short circuit between these two wires is created. Even if the material transferred is not adequate to reach the adjacent wire, the decreased distance enhances the electric field locally, thus making the dielectric material breakdown easier. The following electronic microscope photos illustrate EM- induced voids and extrusions, respectively.

Figure 2.2. EM-induced void above a via.

Figure 2.3. EM-induced extrusion near an adjacent wire.

Figure 2.4. Progressive void formation in a wire over time, due to EM.

Because of the thermal nature of the process of EM, temperature is a critical parameter for the underlying wear-out's development, influencing the evolution of the phenomenon exponentially, by both accelerating it and amplifying its results, as it will be shown in the mathematical formulation given below. The positive feedback loop observed in the figure below, demonstrates how the temperature dependence acts on the void's nucleation and expansion, consequently increasing the wire's resistance.

Figure 2.5. Positive-feedback EM acceleration phenomenon.

However, EM only occurs in wires whose length exceeds the Blech length, for a given value of current density. This sets the lower limit of length and density, below which a mechanical stress buildup causes a reversed migration process, which reduces or even compensates the effective material flow towards the anode. The upper limit of the critical product of current density and wire length has been determined to be 3700 A/cm, by conducting extensive experiments. For a given density of current flowing though a wire, the Blech length can then be easily calculated by performing a single division. In conclusion, only wires which are longer than  $\frac{jL_{critical}}{j_{normal}}$  are affected by EM.

Additionally, wires conducting DC current are more susceptible to EM than those conducting AC current. In the case of the later, the bidirectional electron flow is considered to have healing effects, counterbalancing the mass transfer caused by EM. Due to the lack of experimental data and therefore of a model for AC current driven EM, the equivalent DC current is estimated as the absolute difference of rise and fall current and a DC current driven EM model is used to calculate the results of EM.

Due to the relatively high lifetime of interconnects despite the influence of EM, it is impractical to characterize EM under operating conditions as this would require year-long experiments. A semi-empirical mathematical equation, Black's equation, is commonly used instead to predict the lifetime of interconnects in VLSI circuits, based on experiments conducted under stress conditions of high temperature and voltage. The model's results can then be extrapolated to operating conditions to estimate the expected lifetime as common practice suggests. This method is widely accepted as it is known to provide accurate predictions.

Black's equation estimates the mean time to failure (MTTF) of a wire, that is the time until the resistance step rise occurs, using experimental data as:

$$t_{50,stress} = \frac{A}{J^n} e^{\frac{E_a}{kT}} \quad (2.1)$$

, where A is a constant, n is the current density exponent factor (ranging between 1 and 2, depending on the technology of implementation),  $E_a$  is the activation energy in Joule, depending on the metal of the conductor, J is the wire's current density, k is the Boltzmann constant and T is the temperature in Kelvin. The first three of the aforementioned parameters are derived from experimental data. The following graph displays Black's equation for a given set of these parameters:

Figure 2.6. Graphical representation of Black's equation.

In order to extrapolate the lifetime to operating conditions the following statistical equation is used:

$$t_{50,normal} = t_{50,stress} \cdot \left(\frac{J_{stress}}{J_{normal}}\right)^n e^{\frac{E_a}{k} \cdot \left(\frac{1}{T_{normal}} - \frac{1}{T_{stress}}\right)} \quad (2.2)$$

, where the indexes stress and normal are used to denote the conditions each variable refers to. Another equation is then used to estimate the wire's resistance rise rate after  $t_{50}$ , as:

$$R_{slope,stress} = A \cdot J \cdot e^{-\frac{E_a}{kT}} \quad (2.3)$$

, where all symbols have the same meaning as before. Using the same statistical method to extrapolate to operating conditions, the following equation is obtained:

$$R_{slope,normal} = R_{slope,stress} \cdot \frac{J_{normal}}{J_{stress}} \cdot e^{\frac{E_a}{k} \cdot \left(\frac{1}{T_{stress}} - \frac{1}{T_{normal}}\right)} \quad (2.4)$$

Finally, the resistance step,  $\Delta R$ , is calculated as follows:

$$\Delta R = \left(\frac{\rho_b}{t_b \cdot (W + \cdot 2H)} - \left(\frac{\frac{\rho_m}{H \cdot W} \cdot \frac{\rho_b}{t_b \cdot (W + \cdot 2H)}}{\frac{\rho_m}{H \cdot W} + \frac{\rho_b}{t_b \cdot (W + \cdot 2H)}}\right)\right) \cdot L_{void} \quad (2.5)$$

, where  $\rho_b$  is the resistivity of the diffusion barrier,  $t_b$  is its thickness, W is the wire width, H is its thickness,  $\rho_m$  is the resistivity of the metal and  $L_{\text{void}}$  is the void's length, formed in the timing window at which the EM impact is examined.

The above formula essentially calculates the difference of resistance when the current exclusively flows through the metal and when it is forced to flow through the diffusion barrier for the length of the void. The following figure explains how the resistance is obtained in each case by breaking the wire down to its metal, barrier and void and combining their individual resistances which are calculated as the quotient of the product of resistivity and length, divided by the cross-section.

Figure 2.7. Void demonstration in a copper wire.

#### 2.2 Time-dependent Dielectric Breakdown

The breakdown of the dielectric material refers to the destruction of the dielectric layer that insulates adjacent conductive areas from each other, preventing an unwanted short circuit. Such insulating layers are found in various parts of an IC, such as the gates of MOSFETs, between the plates of capacitors and between adjacent wires of the same metal layer. This last case, which is highly related to the Time-Dependent Dielectric Breakdown (TDDB), namely the second interconnect wear-out we are focusing on in this thesis, has been gaining in significance lately, due to the scaling of interconnect dimensions, as the CMOS process technologies reach the deep-deep submicron era. This is mainly for two reasons:

- Low-k dielectric materials are used in order to decrease the parasitic capacitances of various circuit components and consequently improve both its performance and its power consumption. However, these materials have poorer electrical characteristics and break down sooner and under weaker electric fields.

- The electric fields between adjacent wires are amplified as their distance and therefore the thickness of the dielectric material is reduced. As a result, electric fields between adjacent wires are nowadays approaching those encountered in the gates of transistors one or two decades ago.

The Time-dependent Dielectric Breakdown (TDDB) occurs due to the gradual wear-out of all dielectric materials over time. Even those of high quality are threatened by TDDB over time. But this process of wear is accelerated by the presence of defects and imperfections in the dielectric material, as it will be explained below. The wear-out mechanism is divided in two stages in general:

During the first stage of build-up, charges (holes) are trapped in weak spots of the dielectric where defects or imperfections exist, as leakage current flows through it. These rise in number over time, leading to the formation of high electric fields and high leakage current regions along the wire. This process continues for quite a long time (under normal conditions year-long), until a critical concentration of trapped charges is reached, which is when a transition to the next stage of runaway occurs.

At the stage of runaway, the electric field, which is enhanced by the charge injection, exceeds the breakdown threshold in the weak spots of the dielectric material. Strong leakage currents flowing through those spots heat up the dielectric, which in turn leads to further increase of the current flow. This positive feedback loop eventually results in electrical and thermal runaway, eventually destroying the dielectric. The runaway stage happens in a very short period of time. A region where a dielectric breakdown has occurred, resulting in high leakage current and possibly to a hotspot in the specific die location can be seen in the following figure.

#### Figure 2.8. TDDB-induced leakage between adjacent wires of the same metal layer.

The presence of defects and imperfections in low-quality porous dielectrics greatly reduces the time needed for transition from the build-up to the runaway stage. These defects actually have the effect of "thinning" down the dielectric where they are located, since they are occupying space that should be occupied by the dielectric. The effective electric field is higher in these thinned-out areas compared to defect-free areas for any given voltage. This is why it takes a lower voltage and shorter time to break down the dielectric at its defect points. The TDDB leads to gradual increase of the leakage current until the dielectric breaks down as explained above. This leakage current increase can be divided in three stages that are demonstrated in the following diagram.

Figure 2.9. Inter-metal leakage current versus time.

During the first stage, the leakage current increases because of the accumulation of trapped charges. During the second stage, it decreases at a rate that depends on the quality of the dielectric material as new electron trapping spots are created. Finally, during the third stage, the leakage current increases at a logarithmic rate before the final breakdown that leads to short circuit. At that point, a conducting path connecting the anode and the cathode has formed. The evolution of such a path is shown in the following figure, which explains the idea behind the statistical percolation model that is used to estimate various parameters of the phenomenon of TDDB:

Figure 2.10. TDDB evolution stages.

The circles represent charge-trapping defects. The creation of such defects begins from the sparse trapping of positive charges (holes) that don't form any

conducting path which is a temporary situation (A). At some point in time, a path consisting of both permanent (green circles) and temporary (orange circle) defects may be formed (B). A defect that has trapped a hole can then either return to its initial state by losing the charge (A) or become permanent with the "connection" of the hole with an electron (C). When the leakage current rises significantly, the path (C) can be expanded (D) in combination with the elevated temperature, resulting in the breakdown of the dielectric material.

Under operating conditions encountered in a typical IC, TDDB takes a very long time to fully develop (possibly even decades), so the indicated method of study is through accelerated testing under stress conditions of high temperature and high voltage. The data collected from such experiments can stretch over a period of several days or up to a month. These are then extrapolated using empirical and statistical models to the desired time period and normal conditions.

The most widely used models are two. The first and more well-known is the E-model, which is based on the electric field in order to interpret the phenomenon [11]. The second, namely the 1/E-model, assumes that the dielectric breakdown process is driven by the leakage current [11]. In more detail:

- In the electrochemical E-model, the cause of low-field (<10 MV/cm) high temperature TDDB is due to field-enhanced thermal bond-breakage. In this model, the field serves to stretch molecular bonds thus making them weaker and more susceptible to breakage by standard Boltzmann (thermal) processes. Since the field reduces the activation energy required to break a bond, the degradation rate is expected to increase exponentially with field. Failure occurs when a localized density of broken bonds (or percolation sites) becomes sufficiently high to cause a conductive path to form from anode to cathode.

- The 1/E-model for TDDB (even at low fields) postulates that TDDB is due to current flow through the dielectric due to Fowler-Nordheim (F-N) conduction. Electrons, which are F-N injected from the cathode, may cause damage to the dielectric due to impact ionization as the electrons are accelerated through the dielectric. Also, when these accelerated electrons finally reach the anode, hot holes may be produced which can tunnel back into the dielectric causing damage (hot-hole anode-injection model). Since both the electrons from the cathode and the hot-holes from the anode are the result of F-N conduction, then the MTTF is expected to show an exponential dependence on the reciprocal of the electric field, 1/E.

Despite all the research that has been and is still being conducted on TDDB, there is no definitive consensus on the physical mechanism underlying the phenomenon. So both models are used depending on how well they fit the experimental data obtained using different dielectric materials, electric fields and temperatures.

In the case of interconnects, however, where the dielectric materials are still a few micrometers thick, their dielectric constant is low and the electric field is moderate in intensity, the E-model seems to provide a closer fit to experimental data and therefore it is preferred. The extrapolation proposed in this case is exponentially proportional to the electric field and results in an almost linear rise in the leakage current until the dielectric breakdown. Once again, the temperature plays a very important role in the evolution of TDDB.

# 3

## Design flow methodology

#### 3.1 Basic concepts

The presented design flow extracts the target interconnects from the design in order to estimate the system's lifetime due to timing violations, caused possibly by the gradual degradation of the electrical characteristics of interconnects. As target interconnects, we define those belonging to register-to-register timing paths, the timing of which is evaluated before and after the studied wear-out mechanisms' impact annotation. An important feature is the flow's expandability to other reliability-threatening phenomena besides EM and TDDB, by just incorporating the appropriate model calculations, following the existing generic flow's steps. These steps include, first of all, the retrieval of layout-specific interconnect data, required for the model's computations, and the temperature profile estimation for the given IC. The temperature is calculated for each unit of the design's floorplan, while the wire information for the target interconnects is derived from the Cadence SoC Encounter Database Access (DBAccess) command set [21].

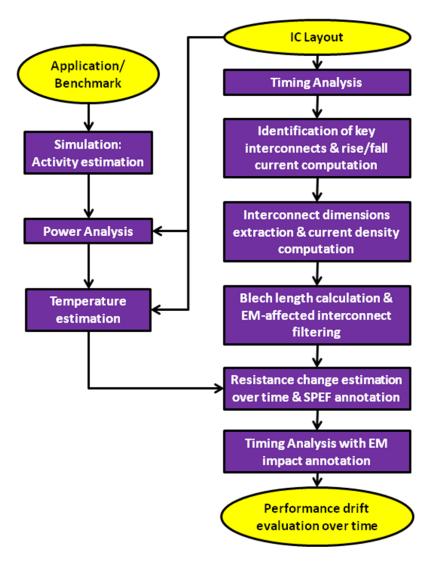

As a result, the presented generic flow can be adopted to estimate the impact of any relevant interconnect wear-out mechanism that may progressively lead to the system's parametric (e.g. timing) failure over time. However, in this thesis, we have focused on EM and TDDB, not only because of the expected impact of the aforementioned phenomena on the interconnect delay (see Section 1.4), but also because of the presence of a pre-existing estimation framework [1][2], which evaluates the system's performance degradation due to these phenomena. Therefore, our intention was to make a step towards the improvement of the initial interconnect reliability toolflow, by considering a more realistic temperature distribution across the target design's layout in order to increase the accuracy of its predictions.

Regarding the flow's steps for EM, the proposed methodology, which has been strongly based on the initial framework, extracts the wires from each interconnect that belongs to the selected timing paths and updates its resistance, only if the examined wire is longer than the Blech length. Then, the updated wire resistances are annotated to the SPEF file of the design, which is input, together with the post-layout netlist, to the static timing analyzer, in order to evaluate the impact of EM on the design's performance.

A similar approach is followed for TDDB, as far as the wire extraction and the final performance evaluation are concerned. Regarding the core of the model, due to the lack of consensus on a formula for Inter-Metal Dielectric leakage current, the proposed flow, as well as its initial version [1][2], rely on the extrapolation of leakage current measurements from stress to operating conditions. The delay overhead introduced to the affected wires is computed in two steps. First of all, a look-up table library, relating the leakage current of several wire patterns to the corresponding delay overhead, is constructed. This library includes wire patterns covering a wide range of length, spacing and leakage current values, interpolation between which, is performed to estimate the actual delay overhead of each wire. The total delay for a specific interconnect is calculated as the weighted mean of its wires' delays and it is annotated to the SDF file, which is used as input to the static timing analyzer in order to evaluate the impact of the studied phenomenon on the design's performance.

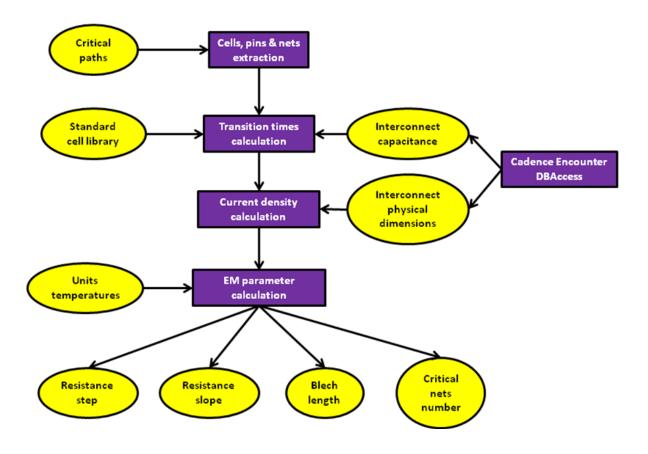

The incorporation of an accurate temperature profile comprises the main contribution of the presented thesis, as it improves the accuracy of the timing drift evaluation. However, there are several other features, which differentiate the proposed work from the previous analysis framework [1][2], by contributing to the accurate estimation of current density for EM through Spice simulations, as well as to the wires' delay computation for TDDB through improved interpolations. Moreover, our toolflow is not limited to the analysis of the interconnects of the single most timing-critical path, as experimental results have shown that initially sub-critical paths may become critical after the annotation of the wear-out mechanisms' additional delay [3]. Hence, the new version of the framework is able to analyze as many paths as the designer selects concurrently, and to annotate and evaluate the total impact of the aforementioned novel features is illustrated in Figure 3.1, where we provide a holistic view of the proposed reliability framework, by depicting the individual steps required to evaluate the impact of EM and TDDB on a design's timing.

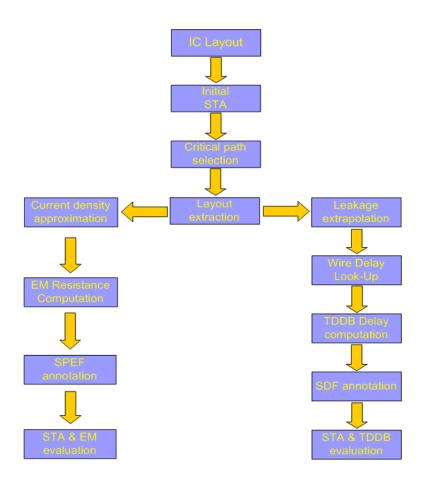

Figure 3.1. The proposed interconnect reliability framework for EM and TDDB.

The comparison of Figures 3.1 and 3.2 clearly reveals several improvements. First of all, the current density estimation performed in the initial flow of Figure 3.2 is quite approximate, as Spice simulations are not involved at all and the tree structure of the interconnect is ignored. Namely, the current of every wire is assumed to be equal to the total current flowing through the net it belongs to. However, this approach, greatly overestimates the current density, which leads to unrealistic results regarding the intensity of EM. Additionally, the boxes of multiple path selection and temperature estimation are missing, whereas in our flow, they comprise two of the main introduced features. Especially the temperature estimation is the most significant feature not included in the early stage of this estimation framework, which has been mainly focused on capturing the system's performance drift, rather than guaranteeing the accuracy of the results in such a detailed granularity. Moreover, the calculation of the TDDB-induced delay overhead used to be based on a rather "poor", layoutunaware, delay look-up library, in contradiction to our approach, which takes the characteristics of the examined layout into account. Nevertheless, the initial framework introduced an innovative approach into the field of reliability-aware design, as it was the first work that attempted to link the degradation of the electrical characteristics of interconnects to the design's performance drift over time.

Figure 3.2. The initial reliability analysis framework presented in [1] and [2].

Regarding the required tools for the analysis described above, both flows are based on industrial EDA suites, which aid in the extraction of the layout-specific information and in the static timing analysis of the design. A slight differentiation exists regarding the temperature profiling, which is based on an open-source academic platform, as it is described in the next section.

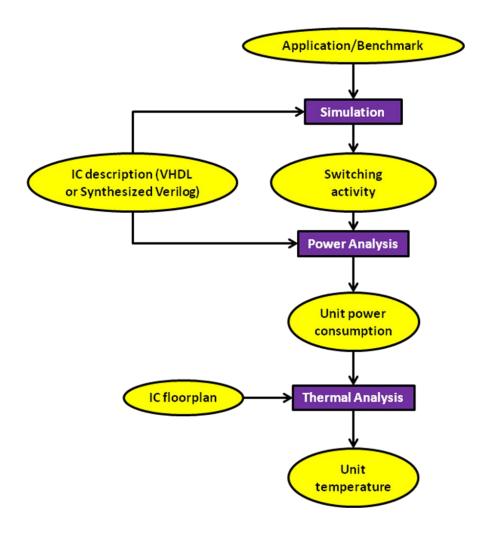

## 3.2 Temperature estimation

The temperature for each unit is derived from the HotSpot tool, provided as an open-source temperature estimation framework, developed by the University of Virginia. The input is just the floorplan of all the design's units, the number of which can vary depending on the design's hierarchy levels and the desired granularity, as well as the power consumption for each of them. The result is the individual temperature estimation for each unit, which is strongly dependent on the power consumption's accuracy.

Based on the obtained temperature profile, the proposed flow, which is generic enough, can be used to analyze any path that is given as input, allowing the use of any path selection algorithm or method considered as appropriate, depending on specific parameters and criteria. The selection of specific paths may focus, for instance, on specific regions of the design that are suspected to be susceptible to the studied interconnect reliability problems, or on any set of architectural, temperature-aware or physical implementation criteria.

In perspective, the design flow consists of discrete steps in order to calculate all required data and we will elaborate on these steps further below. First of all, the temperature for each individual floorplan unit needs to be determined, through HotSpot. This requires the presence of:

- The design's floorplan, which designates the exact placing of each unit on the chip and can be directly exported from the design itself through the Cadence SoC Encounter place-and-route tool, using specific commands.

- The estimated power dissipation for each unit, which can be derived either by assuming certain switching activity information for the design's inputs, or by simulating the post-layout netlist of the design, based on a specific application. In this thesis, we performed the experiments by applying both practices, but the latter has been preferred, even though it is more time-consuming, because of its accuracy on the power profile's estimation.

Figure 3.3. Temperature estimation flow.

## 3.3 EM flow

Once the temperature of each hierarchical unit is extracted, the necessary calculations, in order to obtain the results for the EM impact estimation can be performed. The EM flow consists of the following steps:

- <u>Cell, pin and net extraction</u>: The cells, pins and nets involved in the selected register-to-register critical paths are extracted from the timing analysis results.

- <u>Output transition time calculation</u>: The output pin rise and fall transition times can be retrieved through static timing analysis from within SoC Encounter using a DBAccess command. Alternatively, and in order to cross-check the command's results, the output transition time can be calculated through a lookup in the timing table for the specific cell in the standard-cell library, because it depends on the input pin transition time, the standard-cell driving strength and the output pin load capacitance. The library's format is assumed to conform to the Synopsys Liberty format's specifications, according to which the output transition time look-up is carried out using the input pin transition time, as a row index, and the output pin load capacitance, as a column index. Each input pin's transition time obviously equals the transition time of the output pin that drives that specific input pin and thus can be recursively calculated using the method described here. The output pin load capacitance is obtained using a relative Encounter DBAccess command.

- <u>*Current density calculation:*</u> The most accurate way to estimate the individual current of each wire of a net is through a Spice simulation. But in order to perform a Spice simulation of a charge and discharge cycle of a net, three components need to be modeled:

- First of all, the wires of the net themselves. Their Spice netlist is generated from the corresponding net's SPEF distributed *RC* netlist.

- Second, the input pins that the net is connecting the output pin with. These are modeled as capacitors, whose value is also derived from the SPEF file.

- Finally, the output pin that drives the net. This has been modeled as a voltage source with specific parameters that closely resemble the behavior of an output pin of the system. Specifically, the voltage low level has been set to ground, the high level to  $V_{dd}$  and the rise and fall delays have been set to the rise and fall transition times that have been calculated through the extraction script for the specified output pin respectively.

The simulation of the above Spice netlist is performed and the average value of the rise and fall current flowing through each wire is estimated. The equivalent current is then calculated as their absolute difference and used in order to estimate the evolution of EM through its model. The above procedure is repeated for every net that is part of the examined critical paths.

An approximation formula for current density has also been used to crosscheck the results of the above procedure. This formula is  $\frac{V_{op}C_{net}}{t_{transition}A}$  where  $V_{op}$  is the operating voltage,  $C_{\text{net}}$  is the total net capacitance, A is the cross section area of the net's wire that is driven by a specific standard-cell's output pin, and  $t_{\text{transition}}$  is the transition time of the net. The output pin's load capacitance and the output net dimensions for the determination of its cross-section area are obtained using the respective Encounter DBAccess commands. The output transition times for the calculation of the rise and fall current density are known from the previous step. A great disadvantage of the above formula is its reduced accuracy due to ignoring the tree structure of the interconnect and thus the distribution of the current to each branch.

- <u>EM parameters estimation</u>: After having calculated the rise and fall current density as described above, the average current density is calculated as their absolute difference as the EM model is for DC current. The parameters  $t_{50}$ ,  $R_{slope}$ ,  $\Delta R$  and  $l_{critical}$ , that quantify the impact of EM, are then calculated using the EM model described in the previous chapter and they are written along with the net's name to an intermediate file, which includes all the information regarding the wires of the examined path's nets which are affected by EM in the timing window of the desired system's lifetime. We will elaborate further on the generation, the structure and the context of this file, namely *deltaR.report*, in the next chapter. The computed EM parameters are needed later in the flow to update the elevated wire resistance values in the SPEF file of the design, in order to take the effect of EM into account while estimating the system's performance drift over time.

- <u>SPEF annotation</u>: Depending on the operation time period that is desired to be simulated, the total resistance increase for each net wire is calculated as the sum of the resistance step and the resistance slope multiplied by the number of years since  $t_{50}$ . It must be noted that all the aforementioned steps of this flow are performed for nets that belong to certain register-to-register paths of the target design. Then, using the net's name, its parasitic resistances are located in the SPEF file. It must be noted that only those wires longer than the critical length for the specified net must be updated. This is ensured by updating only the wires of each net with resistance values higher than the product of the critical length by the average resistance per length value.

- <u>Estimation of EM impact on system's timing</u>: A new timing analysis using the annotated SPEF file will reveal the impact of EM on the timing of the system and will indicate possible timing violations due to the EM-induced interconnect resistance rise.

Figure 3.4. The temperature-aware EM flow.

## 3.4 TDDB flow

In this section of the flow, the interconnects that run parallel to each other, posing increased TDDB induced risk are identified and the impact of the leakage current between them on the system's timing is estimated. The TDDB flow consists of the following steps:

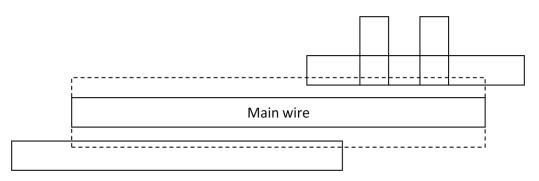

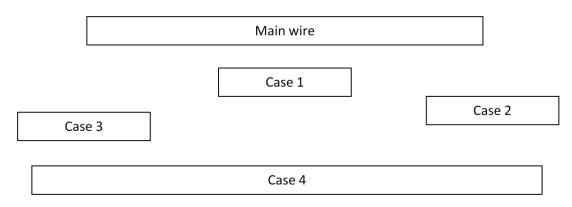

• <u>Detection of adjacent wires:</u> TDDB only takes place in wires that are close enough to each other. So, a filtering of all adjacent wires of each wire of a net must be carried out in order to identify them. The maximum distance can be altered, depending on the fabrication technology used. The wires that are discovered are written to a report with their positions and relative distances, which are exploited later in the tool flow. We will elaborate further on the generation, the structure and the context of this file, namely *wire.report*, in the next chapter.

- <u>Estimation of the TDDB-induced leakage current:</u> Using the adjacent wire data gathered before, a calculation of the leakage current by extrapolation of lab measurements under stress conditions to operating conditions is performed as described in the corresponding TDDB model, shown in Chapter 2.

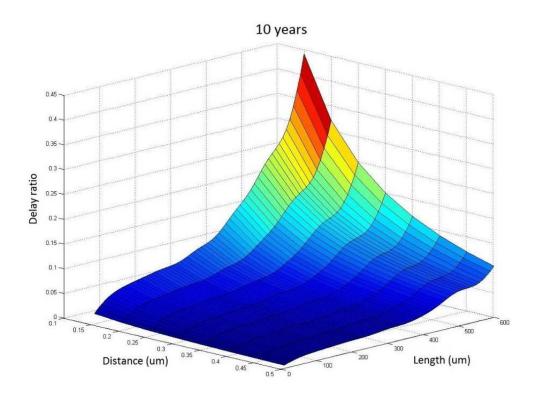

- <u>Estimation of the delay change due to TDDB-induced leakage current</u>: The only way to obtain an accurate estimation of the impact of the TDDB-induced leakage current on the system's timing is a set of SPICE simulations to generate a pre-characterized library of representative layout patterns combined with a range of leakage currents. For the rest of the tool flow, on-the-fly simulations using real and accurate wire patterns would be too time consuming and not worth the extra timing overhead for each separate design, so another approach was preferred instead. This involved the generation of a LUT containing permutations of all possible TDDB-influencing values within certain ranges which are expected to be encountered throughout the design, along with their corresponding delay change ratios. The generation is performed based on a distributed *RC* model of the wire, with representative values of resistance *R* and capacitance *C*, as well as leakage current sources, all uniformly scattered across the overlapping section of the wire.

The constructed LUT library contains key values of the wire's length, the adjacent wire (overlapping) length, the relative position of the wires, the leakage current and finally, the distance from each other. This LUT needs to be constructed only once for each CMOS technology of implementation. Afterwards, the delay change ratio of real wires is estimated using interpolation, so the overhead added is very limited. The characteristics of real wires are read from the report mentioned earlier. Hence, through a look-up table search, followed by an interpolation, if needed, the delay overhead for a specific wire is estimated.

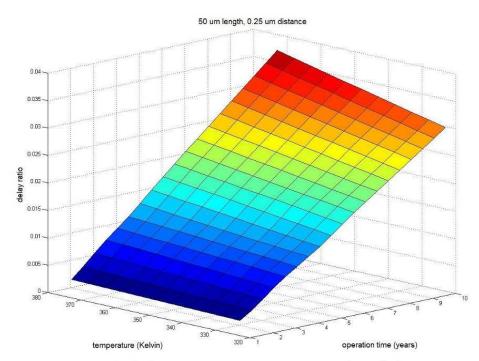

The following figure provides an insight into how the TDDB delay ratio of a net's wire depends on the wire's length and also on the adjacent wire's distance, when all other parameters (e.g. temperature) are kept constant.

Figure 3.5. Delay impact on a wire due to TDDB, depending on wire length and distance.

- <u>SDF annotation</u>: The last step is to update the interconnect delays of the SDF file. Using the interconnect output and input pin, the initial delays are located and read. The total delay change ratio of each interconnect is calculated as the weighted mean (based on lengths) of the delay change ratio of its individual wires. Then the delay of that interconnect in the SDF file is incremented by the total delay change ratio.

- <u>Estimation of TDDB impact on system's timing</u>: A new timing analysis using the annotated SDF file will reveal the impact of TDDB on the timing of the system and will indicate possible timing violations due to the TDDB induced leakage current increase which leads to transition delay increase.

Figure 3.6. The TDDB flow with the temperature profile's annotation from HotSpot.

## 3.5 Combined impact methodology

In the presented thesis, the studied reliability wear-outs, namely EM and TDDB, were considered as independent phenomena and consequently, the developed estimation framework captures the timing impact of each one of them without considering any inter-dependence between them. However, EM can affect the intermetal distance of affected wires, as the void formation leads to extrusions of copper wires' segments at the cathode end. Hence, in such a case, the spacing between the extruded wire and its adjacent one on the same metal layer is locally reduced and the corresponding electric field is enhanced. It is noted that wire extrusions due to EM may occur only when current densities are significantly high and the specific wire is stressed for a long time, which is not a typical case in operating conditions. However, high peak currents in computational-intensive parts of designs such as processors or arithmetic units with high fan-out logic cells may include wires that could be candidate to suffer from extrusions, especially as the technology scaling shrinks the interconnect dimensions. As a result, the development of a methodology that could

incrementally capture the combined impact of EM and TDDB gains in significance, as does the need for a model to estimate the location of possible wire extrusions.

From a purely technical point of view, the estimation of the combined impact of both reliability wear-outs on the target design's timing is based on a technique that uses an intermediate step after the annotation of the updated resistances due to EM into the design's SPEF file. This step involves the generation of an updated SDF file of the design through a static timing analysis, based on the annotated SPEF file that includes the impact of EM. In this way, the produced SDF file includes the impact of EM and it can be used as input to the TDDB analysis flow. The execution of the TDDB flow's steps leads to the generation of the final SDF file, including the total delay shifting because of both EM and TDDB. The combined impact is evaluated by the final static timing analysis for the examined design's paths.

In either the separate or the combined version of the proposed framework, the analysis of the steps required to evaluate the timing impact of the studied reliability phenomena is viewed from a rather abstract point of view, as it is presented in this chapter. However, in the next chapter, we elaborate further on the detailed implementation of the aforementioned design flow steps, describing each part of our tool flow in detail, including the DBAccess commands used for the layout extraction and the way each step interacts with the industrial EDA tools. Also, a view on the Encounter DBAccess layout extraction tools is provided, along with the analysis of the scripts used for the proposed flows' implementation.

# 4

## **Design flow implementation &**

## Automation

## 4.1 Flow implementation tools and components

This paragraph covers the implementation details of the design flow including mainly the technical section, such as the tools used and the scripts written to realize each of the EM and TDDB flow steps.

## 4.1.1 Temperature estimation (HotSpot)

The units' temperature estimation is done with the help of an academic tool named HotSpot that is developed, maintained and distributed by the University of Virginia. HotSpot is an accurate and fast thermal model suitable for use in architectural studies. The actual tool is based on an equivalent circuit of thermal resistances and capacitances that correspond to micro-architectural blocks and essential aspects of the thermal package. The model has been validated using finite element simulation.

HotSpot has a simple set of interfaces and hence can be integrated with most power-performance simulators. The main advantage of HotSpot is that it is compatible with the kinds of power and performance models used in the computerarchitecture community, requiring no detailed design or synthesis description. HotSpot makes it possible to study thermal evolution over long periods of real, fulllength applications.

HotSpot requires a configuration file which contains various fabrication and packaging dependent parameters such as the chip and spreader thickness. Other than that, being generic, it only requires two input files, which contain the units' placement on the chip and each unit's power consumption respectively. These can be produced by any tool or method the user prefers.