### NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

COMPUTER SCIENCE DIVISION COMPUTING SYSTEMS LABORATORY

A study of a dynamic placement policy in a NUCA cache

by

### Alexandros I. Daglis

Supervisor: Nectarios Koziris Associate Professor

Athens, July 2012

NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING COMPUTER SCIENCE DIVISION COMPUTING SYSTEMS LABORATORY

## A study of a dynamic placement policy in a NUCA cache

by

Alexandros I. Daglis

Supervisor: Nectarios Koziris Associate Professor

Approved by the three-man evaluation committee on the 18th of July 2012.

Nectarios Koziris Associate Professor

Panayiotis Tsanakas Professor Nikolaos Papaspyrou Assistant Professor

Athens, July 2012.

.....

Alexandros I. Daglis Electrical and Computer Engineering Diploma holder

©Alexandros I. Daglis, 2012

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα. Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# Περίληψη

Ένα σημαντικό πρόβλημα στα μοντέρνα υπολογιστικά συστήματα είναι η διάρκεια των προσβάσεων στην ιεραρχία μνήμης. Καθώς τα μεγέθη των μνημών μεγαλώνουν και μαζί τους και αυτές οι καθυστερήσεις, το να απαιτείται ένας ομοιόμορφος, μεγάλος χρόνος για κάθε πρόσβαση στη μνήμη, είναι απαγορευτικό. Για να αντιμετωπιστεί το πρόβλημα αυτό, η κλασσική μονολιθική αρχιτεκτονική της μνήμης εξελίσσεται σε μια κατανεμημένη μορφή, η οποία παρέχει τη δυνατότητα για μη ομοιόμορφους χρόνους προσπέλασης. Η νέα αυτή αρχιτεκτονική είναι γνωστή ως Non-Uniform Cache Architecture (NUCA). Μια μνήμη NUCA απαρτίζεται από πολλά μικρά κομμάτια, τα οποία κατανέμονται χωρικά στην επιφάνεια του chip. Ο χρόνος πρόσβασης σε καθένα από αυτά τα κομμάτια είναι μεταβλητός και εξαρτάται από την απόσταση μεταξύ του αιτούντος επεξεργαστή και του κομματιού της NUCA που εξυπηρετεί το αίτημα.

Σε μια στατική NUCA, τα δεδομένα τοποθετούνται στατικά ανάλογα με τη διεύθυνσή τους. Αυτή η τακτική είναι αρκετά περιοριστική, αφού δεν εξασφαλίζει ότι η πλειονότητα των αιτημάτων θα εξυπηρετηθεί από τα ταχύτερα κομμάτια της NUCA, αυτά δηλαδή που βρίσκονται πιο κοντά στον αιτούντα επεξεργαστή. Έτσι, η έρευνα έχει οδηγήσει τις μνήμες NUCA σε δυναμικές μορφές οργάνωσης, όπου τα δεδομένα τοποθετούνται και μετακινούνται ελεύθερα μέσα στη NUCA. Σε αυτή τη διπλωματική εργασία, αξιολογείται η χρήση δυναμικής NUCA σε ένα πολυεπεξεργαστικό σύστημα, εστιάζοντας κυρίως σε μια πολιτική δυναμικής τοποθέτησης δεδομένων που στοχεύει στη μεγιστοποίηση του αριθμού των προσπελάσεων στα ταχύτερα κομμάτια της. Η πολιτική αυτή συμπληρώνεται με κατάλληλες πολιτικές για την αντικατάσταση, μετακίνηση και αναζήτηση δεδομένων στη μνήμη. Η πολιτική αντικατάστασης επιτρέπει σε ένα κομμάτι της μνήμης να τοποθετεί δικά του δεδομένα σε γειτονικά κομμάτια, αντί αυτά να επιστρέφουν απ' ευθείας στην κύρια μνήμη, ενώ η πολιτική μετακίνησης δεδομένων αποσκοπεί στη μεταφορά τους προς τους επεξεργαστές που τα ζητούν συχνότερα. Για την αξιολόγηση της δυναμικής NUCA χρησιμοποιήθηκαν μετροπρογράμματα με διαφορετική συμπεριφορά, όπως επιστημονικά, server και multi-programmed workloads. Η δυναμική μας NUCA πετυχαίνει σημαντική βελτίωση για όλα τα workloads έναντι της στατικής: 7.7% κατά μέσο όρο και μέγιστη βελτίωση 15.6% για το multi-programmed workload.

**Λέξεις-κλειδιά:** δυναμική μνήμη μη ομοιόμορφου χρόνου προσπέλασης, πολιτική αντικατάστασης, πολιτική δυναμικής τοποθέτηση, πολιτική μετακίνησης δεδομένων, Flexus

## Abstract

An important problem in modern systems is long memory access times, which are a major bottleneck to performance. More specifically, as cache capacities grow, suffering a long, uniform access latency is intolerable. To mitigate this problem, the classic monolithic cache evolves into a distributed cache design, that provides non uniform access, known as Non-Uniform Cache Architecture (NUCA). A NUCA cache is split into smaller slices, which are distributed across the die. Accesses to data that resides in one of these tiles display a variable latency, depending on the physical distance between the requesting core and the cache slice servicing the request.

In a static NUCA, data is statically placed in the cache, according to its address. However, this design imposes limitations, since accesses to local, faster cache tiles are not maximized. Therefore, research has led to dynamic NUCA designs, where data can be freely placed and moved in the cache.

This diploma thesis investigates dynamic NUCA policies in a tiled Chip Multiprocessor (CMP) system, focusing on a dynamic placement policy that aims to maximize accesses to the fastest cache slices. The dynamic placement policy is complemented with an appropriate replacement policy, a migration policy and a lookup mechanism. The replacement policy allows a cache bank to spill data to its neighbors, if there are additional capacity needs, while the migration policy gradually moves data towards the cores that are most frequently accessing it. For our design's evaluation, a diverse workload set comprising of server, scientific and multi-programmed workloads was used. Our dynamic NUCA scheme has shown an average performance improvement of 7.7% over the static NUCA and a maximum performance improvement of 15.6%.

**Keywords:** dynamic NUCA, placement policy, replacement policy, migration policy, Flexus, tiled architecture, CMP

# Acknowledgements

This diploma thesis was conducted in the Computing Systems Laboratory of the School of Electrical and Computer Engineering of the National Technical University of Athens, under the supervision of Associate Professor Nectarios Koziris.

I would like to thank my supervisor, Dr. Nectarios Koziris, for his guidance during the process of this thesis and throughout my undergraduate studies.

I want to express my gratitude to the Post-Doctoral Researcher Dr. Konstantinos Nikas, for his continuing support and encouragement in the course of the months of work required for the completion of this thesis and to the PhD student Stavros Volos, for his help with the numerous technical issues of the toolchain that was used.

Finally, I especially thank my parents and brothers for standing by my side throughout the duration of my undergraduate studies.

# Contents

| 1        | Intr | oducti        | on 14                                                                                                                       |   |  |  |  |  |  |

|----------|------|---------------|-----------------------------------------------------------------------------------------------------------------------------|---|--|--|--|--|--|

|          | 1.1  | Memo          | ory hierarchy $\ldots \ldots 14$ | 1 |  |  |  |  |  |

|          | 1.2  | Last le       | evel cache                                                                                                                  | 5 |  |  |  |  |  |

|          | 1.3  | The li        | mitations of the UCA design 16                                                                                              | 3 |  |  |  |  |  |

| <b>2</b> | NU   | $\mathbf{CA}$ | 18                                                                                                                          | 3 |  |  |  |  |  |

|          | 2.1  | Introd        | lucing the NUCA design                                                                                                      | 3 |  |  |  |  |  |

|          |      | 2.1.1         | Static NUCA 19                                                                                                              | 9 |  |  |  |  |  |

|          |      | 2.1.2         | Dynamic NUCA                                                                                                                | ) |  |  |  |  |  |

|          |      | 2.1.3         | Policies of a NUCA design                                                                                                   | 1 |  |  |  |  |  |

|          | 2.2  | Backg         | ground - Related Work                                                                                                       | 2 |  |  |  |  |  |

|          |      | 2.2.1         | NUCA for uniprocessors                                                                                                      | 2 |  |  |  |  |  |

|          |      | 2.2.2         | NUCA for CMPs                                                                                                               | 1 |  |  |  |  |  |

|          |      |               | 2.2.2.1 Migration                                                                                                           | 1 |  |  |  |  |  |

|          |      |               | 2.2.2.2 Replication                                                                                                         | 3 |  |  |  |  |  |

|          |      |               | 2.2.2.3 Dynamic Placement                                                                                                   | 9 |  |  |  |  |  |

|          |      |               | 2.2.2.4 Other approaches for NUCA designs 34                                                                                | 1 |  |  |  |  |  |

|          |      | 2.2.3         | To migrate or not to migrate?                                                                                               | 3 |  |  |  |  |  |

| 3        | Тоо  | ols used      | d 37                                                                                                                        | 7 |  |  |  |  |  |

| 0        | 3.1  |               | luction $\ldots$ $\ldots$ $\ldots$ $\ldots$ $37$                                                                            |   |  |  |  |  |  |

|          | 3.2  | SimFl         |                                                                                                                             |   |  |  |  |  |  |

|          | 0.2  | 3.2.1         | SMARTS                                                                                                                      |   |  |  |  |  |  |

|          |      | 3.2.2         | Flexus                                                                                                                      |   |  |  |  |  |  |

|          | 3.3  | -             | xperimental procedure                                                                                                       |   |  |  |  |  |  |

|          | 0.0  | 3.3.1         | Preparing a new workload                                                                                                    |   |  |  |  |  |  |

|          | 3.4  |               | marks                                                                                                                       |   |  |  |  |  |  |

|          |      | 3.4.1         | Common benchmark classes                                                                                                    |   |  |  |  |  |  |

|          |      | 3.4.2         | Benchmarks for Flexus                                                                                                       |   |  |  |  |  |  |

|          |      |               | 3.4.2.1 General purpose benchmarks                                                                                          | 3 |  |  |  |  |  |

|          |      |               | 3.4.2.2 Server benchmarks                                                                                                   | 7 |  |  |  |  |  |

|          |            | $3.4.2.3$ Scientific benchmarks $\ldots \ldots \ldots \ldots 4$ | 18         |

|----------|------------|-----------------------------------------------------------------|------------|

|          |            | 3.4.2.4 Benchmark selection summary 4                           | 19         |

| <b>4</b> | Dev        | veloped Dynamic Placement Model 5                               | 60         |

|          | 4.1        | System architecture                                             | 50         |

|          | 4.2        | Motivation                                                      | 51         |

|          | 4.3        | Dynamic NUCA policies                                           | 53         |

|          |            | 4.3.1 Dynamic Placement policy                                  | 53         |

|          |            | 4.3.2 Replacement policy                                        | 53         |

|          |            |                                                                 | 55         |

|          |            | 4.3.4 Migration policy                                          | 55         |

|          | 4.4        |                                                                 | 57         |

|          |            | 4.4.1 System architecture                                       | 57         |

|          |            |                                                                 | 57         |

|          |            | 4.4.3 The centralized directory component                       | 59         |

|          |            | 4.4.4 Dynamic placement policy implementation 5                 | 59         |

|          |            | 4.4.5 Replacement policy implementation 6                       | 60         |

|          |            | 4.4.6 Migration policy implementation 6                         | 51         |

|          | 4.5        | Customizing the flexpoints                                      | 52         |

| <b>5</b> | Exp        | perimental evaluation 6                                         | 66         |

|          | $5.1^{-1}$ | Simulated system's parameters                                   | 66         |

|          | 5.2        |                                                                 | 37         |

|          | 5.3        |                                                                 | 58         |

|          | 5.4        | Replacement policy evaluation                                   | 71         |

|          | 5.5        | Overhead estimation                                             | 73         |

| 6        | Cor        | nclusions 7                                                     | <b>'</b> 9 |

|          | 6.1        | Our dynamic NUCA design                                         | 79         |

|          | 6.2        |                                                                 | 30         |

# List of Figures

| 1.1  | A memory hierarchy with two cache levels                                              | 14 |

|------|---------------------------------------------------------------------------------------|----|

| 1.2  | A CMP cache hierarchy with three cache levels $\ldots \ldots \ldots$                  | 15 |

| 2.1  | Level-2 Cache Architectures                                                           | 19 |

| 2.2  | Mapping bank sets to banks                                                            | 22 |

| 2.3  | NuRAPID Cache                                                                         | 23 |

| 2.4  | CMP-NUCA layout with bankcluster regions                                              | 25 |

| 2.5  | Sharing degree: $1, 2, 4, 8$ and $16 \dots \dots \dots \dots \dots \dots \dots \dots$ | 26 |

| 2.6  | D-NUCA Block Migration Policies                                                       | 27 |

| 2.7  | ASR: Replication Effectiveness curve                                                  | 29 |

| 2.8  | Determining the eviction based on cluster priorities                                  | 30 |

| 2.9  | Address-based versus pressure-aware placements                                        | 31 |

| 2.10 | Pressure-aware group-based placement strategy                                         | 32 |

| 2.11 | NUCA Architectures                                                                    | 35 |

| 2.12 | Structures for migration prefetching                                                  | 35 |

| 3.1  | Systematic sampling in SMARTS                                                         | 39 |

| 3.2  | Warming approaches for simulation sampling                                            | 42 |

| 3.3  | Empirical warming determination                                                       | 44 |

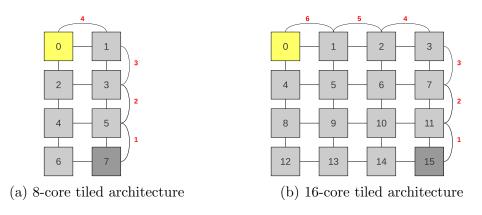

| 4.1  | Typical tiled architecture                                                            | 50 |

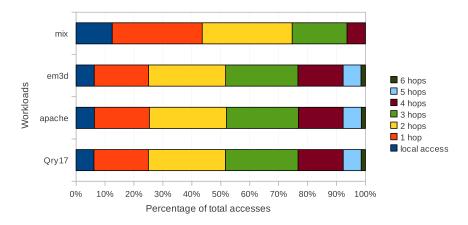

| 4.2  | Hops required for the accesses to the NUCA                                            | 51 |

| 4.3  | Worst-case access scenario                                                            | 52 |

| 4.4  | The replacement decision                                                              | 54 |

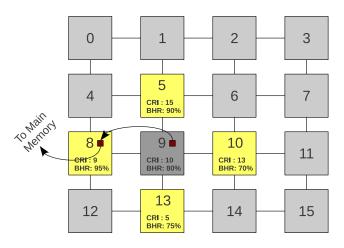

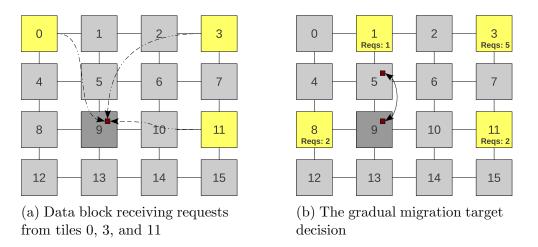

| 4.5  | Migration caused by requests to a block in tile 9                                     | 56 |

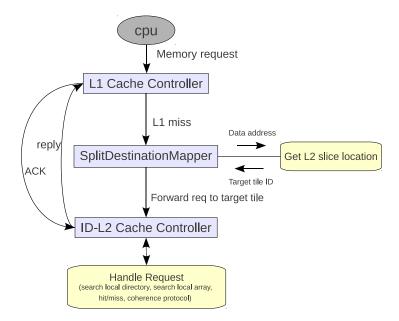

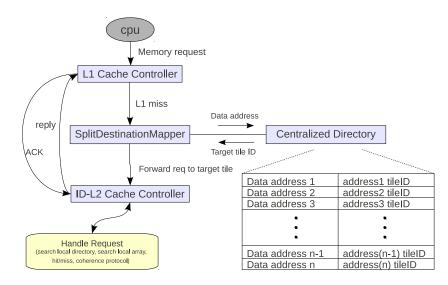

| 4.6  | Default procedure for a L2 request                                                    | 58 |

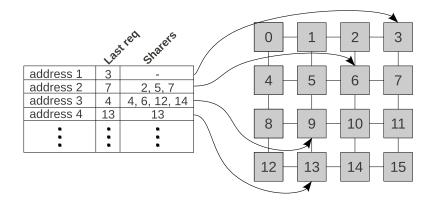

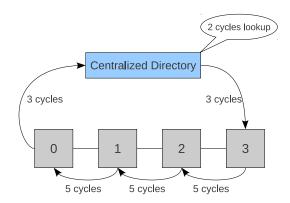

| 4.7  | Centralized directory                                                                 | 59 |

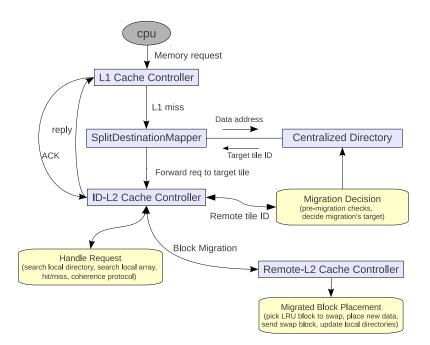

| 4.8  | Adapted procedure for a L2 request and migration mechanism                            | 61 |

| 4.9  | Default flexpoint load                                                                | 63 |

| 4.10 | Adapted flexpoint load                                                                | 64 |

| 5.1  | Sampling a throughput application                                                     | 67 |

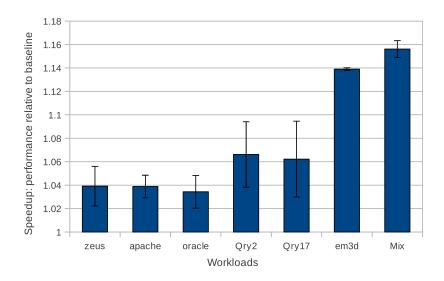

| 5.2  | Performance speedup                                             | 69 |

|------|-----------------------------------------------------------------|----|

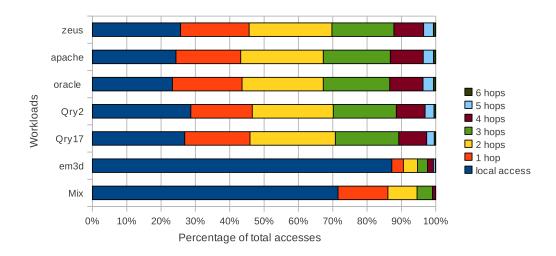

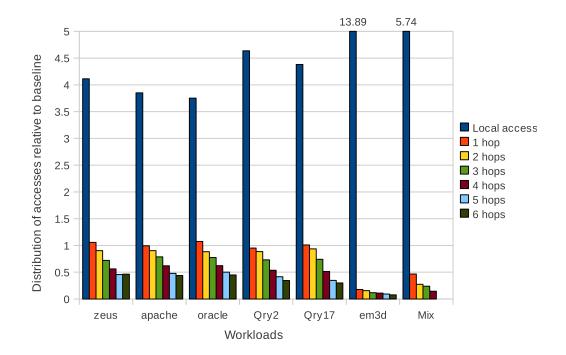

| 5.3  | Hops required for the accesses in the dynamic NUCA              | 69 |

| 5.4  | Distribution of hops required per L2 cache access               | 70 |

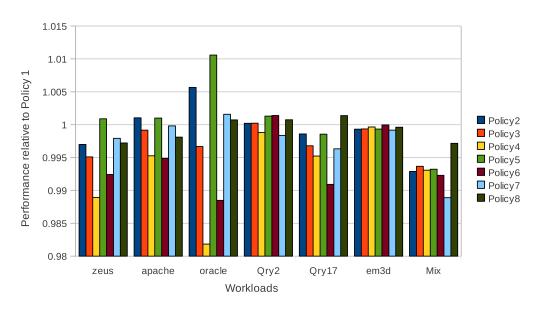

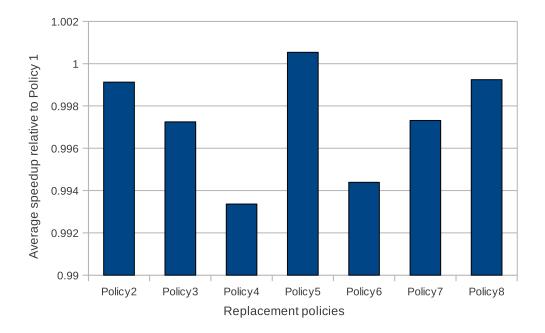

| 5.5  | Replacement policies performance, relative to policy 1          | 72 |

| 5.6  | Average performance speedup for all replacement policies        | 73 |

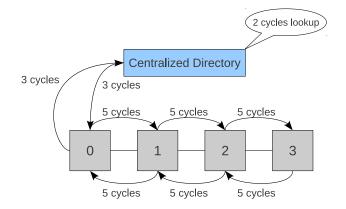

| 5.7  | Network latencies for the naive access design                   | 74 |

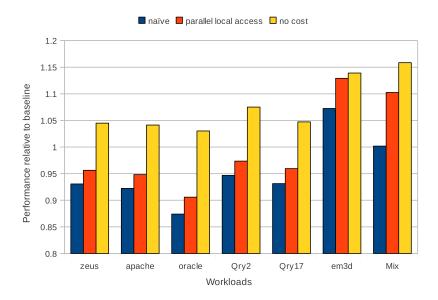

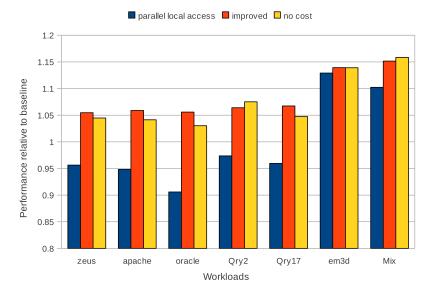

| 5.8  | Performance for the naive and parallel local access design      | 75 |

| 5.9  | Network latencies for the improved access design                | 76 |

| 5.10 | Performance for three different centralized directory designs . | 77 |

|      |                                                                 |    |

# List of Tables

|     | Performance of UCA organizations                              |    |

|-----|---------------------------------------------------------------|----|

| 2.1 | Performance of NUCA organizations                             | 20 |

| 3.1 | Application parameters                                        | 49 |

| 4.1 | Impact of remote accesses to the NUCA                         | 52 |

| 5.1 | System parameters                                             | 66 |

| 5.2 | Baseline vs dynamic comparison of average hops per L2 access  | 71 |

| 5.3 | Benefit from the improved access design for each request type | 76 |

# Chapter 1 Introduction

Chip Multiprocessors (CMPs) are dominating modern systems. With integration of transistors on a single chip doubling almost every 18 months, CMPs seem to be a one-way road. The successors of the classic uniprocessor design manage to provide solutions to a wide range of problems: frequency scaling, design complexity, power dissipation. Furthermore, new horizons are opened: parallel execution on a single chip, which reveals new opportunities as well as architectural challenges.

## 1.1 Memory hierarchy

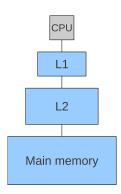

A system's memory hierarchy is of crucial importance for overall performance. In general, the greater the computing power of the system, the greater the access intensity to the memory. With memory access latency being orders of magnitude slower than processors' operation speed, the memory hierarchy can easily turn out to be a major bottleneck to performance. Therefore, memory structures that provide fast access to data are needed. These structures are no other than caches, i.e. small and fast memories that are placed as close to the processors as possible. To balance the tradeoff between size and access latency, multi-level memory hierarchies have emerged as a common architectural trend. Figure 1.1 shows the memory architecture of a system with two levels of caches. The closer to the processor a cache level is located, the smaller its capacity and the faster its access.

Figure 1.1: A memory hierarchy with two cache levels

Due to their importance, multi-level memory hierarchies have been extensively studied in the context of uniprocessors. However, CMPs give birth to further challenges. As the number of cores on the chip is increased, the pressure to the memory hierarchy heightens. Each running thread could have its own data workset but there could also be sharing between them. Typically, the memory hierarchy becomes more complex, with each processor having one or two private levels of caches and varying degrees of sharing for lower levels. Figure 1.2 illustrates a memory hierarchy with three cache levels for a quad core system, where the L1 caches are private for their processors, L2 caches have a sharing degree of two and the L3 cache has a sharing degree of four, thus it is shared by all processors.

Figure 1.2: A memory hierarchy for a quad core CMP with three cache levels

### **1.2** Last level cache

The Last Level Cache (LLC) is a component of the memory hierarchy with a particular significance:

- Being the last on-chip memory component, finding data in it is the last chance to avoid a long off-chip request.

- It is usually shared by all of the chip's processors, thus being used and manipulated by all possible request sources.

Thus, the LLC is designed to be as big as practically possible. However, with the ongoing size shrinkage of transistors and increase of integration density, LLCs become so big that new problems arise. A major consequence is that access latency grows prohibitively, resulting in an important performance bottleneck.

### **1.3** The limitations of the UCA design

Increasing a cache's size is not a straightforward design choice, since it bears a significant tradeoff. Larger capacity comes at the cost of increased access latency, as wire delays grow along with the physical size of the memory structure. For that reason, large on-chip caches with a single, large and uniform latency are undesirable. Especially for an LLC, being the largest on-chip cache, the latency lies in the tens of cycles, making accesses to the LLC unbearably slow. In other words, increasing cache sizes only makes the existing gap between processor and memory access speeds grow even wider.

| Tech. | L2   | Num.      | Unloaded | Loaded  |      | Miss |

|-------|------|-----------|----------|---------|------|------|

| (nm)  | Size | Sub-banks | Latency  | Latency | IPC  | Rate |

| 130   | 2MB  | 16        | 13       | 67.7    | 0.41 | 0.23 |

| 100   | 4MB  | 16        | 18       | 91.1    | 0.39 | 0.20 |

| 70    | 8MB  | 32        | 26       | 144.2   | 0.34 | 0.17 |

| 50    | 16MB | 32        | 41       | 255.1   | 0.26 | 0.13 |

Table 1.1: Performance of UCA organizations

The limitations of the classic design where the memory exhibits a Uniform Cache Access time (UCA), are very well presented by Kim et al. [17], who used Cacti 3.0 [21] to estimate the access times for various cache designs. The parameters and achieved Instructions Per Cycle (IPC) of the UCA organization are shown in Table 1.1. Unloaded latency is the average time in cycles, assuming uniform bank access distribution and no contention, while loaded latency was obtained through an experimental evaluation and is the actual L2 cache access time -including contention- across all of the used benchmarks. Contention includes both *bank* and *channel* contention: bank contention occurs when a request must stall because a precious request is being serviced by the same bank, while channel contention occurs when the bank is free but the routing path to it is busy.

As observed in Table 1.1, unloaded access latency grows significantly with the cache size, which, in turn, has an even greater impact on the loaded latency. A small increase in the cache's unloaded latency greatly increases the probability of overlying requests, which makes contention much worse; thus, it results in a great increase of the loaded latency. This observation suggests that even multiported cells are a poor solution for overlapping accesses in large caches, as increases in area expand loaded access times significantly. To illustrate this further, for a 2-ported, 16 MB L2 cache at 50nm, Cacti reports a significant increase in the unloaded latency, which makes the 2-ported cache perform worse than a single-ported cache of the same size [17].

Kim et al. presented these results in 2002, when one of the latest processors at the time, IBM's POWER 4 [5], featured a 1.41 MB L2 cache as its LLC. Nowadays, a 16 MB or even bigger on-chip LLC is common, as can be en in Table 1.2. It is obvious, therefore, that the inefficiencies of the UCA design regarding access latency and contention need to be addressed.

| Processor<br>codename  | Bloomfield    | Beckton    | Beckton    | Interlagos  |

|------------------------|---------------|------------|------------|-------------|

| Branding &             | Intel Core-i7 | Intel Xeon | Intel Xeon | AMD Opteron |

| Model                  | 940           | E7540      | X7560      | 6284SE      |

| Technology             | 45 nm         | 45  nm     | 45  nm     | 32 nm       |

| Number<br>of Cores     | 4             | 6          | 8          | 16          |

| CPU<br>Clock Rate      | 2.93 GHz      | 2.00 GHz   | 2.26 GHz   | 2.70 GHz    |

| Year of<br>Release     | 2008          | 2010       | 2010       | 2012        |

| LLC size<br>(L3 cache) | 8 MB          | 18 MB      | 24 MB      | 2x8 MB      |

Table 1.2: Last level cache sizes on modern processors

# Chapter 2 NUCA

In order to adapt to the ever-growing needs of modern memory-hungry workloads, on-chip caches keep growing bigger. Unfortunately, expanding the cache size alone is not sufficient to increase modern systems' efficiency, since the traditional UCA design exhibits serious limitations, as was briefly explained in Chapter 1. The solution lies in a distributed cache design, that manages to provide varying access times and increased bandwidth.

## 2.1 Introducing the NUCA design

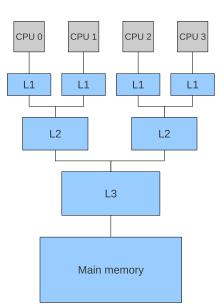

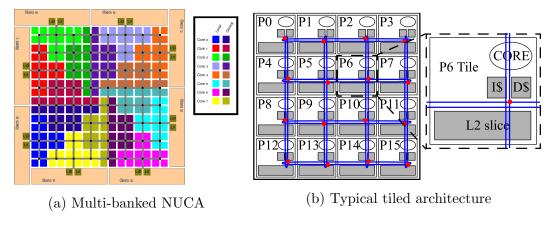

What makes big uniform caches inefficient is the fact that all accesses require the same large amount of time to be serviced, regardless of the data's physical location on the cache array. Ideally, we would like data that resides in the part of the cache that is physically located close to the processor to be accessed faster than data that resides physically farther from the processor. In order to achieve this goal, a complete shift in the cache architecture design paradigm was required. The previously single, monolithic chunk of cache is transformed to a finer-grained structure, as shown in Figure 2.1. More specifically, the last-level cache is composed by physically independent *banks*, which are evenly distributed across the die area. This design provides varying access latencies between the cores and the cache banks, depending on the physical distance between the requesting core and the cache bank where the requested data resides. Thus, we are led to a Non-Uniform Cache Access (NUCA) organization of the cache.

So, NUCA provides faster access to cache blocks in the banks that reside closer to the processor. For example, as suggested by Kim et al. [17] and

Figure 2.1: Level-2 Cache Architectures

illustrated in Figure 2.1b, the closest bank in a 16 MB, on-chip L2 cache built in a 50 nm process technology can be accessed in 4 cycles, while an access to the farthest bank might take up to 47 cycles. On the other hand, every access to a UCA of the same size would require a constant latency of 41 cycles. As access time is directly related to the block's placement, the placement is an important decision.

NUCA can be classified into two great categories:

- *Static NUCA*, which only places a block in a specific location in the cache .

- *Dynamic NUCA*, which supports a more flexible placement scheme for blocks by not limiting a block's placement to a single location.

### 2.1.1 Static NUCA

Figure 2.1b shows a banked NUCA cache, as opposed to the classic UCA shown in Figure 2.1a. This static NUCA design uses a two-dimensional switched network, permitting a large number of small, fast banks to be interconnected. Table 2.1 shows the performance metrics for this NUCA cache [17]. Unloaded latency values are estimated by Cacti and loaded latency values are the average of the experimental evaluation on a range of different workloads. Cacti provides three different values for the unloaded latency: min, max and average. This illustrates the nature of the NUCA: it allows accessing each bank at different speeds, proportional to the distance of the bank from the cache controller. Thus, the closest bank can be accessed in the minimum time, while an access to the farthest is the slowest. As shown in Table 2.1, not only does latency (both unloaded and loaded) scale much

better with cache size, but there is also a boost in IPC.

| Tech | L2               | Num.  | Unloaded Latency |        |        |     | Loaded  |      |

|------|------------------|-------|------------------|--------|--------|-----|---------|------|

| (nm) | Size             | Banks | bank             | $\min$ | $\max$ | avg | Latency | IPC  |

| 130  | 2MB              | 16    | 3                | 4      | 11     | 8   | 9.7     | 0.55 |

| 100  | 4 MB             | 32    | 3                | 4      | 15     | 10  | 11.9    | 0.58 |

| 70   | 8MB              | 32    | 5                | 6      | 29     | 18  | 20.6    | 0.62 |

| 50   | $16 \mathrm{MB}$ | 32    | 8                | 9      | 32     | 21  | 24.2    | 0.65 |

Table 2.1: Performance of NUCA organizations

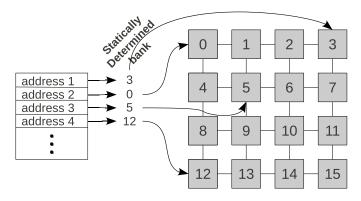

Apart from the varying access times, there are no functional differences between the UCA and the static NUCA. Block placement treats the cache as logically unified: a block will be placed in a location statically determined by its address. A block can only be placed in a single location during its lifetime. This, of course, imposes serious limitations: a frequently accessed block may be placed in a bank located far from the cache controller, thus suffering the overhead of a high access time everytime it is accessed. The block cannot be placed to any other bank, closer to its requester, in order to improve its access time, since its location in the cache is statically defined by its address. This limitation of the static NUCA gave birth to NUCA's next generation designs, the dynamic NUCA, which address the problems that rise from static placement.

### 2.1.2 Dynamic NUCA

Modern workloads already spend most of their execution time on on-chip cache accesses. Enabling the latency of a cache access to be possibly smaller than that of accessing a large unified cache is not enough. Even for the multi-banked design presented in the previous section, performance can still be improved by exploiting the fact that accessing closer banks is faster than accessing farther banks. Various strategies can be applied in order to maximize the number of accesses to local banks by allowing the cache to dynamically manage its contents. Ideally, frequently used data can be placed in the closest banks, or moved into them, using the interconnection of the cache banks. Of course, for a transition from a completely static configuration to a dynamic one, certain mechanisms have to be designed and implemented to enforce the new functionality. Thus, we move towards a new design of a dynamic NUCA. The physical layout described in Section 2.1.1 and shown in Figure 2.1b remains the same; what changes is the logic behind data placement in the cache array.

### 2.1.3 Policies of a NUCA design

A NUCA design can be characterized based on four policies which define its behavior:

- *Bank placement*, which determines the first location of data in the cache.

- Bank lookup, which defines the searching algorithm across the banks.

- *Bank migration*, which decides data movements between the NUCA's banks.

- *Bank replacement*, which deals with the evicted data and any actions required upon its eviction.

Static NUCA implements static placement of data (standard placement depending on its address), which also allows a simple static lookup mechanism, using the same static function that is used for placement. It also implements a classic replacement policy, e.g. LRU, and no migration of data at all. A data block is placed in a predefined, statically determined by its address, position and never moves until evicted.

At the other extreme, in a dynamic NUCA, a data block can be placed in *any* bank of the cache. This approach provides the greatest flexibility and unlocks the possibility for greater performance gains. However, such an extremely dynamic placement strategy comes at a cost. The overhead of locating a data block in the cache when it could be found *anywhere*, can be too large. Locating data blocks with no limitation on their possible location, requires a broadcast to all the banks for each access. That would be prohibitive in terms of both latency and energy. Therefore, placement is strongly paired with the lookup mechanism and the greatest challenge is developing hybrid solutions that lay somewhere between the static and the extremely dynamic policies, which would deliver high performance at an affordable cost.

## 2.2 Background - Related Work

### 2.2.1 NUCA for uniprocessors

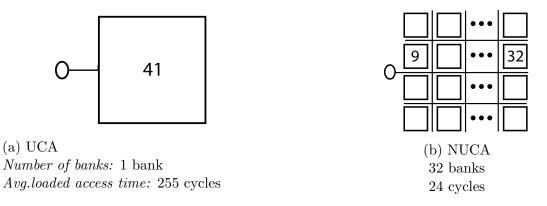

Kim et al. [17] proposed organizing the NUCA banks into *banksets*. In this organization, the multibanked cache is treated as a set-associative structure, where each set is spread across multiple banks and each bank holds one "way" of the set. The collection of banks used to implement this associativity is called a *bankset* and the number of banks in the set corresponds to the associativity. The primary distinction between this organization and a classic set-associative cache is that each way has a different access time.

Three different topological mappings of banksets were evaluated: simple, fair and shared mapping, which are also displayed in Figure 2.2. Each of the mappings has its own advantages and disadvantages. Simple mapping is the simplest but latencies to all bank sets are not the same, since some rows are closer to the cache controller than others. Fair mapping eliminates that problem at the cost of a more complex routing path by a better grouping of banks in each set, so that the average access time across all bank sets is equalized. Finally, the shared mapping, which is proved to be the best, attempts to provide fastest-bank access to all banksets by sharing the closest banks among multiple banksets.

Figure 2.2: Mapping bank sets to banks

Lookup policies for finding a data block in the cache were also investigated. There are two distinct search policies: the *incremental search*, in which all banks in the bankset are searched sequentially, and the *multicast search*, in which the requested address is multicast to all banks of the bankset. While the latter is significantly faster, it imposes great energy and network contention costs. However, the policy that was evaluated as the best one is a smart search mechanism that exploits the idea of *partial tag comparison*, proposed by Kessler et al. [16], which can be used to reduce both the number

of bank lookups and the miss resolution time. *Smart search* allowed nearly all cache misses to be detected without searching the entire bankset and displayed the best results among the search policies evaluated by Kim et al.

The migration mechanism proposed in that work is fairly simple, since it is tightly related to the organization of the banks in sets. When a hit occurs to a data block in one of the cache's banks, it is swapped with the corresponding block of another bank that belongs in the same bankset and is one step closer to the cache controller.

Finally, different approaches concerning the placement and replacement policies were investigated. A new block may be loaded close to the processor, displacing an important block, or in a distant bank, which would require several accesses before it is eventually migrated to the fastest banks. The replacement policy's decision involve what to do with the victim upon a replacement; two possible approaches are to simply evict the data from the cache (*zero-copy*) or to move the victim to a lower-priority bank (*one-copy*), replacing a less important line. After the evaluation, it was determined that the preferred solution is to place the incoming block in the bank close to the processor and apply the one-copy policy.

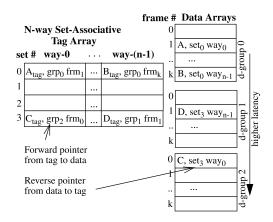

Chishti et al . [7] noticed that previously proposed NUCA designs did not fully exploit the non-uniformity in memory accesses, because of keeping data and tag placement coupled. This coupling results in having to tolerate multi-hop latencies to check for a miss, which is determined by accessing the tags. They also pointed out that NUCA can only place a few blocks within the closest banks with the lowest access times and must employ a high-bandwidth switched network to swap blocks within the cache for high perfor-

Figure 2.3: NuRAPID Cache

mance. To tackle these problems, they proposed the Non-uniform access with Replacement and Placement using Distance associativity (NuRAPID), which leverages sequential tag-data access to decouple data placement from tag placement. NuRAPID makes a distinction between tag and data placement: distance associativity is the placement of data at a certain distance (and latency) from the cache controller, while set associativity is the placement of tags within a set. Tags are placed in a centralized tag array close to the processor, which is smaller than even one data way. The cache's banks are grouped into distance groups (d-groups), which are used as *buckets*, and data is placed in them, decoupled from tags. What make this decoupling possible are a forward pointer, from the tag in the tag array to the data in the d-group, and a reverse pointer, which establishes the connection the other way around. Blocks can be promoted and demoted between faster and slower d-groups, while the tag array remains unchanged. Chishti et al. suggested that Nu-RAPID's data-tag decoupling enables flexible placement of the vast majority of frequently-accessed data in the fastest cache banks, with fewer swaps than the standard D-NUCA. As a result, NuRAPID provides both better performance and energy-efficiency.

### 2.2.2 NUCA for CMPs

NUCA designs described in section 2.2.1 assume a single cache controller as the only entry point to the cache. However, CMPs feature multiple cache controllers which represent individual entry points located all over the cache. Migration causes blocks that are requested by multiple processors at the same time to be pulled in multiple directions which can result in the block ending up in a non-optimal position. Therefore, simple migration mechanisms as the ones previously proposed, only work well in uniprocessor systems and are less effective in CMPs. Furthermore, the range of flexibility for the migration mechanism is more dependent on smart lookup techniques than its uniprocessor counterpart, since such searches are harder to implement in a CMP environment. Doubtlessly, CMPs present additional challenges to be addressed.

#### 2.2.2.1 Migration

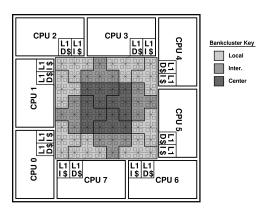

Beckmann and Wood [4] investigated NUCA policies for CMPs using the CMP-NUCA layout shown in Figure 2.4. They used this architecture to evaluate both a static NUCA (S-NUCA) and a dynamic NUCA (D-NUCA). In order to employ more flexible placement and migration policies, the banks were grouped in banksets, similar to the work by Kim et al. [17]. In addition, the banksets were also grouped in bankclusters, according to their proxim-

ity to the processors. The proposed placement policy is simple and static: blocks are initially allocated in the requesting core's corresponding bankset, according to their low-order bits. However, their investigation on migration policies provided some interesting results. While direct migration increases the number of local bankcluster hits for the requesting core, it also increases the proportion of costly remote hits by distant processors. Therefore, D-NUCA implements a *gradual migration* policy that moves blocks among the six bankcluster chain:

Consequently, in order for a block that is placed in processor's A local bankcluster to migrate to processor's B local bankcluster, five consecutive requests for the block have to be made by processor B.

This gradual migration allows blocks frequently accessed by one processor to congregate near that particular processor, while blocks accessed by many processors tend to move within the center banks. Based on this migration policy, hits are more likely to occur in one of the six bankclusters: on the requesting processor's local or inter bankclusters, or the four center bankclus-Therefore, the first phase of ters. the lookup policy is sending requests to these six bankclusters and if all six requests miss, the request gets broadcast to the rest of the bankclusters.

Figure 2.4: CMP-NUCA layout with bankcluster regions

An interesting characteristic of the migration policy proposed in that work is the *lazy migration* mechanism. Every pending migration gets delayed for a thousand cycles and cancelled if the block is accessed during that period by another processor. That way, more than 99% of *false misses*, i.e. where L2 requests fail to find a cache block because it is in transit from one bank to another, are avoided. Finally, Beckmann and Wood conclude that while block migration effectively reduces wire delay in uniprocessor caches, its capability to improve CMP performance relies on a - difficult to implement smart lookup mechanism. Furthermore, the large amount of inter-processor sharing that exists in many workloads, fundamentally limits the profit of block migration.

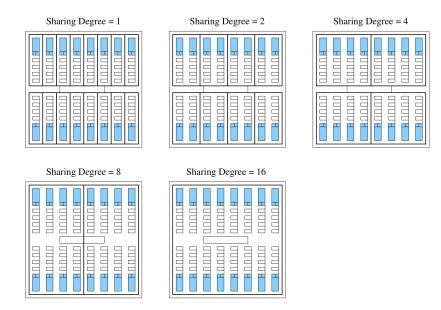

A few months later, Huh et al. presented their own NUCA design for CMPs [14], which was merely an extension of the first NUCA work for uniprocessor systems [17]. The proposed architecture included 16 processors and a very fine-grained L2 NUCA and introduced the concept of the *sharing degree*, which is defined as the number of processors sharing a given pool of cache. The NUCA can be utilized with a sharing degree of 1 as *unshared*, in which each processor has a private portion of the cache, with a sharing degree of 16 as *completely shared*, in which every processor shares the entire cache, and with any sharing other degree in between, as shown in Figure 2.5.

Figure 2.5: Sharing degree: 1, 2, 4, 8 and 16

The sharing degree is an important property of the NUCA design. Higher sharing degrees reduce cache misses, by providing greater effective cache capacity, since there are less data copies on the L2 cache. On the other hand, they lead to longer cache latencies, as the shared cache is larger than the individual private partitions. In addition, the data copies that occur on the different partitions require a L2 coherence mechanism. Thus, choosing the ideal sharing degree is a tradeoff between hit latency, hit rate, inter-processor communication and coherence maintenance overhead. The gap between the two extremes is significant: Huh et al. reported a 54% latency reduction with

Figure 2.6: D-NUCA Block Migration Policies

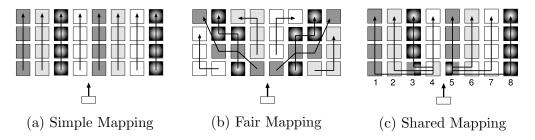

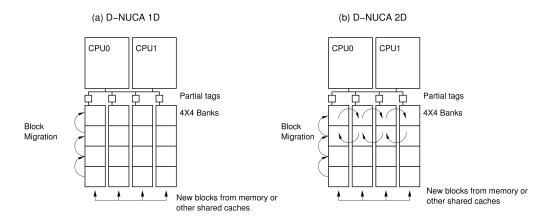

In order to achieve both reduced latency and misses, Huh et al. proposed a migration policy and the use of partial tag arrays to speed up the lookup. illustrated in Figure 2.6. The NUCA is logically grouped in columns and each column keeps a special buffer at its end, containing a partial tag array which tracks the state of blocks cached in that column. These partial tags help to detect L2 misses early and reduce the number of requests to banks. Regarding the migration mechanism, two different ones were proposed. The first policy allows blocks to migrate on the vertical direction only (D-NUCA 1D), while the second one allows migration on both directions (D-NUCA 2D), which gives blocks a greater movement freedom but requires a more complex search mechanism. To avoid pointless ping-ponging of data in the case of conflicting promotion caused by different cores asking for the same block, two-bit saturated counters were embedded in the cache tags, which allow a block to migrate only if the relevant counter for that moving direction is saturated. However, both migration mechanisms showed moderate performance improvement.

Huh et al. conclude that no single sharing degree provides the best performance for all the benchmarks. Based on their evaluation, the simplest design seems to be the best: an S-NUCA organization with a sharing degree of two or four. In addition, they point out that considering the complexity of a D-NUCA implementation and the extra energy consumption due to lookups, it is *unlikely* that implementing dynamic migration is justified for CMPs. However, they also argue that the D-NUCA results still hold promise and research should continue exploring ways to exploit flexible mapping.

#### 2.2.2.2 Replication

As shown in section 2.2.2.1, the consequence of a not fully-shared NUCA organization is that the effective capacity of the L2 cache shrinks and also a L2 coherence mechanism is required. On the other hand, there is also a benefit: access to the replicated data is faster, since the requester can always hit the closest of the copies. This realization led to a new trend in NUCA policies: controlled replication of data.

M. Zhang and K. proposed Victim Replication [24], a replication mechanism that handles data in the cache in such a way that the NUCA ends up as a dynamically self-tuning hybrid between private and shared caches. The Victim Replication mechanism is simple. When a processor misses in the shared cache, a block is brought in from memory and statically placed - according to its address - somewhere in the shared NUCA, known as the block's global location. The requested block is also directly forwarded to the local bank of the requesting processor. If the local bank's block is later evicted, a copy of the victim block is *probably* kept in the block's global location (if not already evicted), which will reduce subsequent access latency to the same block. A global block is never evicted in favor of a local replica; if that is not possible, no replica is made. Thus the cache's effective capacity does not shrink.

All L1 misses check the local L2 tags first and if a replica is found, the block gets invalidated and moved to its global location. In effect, Victim Replication builds a private victim cache in each local L2 cache, effectively reducing both on-chip communication delay and off-chip traffic. Victim replication manages to combine the advantages of private and shared caches, by implementing a simple and straightforward policy.

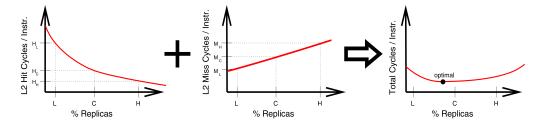

Although Victim Replication implements a simple mechanism that improves performance by replicating selected data, its replication policy is static and cannot dynamically adapt to different workload behavior. Beckmann and Wood proposed Adaptive Selective Replication (ASR), a mechanism that dynamically monitors workload behavior to control replication [3]. ASR exploits the fact that the most frequently requested L2 blocks are also the most frequently evicted L1 blocks and focuses on replicating shared readonly blocks, to avoid the overhead of a L2 coherence mechanism. The choice of the optimal level of replication is a tradeoff between lower hit times for replicated data and greater pressure on the cache, since more replicas reduce its effective capacity. When a L1 cache evicts a shared read-only block and the block is not found in the local L2 cache, the current replication probability determines whether to replicate the block locally. The replication probability is dynamically controlled. ASR monitors the replication's effectiveness and estimates the benefit and cost curves of increasing or decreasing the replication level. The benefit and cost curves are combined to form the *Replication Effectiveness* curve, as illustrated in Figure 2.7, which leads to the final decision for the optimal replication level. The evaluation of ASR showed that it provides better performance to a wider variety of workloads than previously proposed replication mechanisms and both the static shared and private NUCA organizations.

Figure 2.7: ASR computes the potential Replication Effectiveness curve (c) by estimating and combining the replication benefit (a) and cost (b)

### 2.2.2.3 Dynamic Placement

Optimal placement of blocks in the NUCA is very important, since more local hits can occur, which gets translated into performance. Kandemir et al. [15] claimed that an accurate placement decision cannot be taken during the first allocation of a block in the cache, therefore a migration-based design is needed. The scheme they proposed models the problem of optimal data placement in the L2 cache space as a two-dimensional "post office placement" problem.

Kandemir et al. stress that, whereas the private blocks dominate the requested blocks, most of the block accesses are to shared ones. Consequently, the placement of shared blocks in the caches significantly affects overall performance of diverse applications. Replicating these frequently used shared blocks would benefit hit times. However, maintaining multiple replicas within the L2 would require the implementation of L2 cache coherence mechanisms, which are undesirable in terms of complexity, energy and network contention. To avoid the overhead of a coherence mechanism, previous works suggested replicating exclusively read-only data. That approach bears two disadvantages: first, correctly and quickly identifying read-only cache blocks is not an easy task and, second, the majority of shared data for some workloads is read-write, thus it cannot be handled by these replication mechanisms. Without duplicating shared L2 cache lines, the only remaining option is to determine a single *ideal* position for each shared line.

To service the majority of cache lines, which are private, Kandemir et al. propose that all blocks should be initially placed in the local bank of the original requester. They rely on the migration mechanism to move the shared cache lines to a better location, later on. To avoid partitioning the NUCA to multiple private caches, thus reducing the utilization of the aggregate LLC space, an interesting *replacement* mechanism is proposed. The metric of *LLC miss intensity* is introduced for each processor, which also characterizes the processor's local tiles, addressed as the processor's cluster.

The LLC miss intensity of a processor is defined as the number of LLC misses that occur during a period of time, e.g. 10 million cycles, and represents the degree of the memory access intensity of the processor's current running thread. According to the miss intensity, which is constantly updated and periodically checked, the processor's cluster is assigned a *priority*. Thus, when a cache line is evicted from a cluster that has high priority, it has higher ability of keeping its victim on-chip by checking more clusters' status and asking one of them to accommodate this victim if possible, as shown in Figure 2.8. On the other hand, if the evicting cluster has the lowest

Figure 2.8: Determining the eviction based on cluster priorities

priority, the victim will be directly evicted from the cache. On a last note, a very interesting extension of this priority schema is enforcing Quality of Service for specific applications, by allowing the Operating System or the user to directly set thread priorities, i.e. to set processor clusters' priorities.

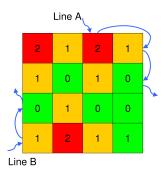

Since data can be placed anywhere in the cache, the lookup mechanism employs a multi-step checking scheme that first checks the local and neighboring clusters, and then sends requests, if necessary, to remote clusters, until it is determined whether we have an L2 cache hit or miss. The migration mechanism tries to optimize accesses to shared L2 cache lines, by placing the hot lines into ideal positions. To achieve this, each cache line observes the number and origin of requests by processors over a period of time. When the number of total accesses surpasses a certain threshold that characterizes a cache line as "hot", the migration is triggered and the line's target is computed as a weighted median that takes origin and frequency of requests as input.

The evaluation of the design proposed by Kandemir et al. showed that this approach leads to both reduced L2 latencies and IPC improvements on a diverse set of benchmarks.

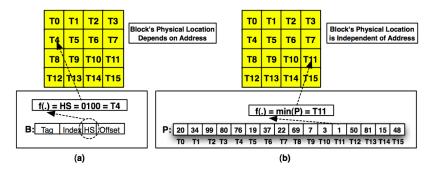

Many of the proposed NUCA designs can result in banks that have their capacity pushed at its limits, while others banks may be almost empty. Hammoud et al. in their *Cache Equalizer* work [10] proposed a solution to this problem. Temporal pressure at the on-chip L2 cache which is also the LLC, is continuously collected at a group - comprised of cache sets - granularity and periodically recorded at the memory controllers to guide the placement process. Specifically, a pressure array is maintained at the memory controllers of the CMP system. Each slot on the array corresponds to a L2 bank and represents the pressure on that bank, as shown in Figure 2.9.

Figure 2.9: Address-based versus pressure-aware placements. (a) Shared scheme strategy. (b) Pressure-aware strategy

On a L2 miss, the main memory is accessed, the pressure array is probed and the block is placed in the tile that exhibits the minimum pressure. Obviously, placing a block to a tile according to the tiles' pressure means that data placement is not statically determined. Thus, it is not possible to measure cache misses in a meaningful way at L2 banks to keep track of each tile's pressure. Therefore, the pressure value is quantified as the number of lines yielding cache hits during a time interval.

The lookup mechanism implemented was the cache-the-cache-tag (CTCT) [9] policy. CTCT stores two corresponding tracking entries in special tables (TR), at the first-requesting and the static home tiles of the block being placed. Subsequently, when the first-requesting core requests the block again in the future, it locates it quickly with a lookup to the local TR. If another core requests the block, it gets located through the TR of the static home tile, which points to the bank holding the data.

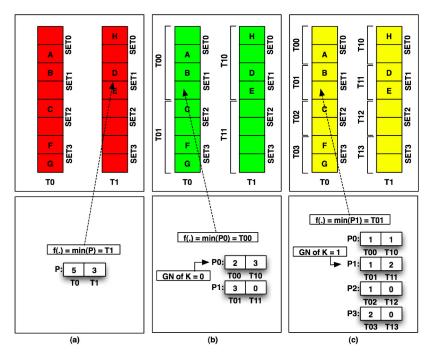

Figure 2.10: Placing block K (with index = 1) using the proposed pressureaware group-based placement strategy with various granularities. (a) 1-group. (b) 2-group. (c) 4-group

Hummad et al. proposed their own pressure-aware placement by refining the mechanism that keeps track of the banks' pressures. They noticed that collecting pressures at a bank granularity might be relatively imprecise. Therefore, they divided each cache bank into a number of groups in order to gather more detailed, and thus more accurate, pressures from individual sets or groups of sets. Figure 2.10 demonstrates the group-based placement strategy

using different granularities. Over the evaluation procedure, Cache Equalizer was tested with various group granularities and further optimizations using a full system simulator. The results showed that Cache Equalizer outperforms all previously proposed pressure-aware designs and reduces the cache misses of a shared NUCA design by an average of 13.6% and by as much as 46.7%.

Hardavellas et al. [11] recognize that access to shared blocks may benefit from migration, but the complex lookup mechanism that a migration mechanism demands is unjustifiable. Instead, in their *Reactive NUCA* work, they focus on efficient placement of data. The proposed scheme of R-NUCA is based on the observation that the cache access patterns of a range of server and scientific workloads can be classified into distinct classes, where each class is amenable to different block placement policies. L2 accesses naturally form three clusters with different distinct characteristics: instructions that are read-only and are shared by all cores in server workloads, shared data that are usually read-write and private data.

- Private blocks are prime candidates for allocation near the requesting tile, ensuring low access time. Since they are always used by the same core, no coherence mechanism is required.

- Instructions are prime candidates for replication across multiple tiles and, again, no coherence mechanism is required since they are only being read. However, uncontrolled replication of instructions is undesirable, since that would increase the cache's capacity pressure and the off-chip miss rate. Therefore, replication is done at a coarser granularity: neighboring slices of the NUCA are logically divided into *clusters*, and replication of instructions is being done at the granularity of clusters instead of individual L2 slices.

- The rest of the shared blocks, i.e. read-only non-instructions and readwrite, could also benefit from replication, but that would require a coherence mechanism which, as already stated, is undesirable. Placing this category of data optimally is a challenging problem. However, in server workloads on which R-NUCA focuses, shared data blocks are universally accessed. Therefore, R-NUCA distributes shared data evenly across all tiles, using standard address interleaving. This way, replication and the need for a coherence mechanism are avoided and lookup is trivial and fast, since a block's address uniquely determines its location.

Classification of blocks. Memory accesses are classified at the time of a TLB

miss. Classification is performed at the OS-page granularity, and communicated to the processors using the standard TLB mechanism. Requests from L1 instruction caches are immediately classified as instructions. All other requests are classified as data requests, and the OS is responsible for distinguishing between private and shared data accesses. Upon the first access, a core encounters a TLB miss and traps to the OS. the OS marks the faulting page as private and the core-ID of the processor is recorded. On a subsequent TLB miss to the page, the OS compares the core-ID in the page table entry with the core-ID of the core encountering the TLB miss. In case of a mismatch, the page is shared by multiple threads an must be reclassified as shared.

In conclusion, R-NUCA avoids block migration in favor of intelligent block placement, eliminating the need for complex lookup algorithms and achieving a 14% performance improvement on average over competing designs, for each workload tested.

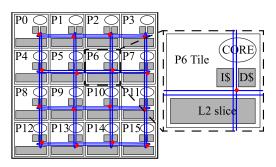

Another major difference between R-NUCA and the other works presented here, is that R-NUCA assumes a *tiled* CMP architecture. As shown in Figure 2.11b, the chip consists of multiple tiles, each comprising a processor core, L1 instruction and data caches, a shared-L2 cache slice and network router/switch, which are replicated to fill the die area. On the other hand, the most commonly used NUCA is a multi-banked cache, as the one shown in 2.11a. The cache is split into a lot more banks than the existing processors, thus there are banks that are local to a processor and others that are placed in the center, equally far from all of the chip's processors. Featuring such a great number of banks imposes greater design and control complexities but at the same time provides greater flexibility. For instance, since there are banks that do not belong to any processor, i.e. they are not local to any, are the ideal location for data that is equally shared by all cores.

#### 2.2.2.4 Other approaches for NUCA designs

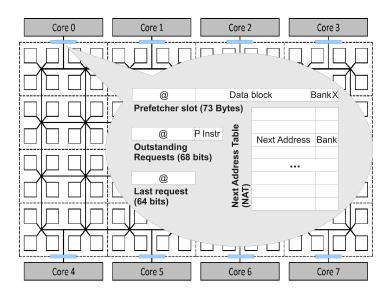

The *Migration Prefetcher* by Lira et al. [18] introduces an important twist in the migration mechanism that differentiates it from previous proposals. Standard migration attempts to move data to its optimal position within the cache, but still almost half the hits occur within non-optimal banks, since a number of hits must occur before migration is triggered. Inspired by the functionality of the typical data prefetchers, Lira et al. complement the migration scheme with a prefetching technique, in order to recognize access patterns and foretell data migrations, moving data blocks closer to their requester

Figure 2.11: NUCA Architectures

in advance of them being requested. Regular prefetchers and the Migration Prefetcher are orthogonal mechanisms that can be used simultaneously.

Figure 2.12: Additional structures introduced to enable migration prefetching

The additional structures introduced to enable migration prefetching are shown in Figure 2.12 and include the *prefetcher slot* (PS), which stores the prefetched data, a structure to manage the *outstanding prefetching request* and the *last request* sent from the L1 and the *Next Address Table* (NAT), which keeps track of the data access patterns. For each address requested, the NAT stores the next address to be accessed. The prefetching technique is speculative: it keeps track of access patterns in the NAT and when a known pattern starts, the prefetcher predicts the next address and then fetches it in the PS. If the prediction was correct, the latency of the access to the prefetched data will be reduced, since it will hit in the local PS instead of a remote bank. When there is a hit in the prefetcher, the cache controller sends the data block to the L1 and then notifies the owner bank that data should migrate one step closer to the requesting core. Lira et al. used *gradual promotion* [4, 17] in their work, but the Migration Prefetcher can be implemented in conjunction with any other migration technique.

The prefetcher is also used to predict the position of data in the NUCA. Each line in the NAT keeps track of the last bankcluster that held the data belonging to the corresponding address. Thus, whenever a lookup is required, a request is sent only to the local bankcluster and the bankcluster suggested by the NAT entry, significantly reducing the network-on-chip traffic as opposed to the contention that a multicast would cause. This lookup method achieved an average accuracy of 70% over the benchmarks selected.

The evaluation procedure showed further that a realistic implementation of the Migration Prefetcher reduces the average NUCA latency by 15%, which translates into an overall speedup of 4% across all benchmarks tested and up to 17% for some. A significant reduction in dynamic energy consumption is also achieved.

### 2.2.3 To migrate or not to migrate?

As we have seen throughout section 2.2, the first works on NUCA designs investigated migration mechanisms and concluded that an efficient migration mechanism holds great promises for performance improvement in NUCAs [7, 17]. Many later works supported this suggestion and focused on developing efficient migration mechanisms [4, 18, 19]. On the other hand, it was claimed that the performance gains by migrations in the NUCA do not justify the complexity and energy overhead of implementing a migration mechanism [11, 14]. One of the aims of this study is to contribute to the clarification of this still ongoing controversy.

# Chapter 3

## Tools used

Computer architects have long relied on software simulation to evaluate the functionality and performance of a proposed design. Furthermore, in order to realistically estimate whether the proposed design will be efficient in real-life applications, widely accepted benchmarks are used for its evaluation. In this chapter, the simulation tools and benchmarks that are used in this study will be reviewed.

## 3.1 Introduction

Software simulation is the only solution for computer architects to evaluate a new design without having to proceed to a time-consuming and expensive hardware implementation. Unfortunately, though, this poses a great bottleneck, since cycle-accurate simulators are several orders of magnitude slower than real hardware. In addition, the growing levels of integration in chip design result in significant increases in computer system size and complexity, thus also increasing the simulator's complexity and the simulation's duration. For instance, simulating a multiprocessor instead of a uniprocessor system does not only suffer the direct overhead of a larger number of simulated cores. It is also essential that additional, complex mechanisms are accurately simulated, such as the cores' interconnection and the coherence mechanism.

Moreover, in order for benchmarking software to provide reliable results, a simulator must be as accurate as possible. This means that simulating the system's basic structures, such as the processors and memory hierarchy, is not enough. A full-system simulation is required, including the simulation of peripheral devices and OS code.

For the above reasons, the simulation throughput is very low, which makes cycle-accurate, full-system simulations especially prohibitive for large-scale multiprocessor systems, because the simulation turnaround for these systems grows almost exponentially with the number of processors. Slow simulation has barred researchers from attempting complete benchmarks and input sets or realistic system sizes on detailed simulators.

## 3.2 SimFlex

The *SimFlex* project [1, 12] was launched by Carnegie Mellon's CALCM team, in order to provide efficient solutions to the afore-mentioned problems of software simulation. It has developed simulation tools as well as a measurement methodology to enable fast, accurate, and flexible performance evaluation of uni- and multiprocessor systems running unmodified commercial applications. SimFlex is proceeding along two synergistic fronts:

- *SMARTS* applies rigorous statistical sampling theory to reduce simulation turnaround by several orders of magnitude, while achieving high accuracy and confidence in estimates.

- *Flexus* is a powerful and flexible simulator framework that allows fullsystem simulation that relies heavily on well-defined component interface models to facilitate both model integration and compile-time simulator optimization.

SimFlex combines SMARTS' sampling, to choose application subsets for measurement, with reusable checkpoints of system state, to enable rapid simulation of the selected measurement. Together, these techniques enable 10,000 times reduction in simulation time relative to cycle-accurate simulation without sampling and up to 1000-way simulation parallelism over a cluster of simulation hosts.

### 3.2.1 SMARTS

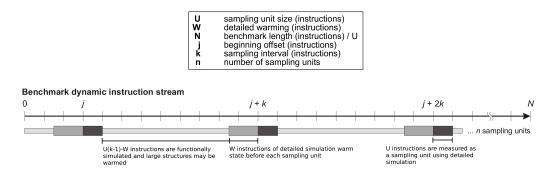

The Sampling Microarchitecture Simulation (SMARTS) framework is an approach to enable fast and accurate performance measurements of full-length benchmarks [23]. It prescribes a statistically sound procedure for configuring a systematic sampling simulation run to achieve a desired quantifiable confidence in estimates. The SMARTS framework was developed in order

to address the issues responsible for the intolerably long software simulation durations. It manages to do so, by selectively measuring in detail only an appropriate benchmark subset.

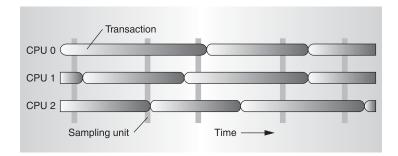

Unlike prior approaches to simulation sampling, the SMARTS framework prescribes an exact and constructive procedure for selecting a minimal subset from a benchmarks instruction execution stream to achieve a desired confidence interval. It uses a measure of variability, i.e. the coefficient of variation, to determine the optimal sample that captures a programs inherent variation. An optimal sample generally consists of a large number of small sampling units. Unbiased measurement of sampling units as small as 1000 instructions is possible by applying careful functional warming – maintaining large microarchitectural state, such as branch predictors and the cache hierarchy – during fast-forwarding between sampling units. Figure 3.1 graphically illustrates how SMARTS functions. The simulation has three distinct phases:

- 1. Fast functional-only simulation of [U(k-1) W] instructions

- 2. Detailed simulation of W warming instructions, without measurement

- 3. Detailed simulation and measurement of U instructions

As shown in [23], SMARTS' primary contributions are the following:

• **Optimal sampling:** Simulations using the SMARTS framework achieve an average error of only 0.64% on CPI and 0.59% on EPI (energy per instruction) by simulating fewer than 50 million instructions in detail for each of the 41 SPEC2K benchmarks tested.

Figure 3.1: Systematic sampling in SMARTS

• Simulation speedup: On a 2 GHz Pentium 4, SMARTSim can achieve average speedups of 35 and 60 relative to *sim-outorder* for 8-way and 16-way super-scalar processor models, respectively. Sim-outorder was one of the most widely used simulators at the time the SimFlex project was launched.

#### 3.2.2 Flexus

*Flexus* is a family of component-based C++ computer architecture simulators that enables full-system timing-accurate simulation of uni- and multiprocessor systems running unmodified commercial applications and operating systems.

Flexus encompasses both a simulation infrastructure and default simulation models. A simulator is composed of individual modules that are hooked together during compilation. A module is often the equivalent of a single hardware structure - for example, a branch predictor or a cache. A key strength of Flexus is its isolation of components: one implementation of a particular module can be swapped for a different implementation without requiring changes to any other modules.

This flexibility also allows a simulator to be tailored to the needs of a specific research hypothesis. If memory system performance is being evaluated, a simple bandwidth-based processor pipeline might be sufficient. Conversely, a study that closely examines microarchitecture could employ a simple memory model. The Flexus core provides services, such as scheduling and statistics, that are common and useful to all simulators.

Flexus builds on *Virtutech Simics* [20], enhancing its functionality with advanced timing models. Simics enables full-system simulation. It is a simulator that allows unmodified commercial operating systems and applications to boot and run. However, Simics provides only functional simulation; it does not attempt to model the passage of time accurately. Flexus hooks into Simics and monitors the instruction stream that the simulated system would executes. In addition, Flexus can control Simics' timing, so as to model outof-order effects and speculative techniques.

Flexus is designed to support the simulation sampling and checkpointing methodologies developed by the SimFlex research project. The keys to this support are *flexpoints*, checkpoints that store the snapshots of the state of Flexus components alongside Simics checkpoints of programmer-visible state. Flexus' component-based design enables easy creation of several components that all model the same hardware at various levels of timing fidelity. These components all share the same format for storing state in flexpoints. This way, a simple, fast simulator can rapidly construct a flexpoint library, which can then be measured using a more detailed simulator.

For the purposes of this study, Flexus 4.0.0 is used, which was the latest release at the time. Flexus 4.0.0 includes the following simulation models:

- Uniprocessor simulators

- UP.Trace: A non-timing uniprocessor simulator

- UP.OoO: Out-of-order uniprocessor simulator

- UP.Inorder: In-order uniprocessor simulator

- Multiprocessor simulators

- CMP.L2Shared.Trace: A non-timing chip-multiprocessor simulator with shared L2

- CMP.L2SharedNUCA.Inorder: In-order chip-multiprocessor, private L1s, shared NUCA L2, based loosely on Compaq Piranha

- CMP.L2SharedNUCA.OoO: Similar to CMP.L2SharedNUCA. Inorder with out-of-order processor cores

- CMP.MT4.L2Shared.Trace: A non-timing chip-multithreaded simulator

- CMP.MT4.L2SharedNUCA.OoO: Out-of-order chip-multithreaded processor with private L1s and shared NUCA L2

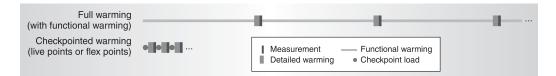

There are two distinct categories of simulators: the trace and the timing simulators. Each timing simulator has a corresponding trace simulator. The trace simulators can be used to study cache miss rates but their most significant purpose is to construct flexpoints, which in turn will be used by the timing simulators. Flexpoints reduce timing simulation duration significantly. As illustrated in Figure 3.2, a flexpoint load can replace a very long functional warming period that precedes a measurement point. The flexpoint functionality and creation procedure are further explained in Section 3.3.

In this study, CMP.L2Shared.Trace simulator has been used for flexpoint generation and the CMP.L2SharedNUCA.OoO simulator for the timing simulation. CMP.L2SharedNUCA.OoO is a timing-accurate simulator simulates CMP systems with a shared L2 Tiled Cache (NUCA) as the last cache

Figure 3.2: Warming approaches for simulation sampling. Checkpointed warming greatly accelerates simulation sampling while maintaining the same accuracy as full warming.

level, using processor cores which support out-of-order instruction execution. The full-system timing simulation includes cores, the whole memory hierarchy and their interconnection network.

## **3.3** The experimental procedure

Prior to recording any results during a timing simulation, functional warming is required in order to acquire an accurate performance estimation with SMARTS. Functional warming dominates simulation time because SMARTS must functionally simulate the entire benchmark's execution, even though it will simulate only a tiny fraction of the execution using detailed microarchitecture timing models. Functional warming may occupy more than 99 percent of the simulation runtime. Furthermore, functional warming requires simulation time proportional to benchmark length rather than sample size. As a result, the overall runtime of a SMARTS experiment remains constant even when we relax the statistical confidence requirements by reducing the measured sample size.

*Flexpoints* provide an alternative to functional warming that reduces simulation turnaround time without sacrificing accuracy. A flexpoint stores the necessary data to reconstruct warm state for a simulation sampling execution window upon loading it. Checkpoint implementations of most modern computer architecture simulators have two limitations:

- They don't provide complete microarchitectural model state.

- They cannot scale to the required checkpoint library size (about 10,000 checkpoints per benchmark), which would require multiple terabytes of storage.

Flexpoints manage to address both limitations by storing only selected microarchitectural state in flexpoints. The key challenge lies in storing microarchitectural state such that flexpoints can still simulate the range of microarchitectural configurations of interest. Fortunately, with the exception of the branch predictor and memory hierarchy, most microarchitectural state can be reconstructed dynamically with minimal simulation, i.e. a few thousand instructions of detailed warming, and thus needs not be stored. The size of conventional checkpoints is shrinked by three orders of magnitude through storing only the subset of state necessary for limited execution windows in the flexpoints. Figure 3.2 illustrates how flexpoints replace functional warming.

### 3.3.1 Preparing a new workload

To prepare a workload for simulation, we must investigate its performance variability to design an optimal sample - one that minimizes total simulation time for a desired confidence level. Then we construct a flexpoint library for the optimal sample. The following steps detail how we construct these libraries [22].

- 1. Create preliminary sample of flexpoints. First, we construct a small preliminary sample, for example 30 flexpoints, which we use to characterize the applications variability and warming requirements. Although this sample is insufficient to provide high-confidence simulation results, it typically provides a good estimate of target metric variance.

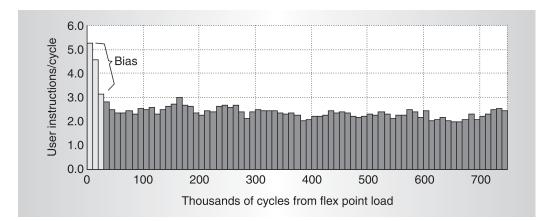

- 2. Determine detailed warming requirement. The preliminary sample is measured for intervals several times longer than our expected detailed warming at a measurement granularity several times finer than our expectations for sampling unit size. Using these extended, fine-grained measurements, we perform the empirical warming analysis illustrated in Figure 3.3, which helps us determine the required length for the detailed warming.

- 3. Create flexpoint library. Now that we have a desired sample at hand, we can launch the flexpoint creation to spread the final sample over a known-representative execution interval. If the workload we investigate has regions of execution with different characteristics, we have to make sure to create a range of flexpoints over all of these different regions, in order to capture the full spectrum of the workload's behavior. Flexpoint generation can be done using one of Flexus' Trace simulators. Since all of our workloads are CMP workloads, we used the CMP.L2Shared.Trace simulator for this matter.