NATIONAL TECHNICAL UNIVERSITY OF ATHENS SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING DIVISION OF COMPUTER SCIENCE

# Design and Implementation of a Versatile Hardware Crypto IP for Symmetric and Asymmetric Algorithms

DIPLOMA THESIS

NIKOLAOS A. EFTAXIOPOULOS - SARRIS

GEORGIOS D. ZERVAKIS

Supervisor: Kiamal Z. Pekmestzi

Professor

Athens, October 2012

ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ Σχολή Ηλεκτρολογών Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών

# Σχεδίαση και Υλοποίηση Κυκλώματος επί Ψηφίδας για Αλγόριθμους Κρυπτογραφίας Συμμετρικού και Ασύμμετρου Κλειδιού

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

ΝΙΚΟΛΑΟΣ Α. ΕΥΤΑΞΙΟΠΟΥΛΟΣ - ΣΑΡΡΗΣ

ΓΕΩΡΓΙΟΣ Δ. ΖΕΡΒΑΚΗΣ

**Επιβλέπων:** Κιαμάλ Ζ. Πεκμεστζή

Καθηγητής

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 30<sup>η</sup> Οκτωβρίου 2012.

..... Κιαμάλ Πεκμεστζή Καθηγητής ..... Δημήτριος Σούντρης Επίκουρος Καθηγητής ..... Γεώργιος Οικονομάκος Λέκτορας

Αθήνα, Οκτώβριος 2012

.....

ΝΙΚΟΛΑΟΣ Α. ΕΥΤΑΞΙΟΠΟΥΛΟΣ – ΣΑΡΡΗΣ ΓΕΩΡΓΙΟΣ Δ. ΖΕΡΒΑΚΗΣ

Διπλωματούχοι Ηλεκτρολόγοι Μηχανικοί και Μηχανικοί Υπολογιστών Ε.Μ.Π.

# Copyright © NIKOAAO $\Sigma$ EYTAEIOΠΟΥΛΟ $\Sigma$ – ΣΑΡΡΗ $\Sigma$ , 2012 Copyright © ΓΕΩΡΓΙΟΣ ΖΕΡΒΑΚΗ $\Sigma$ , 2012

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# **Table of Contents**

| Al | bstract | t           |                                                | 9  |

|----|---------|-------------|------------------------------------------------|----|

| Ke | ey Wo   | r <b>ds</b> |                                                | 10 |

| П  | ερίληψ  | νη          |                                                | 11 |

| Λŧ | έξεις - | Κλειδ       | λά                                             | 12 |

| 1  | Cry     | ptogr       | aphy                                           | 13 |

|    | 1.1     | Intro       | oduction                                       | 13 |

|    | 1.1     | .1          | Symmetric-key Cryptography                     | 14 |

|    | 1.1     | .2          | Public-key Cryptography                        | 15 |

|    | 1.1     | .3          | Cryptanalysis                                  | 17 |

|    | 1.1     | .4          | Legal Issues                                   | 19 |

|    | 1.2     | Tech        | hnical Terms                                   | 19 |

|    | 1.3     | Sym         | metric-key Cryptography                        | 20 |

|    | 1.3     | .1          | Data Encryption Standard (DES)                 | 20 |

|    | 1.3     | .2          | Advanced Encryption Standard (AES)             | 27 |

|    | 1.3     | .3          | International Data Encryption Algorithm (IDEA) | 35 |

|    | 1.3     | .4          | Block Cipher Operation Modes                   | 39 |

|    | 1.3     | .5          | Applications                                   | 48 |

|    | 1.4     | Pub         | lic-key Cryptography                           | 51 |

|    | 1.4     | .1          | RSA                                            | 52 |

|    | 1.4     | .2          | Applications                                   | 56 |

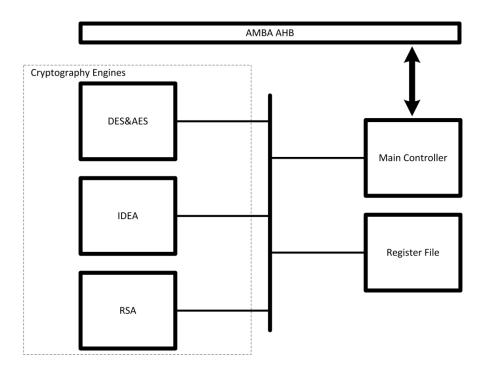

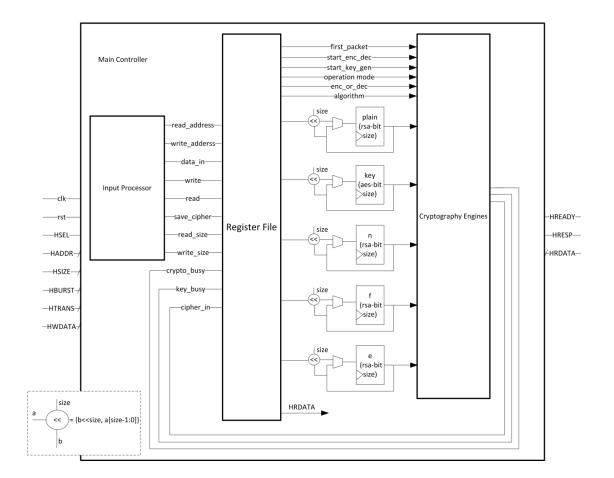

| 2  | Cry     | pto A       | rchitecture                                    | 59 |

|    | 2.1     | Intro       | oduction                                       | 59 |

|    | 2.2     | Cryp        | oto Components                                 | 60 |

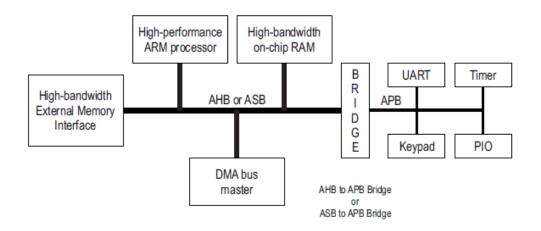

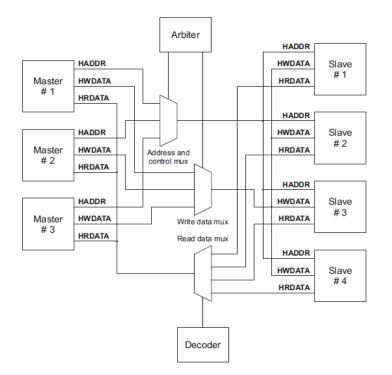

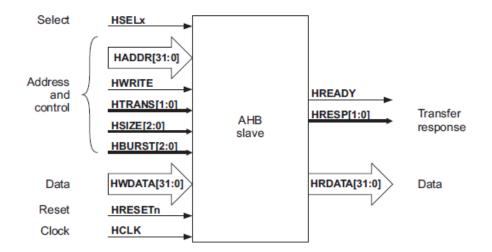

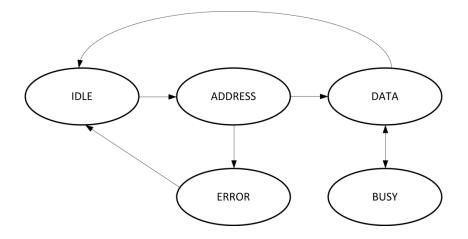

|    | 2.2     | .1          | AMBA AHB Interface                             | 60 |

|    | 2.2     | .2          | Main Controller                                | 66 |

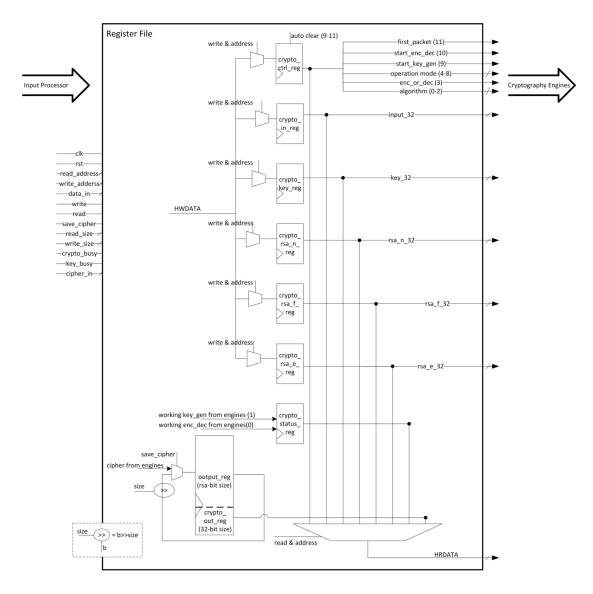

|    | 2.2     | .3          | Register File                                  | 69 |

|               | 2.2.  | 4     | Cryptography Engines                                  | 74  |

|---------------|-------|-------|-------------------------------------------------------|-----|

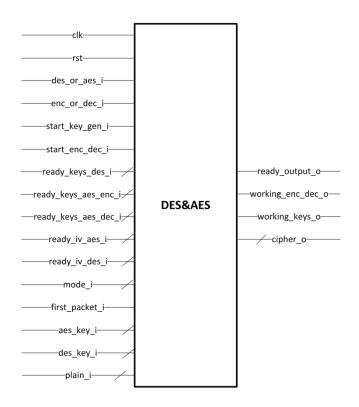

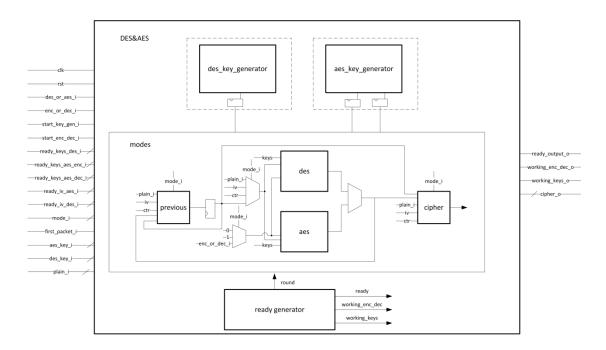

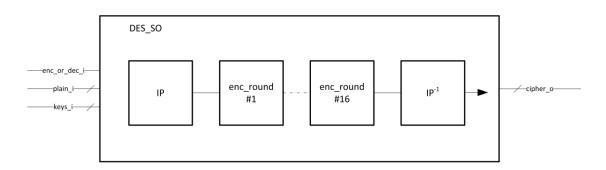

| 3             | DES   | & AE  | S Engine                                              | 75  |

|               | 3.1   | Intro | oduction                                              | 75  |

|               | 3.2   | Con   | figuration Parameters                                 | 75  |

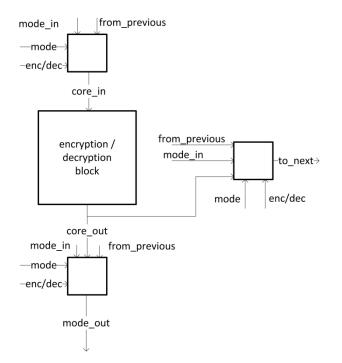

| 3.3           |       | Imp   | ementation                                            | 76  |

|               | 3.3.  | 1     | General Description                                   | 76  |

|               | 3.3.2 |       | Pin Description                                       | 77  |

|               | 3.3.  | 3     | Process of Key Generation and Encryption / Decryption | 79  |

|               | 3.3.  | 4     | Algorithmic Details                                   | 79  |

|               | 3.3.  | 5     | Implementation Details                                | 82  |

|               | 3.3.  | 6     | Block Diagrams                                        | 84  |

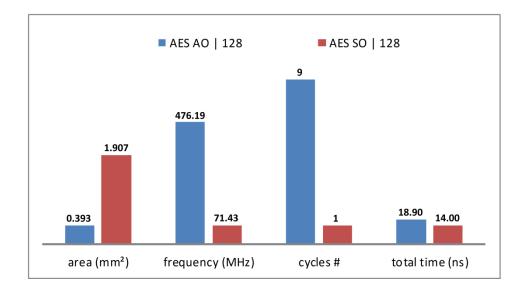

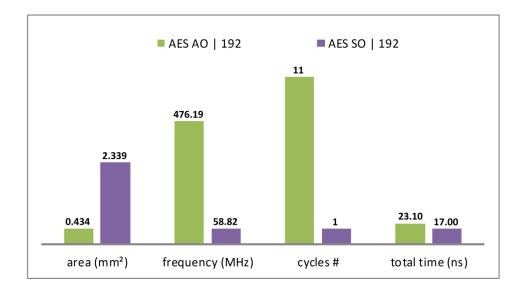

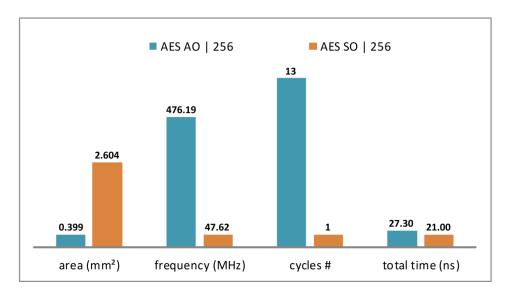

|               | 3.4   | Imp   | ementation Results                                    | 87  |

| 4 IDEA Engine |       | A Eng | ine                                                   | 91  |

|               | 4.1   | Intro | oduction                                              | 91  |

|               | 4.2   | Con   | figuration Parameters                                 | 91  |

|               | 4.3   | Imp   | lementation                                           | 92  |

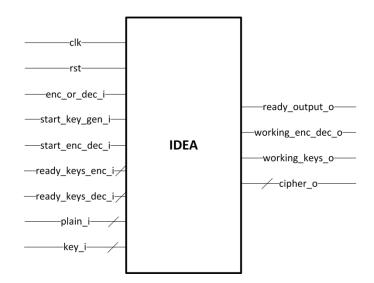

|               | 4.3.  | 1     | General Description                                   | 92  |

|               | 4.3.  | 2     | Pin Description                                       | 93  |

|               | 4.3.  | 3     | Process of Key Generation and Encryption / Decryption | 94  |

|               | 4.3.  | 4     | Algorithmic Details                                   |     |

|               | 4.3.5 |       | Implementation Details                                |     |

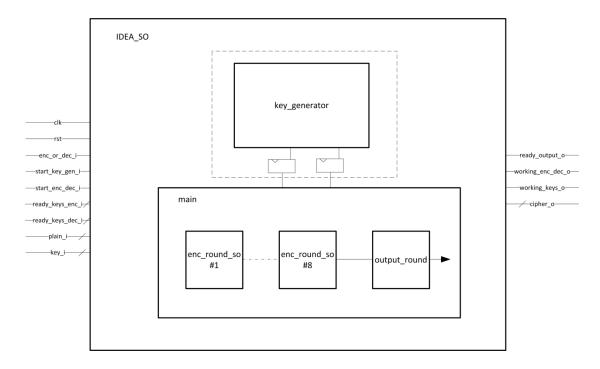

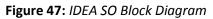

|               | 4.3.  | 6     | Block Diagrams                                        | 97  |

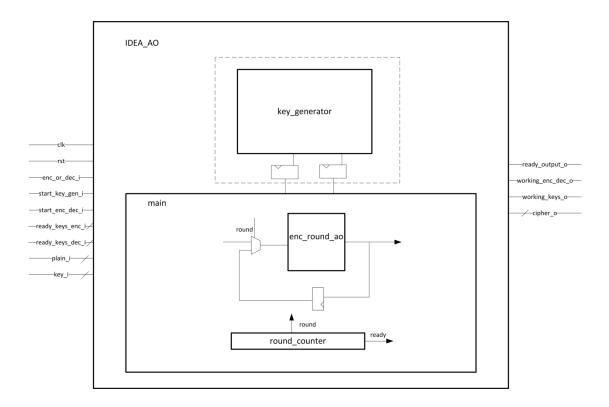

|               | 4.4   | Imp   | lementation Results                                   |     |

| 5             | RSA   | Engi  | ne                                                    | 101 |

|               | 5.1   | Intro | oduction                                              | 101 |

|               | 5.2   | Con   | figuration Parameters                                 | 101 |

|               | 5.3   | Imp   | ementation                                            | 102 |

|               | 5.3.  | 1     | General Description                                   | 102 |

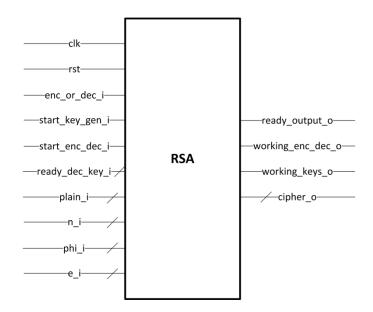

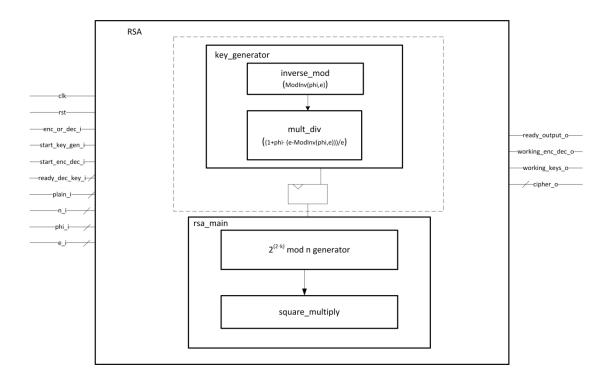

| 5.3.2             | Pin Description                                           |  |  |  |  |

|-------------------|-----------------------------------------------------------|--|--|--|--|

| 5.3.3             | Process of Key Generation and Encryption / Decryption 104 |  |  |  |  |

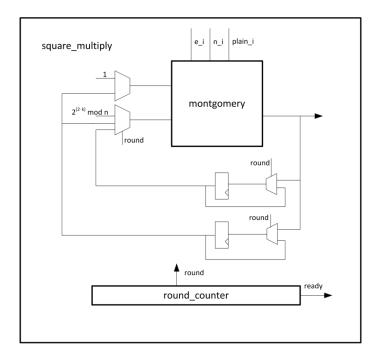

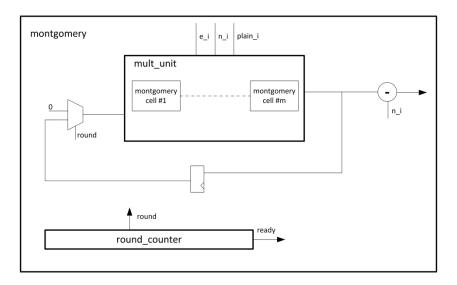

| 5.3.4             | Algorithmic Details 104                                   |  |  |  |  |

| 5.3.5             | Implementation Details 110                                |  |  |  |  |

| 5.3.6             | Block Diagrams 111                                        |  |  |  |  |

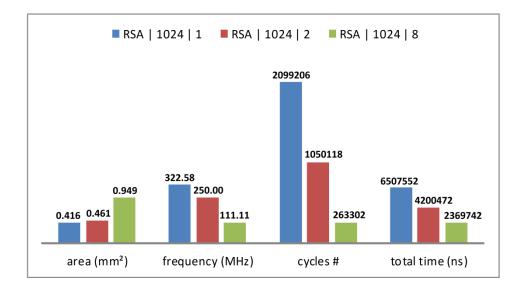

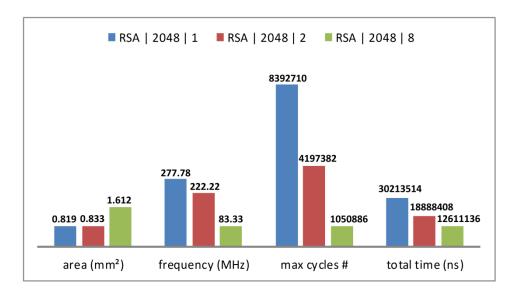

| 5.4 Imp           | plementation Results                                      |  |  |  |  |

| 6 IP Verifi       | cation 117                                                |  |  |  |  |

| 6.1 Inti          | oduction                                                  |  |  |  |  |

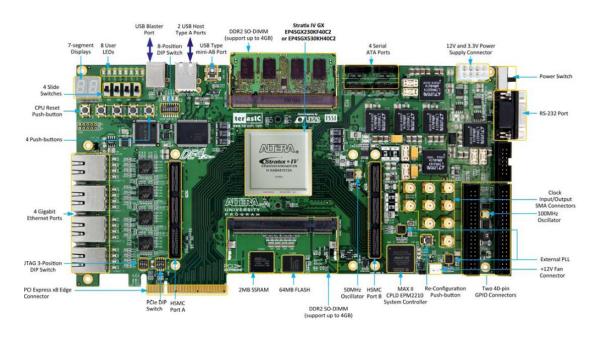

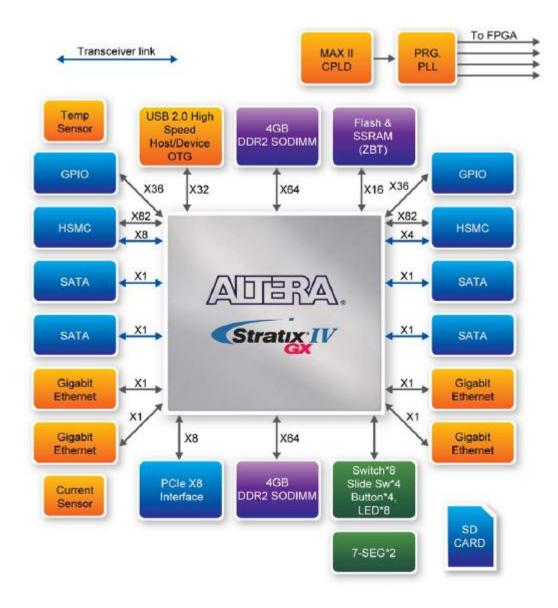

| 6.2 FPC           | GA Platform 117                                           |  |  |  |  |

| 6.2.1             | Key Features 117                                          |  |  |  |  |

| 6.2.2             | Peripherals 118                                           |  |  |  |  |

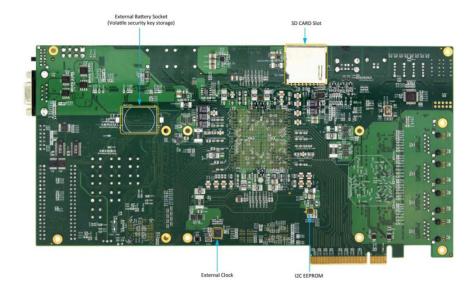

| 6.2.3             | Board Overview 119                                        |  |  |  |  |

| 6.2.4             | Block Diagram 120                                         |  |  |  |  |

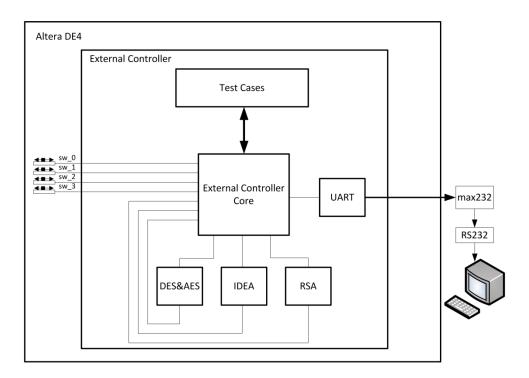

| 6.3 Ext           | ernal Controller 121                                      |  |  |  |  |

| Conclusion        |                                                           |  |  |  |  |

| Appendix          |                                                           |  |  |  |  |

| Basic Table       | es Used in DES Algorithm 125                              |  |  |  |  |

| Basic Table       | es Used in AES Algorithm 130                              |  |  |  |  |

| List of Figure    | ion                                                       |  |  |  |  |

| List of Tables141 |                                                           |  |  |  |  |

| References        |                                                           |  |  |  |  |

# Abstract

This diploma thesis was developed in the Microprocessors and Digital Systems Lab of National Technical University of Athens. As we attended the courses of this lab like Microprocessors Systems, Microprocessors Laboratory and Digital VLSI Systems a great interest was developed in the area of hardware description languages and specifically in the implementation of hardware circuits since in this area, theory and practice converge. That interest became more intense under the observation that the implementation of these circuits is the core of the semiconductor and embedded systems industry with a vast amount of applications in the daily life. An intriguing category of applications is the one related to cryptography. This is the reason why this diploma thesis focuses in the implementation of certain symmetric-key and public-key cryptographic algorithms like DES (Data Encryption Standard), AES (Advanced Encryption Standard), IDEA (International Data Encryption Algorithm) and RSA. As a result a cryptographic IP was designed, implemented and evaluated, called Crypto IP.

This thesis includes six chapters. Chapter 1 contains a brief introduction in cryptography, a detailed description of the implemented symmetric-key and public-key algorithms, as well as references in each one's applications in the daily life. In the second chapter the overall architecture of the Crypto IP is described: the main circuits implementing the cryptographic algorithms and a communication interface with the widely used AMBA bus so that the IP can be connected to a System on Chip. In chapters 3, 4 and 5 there is a detailed description of the implementation of each cryptographic circuit as well as a reference to the parameters which can be configured by the user. In chapter 6 there is a brief reference in the way that the functionality of these circuits was verified on an FPGA board using an external controller which feeds the circuits with the proper test cases. This thesis ends with an Appendix where the basic tables used by DES and AES algorithm are mentioned.

Finally we would like to thank the professor and laboratory supervisor Mr. K. Pekmestzi, the lecturer Mr. N. Moshopoulos whose experience led as in the production of a completed project according to the industry standards and guided us during the entire period of the thesis development, as well as the PhD students K. Tsoumanis and D. Bekiaris for the continuous technical support provided and their valuable advices.

# **Key Words**

- Integrated circuits

- Cryptography

- Crypto IP

- Symmetric key

- Asymmetric key

- Public key

- Private key

- DES

- AES

- IDEA

- RSA

- AMBA AHB

- FPGA

- ASIC

# Περίληψη

Η διπλωματική αυτή εργασία εκπονήθηκε στο εργαστήριο Μικροϋπολογιστών και Ψηφιακών Συστημάτων του Εθνικού Μετσόβιου Πολυτεχνείου. Έχοντας παρακολουθήσει τα μαθήματα του συγκεκριμένου εργαστηρίου όπως τα Συστήματα Μικροϋπολογιστών, το Εργαστήριο Μικροϋπολογιστών και τα Ψηφιακά Συστήματα VLSI αναπτύχθηκε ένα ιδιαίτερο ενδιαφέρον στον τομέα των γλωσσών περιγραφής υλικού και συγκεκριμένα στην υλοποίηση κυκλωμάτων σε επίπεδο hardware καθώς αποτελεί έναν τομέα όπου η θεωρία με την πράξη είναι αλληλένδετες. Το ενδιαφέρον έγινε ακόμα πιο έντονο παρατηρώντας ότι η υλοποίηση κυκλωμάτων αποτελεί τον πυρήνα της βιομηχανίας ημιαγωγών και ενσωματωμένων συστημάτων με πληθώρα εφαρμογών στην καθημερινή ζωή. Μια ιδιαίτερα ενδιαφέρουσα κατηγορία εφαρμογών είναι αυτή της κρυπτογραφίας. Για τον λόγο αυτό αποφασίστηκε η συγκεκριμένη διπλωματική να επικεντρωθεί στην υλοποίηση κάποιων βασικών αλγόριθμων κρυπτογραφίας συμμετρικού και ασύμμετρου (δημόσιου) κλειδιού όπως ο DES (Data Encryption Standard), ο AES (Advanced Encryption Standard), ο IDEA (International Data Encryption Algorithm) και ο RSA. Αποτέλεσμα ήταν η σχεδίαση, υλοποίηση και αξιολόγηση ενός IP κρυπτογραφίας με την ονομασία Crypto IP.

Η εργασία αυτή περιλαμβάνει έξι κεφάλαια. Το κεφάλαιο 1 περιέχει μία σύντομη εισαγωγή στην κρυπτογραφία, αναλυτική περιγραφή των αλγορίθμων συμμετρικού και δημόσιου κλειδιού που υλοποιήθηκαν, καθώς και μια αναφορά στις εφαρμογές του καθενός στην καθημερινή ζωή. Στο δεύτερο κεφάλαιο περιγράφεται η συνολική αρχιτεκτονική του Crypto IP: τα κύρια κυκλώματα που υλοποιούν του αλγόριθμους και μία διεπαφή για επικοινωνία με τον ευρέως χρησιμοποιούμενο διάδρομο AMBA ώστε το Crypto IP να έχει τη δυνατότητα διασύνδεσης σε ένα Σύστημα επί Ψηφίδας. Στα κεφάλαια 3, 4 και 5 γίνεται αναλυτική περιγραφή της υλοποίησης του κάθε κρυπτογραφικού κυκλώματος με αναφορά στις δυνατότητες παραμετροποίησης του από τον χρήστη. Στο κεφάλαιο 6 γίνεται μία σύντομη αναφορά στον τρόπο επαλήθευσης της ορθής λειτουργίας των κυκλωμάτων αυτών σε μια πλακέτα FPGA με τη χρήση ενός εξωτερικού ελεγκτή που τα τροφοδοτεί με τις κατάλληλες περιπτώσεις ελέγχου. Η εργασία ολοκληρώνεται με ένα παράρτημα στο οποίο παραθέτονται κάποιοι βασικοί πίνακες που χρησιμοποιούνται στους αλγορίθμους DES και AES.

Τέλος θα θέλαμε να ευχαριστήσουμε τον επιβλέποντα καθηγητή και υπεύθυνο του εργαστηρίου κύριο Κ. Πεκμεστζή, τον λέκτορα κύριο Ν. Μοσχόπουλο που μέσω της εμπειρίας του μας οδήγησε στην παραγωγή ενός ολοκληρωμένου έργου στα πρότυπα της

βιομηχανίας και μας καθοδηγούσε σε όλη τη διάρκεια εκπόνησης της εργασίας, καθώς και τους διδακτορικούς φοιτητές Κ. Τσουμάνη και Δ. Μπεκιάρη για την συνεχή τεχνική υποστήριξη που μας παρείχαν και τις πολύτιμες συμβουλές τους.

# Λέξεις - Κλειδιά

- Ολοκληρωμένα κυκλώματα

- Κρυπτογραφία

- Crypto IP

- Συμμετρικό κλειδί

- Ασύμμετρο κλειδί

- Δημόσιο κλειδί

- Ιδιωτικό κλειδί

- DES

- AES

- IDEA

- RSA

- AMBA AHB

- FPGA

- ASIC

# 1 Cryptography

#### 1.1 Introduction

Cryptography comes from the Greek words  $\kappa\rho \dot{\mu}\pi\tau \sigma\varsigma$  (hidden, secret) and  $\gamma\rho \dot{\alpha}\phi\epsilon i\nu$  (writing) and is the practice and study of techniques for secure communication in the presence of third parties (called adversaries). More generally, it is about constructing and analyzing protocols that overcome the influence of adversaries and which are related to various aspects in information security such as data confidentiality, data integrity, authentication, and non-repudiation.

Cryptography, prior to the modern age, was effectively synonymous with encryption, the conversion of information from a readable state to apparent nonsense. The originator of an encrypted message shared the decoding technique needed to recover the original information only with intended recipients, thereby precluding unwanted persons to do the same. Since World War I and the advent of the computer, the methods used to carry out cryptology have become increasingly complex and its application more widespread. Encryption was used to (attempt to) ensure secrecy in communications, such as those of spies, military leaders, and diplomats. In recent decades, the field has expanded beyond confidentiality concerns to include techniques for message integrity checking, sender/receiver identity authentication, digital signatures, interactive proofs and secure computation, among others.

Modern cryptography is heavily based on mathematical theory and computer science practice. Cryptographic algorithms are designed around computational hardness assumptions, making such algorithms hard to break in practice by any adversary. It is theoretically possible to break such a system but it is infeasible to do so by any known practical means. These schemes are therefore termed computationally secure. Theoretical advances (e.g. improvements in integer factorization algorithms) and faster computing technology require these solutions to be continually adapted. There exist informationtheoretically secure schemes that provably cannot be broken even with unlimited computing power (an example is the one-time pad) but these schemes are more difficult to implement than the best theoretically breakable but computationally secure mechanisms. The modern field of cryptography can be divided into several areas of study. The chief ones are the symmetric-key cryptography and the public-key cryptography.

# 1.1.1 Symmetric-key Cryptography

Symmetric-key cryptography refers to encryption methods in which both the sender and receiver share the same key (or, less commonly, in which their keys are different, but related in an easily computable way). This was the only kind of encryption publicly known until June 1976. Symmetric key ciphers are implemented as either block ciphers or stream ciphers. A block cipher enciphers input in blocks of plaintext as opposed to individual characters, the input form used by a stream cipher.

The Data Encryption Standard (DES) and the Advanced Encryption Standard (AES) are block cipher designs which have been designated cryptography standards by the US government (though DES's designation was finally withdrawn after the AES was adopted). Despite its deprecation as an official standard, DES (especially its still-approved and much more secure triple-DES variant) remains quite popular and it is used across a wide range of applications.

Stream ciphers, in contrast to the 'block' type, create an arbitrarily long stream of key material, which is combined with the plaintext bit-by-bit or character-by-character, somewhat like the one-time pad. In a stream cipher, the output stream is created based on a hidden internal state which changes as the cipher operates. That internal state is initially set up using the secret key material. Block ciphers can be used as stream ciphers using certain modes of operation.

Cryptographic hash functions are a third type of cryptographic algorithm. They take a message of any length as input, and output a short, fixed length hash which can be used in (for example) a digital signature. For good hash functions, an attacker cannot find two messages that produce the same hash. MD4 is a long-used hash function which is now broken. MD5, a strengthened variant of MD4, is also widely used but broken in practice. The U.S. National Security Agency (NSA<sup>1</sup>) developed the Secure Hash Algorithm series of MD5-

<sup>&</sup>lt;sup>1</sup> The National Security Agency (NSA) is a cryptologic intelligence agency of the United States Department of Defense. (http://www.nsa.gov)

like hash functions. SHA-0 was a flawed algorithm that the agency withdrew. SHA-1 is widely deployed and more secure than MD5, but cryptanalysts have identified attacks against it. The SHA-2 family improves on SHA-1, but it isn't yet widely deployed, and the U.S. standards authority thought it "prudent" from a security perspective to develop a new standard to significantly improve the robustness of NIST's<sup>2</sup> overall hash algorithm toolkit. Message authentication codes (MACs) are much like cryptographic hash functions, except that a secret key can be used to authenticate the hash value upon receipt.

## 1.1.2 Public-key Cryptography

Symmetric-key cryptosystems use the same key for encryption and decryption of a message, though a message or group of messages may have a different key than others. A significant disadvantage of symmetric ciphers is the key management necessary to use them securely. Each distinct pair of communicating parties must, ideally, share a different key, and perhaps each ciphertext exchanged as well. The number of keys required increases as the square of the number of network members, which very quickly requires complex key management schemes to keep them all straight and secret. The difficulty of securely establishing a secret key between two communicating parties, when a secure channel does not already exist between them, also presents a chicken-and-egg problem which is a considerable practical obstacle for cryptography users in the real world.

In a groundbreaking 1976 paper, Whitfield Diffie and Martin Hellman proposed the notion of public-key (also, more generally, called asymmetric key) cryptography in which two different but mathematically related keys are used—a public key and a private key. A public key system is so constructed that calculation of one key (the 'private key') is computationally infeasible from the other (the 'public key'), even though they are necessarily related. Instead, both keys are generated secretly, as an interrelated pair. The historian David Kahn described public-key cryptography as "the most revolutionary new concept in the field since polyalphabetic substitution emerged in the Renaissance".

<sup>&</sup>lt;sup>2</sup> The National Institute of Standards and Technology (NIST) is a measurement standards laboratory which is a non-regulatory agency of the United States Department of Commerce. (http://www.nist.gov)

In public-key cryptosystems, the public key may be freely distributed, while its paired private key must remain secret. In a public-key encryption system, the public key is used for encryption, while the private or secret key is used for decryption. While Diffie and Hellman could not find such a system, they showed that public-key cryptography was indeed possible by presenting the Diffie–Hellman key exchange protocol, a solution that is now widely used in secure communications to allow two parties to secretly agree on a shared encryption key.

Diffie and Hellman's publication sparked widespread academic efforts in finding a practical public-key encryption system. This race was finally won in 1978 by Ronald Rivest, Adi Shamir, and Len Adleman, whose solution has since become known as the RSA algorithm. The Diffie–Hellman and RSA algorithms, in addition to being the first publicly known examples of high quality public-key algorithms, have been among the most widely used. Others include the Cramer–Shoup cryptosystem, ElGamal encryption, and various elliptic curve techniques. Around 1970, James H. Ellis had conceived the principles of asymmetric key cryptography. In 1973, Clifford Cocks invented a solution that essentially resembles the RSA algorithm. And in 1974, Malcolm J. Williamson is claimed to have developed the Diffie-Hellman key exchange.

Public-key cryptography can also be used for implementing digital signature schemes. A digital signature is reminiscent of an ordinary signature. They both have the characteristic of being easy for a user to produce, but difficult for anyone else to forge. Digital signatures can also be permanently tied to the content of the message being signed. They cannot then be 'moved' from one document to another, for any attempt will be detectable. In digital signature schemes, there are two algorithms; one for signing, in which a secret key is used to process the message (or a hash of the message, or both), and one for verification, in which the matching public key is used with the message to check the validity of the signature. RSA and DSA are two of the most popular digital signature schemes. Digital signatures are central to the operation of public key infrastructures and many network security schemes (e.g. SSL/TLS, many VPNs etc.).

Public-key algorithms are most often based on the computational complexity of "hard" problems, often from number theory. For example, the hardness of RSA is related to the integer factorization problem, while Diffie–Hellman and DSA are related to the discrete logarithm problem. More recently, elliptic curve cryptography has developed in which security is based on number theoretic problems involving elliptic curves. Because of the difficulty of the underlying problems, most public-key algorithms involve operations such as modular multiplication and exponentiation, which are much more computationally

16

expensive than the techniques used in most block ciphers, especially with typical key sizes. As a result, public-key cryptosystems are commonly hybrid cryptosystems, in which a fast high-quality symmetric-key encryption algorithm is used for the message itself, while the relevant symmetric key is sent with the message, but encrypted using a public-key algorithm. Similarly, hybrid signature schemes are often used, in which a cryptographic hash function is computed, and only the resulting hash is digitally signed.

### 1.1.3 Cryptanalysis

The goal of cryptanalysis is to find some weakness or insecurity in a cryptographic scheme, thus permitting its subversion or evasion.

It is a common misconception that every encryption method can be broken. In connection with his WWII work at Bell Labs, Claude Shannon proved that the one-time pad cipher is unbreakable, provided the key material is truly random, never reused, kept secret from all possible attackers, and of equal or greater length than the message. Most ciphers, apart from the one-time pad, can be broken with enough computational effort by brute force attack, but the amount of effort needed may be exponentially dependent on the key size, as compared to the effort needed to make use of the cipher. In such cases, effective security could be achieved if it is proven that the effort required is beyond the ability of any adversary. This means it must be shown that no efficient method (as opposed to the time-consuming brute force method) can be found to break the cipher. Since no such proof has been found to date, the one-time-pad remains the only theoretically unbreakable cipher.

There are a wide variety of cryptanalytic attacks, and they can be classified in any of several ways. A common distinction turns on what an attacker knows and what capabilities are available. In a ciphertext-only attack, the cryptanalyst has access only to the ciphertext (good modern cryptosystems are usually effectively immune to ciphertext-only attacks). In a known-plaintext attack, the cryptanalyst has access to a ciphertext and its corresponding plaintext (or to many such pairs). In a chosen-plaintext attack, the cryptanalyst may choose a plaintext and learn its corresponding ciphertext (perhaps many times). Finally, in a chosen-ciphertext attack, the cryptanalyst may be able to choose ciphertexts and learn their corresponding plaintexts.

Cryptanalysis of symmetric-key ciphers typically involves looking for attacks against the block ciphers or stream ciphers that are more efficient than any attack that could be against a perfect cipher. For example, a simple brute force attack against DES requires one known plaintext and 255 decryptions, trying approximately half of the possible keys, to reach a point at which chances are better than even that the key sought will have been found. But this may not be enough assurance; a linear cryptanalysis attack against DES requires 243 known plaintexts and approximately 243 DES operations. This is a considerable improvement on brute force attacks.

Public-key algorithms are based on the computational difficulty of various problems. The most famous of these is integer factorization (e.g., the RSA algorithm is based on a problem related to integer factoring), but the discrete logarithm problem is also important. Much public-key cryptanalysis concerns numerical algorithms for solving these computational problems, or some of them, efficiently (i.e., in a practical time). For instance, the best known algorithms for solving the elliptic curve-based version of discrete logarithm are much more time-consuming than the best known algorithms for factoring, at least for problems of more or less equivalent size. Thus, other things being equal, to achieve an equivalent strength of attack resistance, factoring-based encryption techniques must use larger keys than elliptic curve techniques. For this reason, public-key cryptosystems based on elliptic curves have become popular since their invention in the mid-1990s.

While pure cryptanalysis uses weaknesses in the algorithms themselves, other attacks on cryptosystems are based on actual use of the algorithms in real devices, and are called sidechannel attacks. If a cryptanalyst has access to, for example, the amount of time the device took to encrypt a number of plaintexts or report an error in a password or PIN character, he may be able to use a timing attack to break a cipher that is otherwise resistant to analysis. An attacker might also study the pattern and length of messages to derive valuable information; this is known as traffic analysis, and can be quite useful to an alert adversary. Poor administration of a cryptosystem, such as permitting too short keys, will make any system vulnerable, regardless of other virtues. And, of course, social engineering, and other attacks against the personnel who work with cryptosystems or the messages they handle may be the most productive attacks of all.

### 1.1.4 Legal Issues

Cryptology-related technology has raised a number of legal issues. In the United Kingdom, additions to the Regulation of Investigatory Powers Act 2000 require a suspected criminal to hand over their encryption key if asked by law enforcement. Otherwise the user will face a criminal charge. The Electronic Frontier Foundation (EFF<sup>3</sup>) is involved in a case in the Supreme Court of the United States, which may determine whether requiring suspected criminals to provide their encryption keys to law enforcement is unconstitutional. The EFF is arguing that this is a violation of the right of not being forced to incriminate oneself, as given in the Fifth Amendment.

## **1.2 Technical Terms**

In this section basic terms used in the following chapters are explained.

*Plaintext*: Plaintext is information a sender wishes to transmit to a receiver. Cleartext is often used as a synonym. Before the computer era, plaintext most commonly meant message text in the language of the communicating parties. Plaintext has reference to the operation of cryptographic algorithms, usually encryption algorithms, and is the input upon which they operate. Cleartext, by contrast, refers to data that is transmitted or stored unencrypted.

*Ciphertext*: Ciphertext is the result of encryption performed on plaintext using an algorithm. Ciphertext is also known as encrypted or encoded information because it contains a form of the original plaintext that is unreadable by a human or computer without the proper algorithm to decrypt it.

*Key*: Key is a piece of information that determines the functional output of a cryptographic algorithm. Without a key, the algorithm would produce no useful result. In encryption, a key specifies the particular transformation of plaintext into ciphertext, or vice versa during

<sup>&</sup>lt;sup>3</sup> The Electronic Frontier Foundation (EFF) is an international non-profit digital rights advocacy and legal organization based in the United States (www.eff.org)

decryption. Keys are also used in other cryptographic algorithms, such as digital signature schemes and message authentication codes.

*Encryption – Decryption*: Encryption is the process of transforming information (referred to as plaintext) using an algorithm to make it unreadable to anyone except those possessing special knowledge, usually referred to as a key. The result of the process is information (in cryptography, referred to as ciphertext). The reverse process, i.e., to make the encrypted information readable again, is referred to as decryption.

*Data Integrity*: Data integrity is a term used to refer to the accuracy and reliability of data. Data must be complete, with no variations or compromises from the original, to be considered reliable and accurate.

Authentication: Authentication is the act of confirming the truth of an attribute of a datum or entity. This might involve confirming the identity of a person or software program, tracing the origins of an artifact, or ensuring that a product is what its packaging and labeling claims to be.

# 1.3 Symmetric-key Cryptography

### 1.3.1 Data Encryption Standard (DES)

#### 1.3.1.1 Overview

In 1972, the National Institute of Standards and Technology (called the National Bureau of Standards at the time) decided that a strong cryptographic algorithm was needed to protect non-classified information. The algorithm was required to be cheap, widely available, and very secure. NIST envisioned something that would be available to the general public and could be used in a wide variety of applications. So they asked for public proposals for such an algorithm. In 1974 IBM submitted the Lucifer algorithm, which appeared to meet most of NIST's design requirements.

NIST enlisted the help of the National Security Agency to evaluate the security of Lucifer. At the time many people distrusted the NSA due to their extremely secretive activities, so there was initially a certain degree of skepticism regarding the analysis of Lucifer. One of the greatest worries was that the key length, originally 128 bits, was reduced to just 56 bits, weakening it significantly.

The modified Lucifer algorithm was adopted by NIST as a federal standard on November 23, 1976. Its name was changed to the Data Encryption Standard (DES). The algorithm specification was published in January 1977, and with the official backing of the government it became a very widely employed algorithm in a short amount of time.

Unfortunately, over time various shortcut attacks were found that could significantly reduce the amount of time needed to find a DES key by brute force. And as computers became progressively faster and more powerful, it was recognized that a 56-bit key was simply not large enough for high security applications. As a result of these serious flaws, NIST abandoned their official endorsement of DES in 1997.

#### 1.3.1.2 Algorithm Description

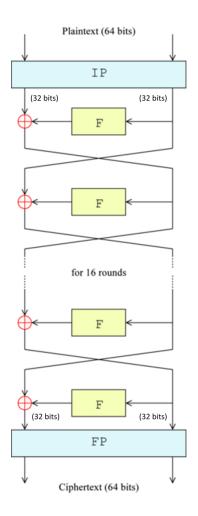

DES encrypts and decrypts data in 64-bit blocks, using a 64-bit key (although the effective key strength is only 56 bits). It takes a 64-bit block of plaintext as input and outputs a 64-bit block of ciphertext. Since it always operates on blocks of equal size and it uses both permutations and substitutions in the algorithm, DES is both a block cipher and a product cipher.

DES has 16 rounds, meaning the main algorithm is repeated 16 times to produce the ciphertext. It has been found that the number of rounds is exponentially proportional to the amount of time required to find a key using a brute-force attack. So as the number of rounds increases, the security of the algorithm increases exponentially.

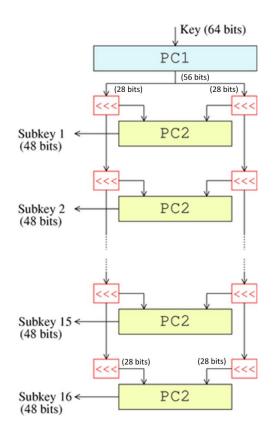

### 1.3.1.3 Key Scheduling

Although the input key for DES is 64 bits long, the actual key used by DES is only 56 bits in length. The least significant (right-most) bit in each byte is a parity bit, and should be set so that there are always an odd number of 1s in every byte. These parity bits are ignored, so only the seven most significant bits of each byte are used, resulting in a key length of 56 bits.

The first step is to pass the 64-bit key through a permutation (see Table 31: *Permuted Choice* 1) to produce the 56-bit key.

Now that the 56-bit key is ready, the next step is to use this key to generate 16 48-bit subkeys, called K[1]-K[16], which are used in the 16 rounds of DES for encryption and decryption. The procedure for generating subkeys - known as key scheduling - is the following:

- 1. Set the round number R to 1.

- Split the current 56-bit key, K, up into two 28-bit blocks, L (the left-hand half) and R (the right-hand half).

- 3. Rotate L left by the number of bits specified in the Table 33: *Subkey Rotation*, and rotate R left by the same number of bits as well.

- 4. Join L and R together to get the new K.

- 5. Apply a permutation (see Table 32: *Permuted Choice 2*) to K to get the final K[R], where R is the number of the current round.

- 6. Increment R by 1 and repeat the procedure until all 16 subkeys K[1]-K[16] are ready.

Figure 1: DES Key Schedule

#### 1.3.1.4 Plaintext Preparation

Once the key scheduling has been performed, the next step is to prepare the plaintext for the actual encryption. This is done by passing the plaintext through a permutation called the Initial Permutation (see Table 34: *Initial Permutation*). This table also has an inverse, called the Inverse Initial Permutation (see Table 35: *Inverse Initial Permutation*). If you run a block of plaintext through the initial permutation and then pass the resulting block through the inverse initial permutation, you'll end up with the original block.

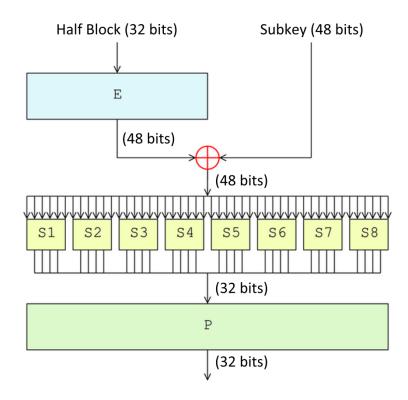

#### 1.3.1.5 DES Core Function

DES core function is also known as the "Feistel function" (see Figure 2). Once the key scheduling and plaintext preparation have been completed, the actual encryption or decryption is performed by the main DES algorithm. The 64-bit block of input data is first split into two halves, L and R. L is the left-most 32 bits, and R is the right-most 32 bits. The

following process is repeated 16 times, making up the 16 rounds of standard DES. The 16 sets of halves are called L[0]-L[15] and R[0]-R[15]. Each DES round has the following steps:

- R[i-1] where i is the round number, starting at 1 is taken and fed into the E-Bit Selection Table (see Table 36: *E-Bit Selection*), which is like a permutation, except that some of the bits are used more than once. This expands the number R[i-1] from 32 to 48 bits to prepare for the next step.

- 2. The 48-bit R[i-1] is XORed with K[i] and stored in a temporary buffer so that R[i-1] is not modified.

- 3. The result from the previous step is now split into 8 segments of 6 bits each. The left-most 6 bits are B[1], and the right-most 6 bits are B[8]. These blocks form the index into the S-boxes (see Table 38 to Table 45), which are used in the next step. The Substitution boxes, known as S-boxes, are a set of 8 two-dimensional arrays, each with 4 rows and 16 columns. The numbers in the boxes are always 4 bits in length, so their values range from 0-15. The S-boxes are numbered S[1] to S[8].

- 4. Starting with B[1], the first and last bits of the 6-bit block are taken and used as an index into the row number of S[1], which can range from 0 to 3, and the middle four bits are used as an index into the column number, which can range from 0 to 15. The number from this position in the S-box is retrieved and stored away. This is repeated with B[2] and S[2], B[3] and S[3], and the others up to B[8] and S[8]. At this point, you now have 8 4-bit numbers, which when strung together one after the other in the order of retrieval, give a 32-bit result.

- The result from the previous stage is now passed into the P Permutation (see Table 37: P Permutation).

- 6. This number is now XORed with L[i-1], and moved into R[i]. R[i-1] is moved into L[i].

- At this point the new L[i] and R[i] are ready. Here, i is incremented and the core function is repeated until i = 17, which means that 16 rounds have been executed and keys K[1]-K[16] have all been used.

When L[16] and R[16] have been obtained, they are joined back together in the same fashion they were split apart (L[16] is the left-hand half, R[16] is the right-hand half), then the two halves are swapped, R[16] becomes the left-most 32 bits and L[16] becomes the right-most 32 bits of the pre-output block and the resultant 64-bit number is called the pre-output.

Figure 2: Feistel Function

Figure 3: Main Process of DES

### 1.3.1.6 Ciphertext Preparation

The final step is to apply the inverse initial permutation at the pre-output. The result is the completely encrypted ciphertext.

#### 1.3.1.7 Decryption

The same algorithm can be used for encryption or decryption. The method described above will encrypt a block of plaintext and return a block of ciphertext. In order to decrypt the ciphertext and get the original plaintext again, the procedure is simply repeated but the subkeys are applied in reverse order, i.e. K[16] to K[1]. Other than that, decryption is performed exactly in the same way as encryption.

# 1.3.2 Advanced Encryption Standard (AES)

#### 1.3.2.1 Overview

The Advanced Encryption Standard (AES) is a specification for the encryption of electronic data established by the U.S. National Institute of Standards and Technology (NIST) in 2002. Originally called Rijndael, the algorithm was developed by two Belgian cryptographers, Joan Daemen and Vincent Rijmen, who submitted to the AES selection process. Strictly speaking, the AES standard is a variant of Rijndael where the block size is restricted to 128 bits.

AES has been adopted by the U.S. government and is now used worldwide. It supersedes the Data Encryption Standard (DES). The algorithm described by AES is a symmetric-key algorithm, meaning the same key is used for both encrypting and decrypting the data.

In the United States, AES was announced by the NIST as U.S. FIPS PUB 197 (FIPS<sup>4</sup> 197) on November 26, 2001. This announcement followed a five-year standardization process in which fifteen competing designs were presented and evaluated, before the Rijndael algorithm was selected as the most suitable. It became effective as a federal government standard on May 26, 2002 after approval by the Secretary of Commerce. AES is included in the ISO/IEC 18033-3 standard. AES is available in many different encryption packages, and is the first publicly accessible and open algorithm approved by the National Security Agency (NSA) for top secret information when used in an NSA approved cryptographic module.

<sup>&</sup>lt;sup>4</sup> A Federal Information Processing Standard (FIPS) is a publicly announced standardization developed by the United States federal government for use in computer systems by all non-military government agencies and by government contractors, when properly invoked and tailored on a contract.

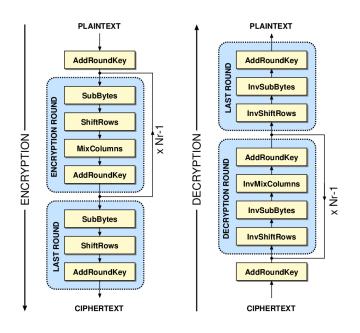

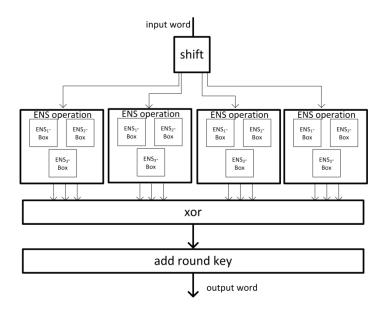

The main process of AES is depicted in Figure 4.

Figure 4: AES Main Process

### 1.3.2.2 Rijndael Key Schedule

AES (Rijndael) uses a key schedule to expand a short key into a number of separate round keys. This is known as the Rijndael key schedule. Rijndael's key schedule utilizes a number of operations, which will be described before describing the key schedule.

- Rotate: The rotate operation takes a 32-bit word and rotates it eight bits to the left such that the high eight bits "wrap around" and become the low eight bits of the result.

- Rcon: Rcon is what the Rijndael documentation calls the exponentiation of 2 to a user-specified value. Note that, this operation is not performed with regular integers, but in Rijndael's finite field. The Rcon can be computed using a specific vector (see Table 46: *Rcon[256]*).

- S-box: The Rijndael S-box is a matrix (square array of numbers) used in the Rijndael cipher. The S-box (substitution box) serves as a lookup table (see Table 47: *Rijndael S-Box*).

# 1.3.2.3 Key Schedule Core

This operation is used as an inner loop in the key schedule, and is done thus:

- The input is a 32-bit word and at an iteration number i. The output is a 32-bit word.

- Copy the input over to the output.

- Use the above described rotate operation to rotate the output eight bits to the left.

- Apply Rijndael's S-box on all four individual bytes in the output word.

- On just the first (leftmost) byte of the output word, exclusive or the byte with 2 to the power of (i-1). In other words, perform the Rcon operation with i as the input, and exclusive or the Rcon output with the first byte of the output word.

Since the key schedule for 128-bit, 192-bit, and 256-bit encryption are very similar, with only some constants changed, the following key size constants are defined here:

- n has a value of 16 for 128-bit keys, 24 for 192-bit keys, and 32 for 256-bit keys

- b has a value of 176 for 128-bit keys, 208 for 192-bit keys, and 240 for 256-bit keys

Rijndael's key schedule is done as follows:

- 1. The first n bytes of the expanded key are the encryption key.

- 2. The Rcon iteration value i, is set to 1.

- 3. Until b bytes of expanded key are produced, the following procedure is executed to generate n more bytes of expanded key:

- $\circ$   $\;$  The following steps are performed to create 4 bytes of expanded key:

- i. Create a 4-byte temporary variable, t.

- ii. Assign the value of the previous four bytes in the expanded key to t.

- iii. Perform the key schedule core (see Key Schedule Core) on t, with i as the Rcon iteration value.

- iv. Increment i by 1.

- v. Exclusive-or t with the four-byte block n bytes before the new expanded key. This becomes the next 4 bytes in the expanded key.

- Then, the following steps are performed three times to create the next twelve bytes of expanded key:

- i. Assign the value of the previous 4 bytes in the expanded key to t.

- ii. Exclusive-or t with the four-byte block n bytes before the new expanded key. This becomes the next 4 bytes in the expanded key.

- If a 256-bit key is generated, the following steps are performed to generate the next 4 bytes of expanded key:

- i. Assign the value of the previous 4 bytes in the expanded key to t.

- ii. Run each of the 4 bytes in t through Rijndael's S-box.

- iii. Exclusive-or t with the 4-byte block n bytes before the new expanded key. This becomes the next 4 bytes in the expanded key.

- If a 128-bit key is generated, the following steps are not performed. If a 192bit key is generated, the following steps are performed twice. If a 256-bit key is generated, the following steps are performed three times:

- i. Assign the value of the previous 4 bytes in the expanded key to t.

- ii. Exclusive-or t with the four-byte block n bytes before the new expanded key. This becomes the next 4 bytes in the expanded key.

## 1.3.2.4 Description of the Algorithm

AES is based on a design principle known as a substitution-permutation network, and is fast in both software and hardware. Unlike its predecessor DES, AES does not use a Feistel network. AES is a variant of Rijndael which has a fixed block size of 128 bits, and a key size of 128, 192, or 256 bits. By contrast, the Rijndael specification per se is specified with block and key sizes that may be any multiple of 32 bits, both with a minimum of 128 and a maximum of 256 bits.

AES operates on a 4×4 column-major order matrix of bytes, termed the state, although some versions of Rijndael have a larger block size and have additional columns in the state. Most AES calculations are done in a special finite field.

The key size used for an AES algorithm specifies the number of repetitions of transformation rounds that convert the input, called the plaintext, into the final output, called the ciphertext. The number of cycles of repetition is as follows:

- 10 cycles of repetition for 128 bit keys

- 12 cycles of repetition for 192 bit keys

- 14 cycles of repetition for 256 bit keys

Each round consists of several processing steps, including one that depends on the encryption key itself.

- 1. Key Expansion: round keys are derived from the cipher key using Rijndael's key schedule

- 2. Initial Round:

- i. AddRoundKey: each byte of the state is combined with the round key using bitwise xor

- 3. Rounds:

- i. SubBytes: a non-linear substitution step where each byte is replaced with another according to a lookup table

- ii. ShiftRows: a transposition step where each row of the state is shifted cyclically a certain number of steps

- iii. MixColumns: a mixing operation which operates on the columns of the state, combining the four bytes in each column

- iv. AddRoundKey

- 4. Final Round (no MixColumns)

- i. SubBytes

- ii. ShiftRows

- iii. AddRoundKey

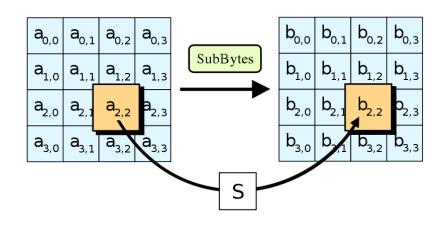

#### 1.3.2.5 The SubBytes Step

In the SubBytes step, each byte in the state matrix is replaced with a SubByte using an 8-bit substitution box, the Rijndael S-box (see Table 47: *Rijndael S-Box*). This operation provides the non-linearity in the algorithm. The S-box used is derived from the multiplicative inverse over GF(2<sup>8</sup>), known to have good non-linearity properties. To avoid attacks based on simple algebraic properties, the S-box is constructed by combining the inverse function with an invertible affine transformation. The S-box is also chosen to avoid any fixed points (and so is a derangement), and also any opposite fixed points.

Figure 5: AES SubBytes

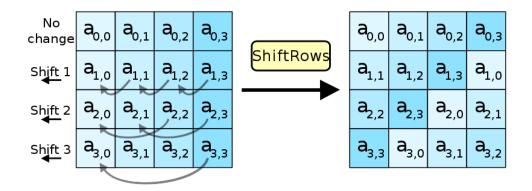

#### 1.3.2.6 The ShiftRows Step

The ShiftRows step operates on the rows of the state; it cyclically shifts the bytes in each row by a certain offset. For AES, the first row is left unchanged. Each byte of the second row is shifted one to the left. Similarly, the third and fourth rows are shifted by offsets of two and three respectively. For blocks of sizes 128 bits and 192 bits, the shifting pattern is the same. Row n is shifted left circular by n-1 bytes. In this way, each column of the output state of the ShiftRows step is composed of bytes from each column of the input state. (Rijndael variants with a larger block size have slightly different offsets). For a 256-bit block, the first row is unchanged and the shifting for the second, third and fourth row is 1 byte, 3 bytes and 4 bytes respectively—this change only applies for the Rijndael algorithm when used with a 256-bit block, as AES does not use 256-bit blocks.

Figure 6: AES ShiftRows

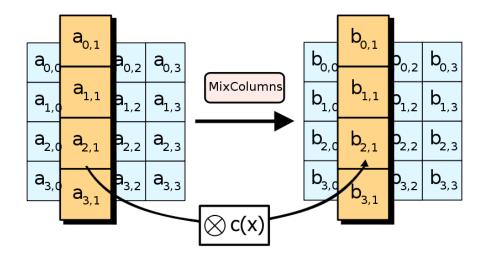

#### 1.3.2.7 The MixColumns Step

In the MixColumns step, the four bytes of each column of the state are combined using an invertible linear transformation. The MixColumns function takes four bytes as input and outputs four bytes, where each input byte affects all four output bytes. Together with ShiftRows, MixColumns provides diffusion in the algorithm.

During this operation, each column is multiplied by a known matrix (see Table 1).

| 2 | 3 | 1 | 1 |

|---|---|---|---|

| 1 | 2 | 3 | 1 |

| 1 | 1 | 2 | 3 |

| 3 | 1 | 1 | 2 |

Table 1: MixColumns Multiplication Matrix

The multiplication operation is defined as multiplication by 1 means no change, multiplication by 2 means shifting to the left, and multiplication by 3 means shifting to the left and then performing xor with the initial unshifted value. After shifting, a conditional xor with 0x11B should be performed if the shifted value is larger than 0xFF.

In more general sense, each column is treated as a polynomial over  $GF(2^8)$  and is then multiplied modulo  $x^4+1$  with a fixed polynomial  $c(x) = 0x03 \cdot x^3 + x^2 + x + 0x02$ . The coefficients are displayed in their hexadecimal equivalent of the binary representation of bit polynomials from GF(2)[x]. The MixColumns step can also be viewed as a multiplication by a particular MDS matrix in a finite field.

Figure 7: AES MixColumns

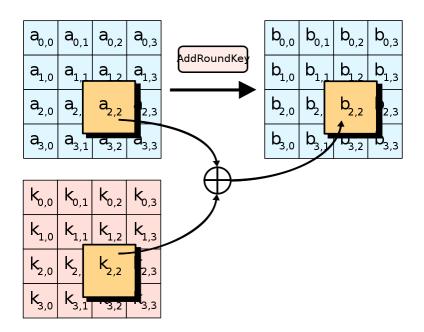

## 1.3.2.8 The AddRoundKey step

In the AddRoundKey step, the subkey is combined with the state. For each round, a subkey is derived from the main key using Rijndael's key schedule; each subkey is the same size as the state. The subkey is added by combining each byte of the state with the corresponding byte of the subkey using bitwise XOR.

Figure 8: AES AddRoundKey

#### 1.3.2.9 Decryption

The above process describes the way encryption is performed. Decryption is almost the same process but the steps (SubBytes, ShiftRows, MixColumns, and AddRoundKey) are executed in a different order using different tables. Details of the way that decryption process is implemented can be found in section 3.3.4).

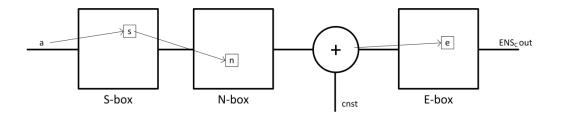

### 1.3.3 International Data Encryption Algorithm (IDEA)

#### 1.3.3.1 Overview

The block cipher IDEA was first presented by Xuejia Lai and James Massey of the Swiss Federal Institute of Technology in 1990 and was then called PES (Proposed Encryption Standard). In 1991 after Biham and Shamir presented their results regarding differential cryptanalysis, the authors developed an improved version of the PES algorithm to increase the security against this attack and the new algorithm was called IPES (Improved Proposed Encryption Standard) while finally in 1992 its name was changed officially to IDEA.

The IDEA is a symmetric, block oriented encryption algorithm, which operates on a 64-bit plaintext and uses a 128 bit length key. The substitution boxes and the associated "lookup tables" used in the rest block ciphers available to-date (and among them DES) have been completely dispensed with. The required confusion in this algorithm is achieved by successively using three different and incompatible group operations on pairs of 16-bit sub blocks and mixing them (in such a way that at no point in the encryption process the same algebraic operation is used contiguously) while the structure of the cipher was carefully chosen to provide the necessary diffusion requirement. These three algebraic operations are the following:

- Bitwise XOR (denoted with ⊕)

- Addition of integers modulo (2<sup>16</sup>) with inputs and outputs treated as unsigned 16-bit integers (denoted with ⊞)

- Multiplication of integers modulo (2<sup>16</sup>+1) with inputs and outputs treated as unsigned 16-bit integers (This operation can be also viewed as IDEA's equivalent S-box) (denoted with ··)

All these operations operate on 16-bit sub-blocks. Their use in combination provides for a complex transformation of the input making cryptanalysis much more difficult than with an algorithm such as e.g. DES, which relies solely on the XOR function.

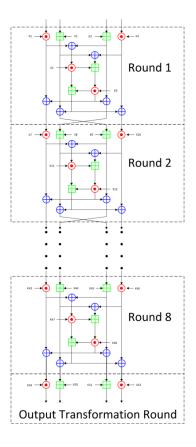

IDEA uses a 128 bit key which is double the key size of DES, making it highly immune to attacks. IDEA uses algebraic operations completely and it entirely avoids the use of any lookup tables or S-boxes. The strength of IDEA lies in its modulo multiplication operations. The working of IDEA can be visualized as—the 64-bit plain text block is divided into 4 portions of plain text (each of size 16 bits), say P1 to P4. Thus, P1 to P4 are the inputs for the first round of the algorithm. There are 8 such rounds. In each round, 6 subkeys (each of size 16 bits) are generated from the original 128 bit key. These subkeys are applied to the 4 input blocks P1 to P4. Thus, for the 1st round there are 6 subkeys K1 to K6. For the 2nd round, there are keys K7 to K12. Finally, keys K43 to K48 will be used. The final step consists of an Output Transformation, which uses just 4 subkeys. The final output produced is the output produced by the Output Transformation round.

The main process of IDEA is depicted in Figure 9.

Figure 9: IDEA Main Process

The designers analyzed IDEA to measure its strength against differential cryptanalysis and concluded that it is immune under certain assumptions. No successful linear or algebraic weaknesses have been reported. As of 2007, the best attack which applies to all keys can break IDEA reduced to 6 rounds (the full IDEA cipher uses 8.5 rounds). Note that a "break" is any attack which requires less than 2128 operations; the 6-round attack requires 264 known plaintexts and 2126.8 operations.

The very simple key schedule makes IDEA subject to a class of weak keys; some keys containing a large number of 0 bits produce weak encryption. These are of little concern in practice, being sufficiently rare that they are unnecessary to avoid explicitly when generating keys randomly. A simple fix was proposed; exclusive-ORing each subkey with a 16-bit constant, such as 0x0DAE. Larger classes of weak keys were found in 2002.

# 1.3.3.2 Key Generation

The initial 6 subkeys K1 to K6 are generated from the original 128 bit key. Since the sub -keys consist of 16 bits each, out of the original 128 bits, the first 96 bits are used for the first round. Thus, at the end of the first round, bits 97–128 of the original key are unused. In the second round, the unused 32 bits of the first round are used. To generate the rest of the sub -keys for the second round, 64 more bits are required. This is obtained by shifting the original key left circularly by 25 bits. Then, the modified key is now used to generate the rest of the second for the same way as the first round keys are generated. The same is done for the subkey generation for the rest of the rounds.

### 1.3.3.3 Encryption Round

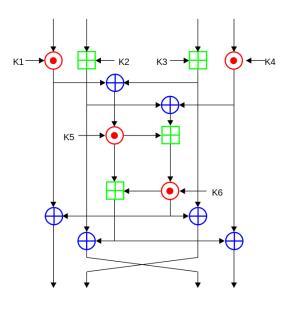

In each round of the 8 rounds of algorithm, the following sequence of events is performed:

- 1. Multiply P1 and K1

- 2. Add P2 and K2

- 3. Add P3 and K3

- 4. Multiply P4 and K4

- 5. XOR the results of step 1 and step 3

- 6. XOR the results of step 2 and step 4

- 7. Multiply the results of step 5 with K5

- 8. Add the results of step 6 and step 7

- 9. Multiply the results of step 8 with K6

- 10. Add the results of step 7 and step 9

- 11. XOR the results of step 1 and step 9

- 12. XOR the results of step 3 and step 9

- 13. XOR the results of step 2 and step 10

- 14. XOR the results of step 4 and step 10

Figure 10: IDEA Round

Sequence of events followed in the output transformation round:

- 1. Multiply R1 and K1

- 2. Add R2 and K2

- 3. Add R3 and K3

- 4. Multiply R4 and K4

The outputs of the round are given in the same order to the next round. After the 8<sup>th</sup> round, the inner 2 blocks are swapped and given as input to the final transformation round. Finally, the four sub -blocks are attached to get the final encrypted result.

#### 1.3.3.4 Decryption

Decryption uses exactly the same sequence of operations of successive 64-bit blocks of the ciphertext, but with a different set of subkeys. The same 52 key sub-blocks generated for encryption are rearranged and inverted accordingly to produce the decryption key schedule. Those that are added are replaced by their two's complement. Those that are multiplied in are replaced by their multiplicative inverse, modulo 2<sup>16</sup>+1, but those used to calculate the cross-footed F-functions are not changed. Keys XORed in would not need to be changed, but there aren't any such keys in IDEA.

The decryption sub -keys (relative to the encryption subkeys s1 to s52) are generated as shown in Table 2.

| 1st round            | s49* | s50# | s51# | s52* | s47 | s48 |

|----------------------|------|------|------|------|-----|-----|

| 2nd round            | s43* | s45# | s44# | s46* | s41 | s42 |

| 3rd round            | s37* | s39# | s38# | s39* | s35 | s36 |

| 4th round            | s31* | s33# | s32# | s34* | s29 | s30 |

| 5th round            | s25* | s27# | s26# | s28* | s23 | s24 |

| 6th round            | s19* | s21# | s20# | s22* | s17 | s18 |

| 7th round            | s13* | s15# | s14# | s16* | s11 | s12 |

| 8th round            | s7*  | s9#  | s8#  | s10* | s5  | s6  |

| Final transformation | -    | -    | s1*  | s2#  | s3# | s4* |

Table 2: Decryption Subkeys Generation Table

- sXX\* = multiplicative inverse of sXX modulus 2<sup>16</sup>+1

- sXX# = additive inverse of sXX modulus 2<sup>16</sup>

# 1.3.4 Block Cipher Operation Modes

### 1.3.4.1 Introduction

In cryptography, a mode of operation is the procedure of enabling the repeated and secure use of a block cipher under a single key. A block cipher by itself allows encryption only of a single data block of the cipher's block length. When targeting a variable-length message, the data must first be partitioned into separate cipher blocks. Typically, the last block must also be extended to match the cipher's block length using a suitable padding scheme. A mode of operation describes the process of encrypting each of these blocks, and generally uses randomization based on an additional input value, often called an initialization vector, to allow doing so safely.

Modes of operation have primarily been defined for encryption and authentication. Historically, encryption modes have been studied extensively in regard to their error propagation properties under various scenarios of data modification. Later development regarded integrity protection as an entirely separate cryptographic goal from encryption. Some modern modes of operation combine encryption and authentication in an efficient way, and are known as authenticated encryption modes.

An initialization vector (IV) is a block of bits that is used by several modes to randomize the encryption and hence to produce distinct ciphertexts even if the same plaintext is encrypted multiple times, without the need for a slower re-keying process.

An initialization vector has different security requirements than a key, so the IV usually does not need to be secret. However, in most cases, it is important that an initialization vector is never reused under the same key. For CBC and CFB, reusing an IV leaks some information about the first block of plaintext, and about any common prefix shared by the two messages. For OFB and CTR, reusing an IV completely destroys security. In CBC mode, the IV must, in addition, be unpredictable at encryption time; in particular, the (previously) common practice of re-using the last ciphertext block of a message as the IV for the next message is insecure (for example, this method was used by SSL 2.0). If an attacker knows the IV (or the previous block of ciphertext) before he specifies the next plaintext, he can check his guess about plaintext of some block that was encrypted with the same key before (this is known as the TLS CBC IV attack).

As a special case, if the plaintexts are always small enough to fit into a single block (with no padding), then with some modes (ECB, CBC, PCBC), re-using an IV will leak only whether two plaintexts are equal. This can be useful in cases where one wishes to be able to test for equality without decrypting or separately storing a hash.

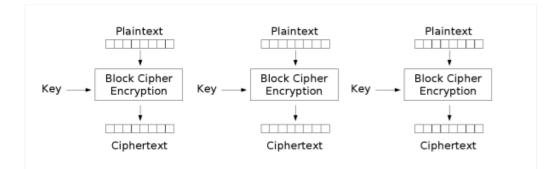

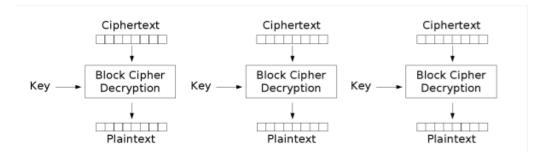

### 1.3.4.2 Electronic Codebook (ECB mode)

The simplest of the encryption modes is the electronic codebook (ECB) mode. The message is divided into blocks and each block is encrypted separately.

Figure 11: Electronic Codebook (ECB) Encryption

Figure 12: Electronic Codebook (ECB) Decryption

The disadvantage of this method is that identical plaintext blocks are encrypted into identical ciphertext blocks; thus, it does not hide data patterns well. In some senses, it doesn't provide serious message confidentiality, and it is not recommended for use in cryptographic protocols at all.

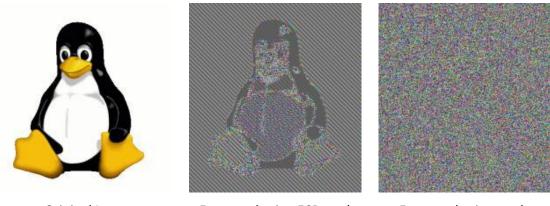

A striking example of the degree to which ECB can leave plaintext data patterns in the ciphertext can be seen when ECB mode is used to encrypt a bitmap image which uses large areas of uniform color. While the color of each individual pixel is encrypted, the overall image may still be discerned as the pattern of identically colored pixels in the original remains in the encrypted version (see Figure 13).

Original Image

Encrypted using ECB mode

Encrypted using modes other than ECB

Figure 13: Difference of ECB Mode from the Others

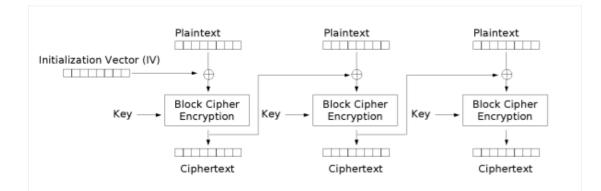

# 1.3.4.3 Cipher-block Chaining (CBC mode)

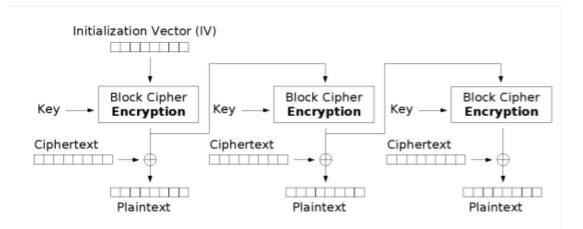

IBM invented the cipher-block chaining (CBC) mode of operation in 1976. In CBC mode, each block of plaintext is XORed with the previous ciphertext block before being encrypted. This way, each ciphertext block depends on all plaintext blocks processed up to that point. To make each message unique, an initialization vector must be used in the first block.

Encryption and decryption algorithms are as follows:

- $C_i = E_K(P_i \bigoplus C_{i-1}), C_0 = IV$

- $P_i = D_K(C_i) \bigoplus C_{i-1}, C_0 = IV$

Figure 14: Cipher-block Chaining Encryption

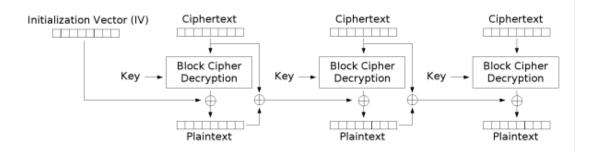

Figure 15: Cipher-block Chaining Decryption

CBC has been the most commonly used mode of operation. Its main drawbacks are that encryption is sequential (i.e., it cannot be parallelized), and that the message must be padded to a multiple of the cipher block size. One way to handle this last issue is through the method known as ciphertext stealing. Note that a one-bit change in a plaintext or IV affects all following ciphertext blocks.

Decrypting with the incorrect IV causes the first block of plaintext to be corrupt but subsequent plaintext blocks will be correct. This is because a plaintext block can be recovered from two adjacent blocks of ciphertext. As a consequence, decryption can be parallelized. Note that a one-bit change at the ciphertext causes complete corruption of the corresponding block of plaintext and inverts the corresponding bit in the following block of plaintext, but the rest of the blocks remain intact.

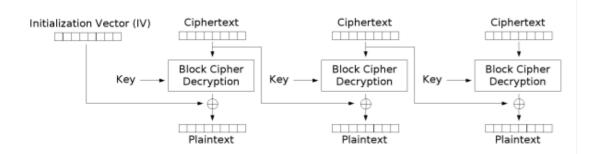

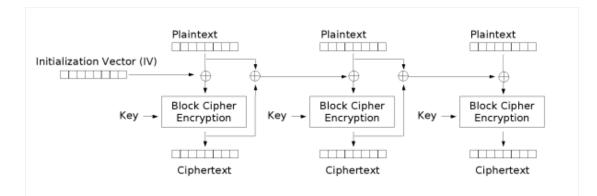

#### 1.3.4.4 Propagating Cipher-block Chaining (PCBC mode)

The propagating cipher-block chaining or plaintext cipher-block chaining mode was designed to cause small changes in the ciphertext to propagate indefinitely when decrypting, as well as when encrypting.

Encryption and decryption algorithms are as follows:

- $C_i = E_K(P_i \bigoplus P_{i-1} \bigoplus C_{i-1}), P_0 \bigoplus C_0 = IV$

- $P_i = D_K(C_i) \bigoplus P_{i-1} \bigoplus C_{i-1}$ ,  $P_0 \bigoplus C_0 = IV$

Figure 16: Propagating Cipher-block Chaining (PCBC) Encryption

Figure 17: Propagating Cipher-block Chaining (PCBC) Decryption

# 1.3.4.5 Cipher Feedback (CFB mode)

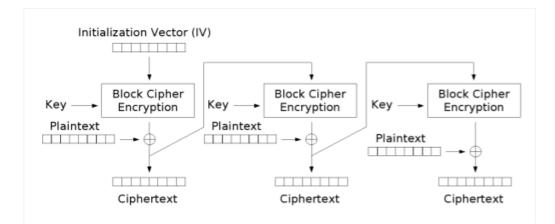

The cipher feedback (CFB) mode, a close relative of CBC, makes a block cipher into a selfsynchronizing stream cipher. Operation is very similar; in particular, CFB decryption is almost identical to CBC encryption performed in reverse:

- $C_i = E_K(C_{i-1}) \bigoplus P_i$

- $P_i = E_K(C_{i-1}) \bigoplus C_i$

- C<sub>0</sub> =IV

Figure 18: Cipher Feedback (CFB) Encryption

Figure 19: Cipher Feedback (CFB) Decryption

This simplest way of using CFB described above is not any more self-synchronizing than other cipher modes like CBC. If a whole block size of ciphertext is lost both CBC and CFB will synchronize, but losing only a single byte or bit will permanently throw off decryption. To be able to synchronize after the loss of only a single byte or bit, a single byte or bit must be encrypted at a time. CFB can be used this way when combined with a shift register as the input for the block cipher.

Like CBC mode, changes in the plaintext propagate forever in the ciphertext, and encryption cannot be parallelized. Also like CBC, decryption can be parallelized. When decrypting, a one-bit change in the ciphertext affects two plaintext blocks; a one-bit change in the corresponding plaintext block, and complete corruption of the following plaintext block. Later plaintext blocks are decrypted normally. CFB shares two advantages over CBC mode with the stream cipher modes OFB and CTR; the block cipher is only ever used in the encrypting direction, and the message does not need to be padded to a multiple of the cipher block size (though ciphertext stealing can also be used to make padding unnecessary).

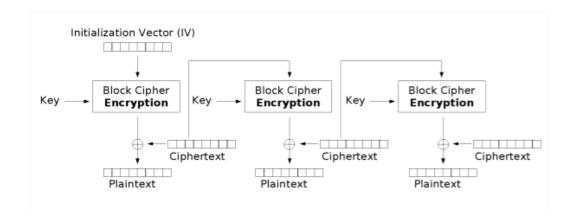

## 1.3.4.6 Output Feedback (OFB mode)

The output feedback (OFB) mode makes a block cipher into a synchronous stream cipher. It generates key stream blocks, which are then XORed with the plaintext blocks to get the ciphertext. Just as with other stream ciphers, flipping a bit in the ciphertext produces a flipped bit in the plaintext at the same location. This property allows many error correcting codes to function normally even when applied before encryption.

Because of the symmetry of the XOR operation, encryption and decryption are exactly the same:

- $C_j = P_j \bigoplus O_j$

- $P_j = C_j \bigoplus O_j$

- $O_j = E_K(I_j)$

- $I_j = O_{j-1}$

- I<sub>0</sub> =IV

Figure 20: Output Feedback (OFB) Encryption

Figure 21: Output Feedback (OFB) Decryption

Each output feedback block cipher operation depends on all previous ones, and so cannot be performed in parallel. However, because the plaintext or ciphertext is only used for the final XOR, the block cipher operations may be performed in advance, allowing the final step to be performed in parallel once the plaintext or ciphertext is available.

It is possible to obtain an OFB mode key stream by using CBC mode with a constant string of zeroes as input. This can be useful, because it allows the usage of fast hardware implementations of CBC mode for OFB mode encryption.

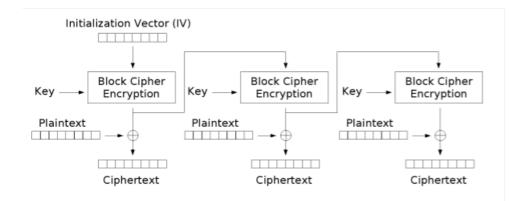

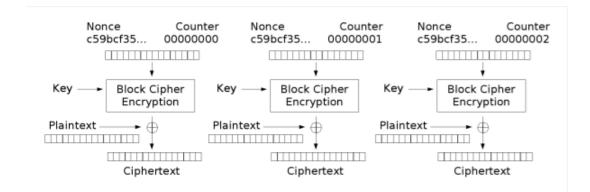

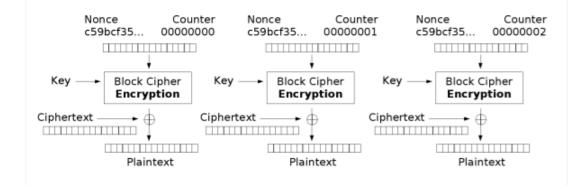

#### 1.3.4.7 Counter (CTR mode)

Like OFB, counter mode turns a block cipher into a stream cipher. It generates the next key stream block by encrypting successive values of a "counter". The counter can be any function which produces a sequence which is guaranteed not to repeat for a long time, although an actual increment-by-one counter is the simplest and most popular. By now, CTR mode is widely accepted, and problems resulting from the input function are recognized as a weakness of the underlying block cipher instead of the CTR mode. Nevertheless, there are specialized attacks like a Hardware Fault Attack that is based on the usage of a simple counter function as input.

CTR mode has similar characteristics to OFB, but also allows a random access property during decryption. CTR mode is well suited to operation on a multi-processor machine

where blocks can be encrypted in parallel. Furthermore, it does not suffer from the shortcycle problem that can affect OFB.

Figure 22: Counter (CTR) Encryption

Figure 23: Counter (CTR) Decryption

# 1.3.5 Applications

#### 1.3.5.1 DES Applications

The DES devices are used by the federal department and other government agencies for cryptographic protection of classified information. The federal government standardizes DES and specifies interoperability and security-related requirements for using encryption at the Physical Layer of the ISO Open Systems Interconnection (OSI) Reference Model in telecommunications systems conveying digital information.

Data encryption (and particularly DES) is primarily applied in:

- Electronic financial transactions: Automatic Teller Machines (devices limited to the issuance of cash or travelers checks, acceptance of deposits, or account balance reporting)

- Secure data communications, paving the road for e-commerce

- Secure video surveillance systems

- Encrypted data storage and proprietary software protection

- Access control: Software or hardware which protects passwords or Personal Identification Numbers (PINs) against unauthorized access.

DES is used in gateways to ensure privacy of user data. Also provides secure digital voice encryption in hand-held communication devices such as land mobile radio and dispatch control consoles. Data encryption through DES and is prevalent in fax machines. This allows secure data transfer over phone lines and prevents active interception of one's faxes at the receiver end, which is prevented by password entry by the user for fax retrieval. Networking applications use DES to provide network protection through data privacy, data integrity, access control and authentication. Message and file security, user authentication, secure remote system logon, and multilevel system access require data encryption, and DES algorithm is the most prevalent.

There is a need for control and access between different entities in a company's business environment, to provide secure communication between remote offices, business partners, customers, and travelling and telecommuting employees. Transmitting messages over the existing Internet backbone poses risks. VPNs were introduced to tackle exactly these issues to provide a company owned and managed network architecture. These networks provide scalable and comprehensive solutions by utilizing existing Internet backbone with additional hardware and software solutions. Strong data encryption is necessary to extend security and control features for which DES is the most commonly used. This provides secure network traffic through data privacy, data integrity, access control and authenticating entities by providing a gateway to each point of access into the business.

DES algorithm has been used for cell payload encryption in ATMs. The cryptographic units heighten security interfaces between a secure LAN and a public network. As data crosses this interface, the system encrypts each ATM cell's payload without affecting the header. Encrypted cells pass through the public network infrastructure and are decrypted upon arriving at the destination LAN. The benefit is that the user can conduct business as usual within the LAN and can encrypt the data as it enters the non-secure public network or non-secure area of a LAN. The system provides privacy and access control guarantees when using public ATM networks.

Data security in e-Commerce applications is required to have secure website, conduct financial transactions over the Internet, authentication of users to Intranets and Extranets, secure messaging, and secure storage of digital signature keys for signature generation and verification for digital documents.

Smartcard solutions are used in wireless communication, loyalty systems, banking Pay TV and government ID. These are used to provide strong authentication in e-business. These solutions are used with standard non-secured PCs. Consumers, vendors and financial institutions need to know that the transactions, documents and identities are authentic. DES algorithm is the most used encryption method in data security for the Smartcard solutions.

#### 1.3.5.2 AES Applications

AES can be used in any application that requires protection of data during transmission through the communication network, including applications such as electronic commerce transactions, ATM machines, wireless communication, Virtual Private Networks (VPN), and many others. Also it can be used as a part of the hardware or hybrid implementation of all major security protocols, including IPsec, SSL, IEEE 802.11a, and the ATM Forum Security Specification.

AES is now the industry standard for encryption. The National Security Agency (NSA) employs it for protecting secret information and industry uses the algorithm for creating commercially available encryption products.

File encryption and email encryption are two common applications for AES. File encryption protects the information on your hard disk or thumb drive. With encryption, your data will be secure even if your computer is hacked or your USB drive stolen. Email encryption protects your messages as they journey through the cloud and keeps them from being read by unintended recipients.

Thanks in large part to extensive input from the cryptographic community and the open review process, it can be trusted and is available to anyone who wishes to protect sensitive information.

### 1.3.5.3 IDEA Applications

Today, there are hundreds of IDEA-based security solutions available in many market areas, ranging from Financial Services, and Broadcasting to Government. IDEA is the name of a proven, secure, and universally applicable block encryption algorithm, which permits effective protection of transmitted and stored data against unauthorized access by third parties. The fundamental criteria for the development of IDEA were highest security requirements along with easy hardware and software implementation for fast execution.

The IDEA algorithm can easily be embedded in any encryption software. Data encryption can be used to protect data transmission and storage. Typical fields are:

- Audio and video data for cable TV, pay TV, video conferencing, distance learning, business TV, VoIP

- Sensitive financial and commercial data

- Email via public networks

- Transmission links via modem, router or ATM link, GSM technology

- Smart cards

# 1.4 Public-key Cryptography

The possibility of public key cryptography was first published in 1976 by Whitfield Diffie and Martin Hellman, who at the time were researchers at Stanford University. Ralph Merkle, a graduate student at the University of California, Berkeley, was studying the concept at the same time, but his ideas were not published until public key cryptography was well known. In their classic paper, Diffie and Hellman proposed the idea of public key cryptography and its use for exchanging keys, but not a public key cryptosystem. Several public key cryptosystems were subsequently proposed, but many were deemed insecure. Some systems are secure but are not practical for routine use either because the key is too large or because the ciphertext is significantly larger than the plaintext.

### 1.4.1 RSA

#### 1.4.1.1 Overview

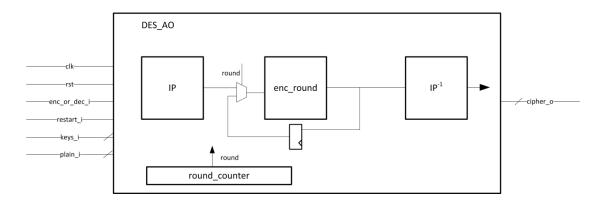

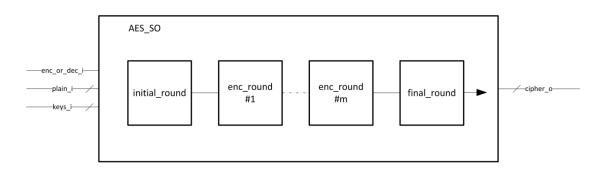

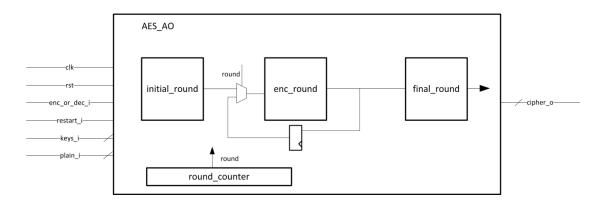

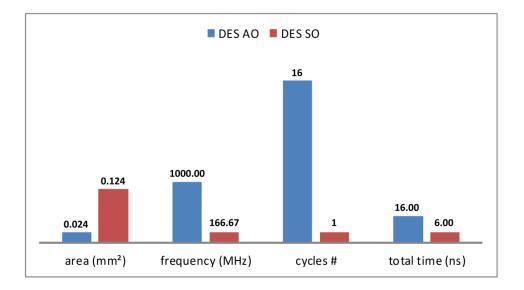

The RSA algorithm for public key cryptography, based on the idea that factorization of integers into their prime factors is hard to do, was proposed by (then) MIT professors Ronald Rivest, Adi Shamir, and Leonard Adleman in 1977. RSA has become one of the most successful algorithms for public key encryption and digital signatures. Many people had suspected that a government cryptographic agency such as the U.S. National Security Agency (NSA) had studied the possibility of public key encryption years earlier, but any evidence to this effect was classified. However, in 1997 CESG, a British cryptographic agency, released previously classified documents which revealed that James Ellis had discovered public key cryptography in 1970 and Clifford Cocks had internally published a version of the RSA algorithm in 1973. Nonetheless, Rivest, Shamir and Adleman are credited with the invention of RSA, and a patent for the algorithm was issued to MIT in 1983. The RSA patent will be discussed in more detail below.