### Έθνικο Μετσοβίο Πολγτεχνείο Τμημα ηλεκτρολογών Μηχανικών και Μηχανικών Υπολογιστών

Τομέας Επιστήμης Υπολογιστών Εργαστηρίο Μικροϋπολογιστών & Ψηφιακών Συστημάτων (MicroLab)

# Big Data Techniques Applied on Transient Integrated Circuit Simulations

### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Γρηγόριου Ν. Λύρα

Επιβλέπων: Δημήτριος Ι. Σούντρης Επίκουρος Καθηγητής

Γρηγόριου Ν. Λύρα

Αθήνα, Ιούνιος 2013

ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ Τομέας Επιστήμης Υπολογιστών Εργαστηρίο Μιχροϋπολογιστών & Ψηφιαχών Συστημάτων (MicroLab)

# Big Data Techniques Applied on Transient Integrated Circuit Simulations

## ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Γρηγόριου Ν. Λύρα

Επιβλέπων: Δημήτριος Ι. Σούντρης Επίκουρος Καθηγητής

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 20/06/2013

.... Κιαμάλ Πεκμεστζή Καθηγητής Δημήτριος Ι. Σούντρης Επίκουρος Καθηγητής ..... Νεκτάριος Κοζύρης Καθηγητής

Αθήνα, Ιούνιος 2013.

.....

**Γρηγόριος Ν. Λύρας** Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright ⓒ Γρηγόριος Ν. Λύρας 2013, Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# List of Figures

| 2.1  | Research Landscape                             | 9  |

|------|------------------------------------------------|----|

| 2.2  | OpenMP pragma in ngspice BSIM loading routines | 12 |

| 3.1  | Execution Framework                            | 17 |

| 3.2  | Mod counter signals                            | 18 |

| 3.3  | Execution Framework Toolchain                  | 21 |

| 3.4  | Sample netlist                                 | 22 |

| 3.5  | Sapp invocation                                | 23 |

| 3.6  | Partitioner invocation                         | 24 |

| 3.7  | Partitioner invocation example                 | 24 |

| 3.8  | Miner invocation                               | 25 |

| 3.9  | Miner invocation example                       | 25 |

| 3.10 | Task Line                                      | 25 |

| 3.11 | Hello world                                    | 26 |

| 3.12 | Hypervisor invocation                          | 26 |

| 3.13 | Hypervisor invocation example                  | 26 |

|      | sapp commmon.h                                 | 27 |

| 3.15 | Task definition                                | 28 |

| 3.16 | Signal definition                              | 29 |

| 4.1  | Inputs and Outputs of a 4x4 multiplier         | 32 |

| 4.2  | Subtractor of two signal pairs                 | 33 |

| 4.3  | Error calculation processj                     | 34 |

| 4.4  | RMSE error compared to hspice results          | 34 |

| 4.5  | Cross platform execution times v1              | 35 |

| 4.6  | Comparison of times of v1 against hspice       | 36 |

| 4.7  | RMSE error compared to spectre results         | 38 |

| 4.8  | Multiple transitions error                     | 39 |

| 4.9  | Temporal offset error                          | 40 |

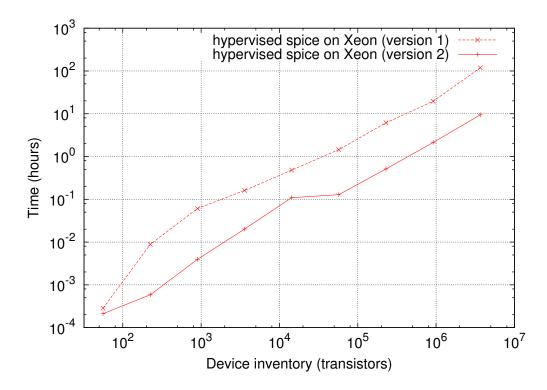

| 4.10 | Cross platform execution times v2              | 41 |

| 4.11 | Comparison of times of v2 against Spectre      | 42 |

| 4.12 | Comparison of execution times of v1, v2 against hspice and |    |

|------|------------------------------------------------------------|----|

|      | Spectre                                                    | 43 |

| 4.13 | Comparison of execution times of v1, v2                    | 44 |

#### Abstract

In the recent years, one can observe a shift in the software design principles. Earlier practices focused on the optimization of signle-thread execution. In an era where anyone has multicore systems at their disposal this approach is limiting. Therefore there is a need for flexible and scalable techniques for parallel application development. This project attempts to attack this issue with the use of a versatile development framework. This principle has been verified on the field of transient integrated circuit simulations.

Digital circuits are an integral part of modern world. Ever since the beginning of digital circuit design there has been a need for accurate simulation and verification. This need generated a family of software tools known as SPICE applications. The constant increase of the number of devices per silicon die has pushed this family of applications to the limit. The increasing device inventory of the simulated circuits is also pushing system memory and CPU times to their limit. Especially in systems with a unified memory hierarchy, the extreme demands in main memory causes transient simulations to halt due to bad allocation errors.

The proposed approach redirects this memory load incrementally to the file system. By partitioning the initial simulation to multiple substantially smaller ones we manage to decrease the amount of memory requested during each simulation.

### Περίληψη

Τα τελευταία χρόνια, μπορεί κανείς να παρατηρήσει μια στροφή στις αρχές του σχεδιασμού λογισμικού. Παλιότερες πρακτικές εστιάζουν στη βελτιστοποίηση της εκτέλεσης ενός νήματος. Σε μια εποχή όπου ο καθένας έχει στη διάθεσή του συστήματα πολλαπλών πυρήνων, η προσέγγιση αυτή είναι περιοριστική. Ως εκ τούτου, υπάρχει ανάγκη για ευέλικτες και κλιμακούμενες τεχνικές για την ανάπτυξη παράλληλων εφαρμογών. Το έργο αυτό, επιχειρή να αντιμετωπίσει αυτο το θέμα με τη χρήση ενός ευέλικτου πλαισίου ανάπτυξης εφαρμογών. Η αρχή αυτή έχει επαληθευτεί στον τομέα της προσομοίωσης ολοκληρωμένων κυκλωμάτων.

Τα ψηφιακά κυκλώματα αποτελούν αναπόσπαστο μέρος του σύγχρονου κόσμου. Από τις απαρχές της σχεδίασης ψηφιακών κυκλωμάτων υπάρχει έντονη ανάγκη για ακριβή προσομοίωση και επαλήθευση. Αυτή η ανάγκη δημιούργησε μια οικογένεια εφαρμογών γνωστές ως εφαρμογές SPICE. Η συνεχής αύξηση του αριθμού των συσκευών ανά τσιπ πυριτίου έχει ωθήσει αυτή την οικογένεια προγραμματιστικών εργαλείων στα όρια. Η αυξητική αυτή τάση στο μέγεθος των προσομοιούμενων κυκλωμάτων πιέζει τα υπολογιστικά συστήματα που εκτελούν τις προσομοιώσεις, τόσο στο επίπεδο της μνήμης όσο και στο επίπεδο χρόνων εκτέλεσης, στα όριά τους. Ειδικά σε συστήματα με ενιαία ιεραρχεία μνήμης, οι ακραίες απαιτήσεις στην κύρια μνήμη, σταματούν προσομοιώσεις λόγω ανεπάρκειας μνήμης.

Η προτεινόμενη προσέγγιση ανακατευθύνει αυτό το φορτίο σταδιακά στο σύστημα αρχείων. Καταμερίζοντας την αρχική προσομοίωση σε πολλαπλά σημαντικά μικρότερα τμήματα, καταφέρνουμε να μειώσουμε την ποσότητα απαιτούμενης μνήμης κατά τη διάρκεια κάθε προσομοίωσης.

# Acknowledgements

The work described in the present thesis has been carried out at the Microprocessors Laboratory and Digital Systems Lab of the School of Electrical and Computer Engineering of NTUA, where I conducted my thesis project, under the supervision of Prof. D.J. Soudris and Dr. D. Rodopoulos.

I am extremely grateful to both of them for their guidance, support and enthusiasm at all stages of this project. I would like to thank them for giving me the opportunity to discover the challenging world of SPICE simulations and Parallel implementations and for all, very generously, they taught me. Their positive attitude and their invaluable advice, whenever I needed it, along with their trust and the freedom they provided me work independently, are very much appreciated.

I would like to thank Dr. Antonis Papanikolaou for his precious work during this work. I thank him for his constant support and innovative ideas he contributed to this project. His experience, guidance and realistic point of view were of great importance to the development of this project.

My special thanks to all my friends in Athens, who contributed in making this story a really worth telling one, Thank you all for the moments we shared, everything we learnt, the fun we had, for being there when needed and for "bringing me back to life" when the work was dragging me down and also the one that gave me that little red book, and all the support they gave me.

Last but not least, I wish to thank my family. The completion of this work wouldn't be possible without their endless love and support. There are no words to express my gratitude... This thesis is dedicated to them.

Γρηγόρης Λύρας

# Contents

| 1 | Intr               | oducti  | ion                                  | 6  |  |  |  |  |

|---|--------------------|---------|--------------------------------------|----|--|--|--|--|

| 2 | Research Landscape |         |                                      |    |  |  |  |  |

|   | 2.1                | Introd  | luction                              | 8  |  |  |  |  |

|   | 2.2                |         | of the Art                           | 9  |  |  |  |  |

|   |                    | 2.2.1   | SPICE in general                     | 10 |  |  |  |  |

|   |                    | 2.2.2   |                                      | 10 |  |  |  |  |

|   |                    | 2.2.3   | SPICE in Generic Hardware            | 11 |  |  |  |  |

|   |                    | 2.2.4   | Industry Standard Tools              | 13 |  |  |  |  |

|   | 2.3                | Motiv   | ration                               | 14 |  |  |  |  |

|   |                    | 2.3.1   | SPICE in Variability Simulation      | 14 |  |  |  |  |

|   |                    | 2.3.2   | SPICE in Time-Dependant Verification | 14 |  |  |  |  |

|   |                    | 2.3.3   | Summary                              | 15 |  |  |  |  |

| 3 | Dat                | a Part  | titioning SPICE                      | 16 |  |  |  |  |

|   | 3.1                | Introd  | luction                              | 16 |  |  |  |  |

|   | 3.2                |         | iples                                | 17 |  |  |  |  |

|   |                    | 3.2.1   | Theoretics                           | 17 |  |  |  |  |

|   | 3.3                | Imple   | mentation                            | 20 |  |  |  |  |

|   |                    | 3.3.1   | User Manual                          | 20 |  |  |  |  |

|   |                    | 3.3.2   | References to Source Code            | 26 |  |  |  |  |

| 4 | Ben                | ichmar  | rks & Results                        | 30 |  |  |  |  |

|   | 4.1                | Introd  | luction                              | 30 |  |  |  |  |

|   | 4.2                |         | ation Description                    | 30 |  |  |  |  |

|   | 4.3                |         | ts                                   | 31 |  |  |  |  |

|   |                    | 4.3.1   | First Benchmarking Session           | 33 |  |  |  |  |

|   |                    | 4.3.2   | 3                                    | 36 |  |  |  |  |

|   |                    | 4.3.3   |                                      | 37 |  |  |  |  |

| 5 | Cor                | nclusio | ons & Future Work                    | 45 |  |  |  |  |

|    |       | Conclusions                 |    |

|----|-------|-----------------------------|----|

| Bi | bliog | raphy                       | 48 |

| 6  |       | endix<br>DATE 2013 Preprint |    |

# Chapter 1

# Introduction

During our time we have witnessed radical changes in the computing world. In the past decade the processing model has gradually evolved from singlethread execution to multithreaded execution and to massively parallel execution. Nowadays, everyday computing is handled by multiple processing nodes. Even smartphones have multiple asymmetric cores. Thus it can be understood that we need frameworks with great versatility that can adapt and port easily applications in various contexts. There is a constant need for tools that will be able to harness the new processing potential as materialized in multi- and many-core platforms.

One field that can greatly benefit from the multi and many core architectures is the field of Electronic Design Automation (EDA) and especially transient integrated circuit (IC) simulations. With the integration level race constantly increasing the devices per silicon dye circuit simulations become more complex and consume a lot more CPU time and system memory, thus increasing the development cost in multiple levels.

Another reason for resource hungry circuit simulations comes as an indirect result of aggressively decreased device feature sizes. With devices reaching lengths at the decananometer order, they also display

a stochastic behaviour. Thus designers need to be able to perform a more comprehensive circuit verification. This is usually achieved by Monte Carlo simulations for time zero device variability and through extensive simulations over large workloads for time dependent phenomena. As a result, it is highly desirable to explore the potential of High Performance Computing techniques (e.g. for big data) on the field of EDA applications, such as transient IC simulations. When we refer to circuit simulations we refer to SPICE applications. There have been attempts to optimise SPICE ever since it was introduced. Novel ideas such as mapping SPICE on custom hardware, such as Field Programmable Gate Arrays (FPGAs) or Graphics Processing Units (GPUs) have been explored, each with its advantages and disadvantages. Open source tools as well as enterprise solutions attempt to improve SPICE performance with the use of multiple threads of execution over a common memory hierarchy. However such approaches cannot overcome the memory wall imposed by the executing system.

In the context of this thesis we propose a framework that can provide a solution to the above problem through partitioning techniques. Since design houses don't have the source code of the commercial tools they use, the framework should remain agnostic with regard to the processing kernel per simulation using the black box paradigm. Instead of running a long massive simulation we propose the execution of multiple smaller ones and forwarding the signals among the simulations. The framework is able to handle multiple simulations and execute them in parallel using a graph of dependencies to determine when the simulations can be executed. Apart from the partitioning in the circuit axis, later referred to as *Node Tearing*, we propose temporal partitioning, referred to as *Workload Tearing*. The latter enables even greater parallelism provided the circuit at hand can be simulated in such a manner.

During our experiments we compared our results with two state of the art commercial tools, hspice by Synopsys and spectre by Cadence. For our simulations we used the open source ngspice. The runtime environment consisted of three different platforms, an Intel Xeon X3470 powered server, the Single Chip Cloud Computer prototype by Intel Labs and a virtual machine hosted on okeanos cloud service by GRNET. We conducted two benchmarking sessions using a multiplier as the circuit to be simulated. During the first benchmarking session we managed to overcome the memory wall imposed by the executing system and we verified the accuracy of the framework. In the second benchmarking session we improved the performance of the framework using more advanced partitioning techniques.

In conclusion we managed to overcome the limitations imposed by the runtime system. The framework we propose can produce accurate results for circuits far larger than the industry standard tools used, with significant speedups. A subset of this work has been accepted in the proceedings of the Design Automation and Testing in Europe Conference, held in Grenoble, France. A preprint of the respective paper can be found in Appendix A.

# Chapter 2

# Research Landscape

# 2.1 Introduction

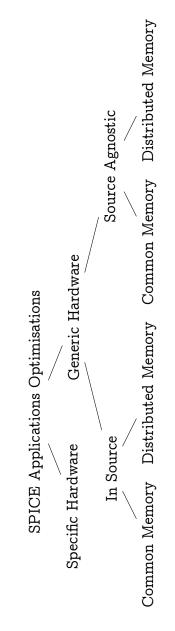

In this chapter of the thesis we present the current landscape and the research areas regarding optimisations in SPICE applications. In order to achieve this we use the graph shown in Figure 2.1. This graph shows binary splits of the field of study. Each path in the tree structure above, describes a series of design choices one has to make when optimising SPICE applications.

As shown in Figure 2.1 we can divide the field based on the hardware type used, the level of the performed optimisations and the memory hierarchy. Regarding the level of the performed optimisations, we use the term *In Source* to designate optimisations that take place in the application source and the term *Source Agnostic* for optimisations that take place without interacting with the SPICE Application source code. Each category is a binary split of it's parent and the both siblings are complementary. For each leaf we have a path from the root to the leaf that designates the design choices made. For example if one chooses the last leaf on the right the path would be *Generic Hardware->Source Agnostic->Distributed Memory*, describing the equivalent design choices in the development of their application.

Figure 2.1: Research Landscape

# 2.2 State of the Art

The need for viable transient circuit simulations has played a significant role in shaping the progress of the EDA industry. This is apparent if one considers the number of EDA tools developed. An area where a lot of work has been delivered is integrated circuits (IC) simulation. For the IC

Grigorios N. Lyras

Page 9 of 78

domain, the tools that have been produced belong to a family of software tools known as SPICE applications.

The "original" SPICE was developed at the Electronics Research Laboratory of the University of California, Berkeley by Laurence Nagel [12]. It changed the skyline of the circuit design world and many research teams started working on derivatives of this work. A lot of work was put in improving the performance of the initial approach with the use of new numerical methods and more efficient code [11]. Compiler optimisations and smarter computer architectures combined with the increasing clock speeds of CPUs provided the EDA industry with enough processing power for the increasing simulation demands. However this approach has reached a saturation point, since CPU frequencies are no longer increasing at the same rate, in comparison to previous years. This leads to the conclusion that we need to explore other means in order to make the ever demanding IC simulations viable for the years to come.

Producing results faster and with less resource consumption along with exploiting parallel architectures are goals well set in the HiPEAC roadmap for the next 10 years [16, 3].

### 2.2.1 SPICE in general

Since it's first release in 1973 SPICE derivatives have reached a significant level of maturity. The past decade has shown that single thread execution has it's limits. Thus there is a need for SPICE to evolve to the next level. Mapping SPICE to parallel architectures is a multidisciplinary problem and there are quite a few attempts each with advantages and disadvantages.

### 2.2.2 SPICE in Specific Hardware

One of the software design constraints when developing SPICE is the running platform. Running SPICE on specialized hardware can provide significant speedups. A fine example of this concept is an implementation of SPICE running on Field Programmable Gate Arrays (FPGAs) [6]. This implementation parallelized the different tasks of the SPICE simulator giving maximum speedup up to eleven ( $\times 11$ ). The idea was to map each of the three demanding tasks to a separate solver. So SPICE was broken down to the Iteration Controller, Model Evaluation and Sparse Matrix Solver components that could run independently. However due to the limitations

of the hardware it could produce results of up to thirty thousand (30000) transistors.

Another attempt to run SPICE in specific hardware took advantage of the processing potential of NVIDIA GPUs as described in [5].

In this project the developers mapped *device model evaluation* to the GPU cores enabling parallelism at a device level. However it required significant effort in order to rewrite the kernels for the CUDA architecture. The speedup achieved by this approach was around three (3) with simulation capacity of about eight thousand (8000) transistors.

A few years later *OmegaSim* was introduced, based on this approach. It was a massively parallel commercial SPICE implementation, designed to run on GPUs by Nascentric. The product was based on the NVIDIA's Tesla hardware platform and claimed that "Using NVIDIA's Tesla platform we can perform circuit simulations in minutes to hours that would previously have taken hours, days and weeks," [1]. The company is now defunct and assets have been purchased by a customer [13].

These implementations hold significant results and insight on the steps that can be taken to parallelize SPICE using this kind of hardware. Using hardware specially designed for the task at hand can give tremendous speeds at the cost of performing platform-specific alterations to the applications, in order to enable efficient mapping. This can be interpreted both as cost of configuring and maintaining the hardware as well as the cost of porting the software from one platform to another which can be a task of significant effort. On the other hand, working with generic hardware allows great versatility and portability which seem to be key concepts for application design.

### 2.2.3 SPICE in Generic Hardware

When one wants to parallelize SPICE for generic hardware it's common to work in the SPICE source. This enables the developers to have finegrained control over the exact structures to run in parallel. Ngspice has a series of OpenMP pragmas for this exact purpose as shown in Figure 2.2. Commercial products have also provided this functionality which can take advantage of the multiple cores of the running platform. That way the developers improve the application speed without compromising its versatility. Moreover, using industry standard architectures and setups, the end users can run the SPICE application of their preference on the

Grigorios N. Lyras

Page 11 of 78

```

1 #pragma omp parallel for num_threads(nthreads) private(here)

2 for (idx = 0; idx < model->BSIM4InstCount; idx++) {

3     here = InstArray[idx];

4     good = BSIM4LoadOMP(here, ckt);

5 }

```

Figure 2.2: OpenMP pragma in ngspice BSIM loading routines

hardware they already own.

This approach seems to apply on the new multiprocessor context towards which the computer systems market has shifted [4, 3, 16, 7]. This assumes that the runtime environment has enough resources to finalise the simulation at hand. However this is not always the case. In unified memory hierarchies the requests for memory allocation consume a common resource. Thus many researchers and circuit designers may reach the memory wall, when running transient simulations with many devices and using complex device models. In order to solve this problem many design houses invest large amounts of money for computer systems with massive resources [10]. Another angle to attack this issue would be to design the SPICE application on a multiple machine context. This would mean that one would use a Message Passing Interface (MPI) framework over a computer cluster context or a grid.

The aforementioned approaches require a lot of development time, specifically for each runtime system in order to achieve optimality. This means that one has a solid understanding of the target platform and can work on the source code of the SPICE application. But when EDA software companies sell their products they obviously don't release the relative source code. The design houses rely on the EDA software companies. Features of a computer system such as cache size and memory size vary greatly among processors even if they belong in the same family (x86,x86\_64). Thus it is an extremely difficult task to build software that runs optimally on a range of platforms even if this range is restricted by the underlying architectures. So relying on the EDA software companies cannot always produce optimal results since the tools provided are not flexible enough. From the above observations, it is highly pragmatic to treat SPICE applications as *black boxes*.

The monolithic *black box* paradigm doesn't provide the end users with the required flexibility one would need from an EDA tool. So instead of attempting to parallelize the EDA tool by performing alterations in its code base, we can treat it as a *black box* and perform development on top of

an existing SPICE executable. Running multiple smaller instances of the monolithic simulator, while breaking the initial simulation into multiple smaller ones, we can execute the partial simulations independently. That way we are able to parallelize an application without really knowing how it operates internally.

## 2.2.4 Industry Standard Tools

The work of this thesis is going to be compared to industry standard SPICE applications. Parallel implementation of SPICE is not a new idea. Significant work has been done on part of the EDA industry. Many leading companies in the field have put effort into building parallel versions of their software. Two products that have such capabilities are **hspice** by *Synopsys* and **spectre** by *Cadence*. In the context of this thesis we used those commercial tools in order to have an objective and realistic estimation of the correctness and the computational viability of our proposal.

### Spectre features

**Specte** is a Circuit Simulator software developed by *Cadence*. It claims to provide improved capacity over other simulators due to effective convergence algorithms for large circuits. Dynamic memory allocation, according to the manual, allows the Spectre circuit simulator to use less than half as much memory as SPICE for large circuits. The developers also claim that it runs two to three and two to five times faster than SPICE for small and large circuits respectively. Models and accuracy are also improved.

### **HSpice** features

**HSpice** is a Circuit Simulator by *Synopsys*. It claims to be a performance leader in the field on both single and multi core computers. It features a client-server model that boosts the performance and improved integration. A significant speedup for large netlists is also claimed.

### Summary

Both of those tools are well known and industry standard. They enable the utilisation of threads and numerical methods to exploit the capabilities of

the multi core architectures available in modern processing environments. For our implementation we used the open source alternative **ngspice** and compared the results and resource consumption with the commercial tools.

# 2.3 Motivation

# 2.3.1 SPICE in Variability Simulation

The past 10 years in digital circuit design have been a race on the integration levels and the number of transistors per silicon die. This trend has led manufacturers to very high integration levels up to a point. Latest technology has reached a significant bounding factor, device variability.

In other words the smaller the gate lengths of the transistors, the more they exhibit a stochastic behaviour [15]. The greater the integration factor of a circuit the greater the variability it presents. Thus there is a need for variability verification for very large circuits [14]. This has lead to the conception of a new field where circuit simulation can provide insight, that of *Device Variability*.

In order to verify the behaviour of a circuit, designers often have to resort to extensive simulations. Particularly for time zero device variability, engineers often have to resort to Monte Carlo simulations which are immensely intensive [9]. This methodology involves iteration of the same simulation, while sampling various random variables that represent the degrees of circuit variability. The pool of statistical samples has to be large enough to cover all of the n-stochastic-variable space. These simulations are very intense with regard to computational power and also have great need for system memory due to the size of the circuits.

### 2.3.2 SPICE in Time-Dependant Verification

In circuit design it is often necessary to study phenomena that evolve in the axis of time. This requires very long transient simulations. Such simulations require large amount of computational power in order to complete and are often brought to a halt due to insufficient resources. This kind of Time-Dependent Verification in circuit simulations requires viable simulations over extensive workloads.

As stated in [15] digital circuits behaviour varies, not only at time zero (immediately after manufacturing), but also as the lifetime of circuit progresses. As argued in [14], in order to account for workload dependent circuit variability, engineers need to perform transient simulations of long workloads. These simulations require large amounts of time and computational resources.

## 2.3.3 Summary

In the context of this thesis, we claim that we can benefit greatly by providing viable and relatively fast SPICE simulations. As circuits continuously grow to larger inventories it is understood that simulations require continuously greater amounts of resources. The memory wall is a bound that we need to overcome in order to be prepared for the circuits to be simulated for the years to come. Both Variability Verification and the study of Time-Dependant phenomena provide a target group that requires simulations that evolve over a large range of time for large circuits. Thus we conclude that researchers, designers and developers in these fields can greatly benefit from faster and less resource hungry simulations.

# Chapter 3

# **Data Partitioning SPICE**

### 3.1 Introduction

In our implementation we used a series of techniques that are applied when handling big data, *data partitioning* in particular. This chapter describes the tools and techniques we used to apply the data partitioning principles in circuits simulations.

The phases of *data partitioning* consist of the *Domain Decomposition*, a process when the data is split into subsets, the *Execution*, when the application runs performing the actual calculation, and the *Data Recollection* when the distributed data is recollected and reconciled in order to produce the final results.

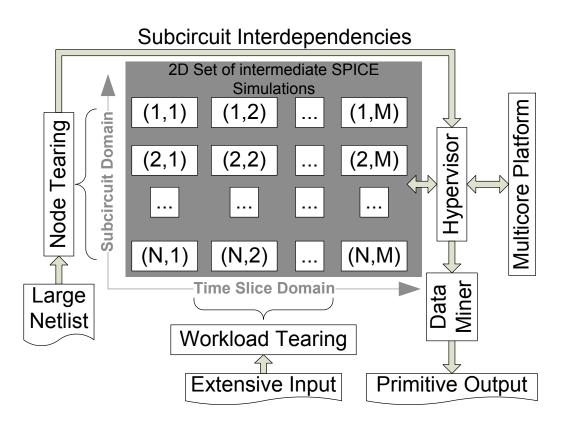

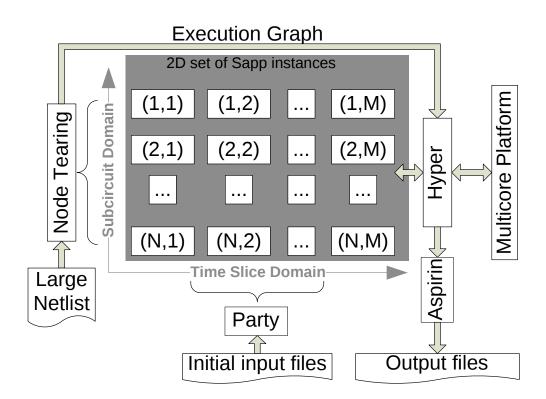

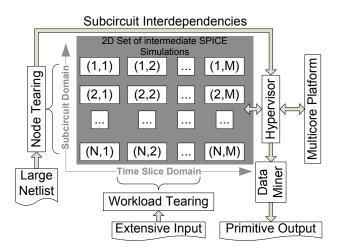

The suggested framework consists of an input signal **partitioner**, a generic **hypervisor**, a SPICE kernel **wrapper** and a data **miner**. This set of tools enables the handling of workload tearing, task dependencies, output forwarding and data mining. An abstract visualisation of the framework is shown in Figure 3.1.

Figure 3.1: Execution Framework

# 3.2 Principles

# 3.2.1 Theoretics

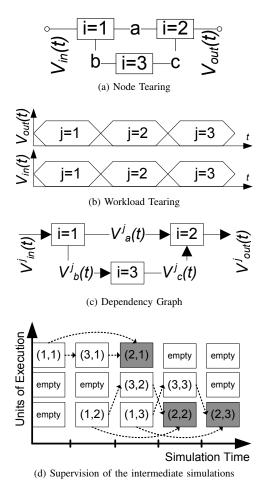

The leading principle behind this project is *data partitioning*. We apply two concepts of partitioning, on the time axis which will be further referred to as *workload tearing* and on the circuit level which will be referred to as *node tearing*.

### Workload Tearing

Workload Tearing consists of breaking the input signals on appropriate time slices. One of the challenges was to identify those time slices, and the overall timeslice duration. Input signals are in the form of PieceWise Linear (PWL) sources described in text files. This form is easily parsed and can be used directly as input following specific naming conventions described in the next section.

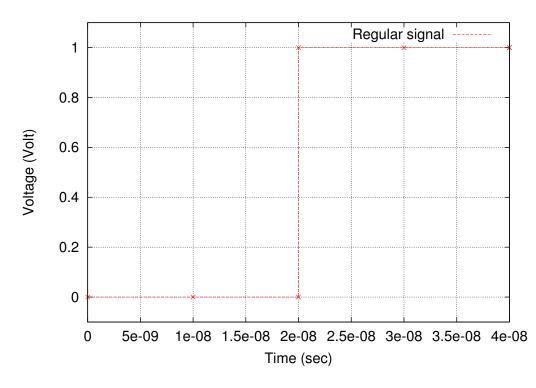

For slicing the input signals we used two methods. For the first version we generated PWL signals that had a specific form. The pulses were in a regular pattern and each pulse contained four points as shown in Figure 3.2. When the input signals have this form, one can easily partition the signals with the use of a mod counter every four points and generate the partitioned output signals. However, in the general case that may not be applicable. Input signals might not be that regular due to the characteristics of the simulation at hand. Thus a new more advanced partitioning scheme needs to be applied.

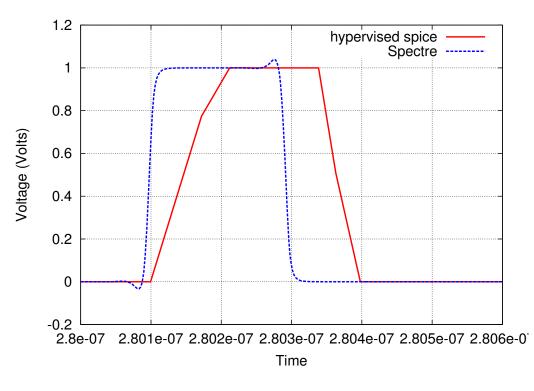

Figure 3.2: Mod counter signals

In order to tear the input signals we need to specify timeslice durations which will be used for the partitioning proceed. Each timeslice has to contain whole pulses of the input signals meaning that there has to be a minimum amount of time after a transition otherwise the accuracy of the simulation will be compromised. In order to achieve that we use a simple but effective method. Since we only perform digital simulations we can safely partition in times where all signals are constant and in a stable state. By stable state, we define one of the two states: logical 0 or logical 1. This way all the transitions will be contained in the partitioned signals.

Additionally we define a minimum time after each transition. We identify the regions where all signals are constant simultaneously and we perform the slicing at these parts.

One should note that we are dealing with digital signals. In case of analog signals that are not latched to constant voltage levels, one would have to interact with the DC operating point solver of SPICE. This task falls beyond the current thesis.

### Node tearing

Node tearing is a well-established technique and many approaches have targeted efficient implementations. In the context of this thesis, we do not elaborate on efficient node tearing algorithms but exploit the modular syntax of a SPICE netlist with a specific subcircuit that is replicated. This requires the user to define the components of the circuit at hand and the dependencies amongst them. After this analysis is complete then the end user can easily compose the configuration file that will be parsed by the **hypervisor** of the framework. This file will describe all the requested input files and all the output files for the simulations along with the dependencies. The user has to follow the same naming conventions described in the next section.

### Signal filtering

When performing digital simulations we comprehend that we don't need multiple points when the signal is in a stable state. Where stable state is defined by the logical 0 and 1 values. SPICE uses adaptive step sizing to stride over such intervals. So while a signal is in one region or the other we only need two points to identify its value, since it's essentially constant. However, the adaptive step sizing, as implemented in ngspice, is highly suboptimal and produces many points. As a result, signal filtering is required, in order to avoid storage of useless time, voltage points between intermediate simulations.

Keeping the above in mind we can devise a filtering function that replaces all the points in a constant signal region with only two points. This will apply only in the logical 0 and logical 1 states of the signal while leaving the intermediate points intact. This procedure can greatly decrease the signal size. In some cases even an order of magnitude, with no observable loss in data. That we can greatly reduce the number of points kept in the signals

and thus improving performance and reducing the memory footprint of the output PWL files of each simulation.

While having this piece of information we can apply an even more crude filtering method if it proves crucial to increase drastically the performance. If in our simulation we claim that we do not care about any intermediate points, we can simply ignore them and perform filtering based on that assumption. This will ensure the preservation of transition information for digital simulations while minimising the signals' size.

### Execution Grid

Instead of task oriented parallelization we implement a data oriented parallel framework. The two axis of partitioning, *Workload Tearing* and *Node Tearing* constitute a 2-D space of simulations as shown in Figure 3.1. These simulations will be handled by the framework and run on the given platform.

# 3.3 Implementation

In Figure 3.3 we observe the set of tools implemented, namely the hypervisor (hyper), the main execution kernel (sapp), the partitioner (party) and the data miner (aspirin). The figure also shows the workflow in order to use the framework. The process is rather simple. Initially one has to partition the input signals with the use of **party**. Afterwards one will generate the execution graph and spawn **hyper**. Hyper will parse the execution graph and spawn as many instances of **sapp** are needed to complete the simulation. Finally the user will spawn **aspirin** in order to reconcile the output signals.

### 3.3.1 User Manual

### Netlist generation

The netlist generation process is simple. The user has to define the circuit as a number of independent components that can be simulated separately. These subcircuits have a number of inputs and outputs. These have to be enumerated in order to be substituted properly by the forwarded input signals.

Figure 3.3: Execution Framework Toolchain

The inputs will be handled by the wrapper provided that the netlist of the subsircuit uses a simple naming convention. The names of the input signals in the netlist wiring instantiation need to be in the form "inX" where X is the number of the input starting from 0. What's more, in the same netlist there need to be a series of include lines in the format ".include INPUT%03d".

The simulation duration can either be constant and common for all timeslices or be different due to custom partitioning. If the first is the case, then the user must ensure that the runtime folder does not contain a timeslice log file. The timeslice log file is named always "tslices.log" so it is easy to recognise and remove if necessary.

In the case of custom timeslice duration the timeslice log file is of utmost importance. This special file is part of the framework's partitioning mechanism and provides the start times and durations for each of the timeslices. This file has always the same name "tslices.log" and should be handled with care. It is in essence a two column data file in the format "<start time> <duration>". In the general case this file should be generated by the **partitioner** and used by the wrapper and the miner. When this file

Grigorios N. Lyras

Page 21 of 78

is present in the directory running the simulation, the wrapper reads it's contents and replaces the ".tran" line in the netlist filling in the proper duration for each execution. So one should be careful not to delete it by mistake since the wrapper as it is at the moment will simply ignore the duration parameters leading to possibly erroneous results.

Output handling follows a similar approach to the input signal handling. The ".print" line in the netlist needs to hold the signals to be forwarded to the next simulation before any other signals of interest. These do not need to follow a specific naming convention but the same numbering as in inputs should be applied to avoid confusion. Below (Figure 3.4) is a sample netlist following the aforementioned conventions.

```

** A 2 x 2 multiplier based on the FA* module **

1

2

** Subcircuits & Modelcards **

3

.include modelcard.nmos

4

.include modelcard.pmos

5

.include subcircuits.cir

6

7

** DC Sources **

8

Vvdd vdd 0 1.0

9

Vvss vss 0 0

10

11

** Multiplier Instantiation (per FA* Module) **

12

X0 vdd vss vss

in0 in2 vss

product0 wire0

module

13

X1 vdd vss vss

in1 in2 wire0 wire1

module

wire2

14

X2 vdd vss wire1 in0 in3 vss

product1 wire3

module

15

X3 vdd vss wire2 in1 in3 wire3 product2 product3 module

16

17

** Inputs **

18

.include INPUT001

19

.include INPUT003

20

.include INPUT002

21

.include INPUT004

22

23

**Simulation Definition **

24

.tran 800.00000ns 800.00000ns

25

26

** Output File Definition **

27

.print tran v(product0) v(product1) v(product2) v(product3) i(Vvdd) i(Vvss)

28

```

Figure 3.4: Sample netlist

### Wrapper (Sapp)

The wrapper we used for *ngspice* is a pure ANSI C tool that was developed for this project. Its role is to prepare and execute an *ngspice* simulation and harvest the outputs. **Sapp** (the wrapper name) is statically linked against the *microsig* signal library developed for this project. As it can be seen in Figure 3.5, **sapp** parses all the information it needs as command line arguments. It copies the contents of the input files to its private namespace as designated by the timeslice id and circuit id and generates the PWL signals that will be used for the particular simulation. It also copies the netlist module and then inserts the PWL input filenames in its personal netlist module. If a timeslice log file is available it reads it and inserts the appropriate ".tran" line in its netlist. Otherwise it ignores this step.

At this point the simulation is ready to start. So it is executed with the use of the system command. If the simulation finishes successfully the wrapper is going to parse the simulation output. While in this step the wrapper will also apply a simple 0-1 high-Z filter on the output signals in order to decrease its size. Afterwards it writes each output as designated by the command line arguments <output 1> <output 2> and so on. After that step the wrapper will delete all intermediate results from the folder to save space. If the simulation finishes with an error status code the wrapper will not try to parse the erroneous output nor delete the files to enable debugging.

Figure 3.5: Sapp invocation

### Input signals generation

The input signals are initially waveforms represented in the PWL format. This is a well known format used by all typical SPICE applications and is used to great extent. Signals in PWL format are relatively easy to parse and generate. The framework can effectively use any set of signals already generated for simulations and does not require any specific handling. When the initial signals are prepared all the end user has to do is invoke the **partitioner** with the PWL files.

The partitioner is a simple tool written in C using the microsig library which was developed for this project. The partitioning process for the

Grigorios N. Lyras

Page 23 of 78

user is as simple as running one shell command (Figure 3.6). Beware of the double quotes " in the command. It is important to add the quotes so that the shell will not expand *\*.in* to all the files in the folder. It is often needed to partition a large number of files and passing them all as command line arguments is impractical. The file pattern is used instead and the **partitioner** searches the current directory for all the files that satisfy the pattern.

For example if we use the command in Figure 3.7 the **partitioner** will search the current directory for all the files that have the suffix ".in". Thus files such as "a0.in", "a1.in" and so on will be partitioned in at most 10 timeslices. Due to the partitioning theory limitations at the moment, the **partitioner** might be unable to provide the requested timeslices. However it will attempt to provide as many as possible. For reasonable slicing the process will provide the requested number of slices.

It is important to note that the initial files are not erased written over or otherwise tampered with. The **partitioner** will use the filename as a base and create a series of files in the format "%04d\_base.prty". This ensures that no matter what the initial files are the output files will not overwrite or corrupt the input. The output files are simple two column raw signals that are handled in the runtime by the wrapper.

partitioner <requested timeslices> "<input file pattern>"

Figure 3.6: Partitioner invocation

partitioner 10 "\*in"

Figure 3.7: Partitioner invocation example

Data mining - Output signals recollection

When the simulation is complete multiple output files will be generated. For every signal there will be n output files containing part of the full output where n is the number of timeslices. These output files will be zero aligned and have to be collected in order to produce the complete output signal. In order to achieve this we created a miner that takes into consideration the number of timeslices the timeslice log in order to generate the final signal. As shown in Figure 3.8 the miner also takes the signal base name as input. The output signals are named in a specific manner with the timeslice index as a prefix (000 <br/>base name>, 0002 <br/>base name>..). Thus the miner

Grigorios N. Lyras

Page 24 of 78

will gather all the signals that have the same <br/>base name> as a suffix and merge them to create the final output. In Figure 3.9 we call the miner for 10 timeslices using the file tslices.log to collect all the 01\_vsout bit signals.

miner <slices> <timeslice log> <base name>

Figure 3.8: Miner invocation

miner 10 tslices.log 01\_vsout

Figure 3.9: Miner invocation example

#### Task graph generation

One of the most complex tasks one has to complete in order to use the framework is the task graph generation. This constitutes the core of the implementation. The task graph will be parsed by the **hypervisor** and provide all the information that is needed to run the entire simulation.

The execution graph or task graph is a text file. The first line contains the program to be executed, which in our case is the ngspice distribution installed in the executing platform. Each of the following lines contain a task. A task line is as shown in Figure 3.10. The arguments are the command arguments that will be passed to the executing program. For example we can have an execution graph as shown in Figure 3.11. The hypervisor understands that the task WORLD depends on the task HELLO. In that context it will execute "/bin/echo Hello" which will print "Hello" and afterwards it will execute "/bin/echo world" so in the end it will print "Hello world".

<task name> <number of dependencies> <dep 1> <dep 2> .. <arguments>

Figure 3.10: Task Line

#### Hypervisor

The hypervisor, as shown in the task graph generation process, is a completely agnostic tool with regard to what it is running. The hypervisor runs only one program, the one specified on the first line in the configuration file. This design choice may seem a bit rigid but allows great flexibility. The invocation process is again simple. As shown in Figure 3.12 the only

/bin/echo HELLO O hello WORLD 1 HELLO world

Figure 3.11: Hello world

options needed are the execution nodes available and the task graph that was created beforehand. The example in 3.13 shows the command that we used to run the **hypervisor** for 48 execution nodes (the SCC).

When the **hypervisor** parses the file it creates multiple tree structures in the system memory representing the dependencies. All roots are available to be executed since they have no dependencies. Each available task can be executed as long as there are resources (execution nodes) available. When the task completes the resource is released and another task can be executed on that node. This is practically implemented with the abuse of the return values when the processes die. The scheduling algorithm is a simple first come first served algorithm using dual ended queues. Prioritisation could be handled if instead of queues we would have heaps but that is left as future work.

hyper <available execution nodes> <input file>

Figure 3.12: Hypervisor invocation

hyper 48 executionGraph

Figure 3.13: Hypervisor invocation example

### 3.3.2 References to Source Code

Wrapper (sapp)

Sapp is a C application used to prepare and run an ngspice kernel and afterwards break the ngspice output file to simple two column files per output bit. It uses the microsig library developed in the context of this thesis. The source code contains a properly written Makefile for it's compilation. It uses two macros in order to specify the command to be run. When compiling with the RUN\_ON\_SCC macro defined, the ngspice command is the ngspice compiled for the SCC in a path the SCC can read. This can be extended with the use of multiple RUN\_ON directives and equivalent NGSPICE CMD LINE macros. The macros are defined in the file

Grigorios N. Lyras

Page 26 of 78

"sapp\_common.h" and the specific part regarding the command executed is shown in Figure 3.14.

```

#ifndef NGSPICE_CMD_LINE

#if RUN_ON_MITSOS

#define NGSPICE_CMD_LINE "/shared/master/bin/ngspice -b %s 2> %04d_%05d.log > %04d_%05d.out"

#elif RUN_ON_SCC

#define NGSPICE_CMD_LINE "/shared/master/bin/ngspice -b %s 2> %04d_%05d.log > %04d_%05d.out"

#endif /* where do you want to run */

#endif /* NGSPICE_CMD_LINE */

```

Figure 3.14: sapp\_common.h

### Hypervisor (hyper)

**Hyper** is a C++ application used to handle the graph of task dependencies describing the simulations. It parses the execution graph and spawns any task that is ready to run on the available execution nodes.

#### Run process

The run process is simple. When there are available execution nodes and jobs that are ready to be spawned the hypervisor forks to new process and spawns task on the given platform by executing the run function. The run function is currently defined at compile time. The run function for the platforms implemented currently uses the system command in order to spawn the configured application. When the run is complete the forked process exits using the execution node id as an exit value.

When the father process runs out of execution nodes or runs out of processes that can be spawned it performs the waitpid system call in order to release an execution node that was previously used. When a process exits the hypervisor identifies the execution node and, with the use of a lookup table, the task that was running. For the task that was running and the hypervisor decreases the reference counter of it's children. If the reference counter reaches zero the child is ready to be put in the available jobs queue.

The exit code conception limits the number of parallel processes to 256. This limitation can easily be overcome with the use of a multi-level spawn process. As an example we can spawn a hypervisor that spawns 256 hypervisors that can in turn handle 256 execution nodes each. Thus the number of parallel processes that can be handled increases exponentially. Extension of the number of parallel processes can also be performed with the use of the pthreads API or any equivalent framework.

#### Data Structures

In this section we explain some of the basic data structures that were developed and used in the hypervisor.

#### Task

The task is a simple data structure (Figure 3.15) containing the command to be executed as a string, the number of dependencies and a vector of the indices of it's children. This allows the hypervisor to decrease the dependencies of the children of every task that is completed.

| 1  | class task {                                     |

|----|--------------------------------------------------|

| 2  | <pre>std::string command;</pre>                  |

| 3  | <pre>int dependencies;</pre>                     |

| 4  | <pre>std::vector<int> children;</int></pre>      |

| 5  | public:                                          |

| 6  | <pre>task(const task &amp;N);</pre>              |

| 7  | <pre>task(int deps, std::string cmd);</pre>      |

| 8  | ~task();                                         |

| 9  | <pre>bool decDeps();</pre>                       |

| 10 | <pre>bool ready();</pre>                         |

| 11 | <pre>void addChild(int i);</pre>                 |

| 12 | <pre>const char *getCmd();</pre>                 |

| 13 | <pre>int childrenN();</pre>                      |

| 14 | <pre>std::vector<int> getChildren();</int></pre> |

| 15 | <pre>void print();</pre>                         |

| 16 |                                                  |

| 17 | };                                               |

Figure 3.15: Task definition

### **Execution** Nodes

For the handling of the execution nodes the data structure is a simple dual ended queue. During the initialization stage the number of execution nodes indicated by the command line arguments is inserted in the deque. When one job needs to be started, if there are available execution nodes, the hypervisor pops the front of the queue and spawns the job on that execution node using the run function defined for the given platform.

### Partitioner (party)

The **partitioner** is a C application developed for the partitioning of input signals. It handles PWL input signals and outputs the partitioned signals as described in the previous section. For the representation of the signals it uses the microsig library signal datatype as shown in Figure 3.16.

```

struct _signal {

1

uint32_t len;

2

uint32_t alloc;

3

double *time;

4

double *value;

5

};

6

7

typedef struct _signal signal;

8

Figure 3.16: Signal definition

```

### Miner (aspirin)

The **miner** is a C application that handles the recollection of signals after the simulation is complete. It uses the same library as the **partitoner** for the signal handling. Specifically it parses the 2-column signals, shifts them according to their respective timeslice offset, and appends them in the right order.

# Chapter 4

# Benchmarks & Results

### 4.1 Introduction

In this chapter of the thesis we provide details regarding the benchmarks we performed and their respective results. The simulation outputs were compared with the reference values and we also compared the execution times of the hypervised version and the reference tool.

During the verification process of this thesis we performed two benchmarking sessions. During the first session we compared the results of the simulations using the results of **hspice** as reference values. For the second benchmarking session we improved the hypervised version and used **spectre** as the reference tools.

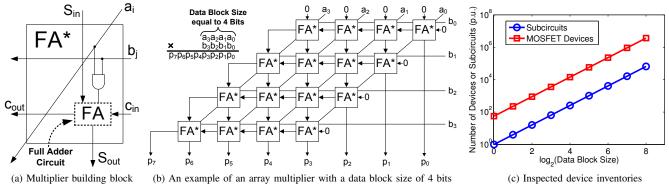

# 4.2 Simulation Description

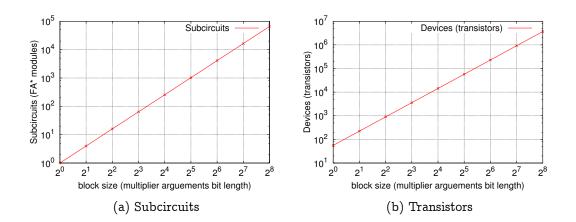

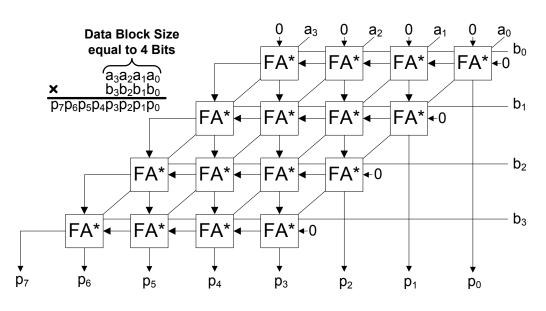

To verify the proof of concept of the implementation we run a set of benchmark simulations. The circuit of choice was a typical multiplier described in [17]. This circuit features great modularity and scales easily as shown in Figures 4.1(a) and 4.1(b). This inherent quality of the circuit allows the verification process to explore large device inventories. Obviously, the modularity of the circuit provides great speed and efficiency when it comes to simulations with the use of our tool. However, even circuits that are not characterised by such modularity can use our tool since its benefits come also from the *Workload Tearing* process.

The decisive factor when using our tool was the type of the simulation.

Due to the algorithm of the filtering process and the concept of output forwarding, we limit the application range to digital simulations in order to be able to use the partitioning methods described in Chapter 3 and the filtering methods described in Section 3.2.1. In conclusion, roughly any Digital Circuit Simulation can be handled with the use of our tool.

## 4.3 Results

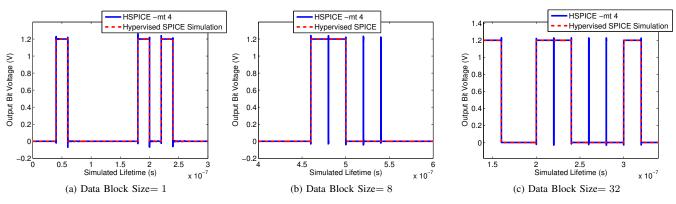

One of the objectives of this process was to evaluate the validity of the approach. Thus we extracted the output signals from our output results and compared them to outputs derived from industry standard tools. The output bits of the multiplier are the  $p_i$  bits shown in Figure 4.1. For each benchmark run, we had two data sets of the bit outputs of the multiplier. One set was the output of our tool and the second set was the output of the reference tool.

The output of our tool was a set of files, each for one output bit. The files themselves are simply two column data files. The first column being the time and the second the voltage values.

For the first benchmarking session the reference tool was **hspice** by *Synopsys*. The outputs were in .tr0 format. In order to parse these files we developed a miner for the specific output format.

For the second benchmarking session the reference tool was **spectre** by *Cadence*. The outputs were in .raw format. For these files a simple awk script was used to extract the useful pieces of information from the data files.

#### CHAPTER 4. BENCHMARKS & RESULTS

Figure 4.1: Inputs and Outputs of a 4x4 multiplier

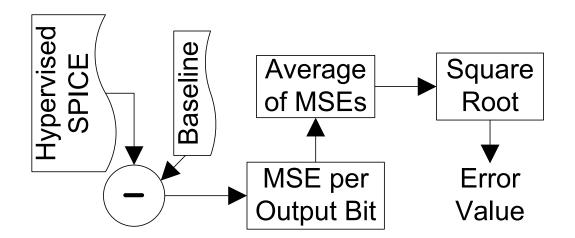

The two digital signal sets (our set and the reference values) have different and variable sample rates. Thus in order to be able to calculate their difference we had to interpolate the signals. Instead of interpolating and performing text handling on the signals we calculated the difference between the two signal sets as shown in Equation 4.1 using a different approach. In order to calculate  $diff_i$  we used an ideal subtractor as shown in Figure 4.2. This technique was used in order to make the data verification more accurate and less strenuous.

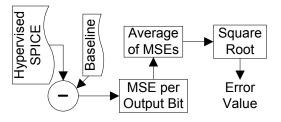

In a later step we extracted the difference signals per output bit. Then we calculated the Root Mean Square Error (RMSE) for each of these difference signals as shown in Equation 4.2. The process is graphically presented in Figure 4.3.

$$diff_i = reference \ bit \ signal_i - hyper \ spice \ bit \ signal_i$$

(4.1)

$$RMSE_i = \sqrt{\sum_{j=0}^{n} \frac{(x_j - mean_i)^2}{n}}$$

(4.2)

The development progress had two major steps. The first round of results has been published in [8].

Grigorios N. Lyras

Page 32 of 78

```

** A signal subtractor for 2 pairs of signals **

1

2

** VCVS instantiations

3

ΕO

output0

0

input0

input1

1

4

0

E1

output1

input2

input3

1

5

6

** Sources **

7

.include input0.in

8

.include input1.in

9

.include input2.in

10

.include input3.in

11

12

** Simulation Definition **

13

.tran 800.00000ns 800.00000ns

14

15

** Output File Definition **

16

.print tran v(output0) v(output1)

17

```

Figure 4.2: Subtractor of two signal pairs

### 4.3.1 First Benchmarking Session

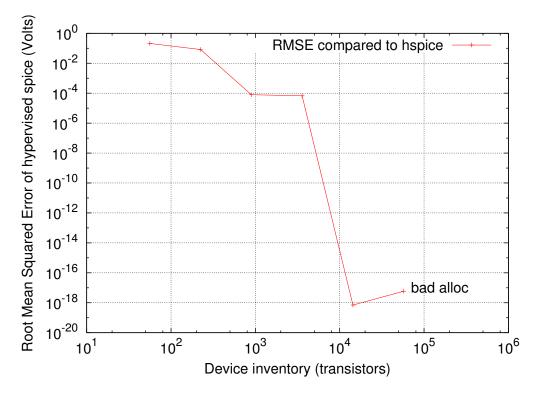

During the first round of results the tool we compared against was hspice by *Synopsys*. We extracted the bit signals directly from the .tr0 output files and compared them bit by bit to the outputs of our tool.

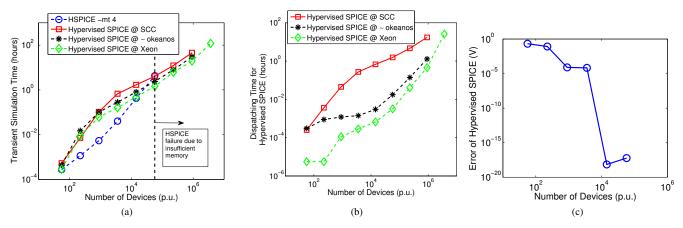

As shown in 4.4 it is apparent that the approach we implemented was not far off the target. In fact, the errors values are as low as  $10^{-18}$ . Due to the RMSE process as described above in 4.2 the error is calculated in Volts. Thus we reach the conclusion that the process remains accurate.

Unfortunately that can only be verified up to data block size of  $2^5$  as the commercial tool failed to produce results further due to bad allocation errors. This fact proves the necessity of our tool since **hspice** cannot produce results for data block sizes greater than a 32 by 32 bit multiplier, given the memory wall of the executing system.

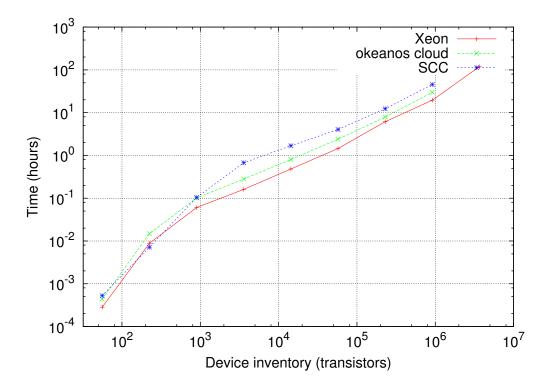

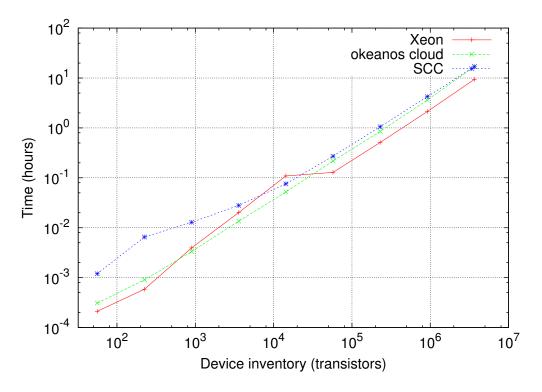

As shown in Figure 4.5 the prototype idea keeps producing results within a viable time frame up to  $2^7$  with almost linear times with regard to the circuit size on all the platforms tested.

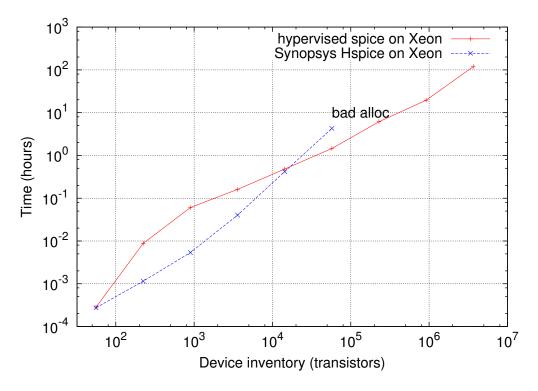

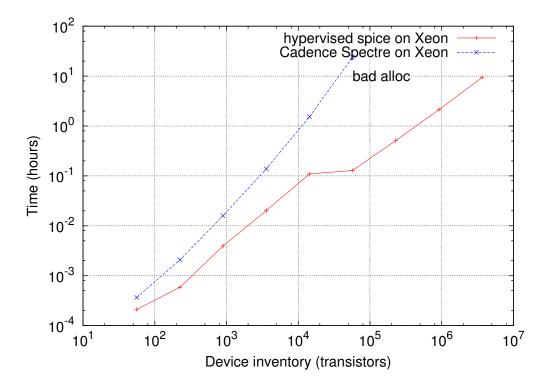

Finally in Figure 4.6 we see a comparison of execution times between the **hspice** and *hypervised spice*. The latter seems to execute at a slower pace for the first smaller circuit sizes, however when the netlist becomes

Figure 4.3: Error calculation processj

substancially large the tool provides faster execution times.

Figure 4.4: RMSE error compared to hspice results

Grigorios N. Lyras

Page 34 of 78

Figure 4.5: Cross platform execution times v1

Figure 4.6: Comparison of times of v1 against hspice

The first set of results led to a series of realisations. One of the first design choices that were made during the development of the *hypervised spice* tool was that all the signal forwarding operations will be conducted over the file system. This way we can overcome the memory wall but the strain on the file system is significant. Thus we can understand that the IO of the application, at the level of produced (and later consumed) PWL text files, appears to be the a bottleneck.

### 4.3.2 Second Benchmarking Session

The hypervised spice tool is bound by the file system. So it becomes necesary that one should minimise the IO in order to increase the performance. During our benchmarks we had a series of file systems, one for each tested platform, that were degrading the performance. In order to overcome that barrier we took two simple but significant measures.

As a first step we incressed the timeslice duration. With the more advanced partitioning technique as described in Chapter 3 we could regulate the partitioning size. Since we no longer needed the input signals to be broken by

a mod counter we could regulate in a finer manner the number of timeslices and consequently their duration.

With a smaller number of timeslices for the same total duration it is apparent that the timeslices for the second benchmarking session were larger. With larger timeslices, the number of accesses to the filesystem were reduced by a factor of aproximately 0.75. This is evident if we keep in mind the number of timeslices for the second round of simulations. During the First Benchmarking Session we used 40 timeslices for a lifetime of 20ns each. During the Second Benchmarking Session we used 10 timeslices, with an average duration of 80ns each. Thus we reduced the number of executed simulations and, as a result, the number of output files by the aforementioned factor. So having only one fourth of the initial load we expected an increase in the performance.

That was not the only action point. During the first set of experiments we observed large signal files that had to be transfered between simulations. When taking a closer look to the matter, one one particular case, the number of data points that were forwarded exceeded the number of 60000 for a simulation duration of merely 20ns. Thus we realised that we needed a method to decrease the signal size, effectively reducing the number of data points that were forwarded between simulations.

From this process the concept that we explored was the idea of signal filtering. Thus we applied the filtering technique described in Section 3.2.1 in order to decrease the number of data points copied from one simulation to the next. This technique had two significant impacts. The first was of course the reduction of the strain on the file system. Smaller data files are faster to read, copy and process in general. The second impact was the duration of each simulation. With less points to parse, **ngspice** was a lot faster to converge.

### 4.3.3 Results

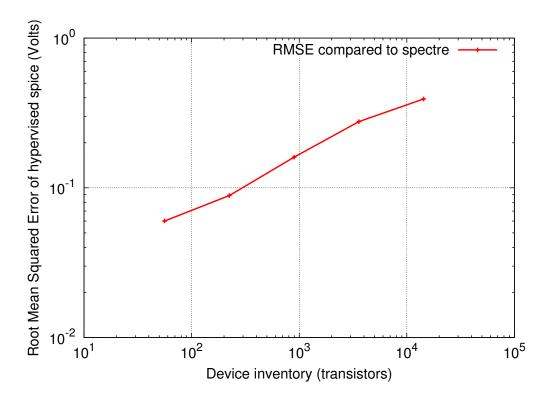

As show in Figure 4.7 the results during the second benchmarking session were degraded regarding the errors. The main factor that these errors can be attributed to is the filtering process. This was an area we expected to present such a descrepancy and requires further development.

Figure 4.7: RMSE error compared to spectre results

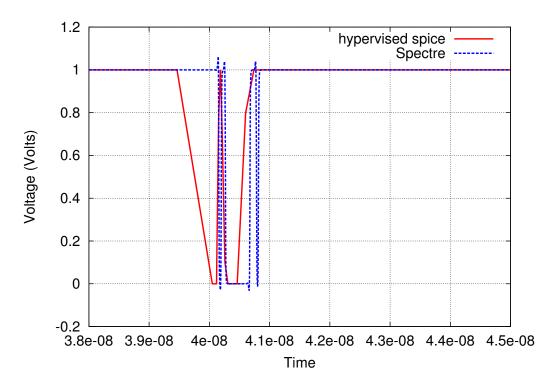

In order to understand why this appears we need to refer back to the filtering process. In the filtering process we search the signal for transitions. When performing digital simulations the transitions are signified by two values. If  $V_1$  is the high voltage level and  $V_0$  is the low voltage level any value below  $V_0 + (V_1 - V_0) \times 0.1$  is considered low and any value above  $V_0 + (V_1 - V_0) \times 0.9$  is considered high. So in the final stage of the filtering process we reset the values in this range to their representatives  $V_0$  and  $V_1$  respectively. This process inserts a minor offset during the executions as shown in Figures 4.8, 4.9. This offset is propagated as the results are forwarded the outputs are filtered again, thus leading to these errors.

Grigorios N. Lyras

Page 38 of 78

Figure 4.8: Multiple transitions error

Figure 4.9: Temporal offset error

On the other hand, we have linear execution times with regard to the circuit size on all execution platforms. This is clearly show in Figure 4.10. This proves that the optimisations we performed were well fiting for this application profile.

Grigorios N. Lyras

Page 40 of 78

Figure 4.10: Cross platform execution times v2

When comparing the tool performance the execution times are significantly smaller when compared to the commercial Spectre. As shown in Figure 4.11 hypervised spice is an order of magnitude faster than Spectre. Moreover we have to note here that Spectre, just as hspice in the First Benchmarking Session, fails to produce results for data block sizes greater than a 32 by 32 bit multiplier.

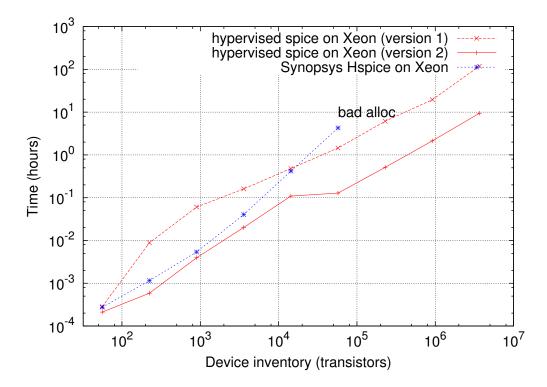

In Figure 4.12 we see a comparison of execution times of all four tools. We can observe that the new implementation is faster by an order of magnitude when compared with either the *Synopsys* or *Cadence* tool. This justifies the steps we took to optimise the performance of the execution, and the bottleneck estimations were valid. However this methods imposed an error factor. This indicates that future work is required to optimise signal filtering in order to reduce these errors.

Finally in Figure 4.13 we see a comparison between the execution times among the two versions. We can observe that the improvement is vast with regard to performance.

Figure 4.11: Comparison of times of v2 against Spectre

Figure 4.12: Comparison of execution times of v1, v2 against hspice and Spectre

Figure 4.13: Comparison of execution times of v1, v2

# Chapter 5

# Conclusions & Future Work

## 5.1 Conclusions

This work has been a multi disciplinary project. It is a merge of ideas from the world of High Performance Computing into the world of Electronic Design Automation.

As part of the technical work, a series of tools and libraries that constitute the framework were designed and implemented.

The backbone of the framework is a configurable **hypervisor** that can handle jobs with dependencies. As a design choice this tool uses a double fork and one execve system call. This allows the return of the resource through the waitpid system call.

The second tool that is used in the framework is the **ngspice wrapper**. This is responsible for all handling input and output signals following a set of strict conventions regarding the naming of the files. Moreover, since it is agnostic regarding the kernel it executes, it also uses the fork and execve system calls.

The microsig library was developed to handle input and output of signals in PWL form and also for performing some simple operations on them. These operations include filtering, addition, interpolation and inversion. Most of the tools are built with the use of this library.

Finally partitioning tools and data mining tools were built with the use of the microsig library

When performing the experiments we had three runtime platforms at hand. An Intel®Xeon®CPU X3470 @ 2.93GHz powered server, the Single-Chip Cloud Computer (SCC) Intel Labs prototype and a virtual machine on GRNET  $\sim$ okeanos infrastructure.

For the experiments we used **ngspice** as the main execution kernel, while we used **hspice** by *Synopsys* and **Spectre** by *Cadence* as reference tools for the first and the second round of experiments respectively. The circuit we used as a benchmark was a multiplier.

During the first experiment cycle we observed great accuracy on the results we obtained from our tool. When we compared the execution times with the execution times of **hspice** we found that our tool was strictly slower for small data block sizes but the performance increased and exceeded **hspice** from a certain point forward. A significant point here is that the commercial tool failed to produce results for any block size greater than a 32 by 32 bit multiplier. On the other hand our tool kept producing results for up to 256 by 256 bit multiplier and a device inventory of 3.6 million transistors.

In order to improve the performance we reduced the partitioning factor and inserted a filtering method in the process. We have to note that the step sizing algorithm we used is the one implemented in **ngspice**. Being far from optimal, it raised the need to filter the signals in order to reduce their size. If the execution kernel we used had a better step sizing algorithm, this step wouldn't be needed.

These courses of action greatly boosted the performance. Compared to the industry standard tools our tool was able to produce results faster by an order of magnitude. The commercial tools kept failing at the same point (32 by 32 bit multiplier). However our tool kept producing results up to 256 by 256 proving that we have overcome the memory barrier imposed by the runtime system. On the other hand this performance boost came with a degradation of the accuracy of the tool.

From the above we can conclude that this approach introduces a viable solution to otherwise unfeasible simulations. Furthermore we can identify a trade-off between accuracy and speed. As it can be understood if we increase the speed of the application we can produce results faster with less accuracy.

## 5.2 Future Work

We approached the field of SPICE simulation for large netlists and extensive workloads and provided a viable solution in order to overcome the memory

limitations of each runtime system. This work can be further extended and improved in various ways.

One step of action would be to improve the **hypervisor**. The hypervisor at the moment uses a simple first come first served scheduling algorithm. If one can prioritise the tasks they can achieve better locality which can improve the performance on certain cases. Furthermore the hypervisor uses a simple fork call to spawn the process control threads. An improvement would be to use the pthread library or an equivalent API which would enable a more fine grained control on the spawns and less strain on the running platform.

Another interesting approach regarding the **hypervisor** would be the concept of local kings. In case of multiple execution nodes one could dispatch, for example, one hypervisor per physical machine. This way you can achieve greater locality and scalability.

Secondly one can improve the **ngspice wrapper**. Sapp as it is it performs all the transactions through the file system. This approach is needed in order to overcome the memory wall. Thus one can improve the file system throughput. Solid State Drives can provide the application with a great performance boost if they are available. Moreover a compression layer on the data as they are written and read from the file system can also reduce the strain on the file system thus greatly improving the performance. A third idea would be to implement the signal forwarding through a Message Passing Interface if we need even greater scalability.

Due to the discrepancy we observed in the second round of experiments we can argue that the filtering method applied is rather crude for such an application. Thus a more advanced filtering method could greatly improve the accuracy of our approach. Alternatively, improvements of the adaptive step sizing algorithm can enhance the performance of intermediate simulations with minimum accuracy degradation.

Another domain where the hypervisor could alleviate significant CPU times is that of time and workload dependent variability simulations. For instance, a very interesting application would be the atomistic models for Bias Temperature Instability (BTI) and Random Telegraph Noise (RTN) [2].

Last but not least, the trade-off between accuracy and speed always remains. The more invasive the filtering method applied the less points the simulations will parse. This way, depending on the application at hand one can fine tune the performance to be suitable to their needs and deadlines.

# Bibliography

- [1] Nascentric announces omegasim(tm) gx the world's first hardwareaccelerated spice simulator. http://www10.edacafe.com/nbc/ articles/view\_article.php?articleid=516299&interstitial\_ displayed=Yes.

- [2] Time and workload dependent circuit simulation. Technical Report EP 2 509 011 A1, 2012.

- [3] M. Duranton, S. Yehia, B. de Sutter, K. de Bosschere, A. Cohen, B. Falsafi, G.N. Gaydadjiev, M.G.H. Katevenis, A. Ramirez, O. Temam, and M. Valero. *The HiPEAC Vision, High Performance* and Embedded Architecture and Compilation. HiPEAC Project, January 2010.

- [4] S.H. Fuller and L.I. Millett. Computing performance: Game over or next level? Computer, 44(1):31 --38, jan. 2011.

- [5] Kanupriya Gulati, John F. Croix, Sunil P. Khatr, and Rahm Shastry. Fast circuit simulation on graphics processing units. In *Proceedings* of the 2009 Asia and South Pacific Design Automation Conference, ASP-DAC '09, pages 403--408, Piscataway, NJ, USA, 2009. IEEE Press.

- [6] Nachiket Kapre. SPICE2 -- A Spatial Parallel Architecture for Accelerating the SPICE Circuit Simulator. PhD thesis, California Institute of Technology -- Pasadena, California, 2010.

- [7] Vangelis Koukis. ~okeanos: Delivering iaas to the greek academic and research community, August 2012. Invited talk at VHPC 2012, Rhodes Island, Greece.

- [8] Grigorios Lyras, Dimitrios Rodopoulos, Antonis Papanikolaou, and Dimitrios Soudris. Hypervised transient spice simulations of large netlists & workloads on multi-processor systems. In *Design Automa*-

tion and Testing in Europe (DATE), 2013 International, march 2013.

- [9] A. Maxim and M. Gheorghe. A novel physical based model of deepsubmicron cmos transistors mismatch for monte carlo spice simulation. In Circuits and Systems, 2001. ISCAS 2001. The 2001 IEEE International Symposium on, volume 5, pages 511 --514 vol. 5, 2001.

- [10] T. McConaghy, K. Breen, and J. Dyck. Variation-Aware Design of Custom Integrated Circuits: A Hands-On Field Guide. Springer, 2013.

- [11] Laurence W. Nagel. SPICE2: A Computer Program to Simulate Semiconductor Circuits. PhD thesis, EECS Department, University of California, Berkeley, 1975.

- [12] Laurence W. Nagel and D.O. Pederson. Spice (simulation program with integrated circuit emphasis). Technical Report UCB/ERL M382, EECS Department, University of California, Berkeley, Apr 1973.

- [13] Daniel Payne. New parallel spice start-up company eda thoughts: From an eda marketing insider. http://www.chipdesignmag.com/ payne/2009/12/24/new-parallel-spice-start-up-company/.

- [14] D. Rodopoulos, S.B. Mahato, V.V. de Almeida Camargo, B. Kaczer, F. Catthoor, S. Cosemans, G. Groeseneken, A. Papanikolaou, and D. Soudris. Time and workload dependent device variability in circuit simulations. In *IC Design Technology (ICICDT), 2011 IEEE International Conference on*, pages 1 --4, may 2011.

- [15] M. Toledano-Luque, B. Kaczer, P.J. Roussel, T. Grasser, G.I. Wirth, J. Franco, C. Vrancken, N. Horiguchi, and G. Groeseneken. Response of a single trap to ac negative bias temperature stress. In *Reliability Physics Symposium (IRPS), 2011 IEEE International*, pages 4A.2.1 --4A.2.8, april 2011.

- [16] Mateo Valero and Nacho Navarro. Multicore: The view from europe. IEEE Micro, 30(5):2--4, 2010.

- [17] N.H.E. Weste and D.M. Harris. CMOS VLSI Design: A Circuits and Systems Perspective [With Access Code]. ADDISON WESLEY Publishing Company Incorporated, 2011.

# Chapter 6

# Appendix

A: DATE 2013 Preprint

# Hypervised Transient SPICE Simulations of Large Netlists & Workloads on Multi-Processor Systems

Grigorios Lyras, Dimitrios Rodopoulos, Antonis Papanikolaou and Dimitrios Soudris

National Technical University of Athens - School of ECE

MICROprocessors and Digital Systems LABoratory

9 Heroon Polytechneiou, Zographou Campus, 157 80 Athens, Greece

Conctact Email: drodo@microlab.ntua.gr

Abstract—The need for detailed simulation of digital circuits has received the attention of both academia and industry since the early stages of design automation. As the number of integrated devices per silicon die increases, the need for faster, device level, circuit simulations becomes more apparent. These simulations are heavy on the system memory, hence limiting the size of the circuit that can be handled by multi-core systems with a unified memory hierarchy. In this work, we present a parallel implementation of a traditional circuit simulation program, based on structural partitioning of the netlist and temporal partitioning of the input signals. This enables scalability of the overall simulation across units of execution. It allows simulation of very large circuits, which cannot be handled even by commercial tools. The proposed simulation framework is validated through simulations of a benchmark circuit with more than a million MOSFET devices and workloads of extended duration. We observe minimal error in comparison to commercial tools and even a  $\times 2.35$  speedup for moderate netlist sizes. Different execution platforms are inspected, thus substantiating the versatility of our implementation.

#### I. INTRODUCTION