Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Ηλεκτρικής Ισχύος

Εργαστήριο Ηλεκτρικών Μηχανών και Ηλεκτρονικών Ισχύος

# Προβλεπτικός Έλεγχος Αντιστροφέων Τριών Επιπέδων για Σύνδεση στο Δίκτυο με LCL Φιλτρο

# Model Predictive Control of Grid Connected Neutral Point Clamped Converters through LCL filters

ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

ΣΤΑΘΑΚΗΣ Π. ΑΡΙΣΤΕΙΔΗΣ

Επιβλέπων: Στέφανος Ν. Μανιάς Καθηγητής Ε.Μ.Π

# Εθνικό Μετσοβείο Πολμτέχνειο

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

ΕΡΓΑΣΤΗΡΙΟ ΗΛΕΚΤΡΙΚΩΝ ΜΗΧΑΝΩΝ ΚΑΙ ΗΛΕΚΤΡΟΝΙΚΩΝ ΙΣΧΥΌΣ  $\label{eq:tomeas} \text{Τομέας Ηλεκτρικής Ισχύος}$

Προβλεπτικός Έλεγχος Αντιστροφέων Τριών Επιπέδων για Σύνδεση στο Δίκτυο με LCL φιλτρο

Model Predictive Control of Grid Connected Neutral Point Clamped Converters through LCL filters

$\Delta$ ιπλωματική Εργασία τος  $\Sigma$ Ταθάκης Π. Αριστείδης

Επιβλέπων: Στέφανος Ν. Μανιάς Καθηγητής Ε.Μ.Π

| Εγκρίθηκε απο την | τριμελή εξεταστική επιτροπή | την $16^{\eta}$ Ιουλίου 2013. |

|-------------------|-----------------------------|-------------------------------|

| Σ.Ν.Μανιάς        | Α.Κλαδάς                    | Σ.Παπαθανασίου                |

Αθήνα, Ιούλιος 2013

A /2 II D 0/

Αριστείδης Π. Σταθάκης Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικος Υπολογιστών

Copyright ⓒ Αριστείδης Π. Σταθάχης 2013. Με επιφύλαξη παντώς δικαιώματος. All rights reserved

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομη της παρούσας εργασίας, εξ ολοκλήρου ή τμηματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπο τη προυπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρών μήνυμα. Ερωτήματα που αφορούν την χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα. Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτο το έγγραφο εκφράζουν το συγγραφέα και δεν πρέπει να ερμηνευθεί οτι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

# ABSTRACT

The objective of this thesis is the development of a grid connected control system of a three level Neutral Point Clamped converter interfacing the grid through LCL filters with switching losses minimization and active damping of the filter resonance. In order to achieve optimum efficiency, an online Model Predictive optimization strategy is considered minimizing switching losses, namely Model Predictive Direct Power Control(MPDPC), and is properly extended to meet active damping of LCL filter requirements. As an outcome of the online optimization process, switching frequency of the converter is variable, thus it is compared in simulation environment with the traditional Direct Power Control(DPC) technique. DPC with and without LCL output filter are thoroughly presented and an analytical way of DPC lookup table design is proposed based on virtual flux quantities. Moreover an effective three-level hysteresis controller design is proposed in order to smooth spikes present in reactive power with conventional DPC. While presenting the MPDPC solution algorithm utilized in this thesis, two new techniques are introduced, aiming at lowering the computational effort required for conventional MPDPC reach a solution. Finally, MPDPC with LCL filters and active damping is evaluated in a broad range of operating points, and proof of concept hardware is implemented. The main conclusions drawn from this study is that high performance converters can be designed utilizing MPC concepts making use of today computational power, while providing a framework for traditional techniques, i.e active damping, to be integrated with Online Optimization Controllers.

**Keywords:** Neutral Point Clamped Converter(NPC), Model Predictive Control(MPC), Direct Power Control(DPC), Model Predictive Direct Power Control(MPDPC), LCL filter, Active Damping, Virtual Flux, Online Predictive Control, Receding Horizon

# ACKNOWLEDGMENTS

This thesis was completed as a collaboration of Electric Machines and Power Electronics laboratory of National Technical University of Athens, and Laboratory of Industrial Electronics of Swiss Federal Institute of Technology in Lausanne in context of LLP/ERASMUS programme 2012.

First I would like to express my gratitude to professor Alfred Rufer for accepting me as an exchange student to the Laboratory of Industrial Electronics, giving me the opportunity to work on such a challenging topic and learn so much from the laboratory environment.

A great thanks is owed to my supervisor Michalis Vasiladiotis, for his guidance and support throughout the whole project and of course everybody in the lab for making my stay there a very friendly and interesting experience.

I would also like to thank my supervisor professor in Greece, Dr Stefanos Manias, for his guidance and support before and after my stay in Lausanne and for giving me the opportunity to participate in the Erasmus programme in first place. My acknowledgements also to Dr A. Kokosis and Dr A.G. Stafylopatis, for helping me out with my Erasmus application dead-ends, without their help this thesis would never have even started.

Finally I feel obliged to express my gratitude to my family, my mother my father and my brother, for their support from the very first moment and of course for their tolerance to my "extended study-plan".

# CONTENTS

| Al | bstra                     | $\operatorname{ct}$                                                 | iii                                                                |

|----|---------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------|

| A  | ckno                      | wledgments                                                          | v                                                                  |

| 1  | Intr<br>1.1<br>1.2<br>1.3 | Background                                                          | 1<br>1<br>2<br>3                                                   |

| Ι  | Lit                       | erature review - State of the art                                   | 5                                                                  |

| 3  | 2.1<br>2.2<br>2.3<br>2.4  | Itilevel Converters         Diode Clamped - NPC Multilevel Inverter | 7<br>7<br>10<br>12<br>14<br>16<br>17<br>17<br>20<br>20<br>22<br>23 |

| 4  | Pre 4.1 4.2               | Introduction                                                        | 25<br>25<br>26<br>26<br>27<br>28                                   |

|    |      | 4.2.4   | Model based Predictive Control                                               | 29         |

|----|------|---------|------------------------------------------------------------------------------|------------|

| 5  | LCI  | filter  | and Damping Techniques                                                       | 33         |

|    | 5.1  | LCL F   | Filter Overview                                                              | 33         |

|    | 5.2  | LCL F   | Filter Design                                                                | 35         |

|    | 5.3  | Passiv  | re Damping                                                                   | 38         |

|    | 5.4  | Active  | Damping                                                                      | 40         |

|    |      | 5.4.1   | Virtual Resistor method                                                      | 40         |

|    |      | 5.4.2   | Lead-Lag compensator method                                                  | 41         |

|    |      | 5.4.3   | Notch Filter method                                                          | 42         |

| II | Aı   | nalysis | s and Comparative Study of DPC and MPDPC                                     | C          |

| te | chni | ques    |                                                                              | 43         |

| 6  | Dire | ect Po  | wer Control                                                                  | 45         |

|    | 6.1  | DPC o   | of 3 level NPC                                                               | 45         |

|    |      | 6.1.1   | Virtual Flux                                                                 | 47         |

|    |      | 6.1.2   | Power Calculation                                                            | 49         |

|    |      | 6.1.3   | Hysteresis Controllers                                                       | 52         |

|    |      | 6.1.4   | Sector decision                                                              | 54         |

|    |      | 6.1.5   | Switching Table                                                              | 55         |

|    |      | 6.1.6   | Midpoint Voltage Balancing                                                   | 61         |

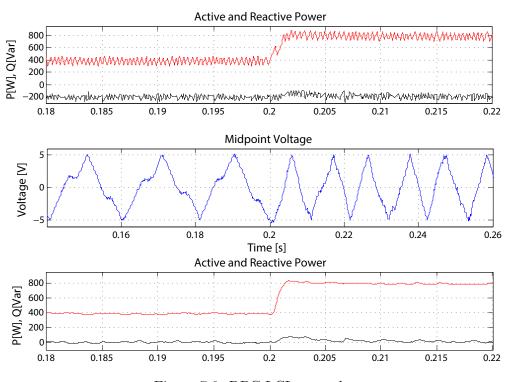

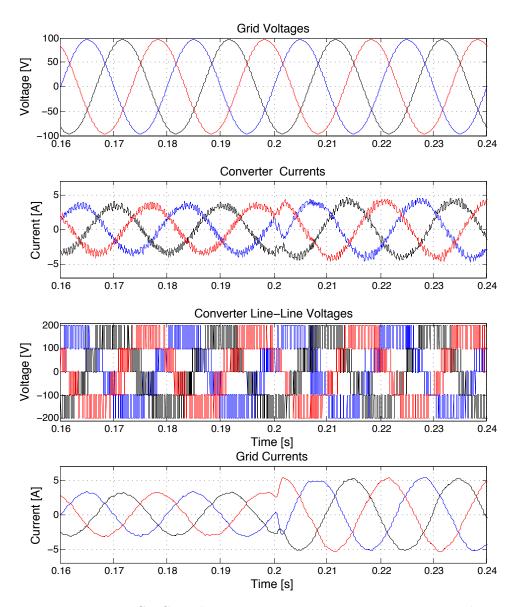

|    | 6.2  | Simula  | ation Results                                                                | 66         |

|    | 6.3  | Exper   | imental Results                                                              | 70         |

| 7  | DP   |         | LCL Output Filter                                                            | <b>7</b> 5 |

|    | 7.1  | DPC o   | of three-level NPC with LCL Output Filter                                    | 75         |

|    |      | 7.1.1   | Virtual Flux and Power estimation                                            | 76         |

|    |      | 7.1.2   | Active damping                                                               | 77         |

|    |      | 7.1.3   | Filter Capacitor Reactive Power Compensation                                 | 80         |

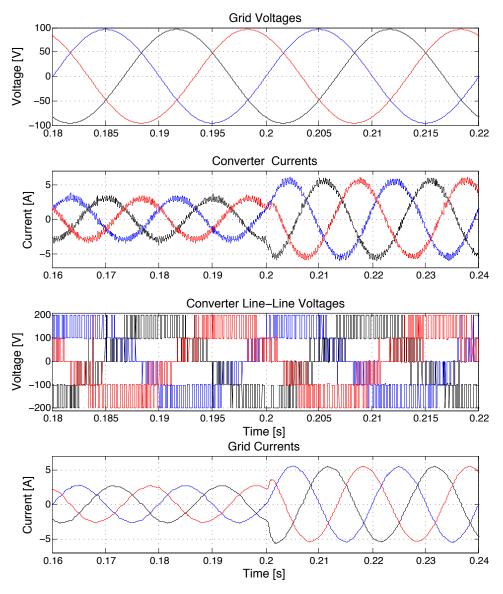

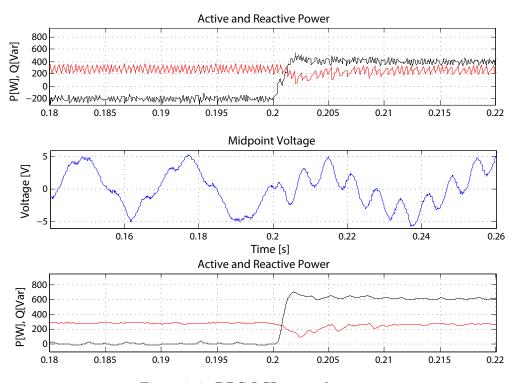

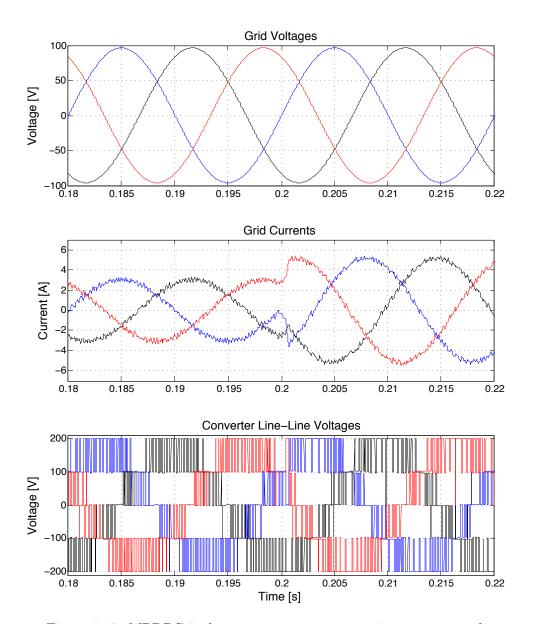

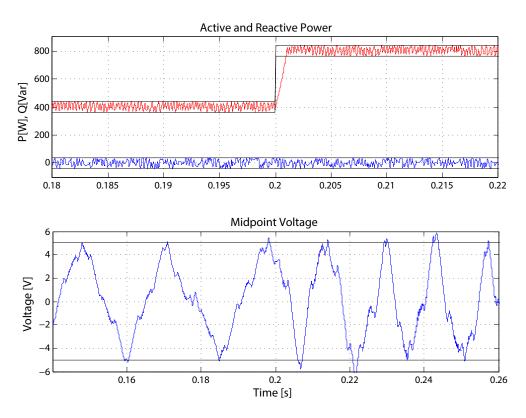

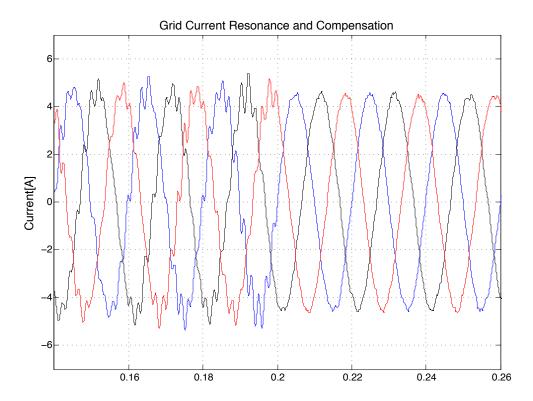

|    | 7.2  | Simula  | ation Results                                                                | 81         |

| 8  |      |         | edictive Direct Power Control                                                | 87         |

|    | 8.1  |         | te time physical modeling                                                    | 88         |

|    | 8.2  |         | em Formulation                                                               | 89         |

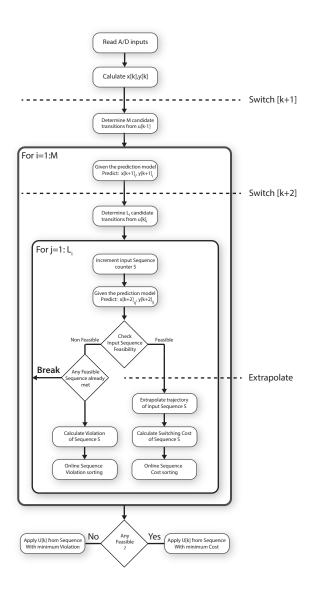

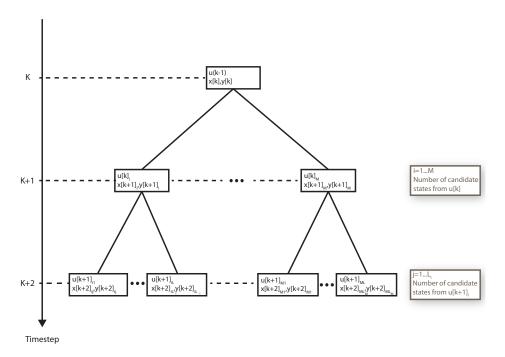

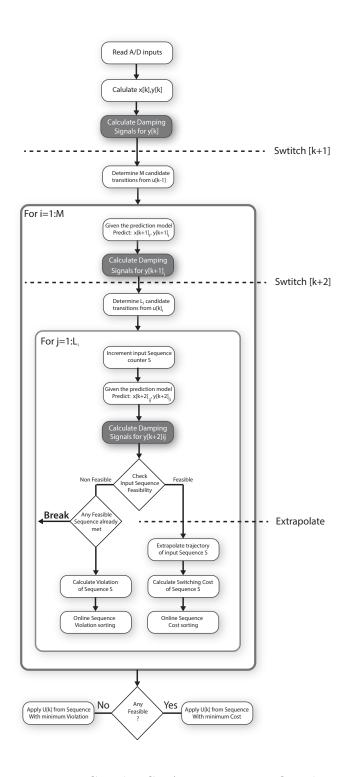

|    | 8.3  |         | on Algorithm                                                                 | 93         |

|    |      | 8.3.1   | Timestep k ,Present State                                                    | 95         |

|    |      | 8.3.2   | $Timestep k+1, Horizon=1 \dots \dots \dots \dots \dots$                      | 95         |

|    |      | 8.3.3   | $\label{timestep k+2, Horizon=2}  \dots \dots \dots \dots \dots \dots \dots$ | 96         |

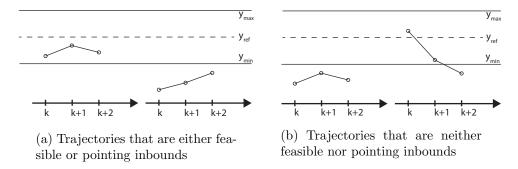

|    |      | 8.3.4   | Sequence Feasibility Sorting                                                 | 96         |

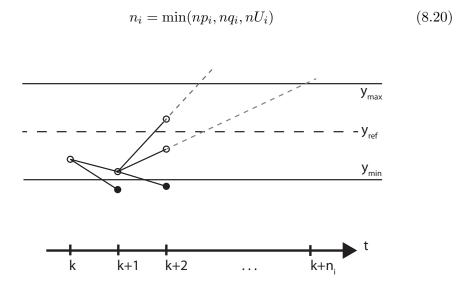

|    |      | 8.3.5   | Extrapolation of Feasible sequences                                          | 97         |

|    |      | 8.3.6   | Cost Calculation                                                             | 98         |

|    |      | 8.3.7   | Handling Infeasibilities                                                     | 99         |

|               |      | 8.3.8    | First Check and Delay Compensation                    | 99  |

|---------------|------|----------|-------------------------------------------------------|-----|

|               |      | 8.3.9    | Branch and bound                                      | 99  |

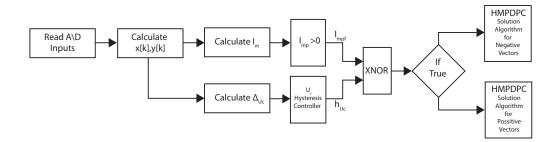

|               | 8.4  |          | ic MPDPC                                              | 100 |

|               |      | 8.4.1    | External Midpoint Balancing                           | 100 |

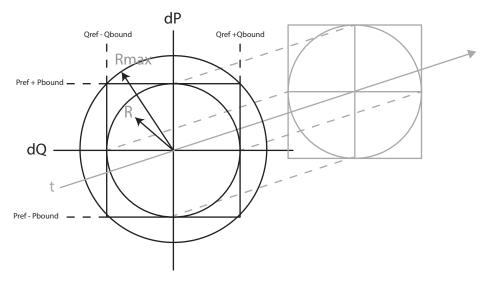

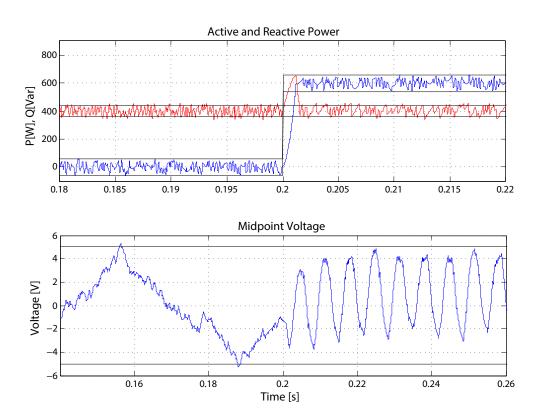

|               |      | 8.4.2    | Active and Reactive Power Coupling - PQ-R             | 101 |

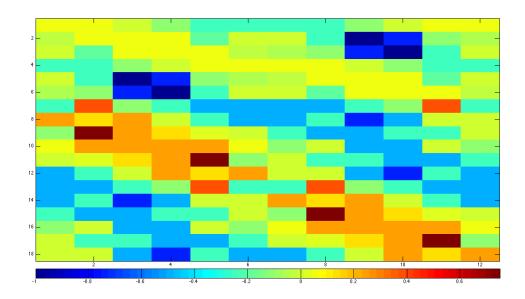

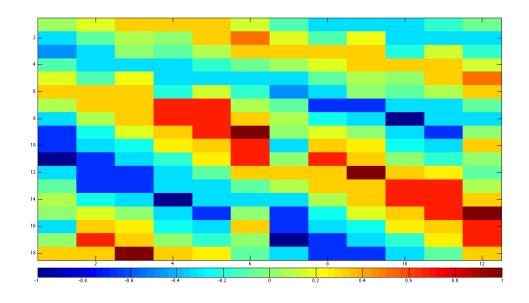

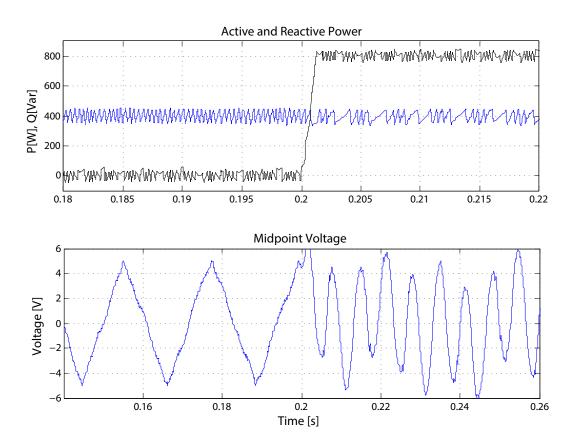

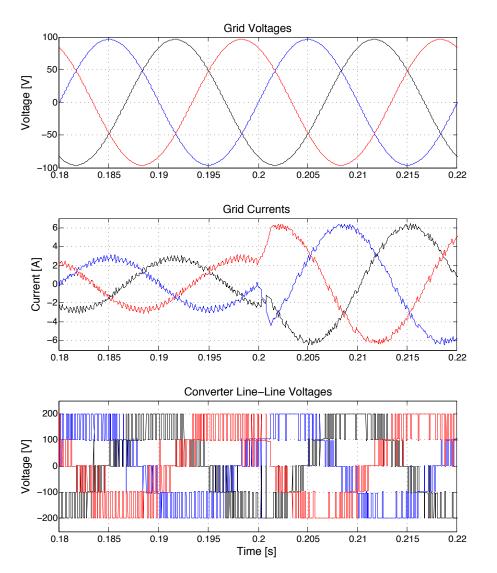

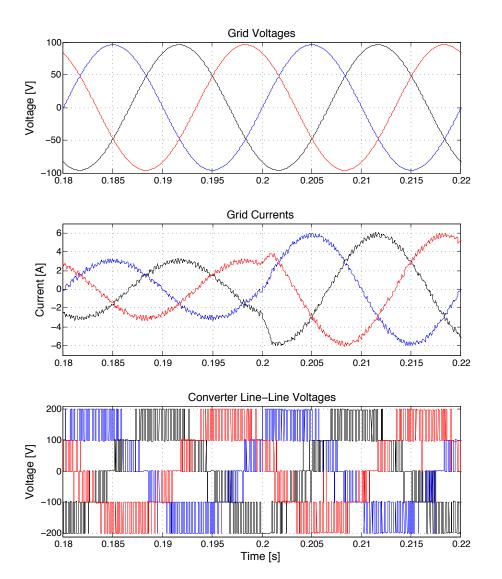

|               | 8.5  | Simulat  | ion Results                                           | 104 |

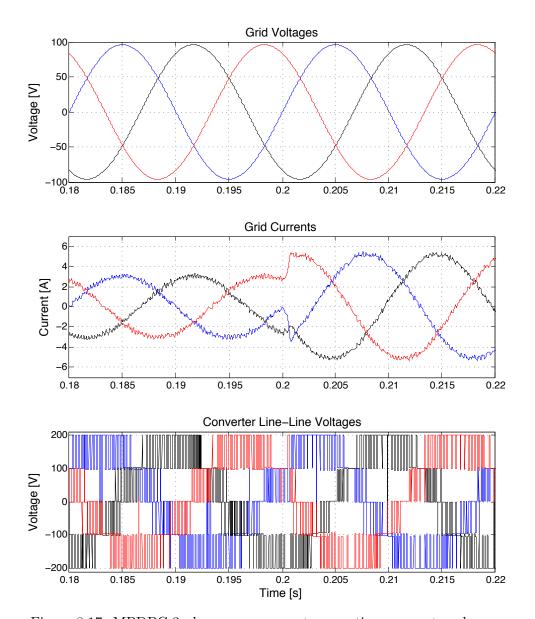

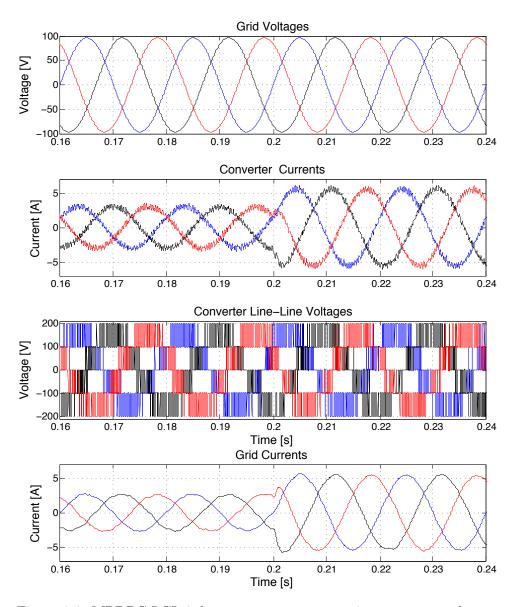

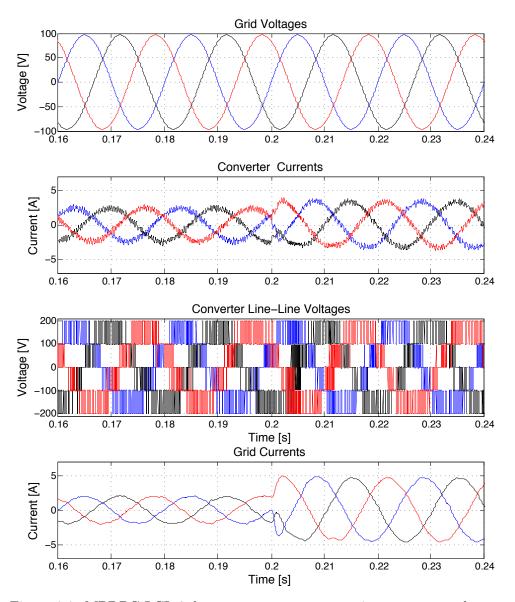

|               |      | 8.5.1    | MPDPC                                                 | 104 |

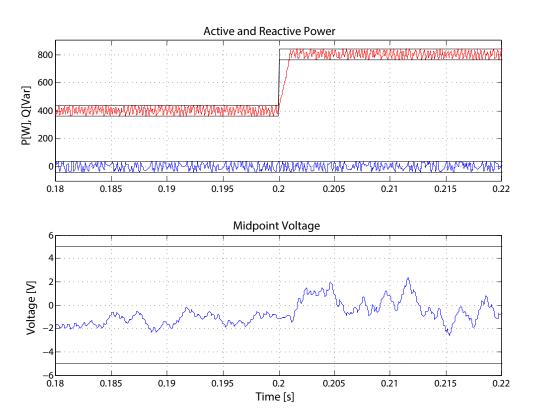

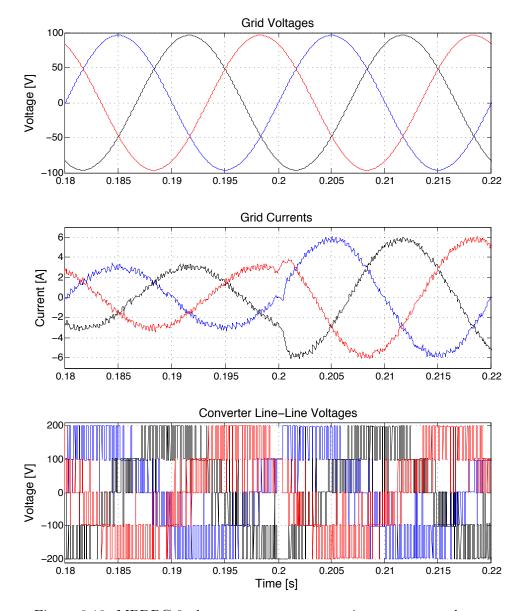

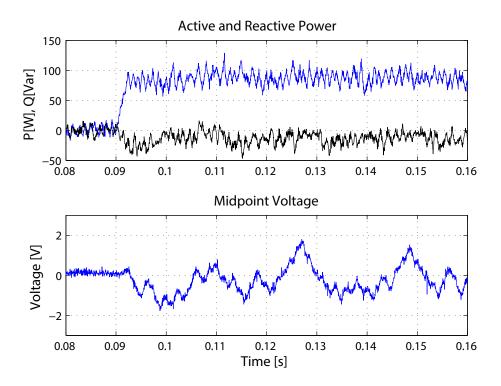

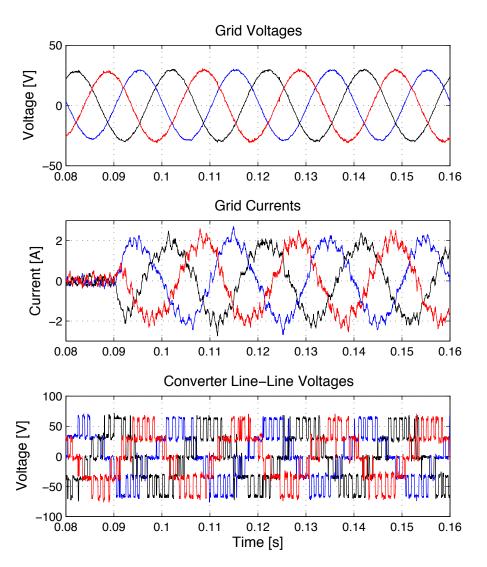

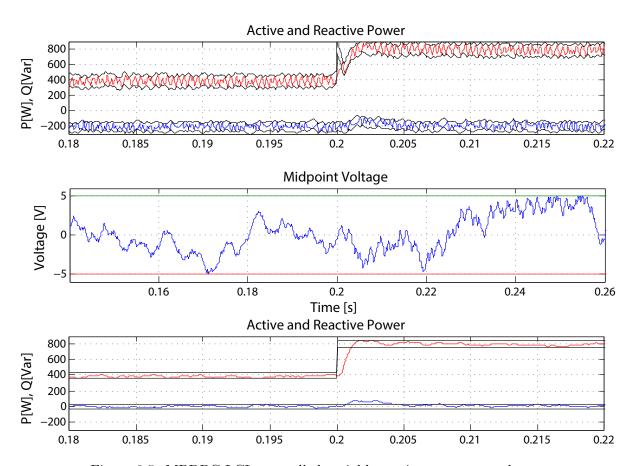

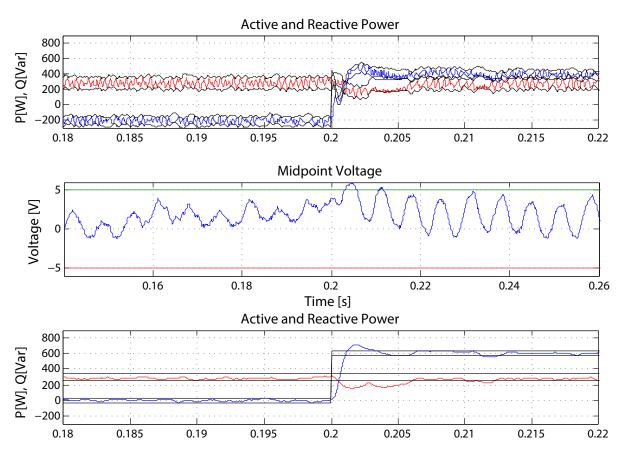

|               |      | 8.5.2    | HMPDPC with external midpoint balance                 | 108 |

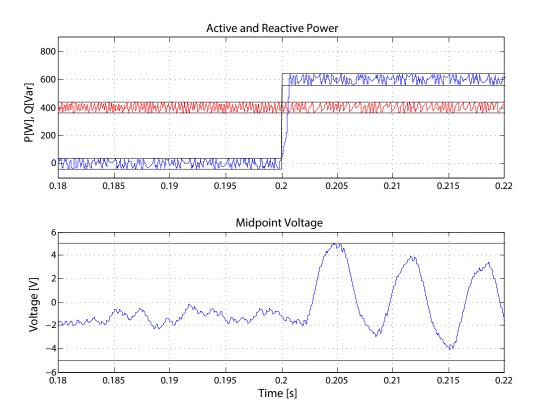

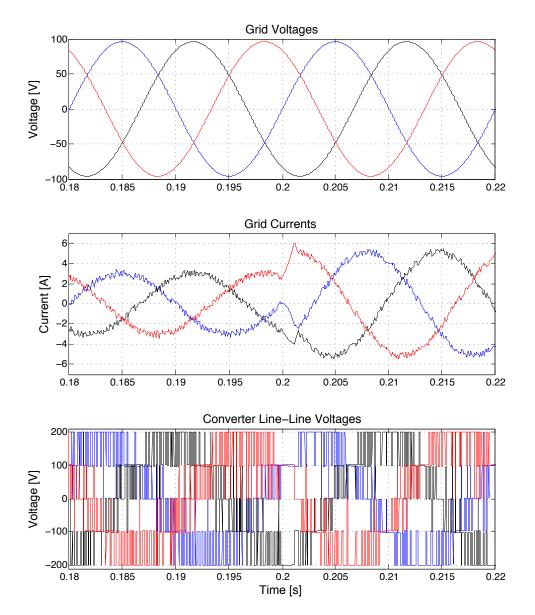

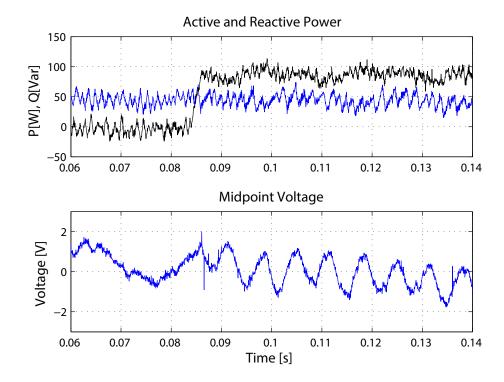

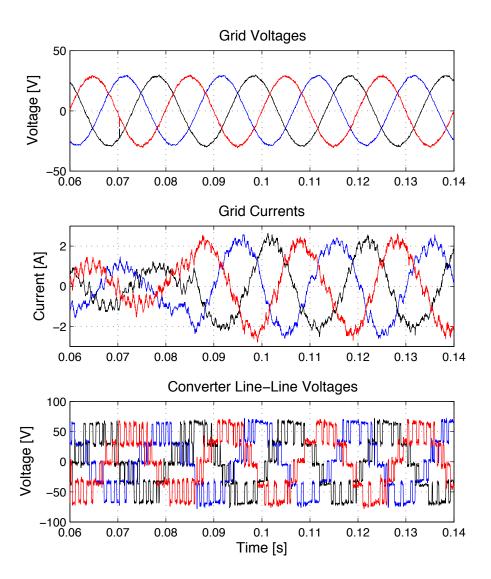

|               |      | 8.5.3    | HMPDPC with PQ coupling                               | 112 |

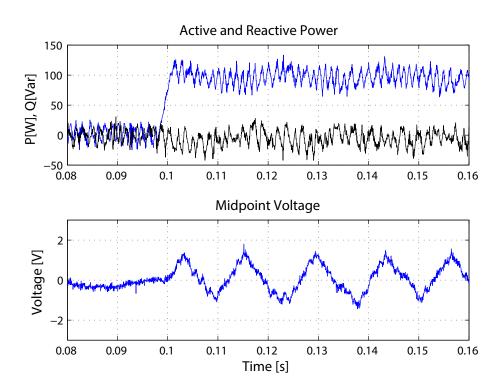

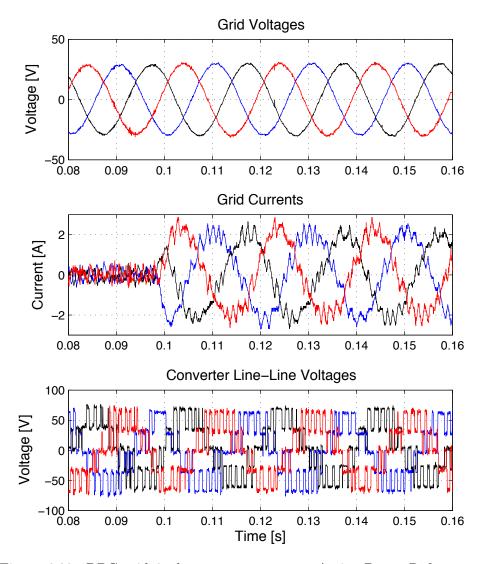

|               | 8.6  | Experin  | nental Results                                        | 116 |

| 9             | MP   | DPC w    | ith LCL filter                                        | 121 |

|               | 9.1  | Physica  | l Modeling                                            | 122 |

|               | 9.2  | Problen  | n Formulation                                         | 123 |

|               | 9.3  | Solution | a Algorithm                                           | 125 |

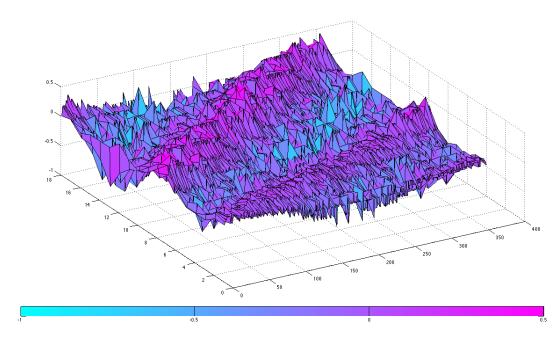

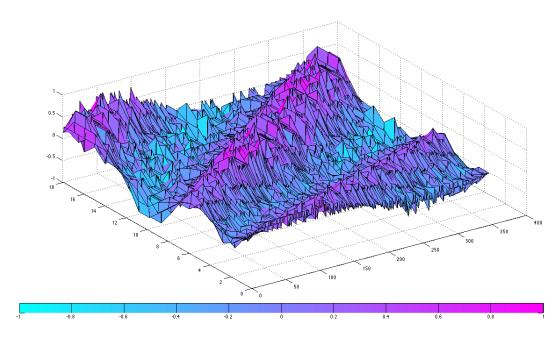

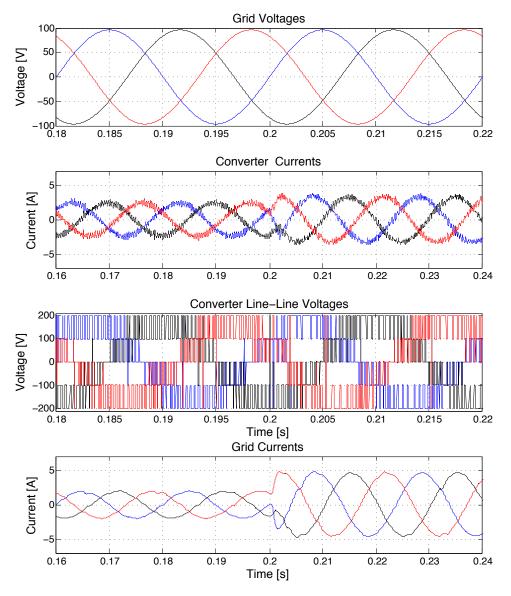

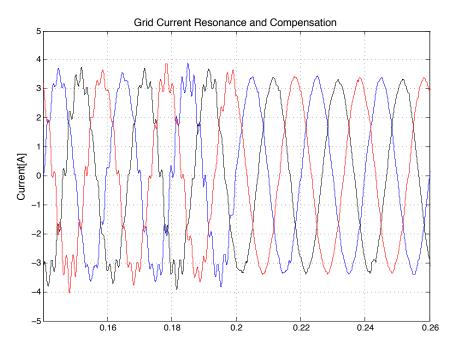

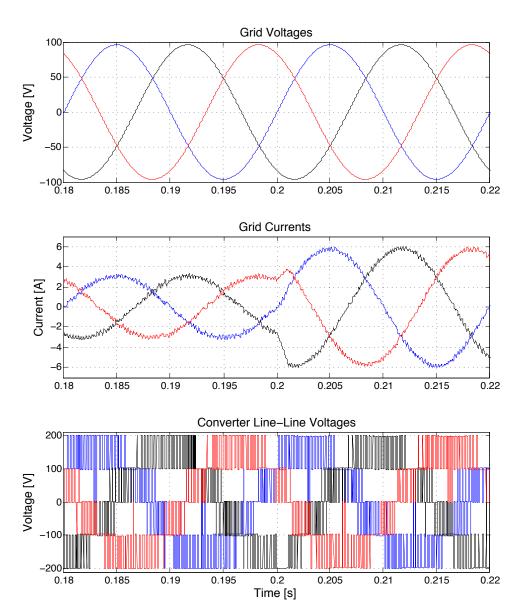

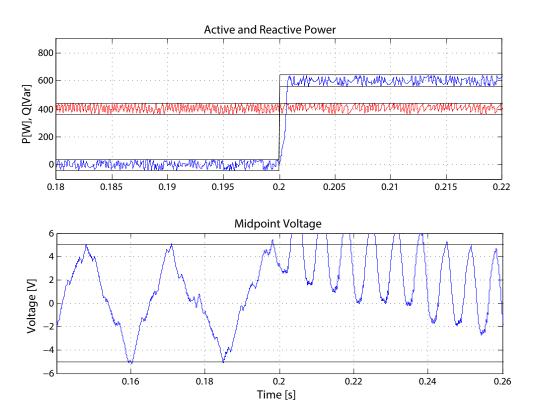

|               | 9.4  |          | ion Results                                           | 129 |

|               |      | 9.4.1    | MPDPC LCL with active damping throughout whole hori-  |     |

|               |      |          | zon                                                   | 129 |

|               |      | 9.4.2    | MPDPC LCL with active damping to present state only . | 135 |

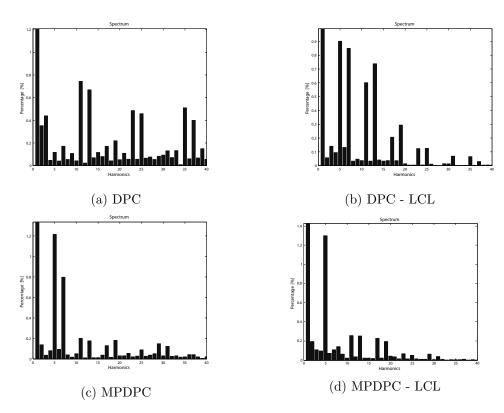

| 10            | Con  | nparativ | ve Study Results                                      | 141 |

| 11            | Con  | clusions | s and Future Work                                     | 145 |

|               | 11.1 | Conclus  | sions                                                 | 145 |

|               | 11.2 | Future   | Work                                                  | 148 |

| III           | Н    | ardwai   | re Setup                                              | 151 |

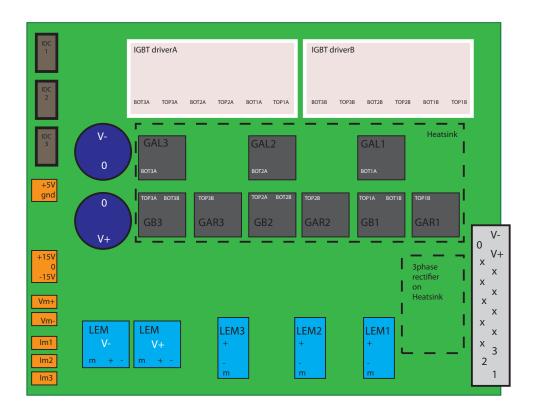

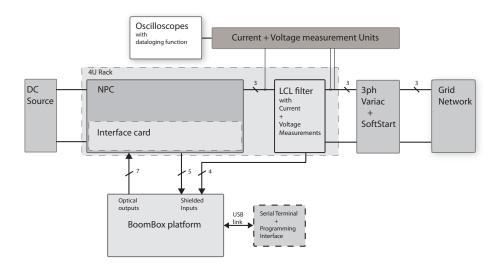

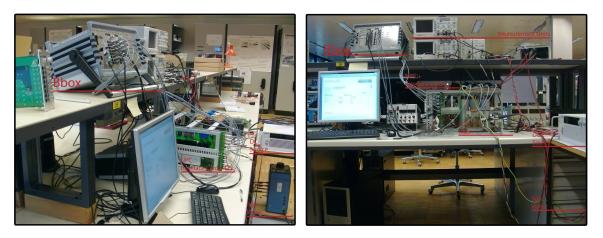

| <b>12</b>     | Exp  | eriment  | tal Setup Description                                 | 153 |

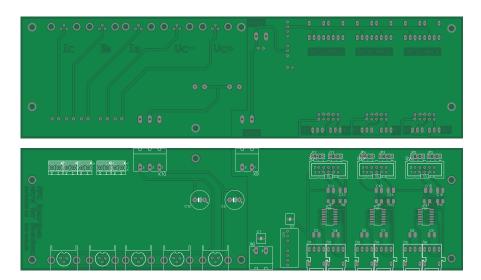

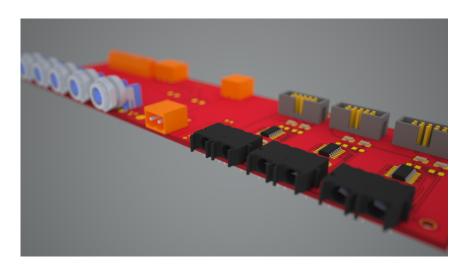

|               | 12.1 | BoomB    | ox platform                                           | 153 |

|               | 12.2 | NPC an   | nd Interface Card                                     | 155 |

|               | 12.3 | Overvie  | ew                                                    | 160 |

| $\mathbf{IV}$ | A    | ppendi   | ix                                                    | 161 |

| $\mathbf{A}$  | Mat  | lab scri | $_{ m ipts}$                                          | 163 |

# INTRODUCTION

# 1.1 Background

Ever since industrial revolution, energy demand is constantly growing, based largely on fossil fuel resources. Electric power is mostly produced by steam powered electric generators through fossil fuel combustion, like coal, natural gas, or petroleum and other non renewable energy sources. Combination of both of these facts and continuous rise of fossil fuels price paralleled to the potential ecological catastrophe that over-exploitation of available resources imply, make massive adoption of renewable energy sources into large scale energy production urgent, towards a sustainable equilibrium.

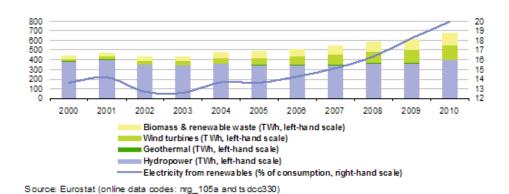

Such a change is happening and can easily be depicted by many statistics illustrating rapid growth of new energy sources, such as figure 1.1, summarizing electricity production from renewable energy sources rise in Europe.

Figure 1.1: Electricity generated from renewable energy resources in Europe for previous decade

Renewable energy sources such as wind, sunlight, tides, waves, biomass, geothermal heat etc., can accommodate for a much larger ratio in electric power generation, if related technological advances are made and constraints, mainly related with intermittent availability and efficient storage, are surpassed. Moreover, with the rise of fossil fuels price, investing on renewable energy electricity production is getting more potent than the past, boosting development of new technologies. Of great importance is the fact that with growth of Distributed Generation Systems, the main picture of centralized electricity production changes, allowing rapid growth of sustainable electricity generation. Moreover for developing countries, renewable energy sources are of great importance, as a way to provide electricity to remote areas and support local economy by natural resources readily available.

All this technological advances needed in the energy domain are closely related to power electronics research area, since modern power converters with efficient operation, and capability of complex implementations, are empowering changes boosting utilization of renewable energy sources. Power converters are the key mechanism allowing different energy sources to connect together and integrate in a larger power distribution network.

# 1.2 Thesis Objectives

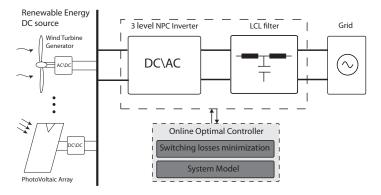

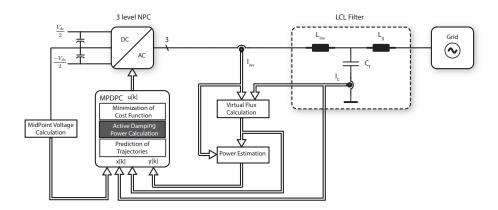

The main objective of this thesis is the study and development of a grid connected high efficiency - high performance system, fig 1.2. In high power-high voltage applications, with rise of applied voltage, switching losses have a greater impact on overall performance and are linearly related to switching frequency. Thus, minimization of switching frequency leads to more efficient power systems by decreasing switching losses of the converter. For this reason a more sophisticated Model Based Predictive Control approach is adopted, targeting switching losses minimization.

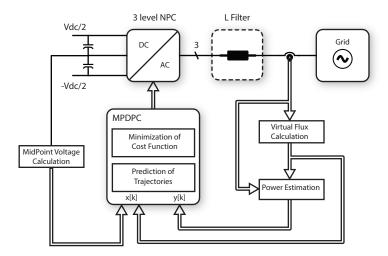

Figure 1.2: Online Predictive Control system block diagram

Neutral Point Clamped converters are utilized in a variety of applications, such as electrical energy transmission systems and active front ends for medium voltage drives. Selection of a multilevel power converter topology in this thesis, such as a three-level NPC, is made due to the proved advantages over conventional two level converters. Multilevel topologies are more efficient, more suitable for high power applications and control algorithms developed for one level can be expanded to higher level topologies due to their modular nature.

One main challenge met in this thesis, is utilization of LCL filter for the grid connection. Since studied control methods produce variable switching frequency, overall system might exhibit strong resonance leading to overall instability. As a result an active damping approach is followed for all studied techniques, and is properly expanded to fit in the Model Predictive Control method used.

# 1.3 Thesis Outline

In order to maintain consistency and provide a continuous reading flow, this thesis is divided in three parts.

In part I the literature review covered during this thesis is presented, in an attempt to situate studied topologies and control techniques in current research and present state of the art, at addressed topics.

- Chapter 2 Multilevel converter topologies are discussed, with a focus on three level Neutral Point Clamped converters, which is the topology utilized in second part. Prevailing topologies are presented and an overview of multilevel converter advantages and tradeoffs are given.

- Chapter 3 Active and Reactive Power control techniques are reviewed, making clear to the reader the necessity of sophisticated control systems for power converters,

- Chapter 4 A basic classification of Predictive control is presented, with a review of main categories, familiarizing the reader with predictive control concepts and setting the background for the predictive control techniques studied in the next part.

- Chapter 5 LCL output filter design for power converters is reviewed, and an approach to passive and active damping techniques through extension of existing control method is given, in an attempt to clarify the benefits and perils of high-order filter utilization.

In part II main study of Direct Power Control and Model Predictive Direct Power Control grid connection techniques follows, with the intention to cover in depth the suggested MPDPC - LCL method as an extension of all previous method analyzed:

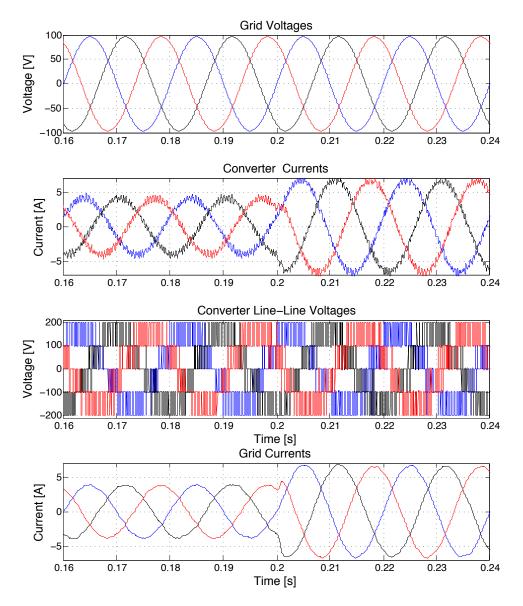

- Chapter 6 the classic Direct Power Control method is reviewed, with an in depth analysis of all its components, with simulation and experimental results are presented and reviewed.

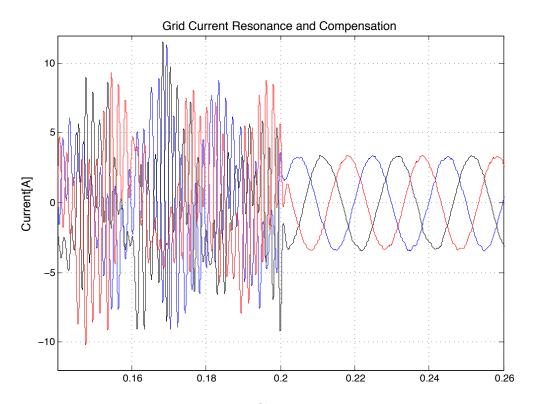

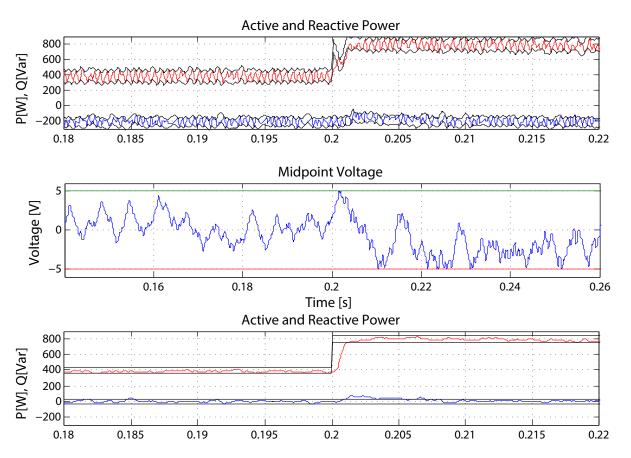

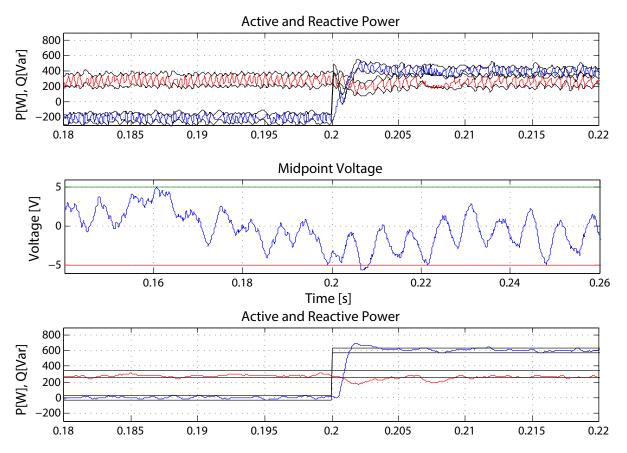

- Chapter 7 DPC method studied in previous chapter is extended in order to incorporate an LCL output filter and actively damp generated resonant harmonics. Simulation results are presented as well.

- Chapter 8 a hybrid technique of Model Predictive Control and Direct Power Control studied in chapter 6 is presented, Model Predictive Direct Power Control. An in depth analysis of the problem formulation, system modeling and solution algorithm implementation is provided to the reader, allowing for a practitioners approach to sophisticated MPC techniques. Chapter finishes with simulation and experimental results.

- Chapter 9 MPDPC method is extended in order to incorporate LCL filter with active damping, as for DPC in chapter 7. A framework for adapting cascaded loops in existing MPC algorithms is suggested, and simulation results are presented.

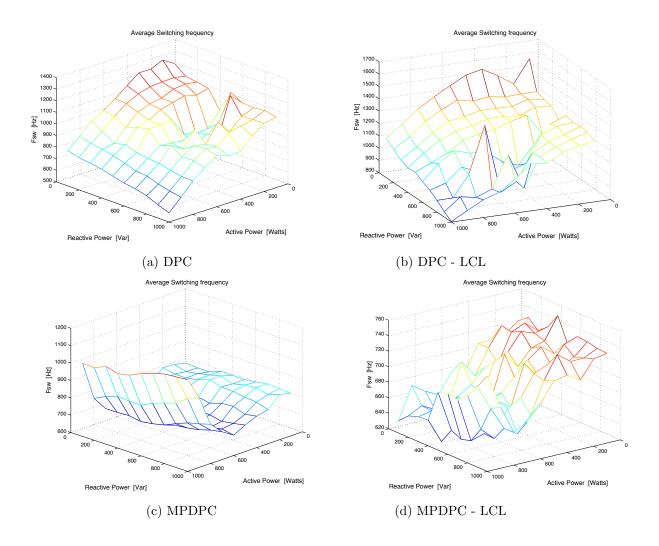

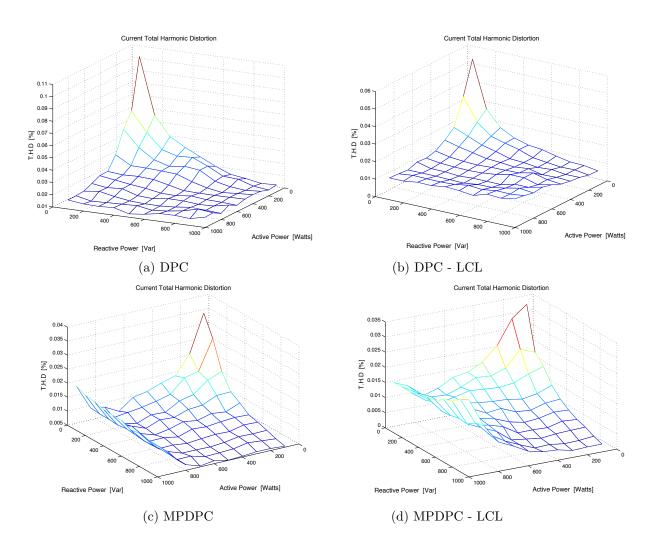

- Chapter 10 An evaluation of four main control techniques studied in previous chapters is made through simulations in steady state for a broad range of operating points. A concluding table and proper graphs illustrate performance acquired of all control techniques evaluated.

- Chapter 11 Conclusions drawn from previous chapters are expressed, following the comparative analysis of four studied control methods and evaluation of the proposed MPDPC-LCL technique.

In part III an overview of the hardware setup utilized in the experimental part of this thesis is given, and a description of hardware developed specifically for this part is presented. The following Appendix contains useful matlab scripts developed during this thesis.

# Part I Literature review - State of the art

# MULTILEVEL CONVERTERS

Use of multilevel converters have increased in high voltage-high power applications due to the main benefits of high voltage capability and low losses that they present. The main concept of all multilevel topologies is to synthesize their output voltage from several voltage levels in a staircase waveform fashion in contrast to conventional two level inverters. In this chapter the three more common topologies of multilevel converters are presented with an emphasis on Neutral Point Clamped converter which is the topology utilized in the following part.

# 2.1 Diode Clamped - NPC Multilevel Inverter

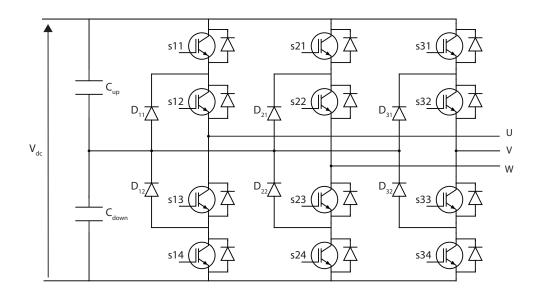

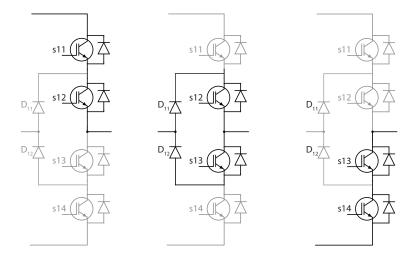

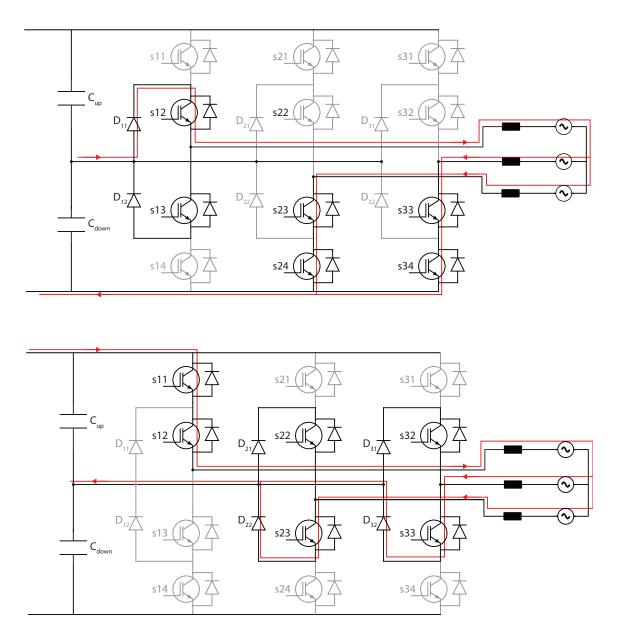

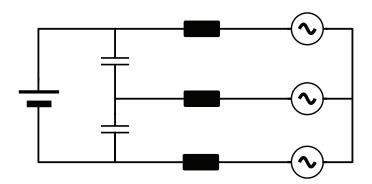

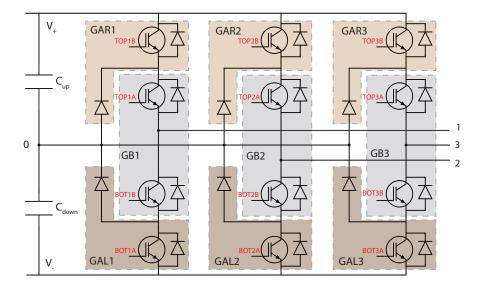

In a three phase m-level NPC as proposed in [1] each leg is composed of 2(m-1) series connected switches and (m-1) dc link capacitors charged with a voltage level equal to  $\frac{Vdc}{m-1}$ . In a 3 level NPC each phase leg is composed of 4 series connected switches ,2 dc link capacitors splitting the dc bus voltage in half and 2 clamping diodes. A basic schematic diagram of a 3 level NPC is shown in figure 2.1.

In general, control strategies employed to a 3 level converter can be extended to higher level topologies due to their modular nature. Obviously the higher the level of one topology the better the output quality is expected to be, with a trade-of in system cost and complexity. One major limitation of higher multilevel implementations is the reverse voltage capability of the clamping diodes, which should be proportional to the level for which they are used to employ clamping action, thus making implementation of high level multilevel converters difficult. In this thesis the case of a 3level NPC converter is considered as the simplest abstraction of multilevel topologies.

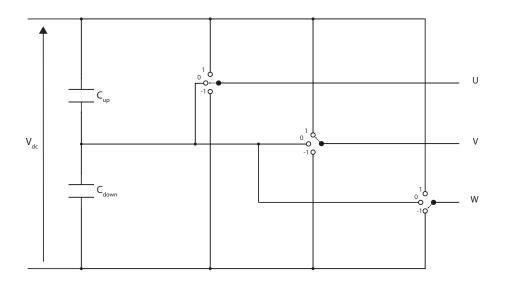

In a 3 level NPC inverter the output voltage of each phase leg can be set to  $\frac{V_{dc}}{2}$ , 0, or  $\frac{-V_{dc}}{2}$ . In that way, each phase leg of the NPC inverter can be seen as a three-state switch able to take values between 1, 0, -1 as illustrated in figure

Figure 2.1: 3 level NPC schematic diagram.

2.2. The input voltage  $V_{dc}$  is equally divided by the dc link capacitors C1,C2 and the output of each phase is referenced to the capacitor connection point, the midpoint, thus balancing the capacitor voltages is critical for proper operation.

Figure 2.2: 3 level NPC phase leg as three-state switch

Given the schematic diagram of figure 2.1, in order to generate a voltage output of  $\frac{Vdc}{2}$  on phase U, switches S11 and S12 are closed while S13 and S14

remain open. In this case the clamping diode D12 balances the voltage sharing between S13 and S14 with S13 blocking the voltage across C1 and S14 the voltage across C2. To generate a voltage output of  $\frac{-Vdc}{2}$  on phase U, switches S13 and S14 are closed while S11 and S12 remain open. In this case the clamping diode D11 balances the voltage sharing between S11 and S12 with S11 blocking the voltage across C1 and S12 the voltage across C2. to generate a voltage output of 0Volt on phase U, switches S12 and S13 are closed while S11 and S14 remain open. In this case diode D11 clamps switch S11 to block the voltage across C1 ans D12 clamps switch s14 to block the voltage across C2. The same switching action exists for the rest of the phases and they can be summarized in table 2.1. The three possible switching states as already described are illustrated in figure 2.3

| Voltage<br>level                               | S      | State       | $\mathbf{s}$ |       |              |  |

|------------------------------------------------|--------|-------------|--------------|-------|--------------|--|

| level                                          | S1     | S2          | S3           | S4    | Sr           |  |

| $ \frac{\frac{Vdc}{2}}{0} $ $ \frac{-Vdc}{2} $ | 1<br>0 | 1<br>1<br>0 | 0 1 1        | 0 0 1 | 1<br>0<br>-1 |  |

| 2                                              |        | 5           | -            | 1     | 1            |  |

Table 2.1: 3 level NPC switching states

Figure 2.3: NPC converter possible switching actions

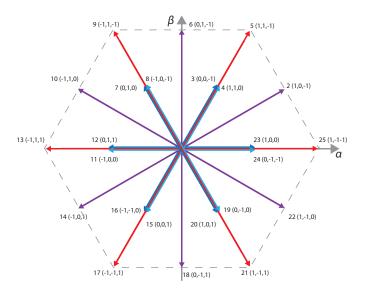

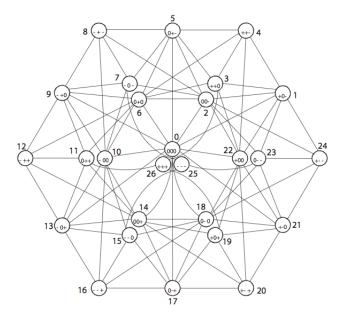

#### 2.1.1 NPC switching vectors $\alpha\beta$ plane analysis

Considering previous switching state analysis for the 3 level NPC, it is very useful for further analysis to consider the representation of all possible output voltage vectors of the converter, related to switches state, transformed from the three phase system,  $V_{inv_{abc}} = [V_{inva}, V_{invb}, V_{invc}]^{\mathsf{T}}$  to  $\alpha\beta0$  static reference plane  $Vinv_{\alpha\beta} = [V_{inv\alpha}, V_{inv\beta}]^{\mathsf{T}}$  using the Clarke-Parke transformation 2.1

$$V_{inv\alpha\beta} = \frac{2}{3} \cdot P \cdot V_{invabc} \tag{2.1}$$

where P is the transformation matrix:

$$P = \begin{bmatrix} 1 & \frac{-1}{2} & \frac{-1}{2} \\ 0 & \frac{\sqrt{3}}{2} & -\frac{\sqrt{3}}{2} \\ \frac{1}{2} & \frac{1}{2} & \frac{1}{2} \end{bmatrix}$$

(2.2)

All possible voltage outputs in phase and magnitude are depicted in figure 2.4. A hexagon is formed containing 27 voltage vectors with sets of,in terms of magnitude, 6 large vectors(5,9,13,17,21,25),6 medium vectors(2,6,10,14,18,22), 12 small(3,4,7,8,11,12,15,16,19,20,23,24) vectors and 3 zero vectors(0,1,26). Zero Vectors are not considered as normal operating switching positions and are mainly used to halt the converter or for other operational functions.

Figure 2.4: 3 level NPC voltage vectors in  $\alpha\beta$  plane.

Of great importance is the fact that small vectors come in pairs. These are redundant states meaning that when employed, same output voltage is achieved and this the key mechanism for midpoint capacitor voltage balancing in the NPC as it will be explained in the direct power control description.

Since in terms of voltage output capacity the NPC inverter bears only 18 states, the voltage vector numbering can be reduced to 18, with three different switching states for the zero state, and two for each small voltage vector. The new voltage vector indexing is addressed in table 2.2. This new voltage vector indexing is a simple way to minimize computation effort to calculations that only magnitude of outpout voltage is of interest.

| $U_n$ | $S_R$   | $S_S$   | $S_T$   | _ | $U_n$    | $S_R$          | $S_S$   | $S_T$   |     | $U_n$    | $S_R$ | $S_S$    | $S_T$ |

|-------|---------|---------|---------|---|----------|----------------|---------|---------|-----|----------|-------|----------|-------|

| $U_1$ | 1<br>0  | 0<br>-1 | 0<br>-1 | - | $U_8$    | 1              | 0       | -1      |     | $U_7$    | 1     | -1       | -1    |

| $U_2$ | 0<br>1  | 0<br>1  | -1<br>0 | - | $U_{10}$ | 0              | 1       | -1      |     | $U_9$    | 1     | 1        | -1    |

| $U_3$ | 0<br>-1 | 1 0     | 0<br>-1 | - | $U_{12}$ | -1             | 1       | 0       | · • | $U_{11}$ | -1    | 1        | -1    |

| $U_4$ | -1<br>0 | 0<br>1  | 0<br>1  | _ | $U_{14}$ | -1             | 0       | 1       |     | $U_{13}$ | -1    | 1        | 1     |

| $U_5$ | 0<br>-1 | 0<br>-1 | 1 0     | _ | $U_{16}$ | 0              | -1      | 1       |     | $U_{15}$ | -1    | -1       | 1     |

| $U_6$ | 0<br>1  | -1<br>0 | 0<br>1  | - | $U_{18}$ | 1              | -1      | 0       |     | $U_{17}$ | 1     | -1       | 1     |

| Small |         |         |         |   |          | $\mathbf{Med}$ | ium     |         |     |          | Lar   | ${f ge}$ |       |

|       |         |         |         |   | $U_n$    | $S_R$          | $S_S$   | $S_T$   | _   |          |       |          |       |

|       |         |         |         |   | T.7      | 0              | 0       | 0       |     |          |       |          |       |

|       |         |         |         |   | $U_0$    | 1<br>-1        | 1<br>-1 | 1<br>-1 | -   |          |       |          |       |

|       |         |         |         |   |          | Ze             | ro      |         |     |          |       |          |       |

Table 2.2: Zero, Small, Medium and Large Converter Output Voltage Vectors Indexing

# 2.2 Capacitor Clamped - Flying Capacitor Multilevel Inverter

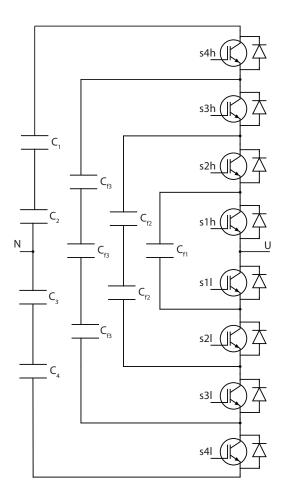

Flying Capacitor multivel inverters [2] are a similar topology to the NPC converter previously presented by the fact that instead of utilizing diodes to provide clamping action, capacitors are used to maintain voltage levels to the desired values. For the same reason, capacitor voltage levels increase quadratically as the number of levels implemented grows.

Figure 2.5: phase leg of a 5 level Flying Capacitor Inverter

For a m-level Flying Capacitor inverter phaseleg, m-1 cells are connected in series, where each cell represents a pair of switches separated by one flying capacitor, resulting to 2(m-1) semiconductor switches and m-2 flying capacitors chargef at m different voltage levels. By relevant switching action, capacitors are serially connected to the phase output, forming a staircase waveform of m

# 2.2. CAPACITOR CLAMPED - FLYING CAPACITOR MULTILEVEL INVERTER

levels. One limitation similar to NPC topology is that at each cell only one of the switches can be closed or else different voltage level capacitors are paralleled resulting in a short circuit.

In figure 2.5 a 5-level flying capacitor multilevel converter phaseleg is illustrated and in table 2.3 switching action of the converter relevant to voltage level output are summarized. h and l indexes denote high and low switches of each cell pair and number of capacitors at each cell denotes their voltage rating ratio.

| Voltage          | Switching States |        |        |        |        |        |        |        |

|------------------|------------------|--------|--------|--------|--------|--------|--------|--------|

| level            | $S4_h$           | $S3_h$ | $S2_h$ | $S1_h$ | $S4_l$ | $S3_l$ | $S2_l$ | $S1_l$ |

| $\frac{Vdc}{2}$  | 1                | 1      | 1      | 1      | 0      | 0      | 0      | 0      |

|                  | 1                | 1      | 1      | 0      | 1      | 0      | 0      | 0      |

| Vdc              | 0                | 1      | 1      | 1      | 0      | 0      | 0      | 1      |

| $\frac{Vdc}{4}$  | 1                | 0      | 1      | 1      | 0      | 0      | 1      | 0      |

|                  | 1                | 1      | 0      | 1      | 0      | 1      | 0      | 0      |

|                  | 1                | 1      | 0      | 0      | 1      | 1      | 0      | 0      |

|                  | 0                | 0      | 1      | 1      | 0      | 0      | 1      | 1      |

| 0                | 1                | 0      | 1      | 0      | 1      | 0      | 1      | 0      |

| 0                | 1                | 0      | 0      | 1      | 0      | 1      | 1      | 0      |

|                  | 0                | 1      | 0      | 1      | 0      | 1      | 0      | 1      |

|                  | 0                | 1      | 1      | 0      | 1      | 0      | 0      | 1      |

|                  | 1                | 0      | 0      | 0      | 1      | 1      | 1      | 0      |

| -Vdc             | 0                | 0      | 0      | 1      | 0      | 1      | 1      | 1      |

| $\frac{-Vdc}{4}$ | 0                | 0      | 1      | 0      | 1      | 0      | 1      | 1      |

|                  | 0                | 1      | 0      | 0      | 1      | 1      | 0      | 1      |

| $\frac{-Vdc}{2}$ | 0                | 0      | 0      | 0      | 1      | 1      | 1      | 1      |

Table 2.3: 5 level Flying Capacitor switching states

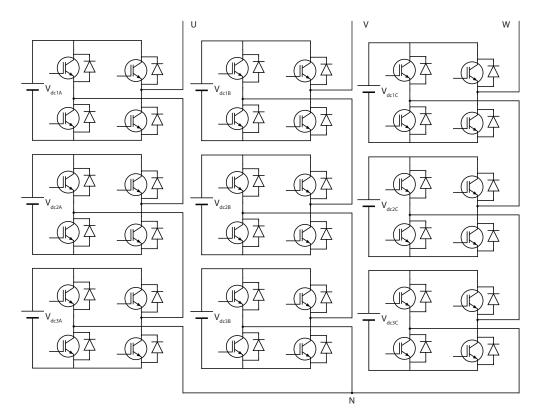

# 2.3 Cascaded H-bridge Multicell Inverter

This topology is a different approach in considering other multilevel topologies previously described. A number of full bridge two level inverter is cascaded using separate isolated dc sources, in a modular setup, in order to synthesize the multilevel output [3]. The number of levels m is proportional to the number of dc sources, thus H-bridges, utilized n as: m = 2n + 1. In figure 2.6 a 7-level three phase converter is illustrated, by properly connecting three H-bridge converters at each phase.

Figure 2.6: 7-level Cascaded H-bridge Multilevel Inverter

Features of this topology are the reduced number of semiconductor components required compared to other topologies already presented, and the fact that no clamping elements exist, either diodes or capacitors. These benefits, in combination with the modular nature of the topology, makes ideal for higher level multilevel converters realization and allows easy expansion of existing converters to higher level output. Especially in applications where multiple dc voltage sources exist, such as photovoltaic applications, battery operated systems, and fuel cells, integration of such a modular architecture is very intuitive and beneficial.

On the other hand, if multiple isolated dc sources are not available, realization of such a topology tends to be hard to implement, thus avoided. For this reason several other modular multilevel converter topologies operating from common dc source have been implemented, such as Reversing Voltage Mutilevel Inverter (RVMI) and Modular Multilevel Inverter (M2I).

# 2.4 Overview

Multilevel Converters present many advantages over conventional two level power converters, most important among them are:

- **High quality waveforms** as their voltage output is synthesized from several voltage levels. Lower voltage semiconductor switches also allow adoption of more efficient semiconductor technologies.

- Low switching losses due to the fact that switching action is shared among a larger number of semiconductor switches, making them ideal for a low switching frequency implementation. Utilization of semiconductors at lower voltage levels allow for even lower switching losses

- **High voltage capability** as seen from the previous analysis a well balanced system can operate at double the voltage ratings of the semiconductors and capacitors used.

- Low EMI interference due to lower  $\frac{dV}{dt}$  stress of the semiconductor switches. Also due to the non constant switching frequency applied throughout this thesis, harmonics generated are less concentrated around specific frequencies, thus produce less noise in specific harmonics leading to reduction of EMI and audible noise, in a similar way to the spread spectrum EMI reduction techniques .

- Common-mode Voltage present in multilevel inverters is minimal and can be totally eliminated by proper control techniques in contrast to two level converters. This is a useful aspect in electrical drives industry as common mode voltage produces stress on the machine bearings and may cause over-voltage stress to the winding insulation, affecting its lifetime.

- **Input Current** that a multilevel converter draws is of reduced harmonic distortion, making their design more easy to adopt to power quality standards.

On the other hand, multilevel converters have design trade-offs, such as high number of semiconductor and clamping devices, and more complex control techniques since with rise of switching elements, the number of possible switching actions of the converter is augmented as well.

Since for a high power-high voltage system which is the case of most grid connected systems, a 3 level NPC converter will be evaluated in the following part, as the simplest abstraction of multilevel converters.

# PQ CONTROL

# 3.1 Introduction

In order to effectively utilize the growing number of alternative energy resources, electric power generated is paralleled to the main power distribution network so as to be made remotely available to an extended consumers network, in contrast to isolated power systems where there is no provision for energy storage. This Distributed Generation scheme, becomes attractive due to the sustainable and pollution free properties that exploitation of renewable energy sources presents. Main challenge of DG systems is the proper arrangement and operation of this network oriented scheme, and can be achieved by use of modern power converters capable of:

#### Grid side:

- Synchronization to mains grid frequency

- Control of mains Voltage

- Control of Active Power flow to the grid

- Control and Compensation of Reactive Power to and from the grid .

- Guarantee current and voltage waveform quality complying to standards

# Energy source side:

- Efficient utilization of energy source, i.e solar MPPT applications

- DC voltage supervision at the converter input

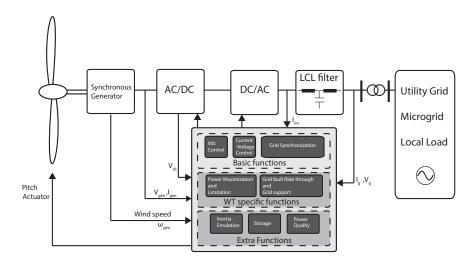

A typical system of a grid connected wind turbine system is illustrated in figure 3.1, illustrating the nested functions that the controller of the power converter perform from basic to supervisory functions. This thesis concentrates on

the grid connection part, thus the case of dc/ac Power control techniques are reviewed in this chapter.

Figure 3.1: overview of a typical System of grid connected wind turbine system

Grid connected control systems have to provide power in an accepted quality, and many control techniques exist. A preliminary classification is whether there exists a communication link between central grid and remote DG system. Main Control techniques of DG systems can be summarized as:

With communication link:

- Active and Reactive power control PQ control

- Distributed Control

- One cycle control

Without communication link:

• Droop control

**Droop Control** is one of the most popular techniques used in literature [4] [5] and is commonly known as Voltage - frequency droop control. Main concept is that power delivered to the grid mimics characteristics of synchronous generators used in centralized power plants. This characteristics depend on synchronous generator rotor inertia which limit frequency variation and natural coupling between frequency and power delivered to the grid. Since active and reactive power of a grid connected inverter can be defined by:

$$P = \frac{3V_{inv}V_g}{X}\sin\delta$$

$$Q = \frac{3V_g}{X}(V_{inv}\cos\delta - V_g)$$

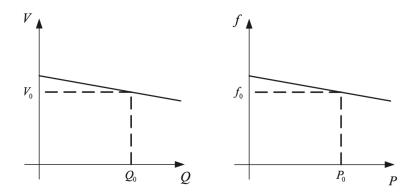

Inverter Active and Reactive power demand is described by droop coefficients m,n of a specific power converter, wich can be illustrated in figure 3.2

$$\omega = \omega_0 - m \cdot P$$

$$V = V_0 - n \cdot Q$$

Figure 3.2: Droop control V-f charactheristics

This method accomplishes acceptable performance only if existing grid voltage is free of distortion and balanced. Moreover it presents drawbacks such as slow transient response, trade off between Voltage output regulation, and frequency and phase deviation that in many applications make this method impractical.

**Distributed control** as introduced in [6] sets power references of the inverter through a communication network. In this network smart metering of the interconnected loads transceive information with power generation units in order to properly coordinate power generation at every DG system. This method is highly depended in a complex by nature bidirectional communication system.

One cycle control This technique as presented in [7] takes advantage of the pulsed and nonlinear nature of switching converters and achieves instantaneous control of the average value of the chopped voltage or current, in contrast to power converter characteristics linearization of simple droop control. This method is favored for its simple control implementation, but restricts its use to specific control strategies. In parallel operation this control method of the DG system might lead to circulating current between phases.

Active and Reactive Power Control in contrast to voltage - frequency control or other current control techniques, sets directly the active and reactive power reference to the power converter. Usually Active power is set by a PI control loop from the dc Voltage input at the inverter so as the grid absorb as much active power as possible, while Reactive power compensation is possible by adjusting the reference value. This method can be classified in three categories depending on the control method employed to regulate Active and Reactive power of the inverter:

- Direct Power Control DPC

- Virtual Flux based control

- Current Control techniques

A brief overview of main control techniques of PQ control will be presented in the following section.

# 3.2 PQ control methods of grid connected converter

Active and Reactive power control is based on instantaneous power theory as presented in [8], and power calculations in rotating and stationary frame can be summarized by:

$$p = \frac{3}{2}(e_{gd}i_{gd} + e_{gq}i_{gq})$$

$$q = \frac{3}{2}(e_{gq}i_{gq} - e_{gd}i_{gd})$$

$$p = \frac{3}{2}\omega(e_{g\alpha}I_{g\beta} - e_{g\beta}I_{g\alpha})$$

$$q = \frac{3}{2}\omega(e_{g\alpha}I_{g\alpha} + e_{g\beta}I_{g\beta})$$

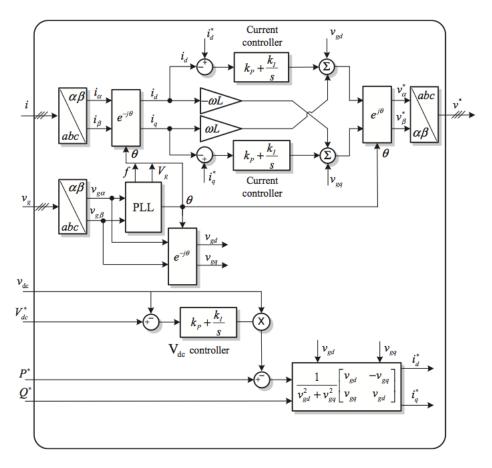

# 3.2.1 Current control techniques - synchronous frame VOC

An easy way to achieve active and reactive power control to a power converter is to incorporate power references to an existing current control scheme. Synchronous frame VOC is a simple to implement control scheme, using a current controller implemented in dq rotating frame and a power calculating stage acting as feedback. Current component references can be calculated by:

$$\begin{bmatrix} i_d^* \\ i_q^* \end{bmatrix} = \frac{1}{V_{gd}^2 + V_{gq}^2} \begin{bmatrix} V_{gd} & -V_{gq} \\ V_{gq} & V_{gd} \end{bmatrix} \begin{bmatrix} P^* \\ Q^* \end{bmatrix}$$

(3.1)

An overall block diagram of the implemented control is illustrated in figure 3.3

Figure 3.3: PQ open loop Voltage Oriented Control based on the synchronous dq frame [9]

Many variations of this technique exist, replacing synchronous frame calculation with static reference coordinate transformations, using PI closed loop controller to adjust the duty cycle of the converter. This technique utilizes a modulator and yields a steady switching frequency output waveform.

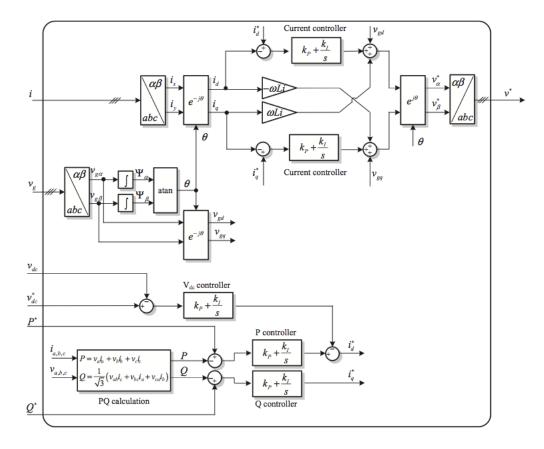

# 3.2.2 Virtual flux based Control

As an alternative to the aforementioned VOC, another scheme utilizing virtual flux concept has been developed. Originally Virtual Flux concept has been proposed for Direct Power Control implementations but can be incorporated to VOC techniques. Due to the resemblance of grid connection to the equivalent schematic of an AC machine, a virtual quantity is considered, that of virtual flux and can be derived by equations:

Figure 3.4: Virtual Flux based Voltage Oriented block diagram [9]

$$\psi_{g\alpha} = \int V_{g\alpha} dt$$

$$\psi_{g\beta} = \int V_{g\beta} dt$$

$$\sin(\theta) = \frac{\psi_{g\beta}}{\sqrt{\psi_{g\alpha}^2 + \psi_{g\beta}^2}}$$

$$\cos(\theta) = \frac{\psi_{g\alpha}}{\sqrt{\psi_{g\alpha}^2 + \psi_{g\beta}^2}}$$

Virtual flux quantities are thus estimated by current feedback of the system and knowledge of the converter output voltage, and can be used for Power Estimation and to replace PLLs for grid synchronization. A more analytical study of Virtual Flux quantity will be presented in the next part of this thesis in the section of Direct Power Control, as it is a very important aspect of all studied Control techniques.

Block diagram of the VOC using the virtual flux concept is illustrated in figure 3.4 and incorporates closed loop PI current controllers. This technique yields also a steady switching frequency since a modulator is used at the output of the control.

#### 3.2.3 Direct Power Control

Direct Power Control presented in [10] originates from Direct Torque Control developed for AC machines drives. Utilizing the Virtual Flux concept, power delivered to the grid is estimated and compared to reference values. Depending on power errors, a switching action is selected based on a pre calculated Look-up table. In this essence, DPC is a predictive control technique of Active and Reactive power, where prediction stage is calculated offline and reflected in the utilized Look-up table. Since no modulator is used, this technique results in variable switching frequency. Benefits of DPC are simple control algorithm and fast response, while there is a trade of in need for a high sampling frequency of the overall system. Many variations of the proposed technique have been developed, some of which incorporate a modulator in order to achieve constant switching frequency.

This technique will be more analytically presented in the respective chapter of DPC control of 3 level NPC inverter. Since this technique yields a variable switching frequency, it is selected as a benchmark to evaluate results of the proposed predictive technique.

Figure 3.5: Direct Power Control block diagram [9]

#### PREDICTIVE CONTROL

#### 4.1 Introduction

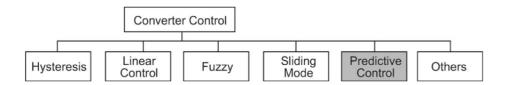

With the increased use of power converters and demand of more complex control schemes, many converter control techniques have been developed. A general classification of the control techniques described in literature is illustrated in figure 4.1. From conventional linear PWM techniques and hysteresis controllers, control methods are evolving to more advanced schemes like fuzzy logic and predictive controllers, utilizing processing power and speed of modern hardware.

Figure 4.1: Classification of converter control methods [11]

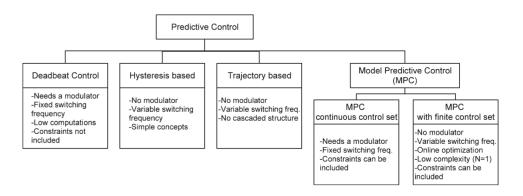

Predictive control has lately being adopted in power converters control concepts, and already represents a wide range of various techniques developed. Following presentation and analysis of predictive control in power electronics in [11],[12] a principal classification of existing techniques is presented in figure 4.2. Main concept of all predictive control techniques is that decision of the controller is not based on past state of the controlled system but on predicted behavior of the state variables and proper selection of the controlled variables after an optimization stage either offline, meaning precalculated, or online. Despite the hard to implement nature of predictive techniques, main concept is very simple and intuitive to the control designer and has proved adequate for power converters control. One of the biggest advantage over other techniques

is that in predictive control, a MIMO (multiple input multiple output) system can be controlled by a single control loop in contrast to other techniques where cascaded control schemes must be implemented.

Moreover, especially for the case of MPC (Model Predictive Control) nonlinearities of the controlled system can easily be implemented in the model used, and additional restrictions of the system can easily be incorporated in the control algorithm and optimization strategy. A brief presentation is following for every predictive technique concepts focusing on Model Predictive Control.

Figure 4.2: Clasification of predictive control method used in power electronics [11]

# 4.2 Overview of Predictive Control Techniques

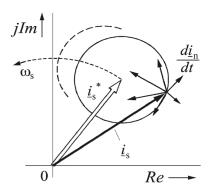

#### 4.2.1 Hysteresis based Predictive Control

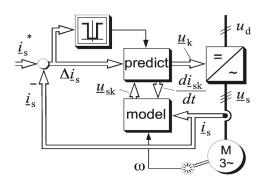

Hysteresis Based predictive control strategies main concept, is to maintain controlled values of the system between certain bounds, while an optimality criterion is achieved by prediction of system states. Block diagram of hysteresis-based predictive current control is shown in figure 4.3b. Given allowed error boundaries as set by control designer, future switching actions are determined by predictive current control. In figure 4.3b the circular bounded region denotes the allowed area of the controlled variables in dq space, as set by the reference values. When the current reaches the boundaries, switching action of the converter is determined by prediction and optimization stages.

In the prediction stage, trajectory of all possible switching vectors are calculated based on machine model equations and time to reach the boundary line is penalized respectively. In the optimization stage, most promising trajectory based on optimality criterion is selected and applied in next time instant. If

- (a) Predictive current control, boundary circle, and space vector

- (b) Hysteresis-based predictive control

Figure 4.3: Hysteresis based control system description [11]

minimization of switching frequency, thus switching losses is the targeted objective of the control, which is common for high power converters, trajectory that is predicted to keep current vector inside bounded area for the longest time interval is selected and applied.

Maximum allowed switching frequency is bounded by the computation time of the algorithm which determines the optimal switching state vector. Many variations of basic hysteresis predictive control, targeting current distortion, emitted EMI, Torque ripple etc. or by altering the bounded area definition.

#### 4.2.2 Trajectory based Predictive Control

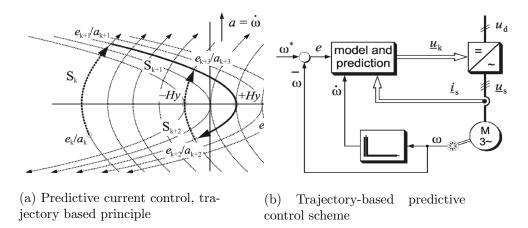

**Trajectory Based** control concept, is to drive the controlled variables of the system, onto precalculated trajectories. Many implementations based on this idea have been presented, like Direct Self Control, Direct mean Torque control and many others like Sliding Mode control and Direct Torque Control, which are a hybrid form of trajectory and hysteresis based predictive control.

Unlike cascaded control, predictive control algorithms offer the possibility to directly control multiple system values. DSPC, shown in figure 4.4a, utilizes no external control loop for speed control, and the switching states applied in the inverter are calculated in a way where speed is directly controlled in a time-optimal manner.

Similar to the methods of [13] and [10], the switching states of the inverter are classified as torque increasing, slowly torque decreasing, or rapidly torque decreasing. For small time intervals, the inertia of the system and the derivatives of machine and load torques are assumed as constant values. The behavior of the system leads to a set of parabolas in the speed error versus acceleration area as shown in figure 4.4b.

Figure 4.4: Trajectory based control system description [11]

The example of DSPC, illustrates the difference of predictive controllers to linear control systems, that instead of linearizing non linear parts of the controlled system so as to be controllable by PI controllers, precalculated optimal solutions are applied depending on knowledge of the system parameters and state variables. Avoidance of cascaded loops leads to more robust control, capable to drive more complex systems in an optimal way.

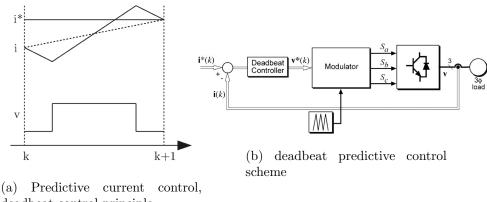

#### 4.2.3 Deadbeat Control

Deadbeat Control can be considered as a different form of predictive controller. Basic principle of this method, is that at every time instant, based on error between reference and measured values of controlled variable, switching state to be applied is selected so as to ideally eliminate the error in next time step, or at least approach the reference value as fast as possible. This kind of predictive controller is used when very fast dynamic response is needed, but has many limitations as unmodeled delays and other errors in the model often deteriorate system performance and may even give rise to instability and non linearities of the controlled system are difficult to incorporate to the control.

In Figure 4.5b a deadbeat current control system is illustrated. This topology is of great resemblance to classic PID control, but instead of the modulator been controlled by the linear controller, it is activated by a deadbeat controller. Main logic of a current deadbeat controller is illustrated in figure 4.5a. At every time instant k, error between measured value and reference value is considered and respective output voltage is selected so as the measured current reaches the reference value in the next time instant k+1.

In real implementations of deadbeat control many issues have to be compensated, with main attention to delays introduced by computation time and

deadbeat control principle

Figure 4.5: Deadbeat control system description [11]

modulation. Also another pitfall of deadbeat control is sensitivity to system parameter variation which might lead to instability. Many variations of simple deadbeat implementation exist and many solutions for deadbeat control drawbacks have been proposed.

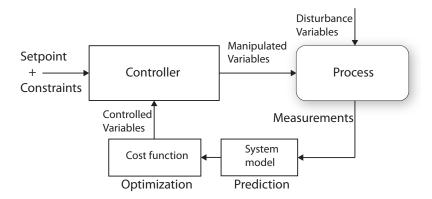

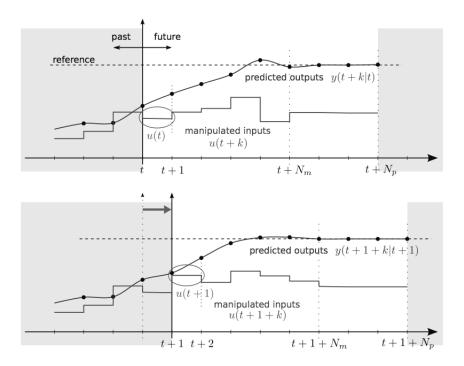

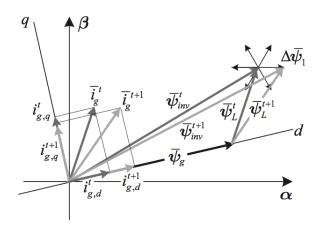

#### 4.2.4 Model based Predictive Control

Model Predictive Control is the most advanced predictive control technique capable to drive multivariable systems with hard constraints on their output. MPC is also referred as receding horizon control, as the main concept is to mimic an infinite prediction horizon solution by continuously sliding the prediction horizon [14]. Main parts of MPC control are illustrated in figure 4.6. Main difference between finite set and continuous set Model Based MPC is that optimization is done in the relevant space, continuous or discrete. For the case of power converters, the continuous optimization output is passed to a modulator and then translated to a switching state with an optimum duty cycle while the FS-MPC optimization stage outputs directly the optimum switching state for the next time interval. As a consequence CS-MPC yields a constant switching frequency while FS-MPC results to variable switching frequency.

System Model is the most important part of Model Predictive Control. More often model of the plant is derived as the state space model describing the controlled system. In other cases more advanced statistical models might be utilized, i.e ARMAX, but then expression of the system should be given in a transfer function form rather than a state space model representation. An MPC setup is expected to be as successful as the model describing the main plant is. In a finite set MPC is usually described as:

Figure 4.6: MPC generalized block diagram

$$x[k+1] = Ax[k] + Bu[k]$$

$$y[k] = Cx[k] + Du[k]$$

Or in a more general expression, the model is used so as to predict future state by present state and input variables,:

$$x[k+1] = f(x[k], u[k])$$

,  $k \in 1, 2, 3, ...$

To complete the system description the set of constraints imposing on state and input variables must be described. Especially in the case of power electronics where the discrete nature of switching actions denotes absolute constraints in the input variables, constraints description is a key mechanism in the optimization process. In the case of Constrained Model based Predictive Control, a set of constraints for the output variables should be devised as well.

$$u(k) \in \mathcal{U} \subseteq \mathcal{R}^p$$

In continuous set MPC the input variable will reflect a value that belongs in a continuous set, i.e  $\mathcal{U} = [0,1]^p$  where u denotes the pwm duty cycle. In FS-MPC the input will reflect a value that belongs to a discrete set, i.e one of the finite possible switching actions of the power converter. State constraints depend on physical limitations of the described system.

$$x(k) \in \mathcal{X} \subseteq \mathcal{R}^n$$

Cost Function is the heart of the optimization stage that takes place inside the MPC controller. Based on the optimality criterion set by the control

designer, an solution of the MPC algorithm is considered optimal when it minimizes a certain cost function. This function may take several forms and complexity, but the general can be described as present and predicted state and input variable dependent:

$$\mathcal{J} = V(x(k), u(k)) = F(x(k+N)) + \sum_{l=k}^{k+N-1} L(x(l), u(l), u(l-1))$$

Where N is the length of the prediction horizon, and F, L weighting functions which serve to penalize predicted system behavior. Once the optimum solution for the given horizon has been accomplished, it is passed to the output of the controller and the solution algorithm is executed for the next time instant with the prediction horizon has moved by one timestep. The idea of the receding horizon is depicted in figure 4.7

Figure 4.7: MPC Receding Horizon concept [14]

Implementation of FS-MPC solution algorithm will be analytically presented in the following part where the case of Model Predictive Direct Power Control (MPDPC) is presented and analyzed in depth.

CHAPTER

**FIVE**

# LCL FILTER AND DAMPING TECHNIQUES

Filters are used in all power converter systems to interface the grid side, from simple first order inductor to more complex high order filters. LCL filters present great performance in current ripple attenuation but introduce a resonance frequency in the system, which should be compensated in order to guarantee stability of the overall system. Several techniques exist for LCL filter damping, but main categorization is amon passive and active damping.

For reasons of completeness a brief overview of the main characteristics of an LCL filter and the design procedure followed in this thesis is described in the next two sections. A matlab script will be provided in the Appendix where calculations of transfer function characteristics and the design procedure will be automatically generated by input system parameters and specifications and an overview of filter resonance damping techniques will follow

#### 5.1 LCL Filter Overview

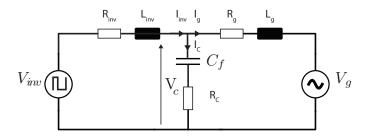

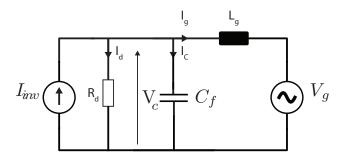

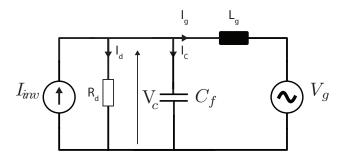

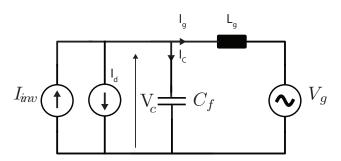

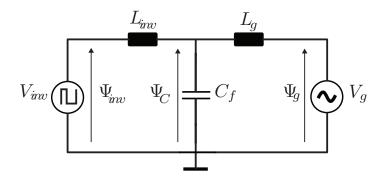

An LCL filter consists of 2 series inductors  $L_{inv}, L_g$  and one parallel capacitor  $C_f$  connected as in figure 5.1. The LCL filter interfaces the converter output to the grid, so the inverter voltage  $V_{inv}$  output is depicted as the filter input and the grid voltage  $V_g$  on the filter output. By applying Kirchhoff voltage and current equations, 5.1, while considering grid voltage as an ideal voltage source meaning that for the filter analysis it will be considered as a short-circuit for harmonic frequencies,  $V_g = 0$ , the transfer function of the filter can be derived by equation 5.2.  $R_{inv}, R_g, R_C$  are parasitic elements of filter components.

Figure 5.1: LCL output filter schematic

$$I_{inv} = I_C + I_g$$

$$V_{inv} = I_{inv}(sL_{inv} + R_{inv}) + V_C$$

$$V_C = I_g(sL_g + R_g) + V_g$$

$$V_C = I_C(\frac{1}{sC_f} + R_{inv})$$

$$V_g = 0$$

$$(5.1)$$

$$\frac{I_g}{V_{inv}} = \frac{sR_C C_f + 1}{s^3 L_g L_{inv} C_f + s^2 C_f (L_g (R_C + R_{inv}) + L_{inv} (R_C + R_g)) + R_g + s(L_g + L_{inv} + C_f (R_c R_g + R_c R_{inv} + R_g R_{inv})) + R_{inv}}$$

(5.2)

Which for neglecting  $R_{inv}$ ,  $R_g$ ,  $R_C$  as small, can be expressed as:

$$\frac{I_g}{V_{inv}} = \frac{1}{s^3 L_q L_{inv} C_f + s(L_q + L_{inv})}$$

(5.3)

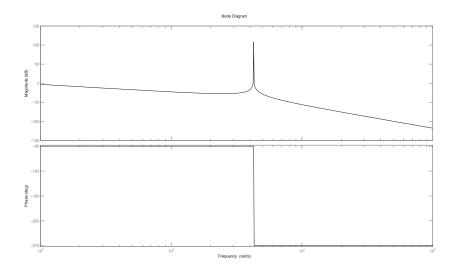

In figure 5.2 magnitude and phase bode diagrams of an LCL filter transfer function are shown. As it gets obvious a resonance effect occurs at a specific frequency. This resonance frequency can be calculated by equation 5.4 and any harmonics generated by the inverter around this frequency should be avoided or they will be augmented, leading to performance deterioration and possibly to instability.

$$f_{res} = \frac{1}{2\pi} \sqrt{\frac{L_{inv} + L_g}{L_{inv} L_g C_f}}$$

(5.4)

Figure 5.2: Magnitude and Phase response of an LCL filter

# 5.2 LCL Filter Design

Designing an output LCL filter for an inverter in a systematic approach has been described in [15],[16], and for the three-level NPC converter specifically in [17]. In all cases the design was set for steady switching frequency PWM converters. Since DPC employs variable switching frequency, the LCL filter will be designed for the average switching frequency expected.

First, parameters of the inverter and the grid should be considered. DC link voltage, average switching frequency of the converter, grid line voltage, grid frequency, and output power desired.

Second, resonance frequency of the filter is selected .As a general guideline, the resonance frequency is selected to be at least ten times the fundamental frequency of the generated output and at least half of the average switching frequency [18].

Then the inverter side inductor is calculated based on the desirable maximum current ripple  $\Delta I_{Lmax}$  at the inverter output, equation 5.5

$$Linv = \frac{V_{dc}}{16f_{sw}\Delta I_{Lmax}} \tag{5.5}$$

Current ripple  $\Delta I_{Lmax}$  refers to the difference between the instantaneous value of the waveform and its fundamental frequency and considering the switching nature of the converter can be calculated by equation 5.6 as a percentage  $p_L$ , where  $P_N$  is the nominal power of the inverter and  $V_{ph}$  the grid phase voltage. A good starting point is a 10% ripple,  $p_L = 0.1$ .

$$\Delta I_{Lmax} = p_L(\%) \frac{P_N \sqrt{2}}{3V_{ph}} \tag{5.6}$$

After that, filter capacitor value can be selected. The value of the capacitance is limited by the decrease of power factor that occurs, which should remain below 5% at rated power,  $p_C=0.05$ . In this particular application where reactive power compensating for the power factor decrease due to the filter capacitor is generated, higher percentage can be used leading to even smaller inductors used in final filter design, as long as current ripple remains acceptable.  $E_N$  is the line to line rms voltage and  $S_N$  the nominal power.

$$C_f = p_C(\%) \cdot C_b \tag{5.7}$$

$$C_b = \frac{1}{\omega_N Z_b} \tag{5.8}$$

$$Z_b = \frac{E_N^2}{S_N} \tag{5.9}$$

At last grid side inductance can be calculated, such as resonance frequency of the filter defined by equation 5.4 is accomplished. Grid side and inverter side inductance are related with a ratio r,  $r = \frac{L_{inv}}{L_g}$ , and the relation between the harmonic current generated by the inverter and the current injected into the grid can be calculated as in equation 5.10.

$$\frac{I_g(h)}{I_{inv}(h_{sw})} = \frac{1}{L_g C_f |\omega_{res}^2 - \omega_{sw}^2|} = \frac{1}{|1 + r[1 - (L_{inv} C_f \omega_{sw}^2) \cdot p_C]|}$$

(5.10)

When designing output filter of a power converter for grid connected applications, compatibility with grid regulations should be taken into account. Among other factors such as reactive power level, grid short circuit current, voltage fluctuations and flicker, harmonic content of the delivered current should be under specific limits. This set of limits and regulations is thoroughly described in the IEEE Standard 519-1992, and presents the limits of total harmonic distortion of currents, for voltage levels below 69kV, table 5.1. The limits in the table are calculated for six pulse rectifiers, so when converters with another number of pulses (q) are used, the limits of the harmonic order are increased by a factor  $\sqrt{\frac{q}{6}}$  which in the case on the 3 level NPC will be  $\sqrt{2}$ .

| Maximum Harmonic Current Distortion in Percent of $I_L$              |      |                 |                 |                 |            |      |  |  |

|----------------------------------------------------------------------|------|-----------------|-----------------|-----------------|------------|------|--|--|

| Individual Harmonic Order (Odd Harmonics)                            |      |                 |                 |                 |            |      |  |  |

| $I_{sc}/I_L$                                                         | < 11 | $11 \le h < 17$ | $17 \le h < 23$ | $23 \le h < 25$ | $35 \le h$ | TDD  |  |  |

| < 20                                                                 | 4.0  | 2               | 1.5             | 0.6             | 0.3        | 5.0  |  |  |

| 20 < 50                                                              | 7.0  | 3.5             | 2.5             | 1               | 0.5        | 8.0  |  |  |

| 50 < 10                                                              | 10.0 | 4.5             | 4.0             | 1.5             | 0.7        | 12.0 |  |  |

| 100 < 1000                                                           | 12.0 | 5.5             | 5               | 2               | 1          | 15.0 |  |  |

| > 1000                                                               | 15.0 | 7.0             | 6.0             | 2.5             | 1.4        | 20.0 |  |  |

| Even harmonics are limited to 25% of the odd harmonics limits above. |      |                 |                 |                 |            |      |  |  |

Table 5.1: Current distortion limits described by IEEE Standard 519-1992

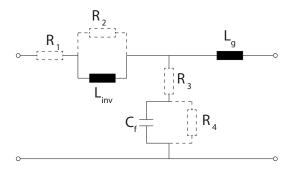

# 5.3 Passive Damping

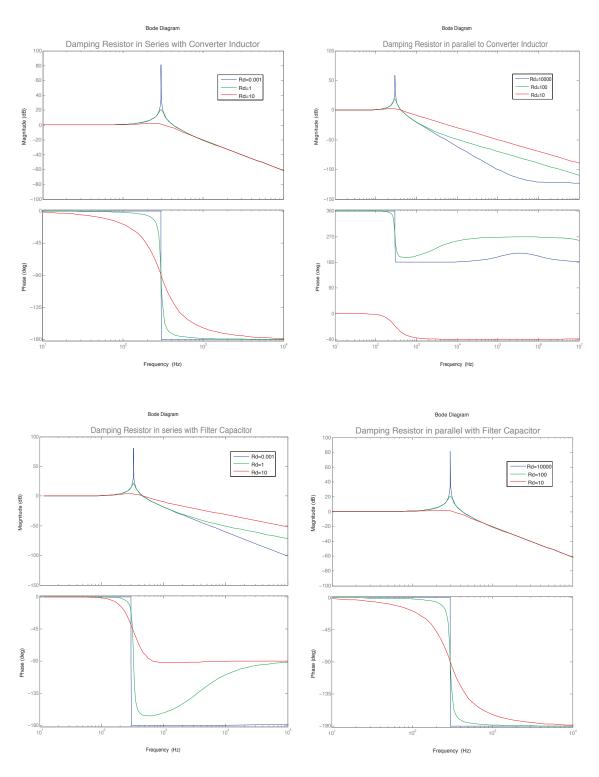

Passive damping of the resonant frequency of the filter is achieved by adding a resistance in series or in parallel with the capacitance or inductance of the filter. The four possible positions are shown in figure 5.3 where no parasitic values of the filter are considered.

Figure 5.3: possible topologies for passive damping

The effect of the damping resistance placed in each of the four positions is shown in figure 5.4. By observing the bode diagrams, for critical damping values, the parallel to filter capacitor damping resistor, and the the series to converter side inductor damping resistor placement respond as expected, by following the filter response throughout whole frequency range, except the resonance frequency. Also both damping resistor topologies introduce minimal delay compared to the others.

Power losses on a damping resistor  $R_d$  can be calculated by:

$$P_d = 3R_d \sum_{h} [i_i(h) - i_g(h)]^2$$

Since extra power losses on the power converter chain lead to low power efficiency, other methods to actively damp resonant frequency of the filter should be considered. In the next section, three main approaches to active damping through extra control loops in the existing control scheme are reviewed.

Figure 5.4: Bode plots of LCL filter with passive damping

### 5.4 Active Damping

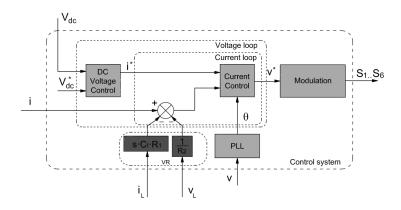

#### 5.4.1 Virtual Resistor method

One approach to actively damp unwanted resonant content of the output current due to the LCL filter transfer characteristics, is to mimic the behavior of passive damping resistor previously described, by introducing a virtual resistor in the control loop. Through this extension, damping current that would dissipate onto the damping resistor is calculated and forwarded to the reference value, avoiding physical power losses on the resistor.

As for passive damping, there are four places for the damping resistor to be placed, or a combination of them. Depending on the virtual resistor placement, an extra sensor will be needed, a current sensor if the virtual resistor is considered in series with filter inductor or capacitor, and a voltage sensor if it is considered in parallel.

By considering from the filter equivalent schematic with damping resistor  $R_d$  virtually connected parallel to filter capacitor, figure 5.5, converter side inductor and converter voltage act as a current controlled source, and we can express the transfer function of the system as:

$$\frac{I_g}{I_{inv}} = \frac{\frac{1}{L_g C}}{s^2 + s \frac{1}{R_d C} + \frac{1}{L_g C}}$$

Figure 5.5: LCL filter diagram with converter output and inductor as a current source

Damping current of the virtual resistor is calculated as,  $I_d = \kappa_d V_c$ , where  $K_d$  is the gain  $\kappa_d = \frac{1}{R_d}$  of the controllable current source and controls the amount of filter resonance damping applied. By examining filter transfer function as a general form second order system, the undamped natural frequency of the system and damping factor can be calculated based on the filter parameters  $C, L_g$  and damping ratio  $\zeta$ .

$$\omega_n = \sqrt{\frac{1}{L_g C}}$$

$$\kappa_d = 2\zeta \sqrt{\frac{C}{L_g}} = \frac{1}{R_d}$$

An example of a current controlled power converter incorporating virtual resistor concept block diagram is illustrated in figure 5.6

Figure 5.6: Virtual Resistor method Active Damping block diagram [18]

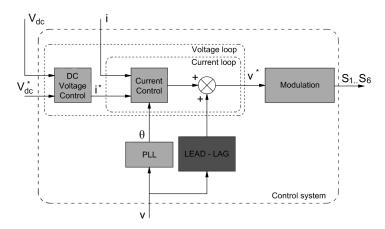

#### 5.4.2 Lead-Lag compensator method

The shift in the phase angle introduced by the filter can be compensated with an lead-lag compensator. The lead compensator has the following equation:

$$L(s) = k_d \frac{T_d s + 1}{\alpha T_d s + 1}$$

The lead compensator adds positive phase to the system. The compensator needs to be tuned to the resonance frequency of the filter.

An active damping method using a lead-lag compensator is described in [19]. This method uses a lead-lag element in the synchronous reference frame applied to the feedback from the capacitor voltage, figure 5.7

Figure 5.7: Lead-Lag compensator method Active Damping block diagram [18]

The grid voltages are used both for the grid synchronization and for the active damping. First, they are transformed in the reference frame the controller works with and then inputed to a lead-lag block. Then, the output from the lead-lag block are added to the output of the current regulators and then processed to obtain the duty cycles to be sent to the inverter.

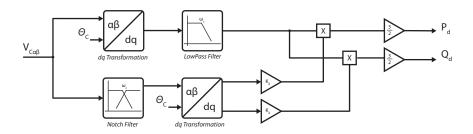

#### 5.4.3 Notch Filter method

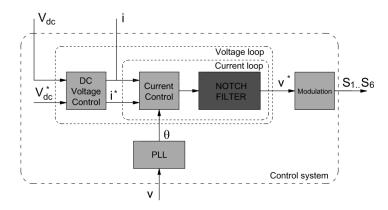

This method consists of adding a filter in series with the reference voltage of the modulator, figure 5.8

The basic idea can be explained in the frequency domain by introducing a negative peak (notch) in the system, that compensates for the resonant peak due to the LCL filter [20]. This can be done by adding a notch filter in the current loop. The frequency of the Notch filter has to be tuned at the resonance frequency of the LCL filter, in order to provide a good damping.

Figure 5.8: Notch Filter method Active Damping block diagram [18]

# Part II

# Analysis and Comparative Study of DPC and MPDPC techniques

#### DIRECT POWER CONTROL

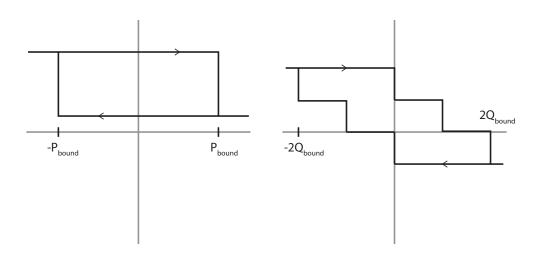

Direct Power Control of DC/AC inverter stems from the well known Direct Torque Control of AC machines, based on the similarity of an induction motor's electric equivalent circuit to the output load and the grid connection equivalent of a DC/AC inverter. Basic principles of DTC are incorporated in the DPC technique in order to control active and reactive power at the inverter terminals, in the same manner as torque and flux of an induction motor are controlled in DTC. Key differences of DPC from vector control are that no modulator is used, leading to a variable switching frequency output, and that current is regulated indirectly, in terms of active and reactive power.

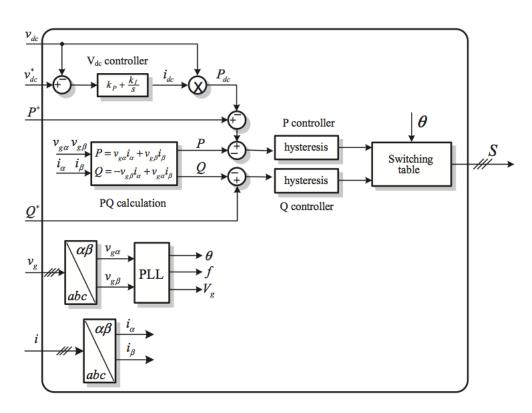

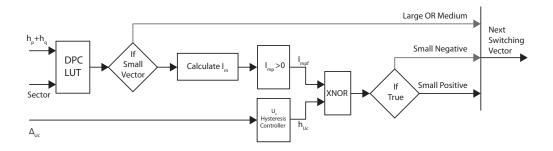

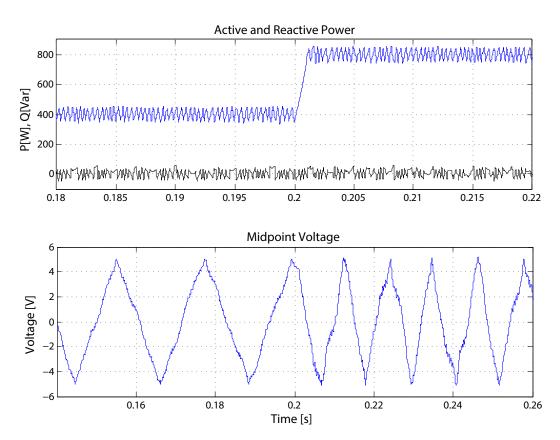

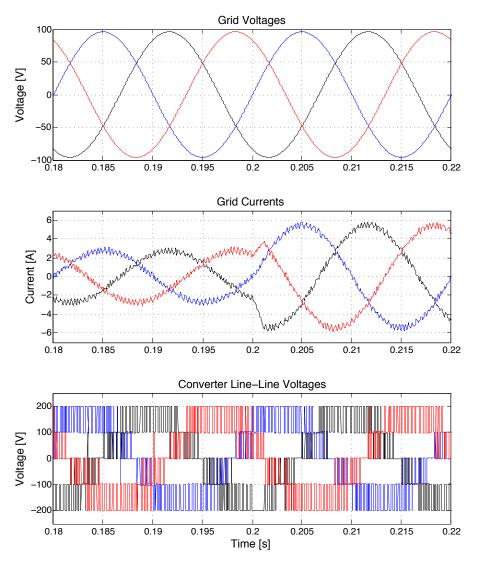

The basic control scheme of DPC is that, active and reactive power are calculated and are fed to hysteresis controllers whose output, together with grid voltage angle information select the optimum switching state from a predefined lookup table. As it is obvious, both accurate calculation of active-reactive power and correct design of the switching table is critical. System quality parameters can be tuned through the hysteresis controllers, either by utilizing a multilevel controller or by tightening them bounds, or through a different design approach of the lookup table. More control loops might exist, like midpoint voltage balancing as in the case of 3 level NPC inverter but a more in depth analysis of the case specific DPC scheme will be presented in the next section. Usually active power reference of the P hysteresis controller is set by a PI loop monitoring the DC bus voltage and the reactive power reference of the Q hysteresis controller is set to zero to assure unity power factor at the converter terminals.

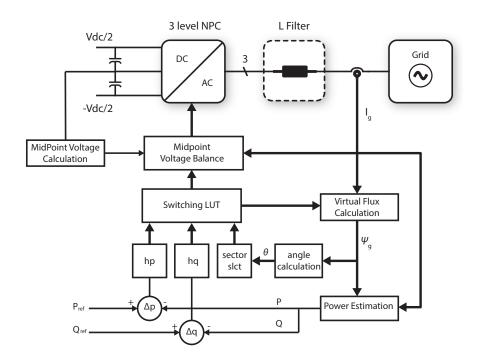

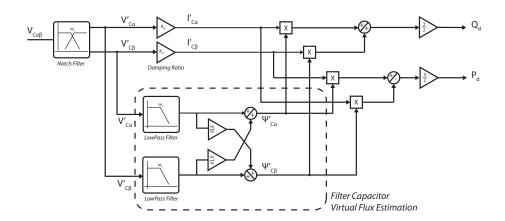

#### 6.1 DPC of 3 level NPC

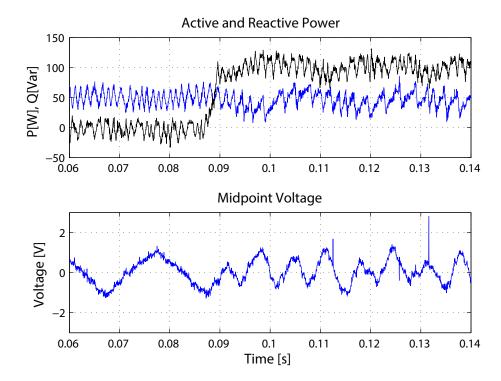

Direct Power Control of a 3 level NPC inverter is shown on the block diagram in figure 6.1 .

Figure 6.1: 3 level NPC Direct Power Control Block Diagram

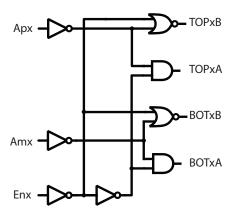

Measurements of current in the three phases of the VSI  $^1$  and voltage across two DC link capacitors are performed. A virtual flux estimator is employed, to calculate virtual flux at the output of the inverter, based on current measurements and voltage output of the inverter which can be estimated from the switching state and the DC link voltage. Based on virtual flux, active and reactive power are estimated in a PQ estimator and are fed to the P and Q hysteresis controllers. Also angle information of the connected grid voltage is acquired from virtual flux which is fed to a sector decision control block where it is determined in which sector of the  $\alpha\beta$  plane the virtual flux vector is moving. From the hysteresis controllers and the sector decision control block outputs the next switching output, or better the next inverter voltage vector in the  $\alpha\beta$  plane, is selected from an existing switching Look Up Table. The inverter voltage vector is fed in a midpoint voltage balancing control block where it gets translated to the switching control signals, in respect to the voltage balancing action.

As it gets obvious, the control loop must be executed very fast in order to have a properly functioning system with accurate power estimation and fast switching state determination, demanding a control system with fast processing resources which might be a serious drawback of the DPC control method in certain applications. On the other hand use of virtual flux and absence of dq coordinate transformations allow for very fast control loop of a DPC imple-

<sup>&</sup>lt;sup>1</sup>only two phase current measurements are needed if the system is considered balanced

mentation with most modern processors available. Next each control block is analysed in depth.

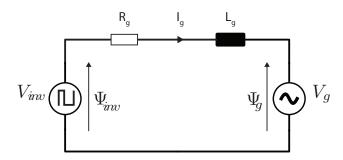

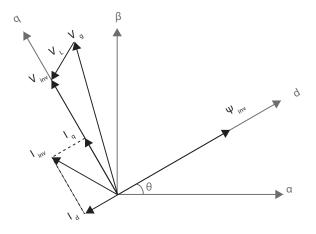

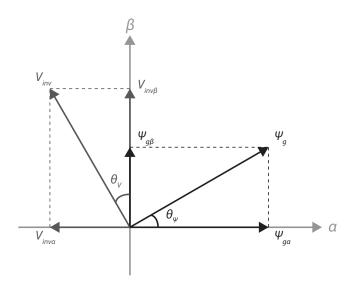

#### 6.1.1 Virtual Flux

Due to the resemblance of a grid connected NPC inverter to the stator equivalent of an AC motor with resistance and inductance of grid side connection resembling the stator resistance and leakage inductance, while grid voltage is similar to motor's electro-motive force, a virtual measurement can be considered, that of virtual flux. Virtual flux is defined in the same way as magnetic stator flux linkage would be, by integrating stator voltage, hence grid side virtual flux can be estimated by integrating grid voltage, as in equation 6.1. Without the use of virtual flux concept, when calculating active and reactive power, derivation of the grid side current would be needed which would lead to added distortion due to extra noise present in the control loop.

Figure 6.2: grid connected VSI equivalent circuit

$$\psi_g = \int V_g \, \mathrm{d}t \tag{6.1}$$

$$\psi_g = \int (V_{inv} - R_g \cdot I_g) \, \mathrm{d}t - L_g \cdot I_g \tag{6.2}$$

Which for neglecting series resistance transforms to:

$$\psi_g = \int V_{inv} \, \mathrm{d}t - L_g \cdot I_g \tag{6.3}$$

Voltage inverter  $V_{inv}$  can be estimated by the measured DC link voltage and knowledge of the current switching state, and after the  $\alpha\beta$  transformation

inverter output voltage can be calculated by:

$$V_{invR} = S_R \cdot V_{dc}$$

$$V_{invS} = S_S \cdot V_{dc}$$

$$V_{invT} = S_T \cdot V_{dc}$$

$$V_{inv\alpha} = \frac{V_{dc}/2}{3} (2S_R - S_S - S_T)$$

$$V_{inv\beta} = \frac{V_{dc}/2}{\sqrt{3}} (S_S - S_T)$$

$$(6.4)$$

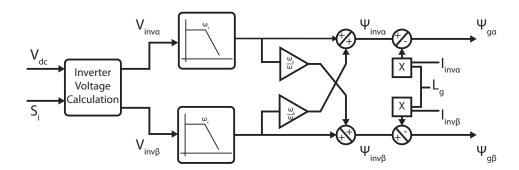

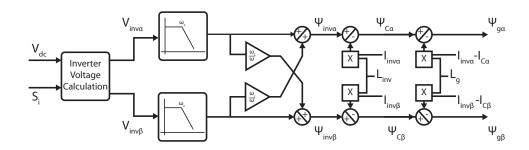

And Virtual Flux can finally be estimated by equations:

$$\psi_{g\alpha} = \int V_{inv\alpha} dt - L_g \cdot I_{g\alpha}$$

$$\psi_{g\beta} = \int V_{inv\beta} dt - L_g \cdot I_{g\beta}$$

(6.5)

In practice when integrating a measured voltage, a dc value is present, which in steady state can be calculated as  $\frac{V_{dc}}{\omega_s}$ . In order to avoid rounding errors of dc offset subtraction and make the virtual flux calculation less immune to noise the pure integrator is replaced by a first order low pass filter with a cut off frequency at 5 Hz. Phase and magnitude compensation is followed as presented in [21] and [22] for virtual flux estimation in a induction machine stator. Calculating inverter flux with pure integration in the frequency domain

$$\psi_{inv} = \frac{V_{inv}}{j\omega} \tag{6.6}$$

Calculating inverter flux with low pass filter with a cut off frequency  $f_c$ :

$$\psi'_{inv} = \frac{V_{inv}}{j\omega + \omega_s} \tag{6.7}$$

Solving equation 6.7 for  $V_{inv}$  and replacing in equation 6.6 we can relate the calculated inverter flux from the pure integrator with the low pass filter technique as

$$\psi_{inv} = \psi'_{inv} - j\frac{\omega_c}{\omega}\psi'_{inv} \tag{6.8}$$

Which in the  $\alpha\beta$  plane can be expressed as in equation 6.9 and the implemented control block can be summarized in figure 6.3 where grid flux is derived by subtracting quantity  $L_g \cdot I_g$  from the calculated inverter flux, as described in equation 6.3

$$\psi_{inv\alpha} = \psi'_{inv\alpha} + \frac{\omega_c}{\omega} \psi'_{inv\beta}$$

$$\psi_{inv\beta} = \psi'_{inv\beta} - \frac{\omega_c}{\omega} \psi'_{inv\alpha}$$

(6.9)

Figure 6.3: Virtual flux calculation block diagramm

#### 6.1.2 Power Calculation

As previously explained, fast and accurate estimation of active and reactive power is critical in Direct Power Control. In order to avoid complex calculations and rotating coordinate transformations, power is calculated in the  $\alpha\beta$  reference frame from virtual flux already calculated by the previously described estimator. According to the space vector theorem, instantaneous power can be calculated by real and imaginary product of voltage vector and the conjugate current vector: