## Εθνικό Μετσοβίο Πολυτέχνειο

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΏΝ ΚΑΙ ΜΗΧΑΝΙΚΏΝ ΥΠΟΛΟΓΙΣΤΏΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΏΝ

## Market-Based Resourse Management for Many-Core Systems

## $\Delta$ ιπλωματική Εργασία

του

ΘΕΜΙΣΤΟΚΛΗ Γ. ΜΕΛΙΣΣΑΡΗ

Επιβλέπων: Δημήτριος Σούντρης

Επ. Καθηγητής Ε.Μ.Π.

ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ & ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ  $\label{eq:continuous} A\vartheta \acute{\eta} \nu \alpha, \ Iούλιος \ 2014$

## Market-Based Resourse Management for Many-Core Systems

### $\Delta$ ΙΠΛΩΜΑΤΙΚΉ ΕΡΓΑΣΙΑ

του

#### ΘΕΜΙΣΤΟΚΛΗ Γ. ΜΕΛΙΣΣΑΡΗ

Επιβλέπων: Δημήτριος Σούντρης

Επ. Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την η Ιουλίου 2014.

(Υπογραφή) (Υπογραφή) (Υπογραφή)

.....

Δημήτριος Σούντρης Κιαμάλ Ζ. Πεκμεστζή Γεώργιος Οικονομάκος Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π. Καθηγητής Ε.Μ.Π.

| (Υπογραφή)  |      |

|-------------|------|

| (1 πογραφη) |      |

|             | I.Π. |

|             |      |

|             |      |

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Εργαστήριο Μικροϋπολογιστών & Ψηφιακών Συστημάτων

Copyright ©-All rights reserved ΘΕΜΙΣΤΟΚΛΗΣ Γ. ΜΕΛΙΣΣΑΡΗΣ, 2014. Με επιφύλαξη παντός δικαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

# Ευχαριστίες

Θα ήθελα να εκφράσω τις θερμές μου ευχαριστίες προς τον επιβλέποντα καθηγητή κ. Δ. Σούντρη για την εμπιστοσύνη και την πολύτιμη καθοδήγηση καθ΄ όλη τη διάρκεια της άριστης αυτής συνεργασίας, που οδήγησαν στην επιτυχημένη ολοκλήρωση της διπλωματικής εργασίας. Επίσης, ευχαριστώ ιδιαίτερα τον διδάκτορα Ηρακλή Αναγνωστόπουλο, η συμβολή του οποίου με τις γνώσεις, την πολύτιμη βοήθεια και την συνεχή υποστήριξη ήταν καθοριστική στην πορεία της εργασίας. Τέλος, θα ήθελα να ευχαριστήσω τον διδάκτορα Αλέξανδρο Μπάρτζα που βοήθησε σημαντικά με τις συμβουλές του.

## Περίληψη

Αντιχείμενο της διπλωματιχής αποτελεί η μελέτη και η ανάπτυξη μιας κλιμαχώσιμης και κατανεμημένης πλατφόρμας (framework) διαχείρισης πόρων σε χρόνο εκτέλεσης για συστήματα πολλαπλών πυρήνων. Σε αυτήν την πλατφόρμα η διαχείριση πόρων είναι βασισμένη σε μοντέλα, τα οποία είναι εμπνευσμένα από την οικονομία. Παρουσιάζεται ένας διαχειριστής πόρων, ο οποίος προσφέρει ένα περιβάλλον διαχείρισης πόρων και εφαρμογών καθ΄ όλη τη διάρχεια ζωής τους, στο οποίο η κατανομή και δρομολόγηση των εφαρμογών στους πόρους πραγματοποιείται με αλγόριθμους βασισμένους σε κανόνες αγοράς. Η αποδοτικότητα κάθε μοντέλου αξιολογείται βάσει της πτώσης της αξιοπιστίας των πόρων (μετρική MTTF-Mean Time To Failure).

### Λέξεις Κλειδιά

Πολυ-πύρηνα Συστήματα, Κατανεμημένη Διαχείριση Πόρων, Διαχείριση πόρων σε χρόνο εκτέλεσης, Οικονομικά μοντέλα

## Abstract

The purpose of this diploma thesis is the design and development of a scalable and distributed run-time resource management framework for Many-core systems. In this framework, resource management is based on economy-inspired models. The presented resource management framework offers an environment that manages both application tasks and resources at run-time, matches and distributes application tasks across resources with algorithms which are based on market principles. The efficiency of each model is evaluated with respect to resource reliability degradation (metric MTTF-Mean Time to Failure).

### **Keywords**

Many-core Systems, Distributed Resource Management, Run-time Resource Management, Economic models

# Contents

| $\mathbf{E}'$ | υχαρ           | ιστίες |                                                                 | 1  |

|---------------|----------------|--------|-----------------------------------------------------------------|----|

| П             | ερίλι          | ηψη    |                                                                 | 3  |

| A             | bstra          | ıct    |                                                                 | 5  |

| C             | onter          | nts    |                                                                 | g  |

| Li            | st of          | Figur  | es                                                              | 12 |

| 1             | Bac            | kgrou  | nd knowledge                                                    | 13 |

|               | 1.1            | Introd | luction                                                         | 13 |

|               | 1.2            | Many-  | -core Systems                                                   | 15 |

|               |                | 1.2.1  | Multiple cores                                                  | 15 |

|               |                | 1.2.2  | Interconnection Networks                                        | 16 |

|               |                | 1.2.3  | Memory                                                          | 17 |

|               |                | 1.2.4  | Scalability Considerations for Many-Core Processors             | 18 |

|               |                | 1.2.5  | Future Trends                                                   | 19 |

|               |                | 1.2.6  | Examples of Many-Core Systems                                   | 21 |

|               | 1.3            | Resou  | rce Management                                                  | 25 |

|               |                | 1.3.1  | Scheduling                                                      | 25 |

|               |                | 1.3.2  | The mapping problem                                             | 26 |

|               | 1.4            | Econo  | omic principles                                                 | 29 |

|               |                | 1.4.1  | Supply                                                          | 30 |

|               |                | 1.4.2  | Market equilibrium                                              | 31 |

|               |                | 1.4.3  | Auctions                                                        | 32 |

| 2             | $\mathbf{Rel}$ | ated V | Vork                                                            | 35 |

|               | 2.1            | ADAN   | M: Run-time Agent-based Distributed Application Mapping for on- |    |

|               |                | chip ( | Communication [2] $\dots$                                       | 37 |

|               | 2.2            | A Div  | ride and Conquer based Distributed Run-time Mapping Methodology |    |

|               |                | for Ma | any-Core platforms [3]                                          | 39 |

8 Contents

|   | 2.4 | tems $[25]$                                                            | 41         |

|---|-----|------------------------------------------------------------------------|------------|

|   |     | A taxonomy of market-based resource management systems for utility-    |            |

|   |     | driven cluster computing [35]                                          | 44         |

|   | 2.5 | Economic models for resource management and scheduling in Grid comput- |            |

|   |     | ing [8]                                                                | 46         |

|   | 2.6 | Motivation                                                             |            |

| 3 | Pro | posed Methodology                                                      | 47         |

| J | 3.1 | Introduction                                                           |            |

|   | 3.2 | Resource Degradation Overview                                          |            |

|   | 3.3 | Resource Modeling                                                      |            |

|   | 3.4 | Task Modeling                                                          |            |

|   | 3.5 | Proposed Market Models                                                 |            |

|   | 5.5 | 3.5.1 Introduction                                                     |            |

|   |     | 3.5.2 Commodity Market Model                                           |            |

|   |     | 3.5.3 Posted Price Model                                               |            |

|   |     | 3.5.4 Auction Model                                                    |            |

| 4 | Imr | plementation of proposed framework                                     | 65         |

| - | 4.1 | Introduction                                                           |            |

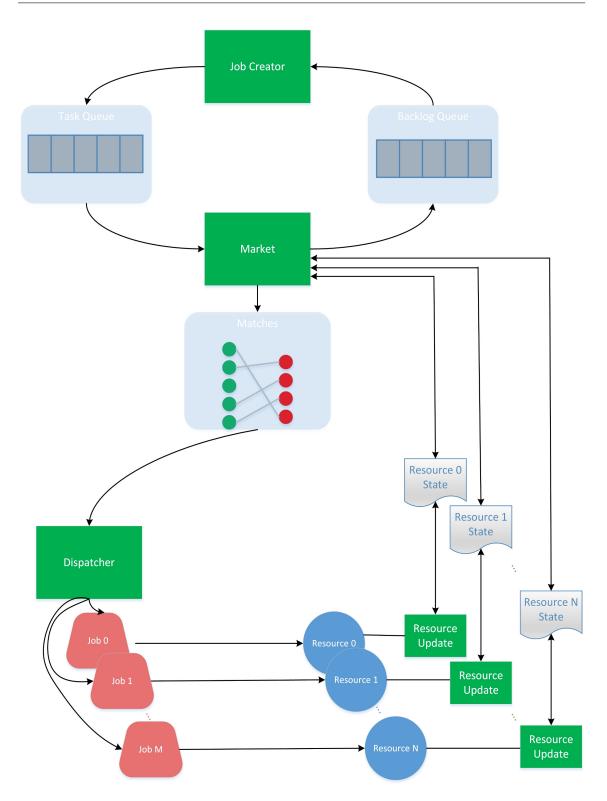

|   | 4.2 | Framework Architecture                                                 |            |

|   | 1.2 | 4.2.1 Job Creator                                                      |            |

|   |     | 4.2.2 Market                                                           |            |

|   |     | 4.2.3 Dispatcher                                                       |            |

|   |     | 4.2.4 Resource Update                                                  |            |

|   | 4.3 | Design Decisions                                                       |            |

|   | 1.0 | 4.3.1 Clock Cycle Abstraction                                          |            |

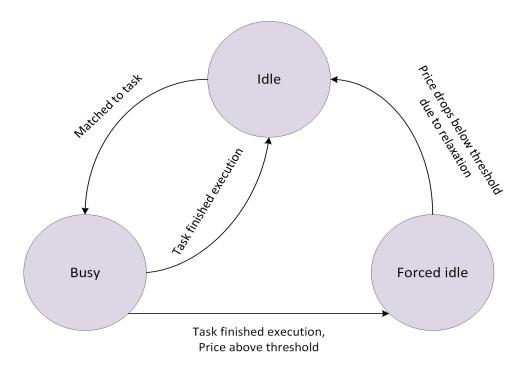

|   |     | 4.3.2 Resource States                                                  | 70         |

|   | 4.4 | Implementation Details                                                 | 72         |

|   |     | 4.4.1 Synchronization scheme                                           | 72         |

|   |     | 4.4.2 Distributed price calculation                                    | 72         |

|   | 4.5 | Conclusion                                                             | 73         |

| 5 | Exp | perimental Results                                                     | <b>7</b> 5 |

| 6 | Cor | nclusion and Future Work                                               | 85         |

| - | 6.1 | Summary                                                                | 87         |

|   | 6.2 | Future Work                                                            | 87         |

|   |     | 6.2.1 Intel SCC and Intel Xeon Phi port                                | 87         |

|   |     | 6.2.2 Task Migration                                                   | 87         |

|   |     | 6.2.3 Parsec Benchmarks and Input Distributions                        |            |

| Contents     |                                              | 9  |

|--------------|----------------------------------------------|----|

| 6.2.4        | Implementing a model for distributed mapping | 88 |

| Bibliography |                                              | 90 |

# List of Figures

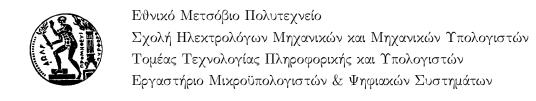

| 1.1  | Intel Microprocessors                                                        | 14 |

|------|------------------------------------------------------------------------------|----|

| 1.2  | Productivity gap between hardware and software design [22]                   | 15 |

| 1.3  | Interconnect Architectures [33]                                              | 17 |

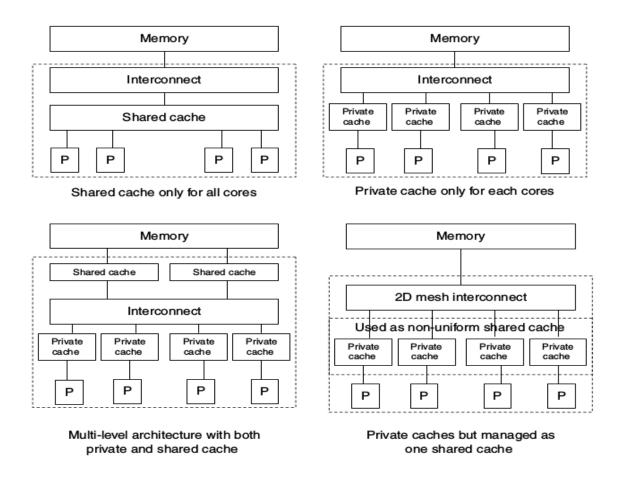

| 1.4  | Cache Memory Architectures [33]                                              | 18 |

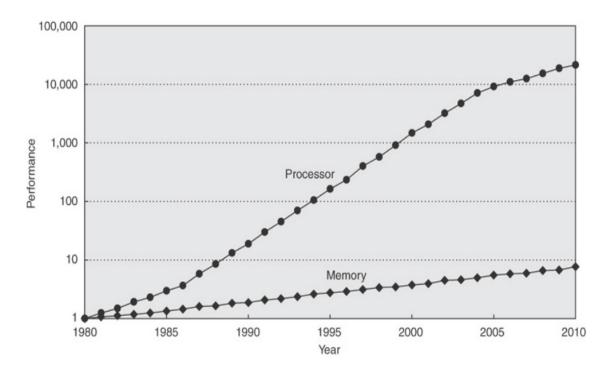

| 1.5  | Processor and memory performance gap [23]                                    | 19 |

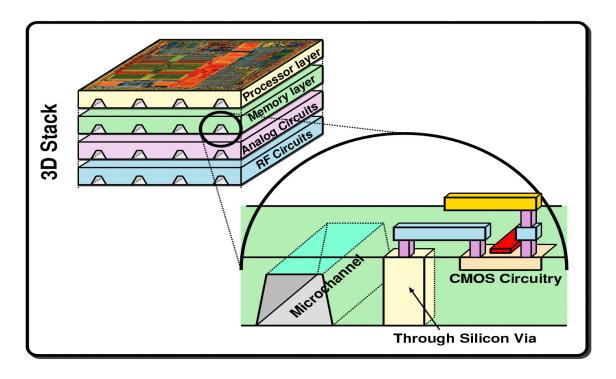

| 1.6  | Scheme of 3D-IC stack and vertical interconnection [16]                      | 20 |

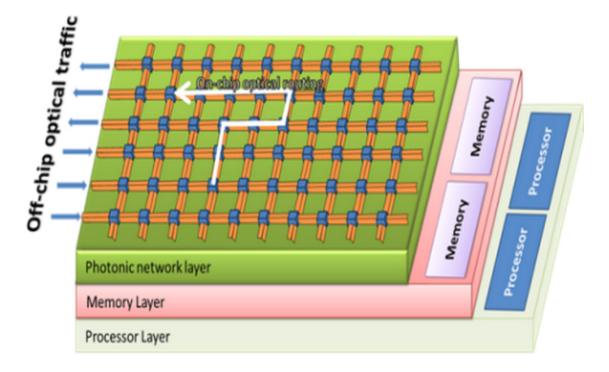

| 1.7  | 3D silicon processor chip featuring on-chip nanophotonic network [19] $$     | 21 |

| 1.8  | The Manycore Integrated Core (MIC) architecture on Xeon Phi $[11]$           | 22 |

| 1.9  | The Xeon Phi Coprocessor core [6]                                            | 22 |

| 1.10 | Scematic of the Intel SCC platform architecture [30]                         | 23 |

| 1.11 | Scematic of the Tile Processor Architecture [12]                             | 24 |

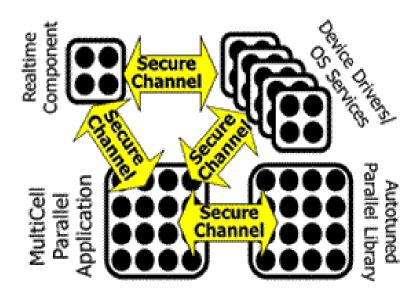

| 1.12 | Inter-cell communication [9]                                                 | 26 |

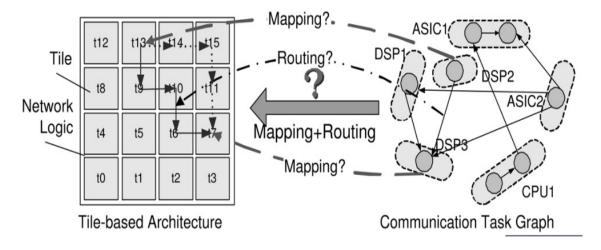

| 1.13 | The mapping/routing problem [20]                                             | 27 |

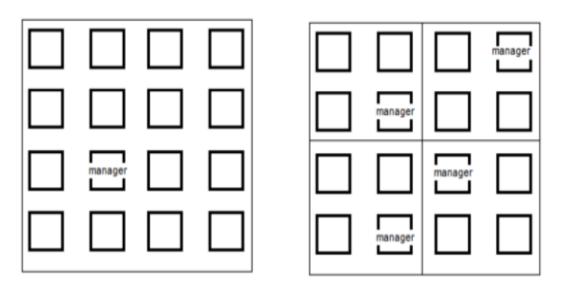

| 1.14 | Processor tiles examples using centralized and distributed mapping $[30]$    | 29 |

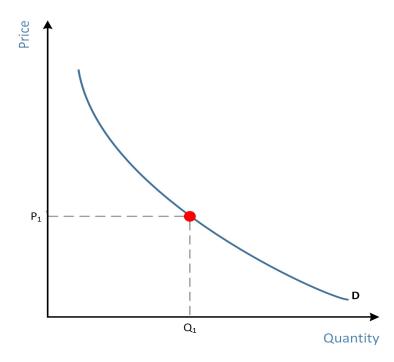

| 1.15 | Demand Curve                                                                 | 30 |

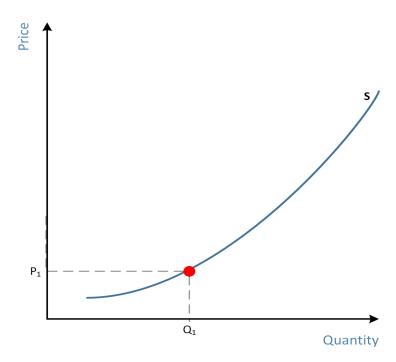

| 1.16 | Supply Curve                                                                 | 31 |

| 1.17 | Market equilibrium                                                           | 32 |

| 2.1  | Flow of the ADAM algorithm [2]                                               | 37 |

| 2.2  | The re-clustering process of the ADAM algorithm. [2]                         | 38 |

| 2.3  | Main idea of the run-time manager of [3]                                     | 39 |

| 2.4  | Flow of the run-time resource management of [3]                              | 40 |

| 2.5  | Communication between agents for a) local and b) distant target regions;     |    |

|      | c) a display the divide-and-conquer behavior for larger target regions [25]. | 42 |

| 2.6  | Interaction of components of the DistRM algorithm [25]                       | 43 |

| 2.7  | Classification of market-based RMSs [35]                                     | 44 |

| 2.8  | Abstract model for market-based cluster RMSs [35]                            | 45 |

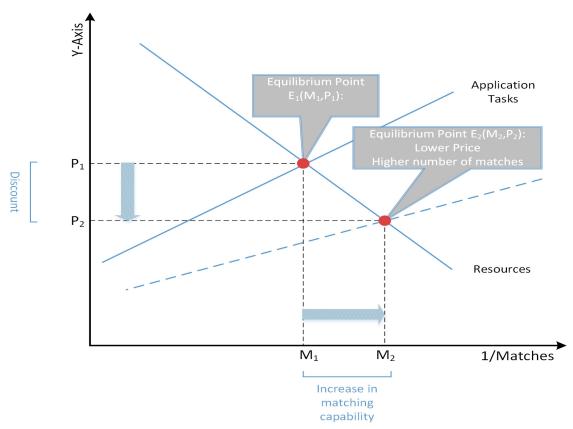

| 3.1  | Supply/demand equivalent for tasks/resources                                 | 52 |

| 3.2  | Impact of reliability fluctuations on equilibrium                            | 53 |

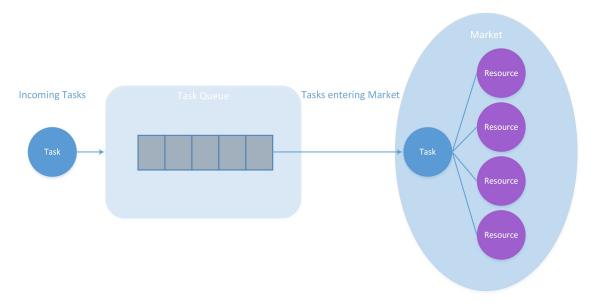

| 3.3  | Market of available resources and application tasks                          | 54 |

| 3.4  | Resource and task matching                                                   | 55 |

12 List of Figures

| 3.5  | Matching example in the Commodity Market model                                            | 56 |

|------|-------------------------------------------------------------------------------------------|----|

| 3.6  | Discount mechanism of the Posted Price model                                              | 57 |

| 3.7  | Behavior of the Posted Price model                                                        | 57 |

| 3.8  | Task queue in auction model                                                               | 58 |

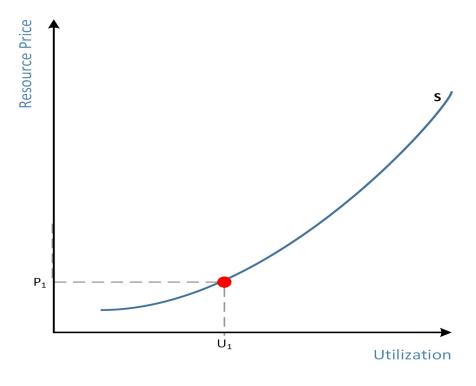

| 3.9  | Supply-based utilization curve                                                            | 59 |

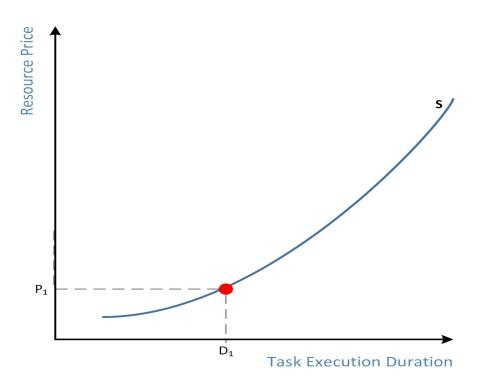

| 3.10 | Supply-based task duration curve                                                          | 60 |

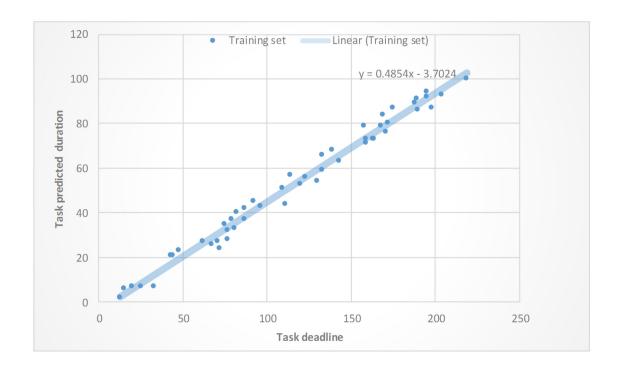

| 3.11 | Optimal linear function produced by gradient descent                                      | 63 |

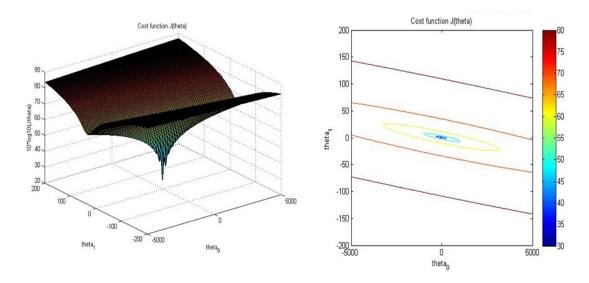

| 3.12 | Cost function used by gradient descent                                                    | 63 |

| 4.1  | The Resource Manager Architecture                                                         | 68 |

| 4.2  | Resource state transitions                                                                | 71 |

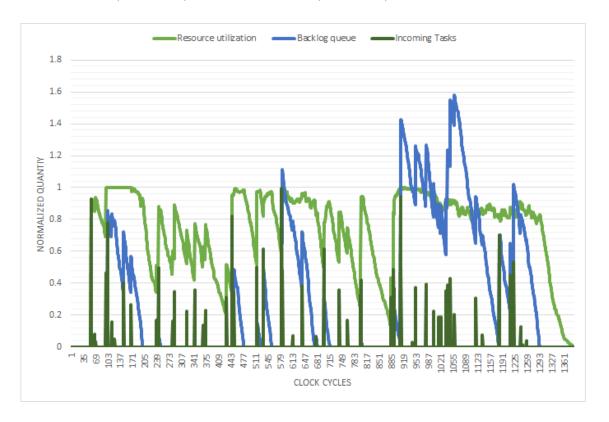

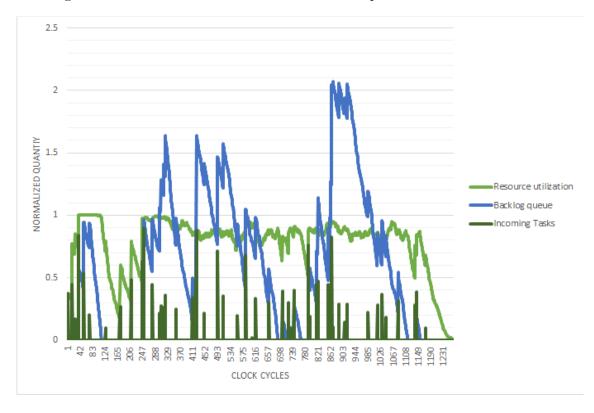

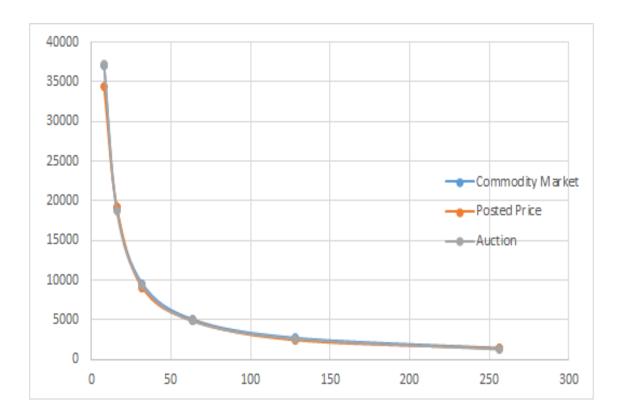

| 5.1  | Behavior of Commodity Model over time                                                     | 77 |

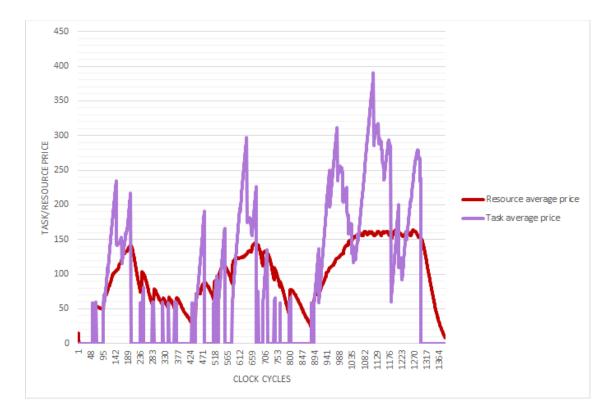

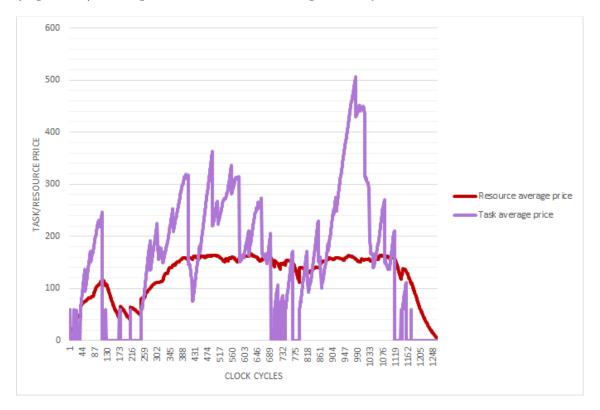

| 5.2  | Commodity model resource and task price fluctuations over time $\ \ldots \ \ldots$        | 78 |

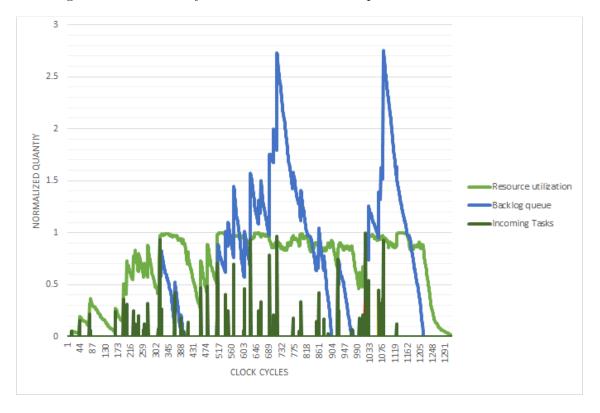

| 5.3  | Behavior of Posted Price over time                                                        | 78 |

| 5.4  | Posted Price model resource and task price fluctuations over time $\dots$                 | 79 |

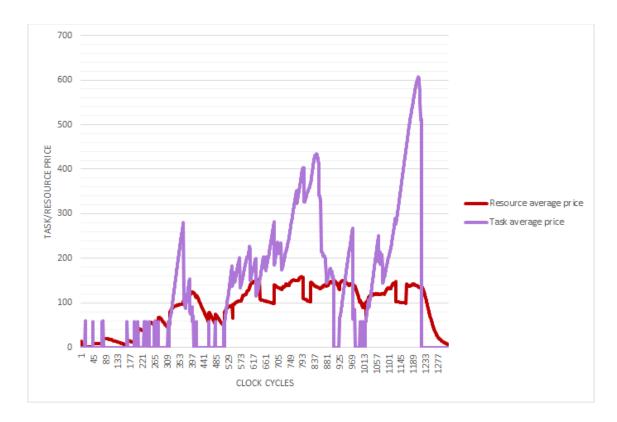

| 5.5  | Behavior of Auction model over time                                                       | 79 |

| 5.6  | Auction model resource and task price fluctuations over time $\ \ldots \ \ldots \ \ldots$ | 80 |

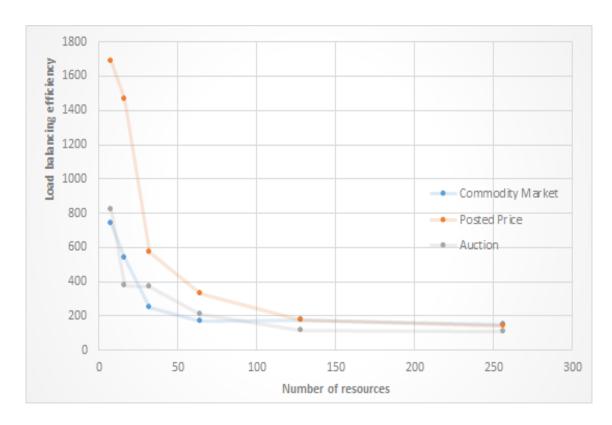

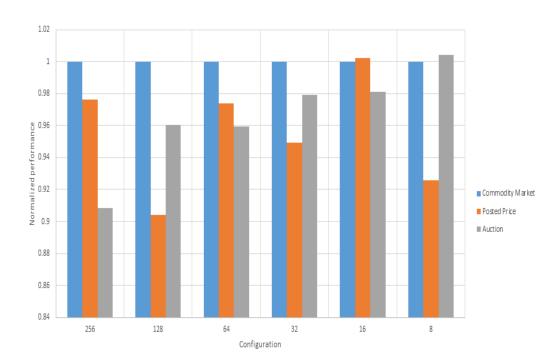

| 5.7  | Comparison of load balancing efficiency                                                   | 81 |

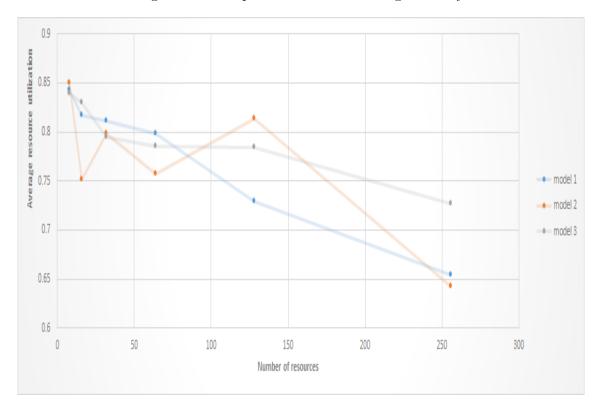

| 5.8  | Comparison of average resource utilization                                                | 81 |

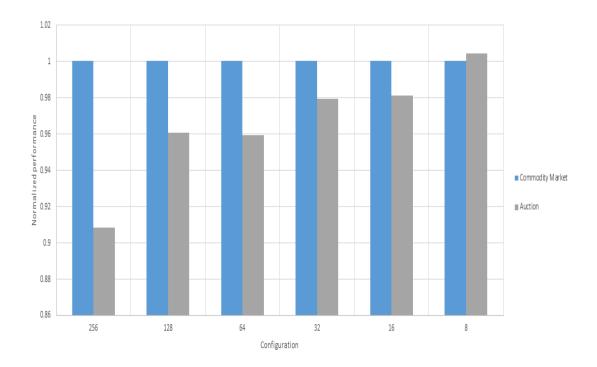

| 5.9  | Comparison of performance between all models                                              | 82 |

| 5.10 | Comparison of performance between the Commodity Market and Auction                        |    |

|      | $models \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                   | 82 |

| 5.11 | Comparison of performance between all models                                              | 83 |

| 6.1  | Using DVFS to aim at reliability                                                          | 88 |

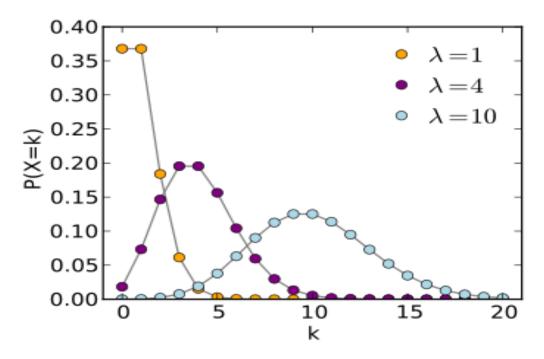

| 6.2  | A Poisson Distribution [34]                                                               | 89 |

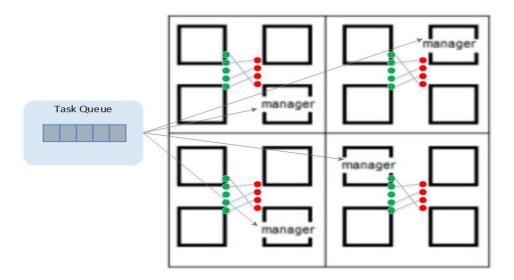

| 6.3  | Agent-based Market model for distributed mapping                                          | 89 |

# Chapter 1

# Background knowledge

1.1 Introduction 15

### 1.1 Introduction

According to Gordon Moore's prediction, the number of transistors in an integrated circuit doubles approximately every two years, leading to more complex systems. However, Dennard scaling suggests that power requirements are proportional to area for transistors. Combined with Moore's law, power density grows at about the same rate as transistor density, making integrated circuits unable to scale down in terms of technology at the same rate. In addition, architecture related modifications cause limited improvement and therefore single-core performance is limited. Despite these, processor chip computing power continues to grow by harnessing the additional processing power from additional processor cores (or CPUs), introducing the use of multicore processor chips [21].

The current trend in System on Chip (SoC) design is the shift from multicore processor chips to many-core [10]. This change towards many processor cores is not only a change in scale, but also a change in the kind of the processor chips.

In 2005, the industry started adopting multicore general purpose processors, which

Figure 1.1: Intel Microprocessors

marked the entrance into the multicore era. Since then, the number of cores in a single chip continues to grow, as it is illustrated in figure 1.1 [29]. Previously, systems used parallelism by putting multiple processors and organizing them in servers and supercomputers. Now, modern processors make every computing system able to use parallel computation. Embedded systems and general purpose systems begin to show signs of convergence, both in terms of software and hardware. The industry dictates increased functionality and at the same time, increased performance and responsiveness, encouraging the shift away from single core systems. Initially, mobile phones only featured basic functionalities with the focus on communication and therefore its hardware requirements were minimal. On the contrary, cutting edge mobile phones and more specifically smartphones use up to 8

cores (e.g. Samsung S5 featuring ARM-based Exynos 5 octa) and feature high definition cameras, hardware accelerators and multiple sensors. Their processing capabilities are equivalent to modern general purpose computing systems[31].

Adding multiple cores to a system adds raw processing power. However, this does not imply that the software makes good use of the processing power. Software needs to alleviate problems caused by the nature of many-core systems in order to successfully manage and coordinate the available resources towards creating an efficient system.

Software for a single-core system behaves in a way programmers can understand easily. Instructions are executed in the order that is defined, and if designed carefully, the program always gives a correct result. In great contrast, exploiting hardware parallelism (in the form of multiple cores) by concurrent programming can only be accomplished when the software is changed. The program has to be split in chunks of work that can be executed in parallel. Programmers accept the fact that they have to face programming for concurrency as well as to face difficult bugs related to communication and heterogeneous hardware component latency. This truly requires co-design of the hardware architecture and the programming approach.

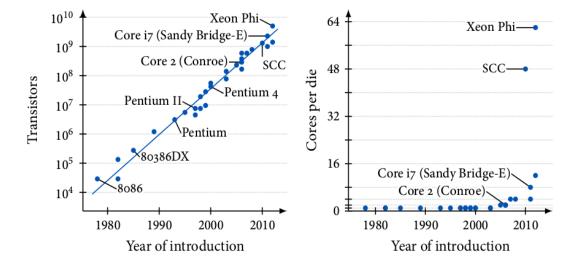

This complexity in multicore systems makes it difficult for the software to efficiently manage the additional requirements and constraints introduced by the hardware. In Figure 1.2 both hardware and software productivity are represented. In particular, the demand for software is currently doubling every 10 months, the capability of technology is currently doubling every 36 months, as well as the productivity of hardware and software design. Productivity of the hardware designers has been improved recently as systems can be created by integrating multiple cores. Thus, all the functionality is provided only with additional software. Software productivity and especially the one regarding hardware-dependent software, is growing at a much slower rate and doubles only every 5 years. The red arrow illustrates the magnitude of the new design gap including both hardware and software.

### 1.2 Many-core Systems

#### 1.2.1 Multiple cores

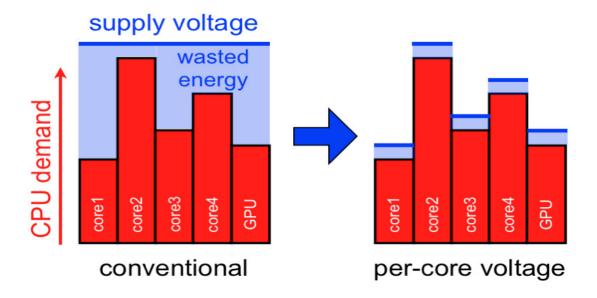

Multi-core processors can be categorised as homogeneous or as heterogenous. Most current general-purpose multi-core processors are homogeneous both in terms of ISA (instruction set architecture) and performance. Homogeneous systems can execute the same binaries and programs on any of their cores without causing any difference in functionality. Many modern multi-core architectures, however provide the capability for system software to dynamically scale the voltage and clock frequency for each core individually. This technique is most commonly referred to as DVFS (Dynamic Voltage and Frequency scaling) and is most often used in embedded processors for power management. The processor can

Figure 1.2: Productivity gap between hardware and software design [22]

regulate its voltage and frequency states accordingly in order to either save power or to temporarily increase single-thread performance.

In order for the cores to be indistinguishable at the software level, most of the homogeneous architectures use a shared global address space. The processes or threads can even migrate from one core to the other at run-time, but the cores are viewed as identical.

Unlike the homogeneous processors, multi-core systems which feature at least two different kinds of cores with possible difference in the instruction set architecture (ISA), functionality and performance, are called heterogeneous. Certain application domains that are limited by the efficiency and capability of general purpose processors can still support the design of custom architectures if they are driven by a large enough market. These conditions exist in domains such as computer graphics, signal processing and embedded computing where accelerators have been designed that offer significant performance and efficiency advantages over general purpose architectures [14]. A typical example of a heterogeneous multi-core architecture is the Cell BE architecture (co-developed by IBM, Sony and Toshiba), used in high performance computing applications, such as in gaming devices.

When it comes to programming architectures for parallel computation, a homogeneous architecture with shared global memory is significantly easier to program for than a heterogeneous architecture where the cores do not feature the same instruction set. However, when an application is partitioned into long lived threads with limited or regular communication it is efficient to have some partitions utilize the task-specific cores.

Regarding the core Microarchitecture, great differentiation can be observed. All modern processor cores are pipelined in order to improve on overall throughput by breaking down instruction decoding and instruction execution in stages. By using pipelined cores, instruction latency is the same or even increased. In addition, designs that aim at high-performance feature speculative dynamic instruction scheduling. These microarchitectural techniques increase the average number of instructions executed per clock cycle. Despite this fact, these tend to become of lower significance in modern multi-core architectures, as they offer limited instruction-level parallelism (ILP), tend to be both complicated and power-hungry and take up valuable silicon surface. As a matter of fact, new architectures such as Intel's Knights Corner, turn to simple single-issue in-order cores (Knights Corner cores also have powerful vector instructions in order to take up less silicon and reduce power consumption).

In order to compensate for limited instruction level parallelism added to the most advanced cores is simultaneous multithreading (SMT). This hardware technique allows better utilization of hardware resources where a multi-issue pipeline can select instructions from two or more threads. For applications with abundant ILP, single-thread performance is high, while with reduced ILP, thread-level parallelism can be utilized. Simultaneous multi-threading is adopted as it introduced only a little additional area and power consumption [33].

#### 1.2.2 Interconnection Networks

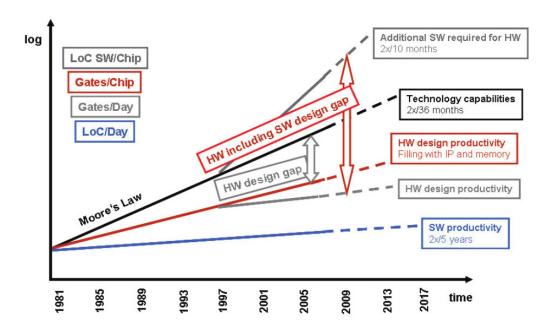

In a multi-core setting, there is need to have mechanisms for cores to efficiently communicate with each other. An early approach to achieve inter-core communication in a multicore chip has been through a common shared bus. In order to overstress the bus with memory and I/O traffic, the design includes local cache memories, typically structured in one or two levels between the processor and the bus. The shared bus also enables the implementation of cache coherence protocols (cores are able to broadcast the shared memory operations in the communication medium in their respective order).

More recent designs have abandoned the shared bus as a communication medium as it is not an efficient solution in terms of latency and bandwidth. One reason is that the shared bus has long electrical wires that create delays. Additionally, all the cores of the system are connected to the shared bus, which does not enable an individual core to have all the bandwidth of the bus allocated for itself.

Other popular designs use a crossbar interconnect. The crossbar connects processor modules that include a two level cache hierarchy with the last level cache and memory interfaces. Emerging designs focus on bandwidth and power consumption improvements and include ring busses and switched on chip networks.

#### **1.2.3** Memory

A key target of multi-core systems is to enable parallelization of the software. Therefore, processing cores need an efficient way to communicate with other. While the actual communication is achieved over the interconnection network, cores can store data in shared memory locations and access them afterwards.

Figure 1.3: Interconnect Architectures [33]

Shared memory is not scalable to thousands of nodes and for this reason it has not been used in high performance computing. Clusters most often use message passing to achieve inter-node communication. Their nodes however, implement a shared address space. For all these reasons, shared memory has been introduced in all modern general-purpose multi-core processors. In addition, memory systems that implement a shared address space need to have cache-coherence. Cache coherence allows the cores to have local copies of its frequently accessed data in private caches, but also a globally consistent view of the values written to each memory location when multiple cores update shared resources. Many memory hierarchies have been proposed, based on different cache structures. The memory system can have only shared or only private caches or both and the architectures can be flat or hierarchical. Figure 1.5 displays different cache architectures that have the characteristics mentioned above.

#### 1.2.4 Scalability Considerations for Many-Core Processors

To take full advantage of a many-core system, a high percentage of core utilization is required. In order to facilitate this, a large number of tasks is required and more specifically, tasks that are parallel. Because of this, it is important to coordinate the

Figure 1.4: Cache Memory Architectures [33]

cores and robust synchronization mechanisms need to be implemented. However, it is very difficult to achieve hardware-only synchronization mechanisms and the more efficient solutions rely mostly on the software with some architectural support.

Most of the synchronization implementations do not scale well as the number of core increases, as the synchronization overhead becomes significant. In order to implement mutexes, the cores access shared memory and this requires some inter-core communication. As the number of cores increases, the overhead introduced by the shared memory accesses becomes significant. A distributed lock algorithm that scales almost linearly both in terms of system performance and in hardware cost is presented in [29]. The implementation uses local memories and message passing and is only bounded by memory bandwidth.

Additionally, as the number of cores increases, the cost of maintaining a coherent memory increases as well, as delay and latency incur by accessing frequently modified memory areas.

Memory bandwidth is also going to become a major concern as the amount of data required by the cores rises. The total amount of data needed is equivalent to the necessary memory bandwidth. If the number of transistors is going to increase with the existing pace, memory bandwidth will require the same trend in order to cope with the demand. However, this has not yet been achieved (Figure 1.5).

Figure 1.5: Processor and memory performance gap [23]

#### 1.2.5 Future Trends

As multi-core processors evolve and the needs for the number of cores increase, issues regarding power consumption, synchronization and memory arise and require attention. Therefore, some innovative approaches have been given as possible solutions to the problems that cause bottlenecks to the scalability of many-core systems [33].

One big challenge of many-core systems is to find alternatives for the on-chip interconnect. As the number of cores is on the rise, the interconnect becomes the bottleneck, as it is limiting the system's throughput and is responsible for most of the system's power consumption. Regarding the types of on-chip interconnect illustrated in Figure 1.4, the Mesh interconnect performs better, as the wiring is shorter.

A concept that may introduce improve the on-chip interconnect in the areas of power consumption, latency and delay is 3D stacking. In the case of a 2D  $32 \times 32$  mesh interconnect of 1024 cores, the number of hops reaching across the chip would be 62, making 31 steps both horizontally and vertically. However, if the cores were placed in a 4 layer stack of  $256\ 16 \times 16$  mesh, then this number would reduce to 33, as the required cost would be 3 across the levels and 30 inside the same level. Similarly, memory can be packaged on top the processor cores, enabling higher speed interconnects.

Another approach is via the optical on-chip networks. These can offer lower power consumption and occupy less silicon area. The basic underlying principle is that a single optical waveguide can carry multiple signals on different wavelengths simultaneously, while having minimal loss across the transmission line. In order to reduce the synchronization overhead, the concept of transactional memory has been introduced, however it has not

Figure 1.6: Scheme of 3D-IC stack and vertical interconnection [16]

Figure 1.7: 3D silicon processor chip featuring on-chip nanophotonic network [19]

beed adopted by the industry yet. Transactional memory enables a thread to progress by performing its own updates until its own transactions are over. These changes are visible only to itself, but after completion the memory location is checked for concurrent accesses. If only an individual access has been performed, all changes are atomically committed and

become global. Otherwise, the thread's transactions are rolled back and re-executed. Transaction memory enables concurrent updating of shared memory locations but only works well in cases where the probability of contention is very low.

#### 1.2.6 Examples of Many-Core Systems

#### Intel Xeon Phi Coprocessor

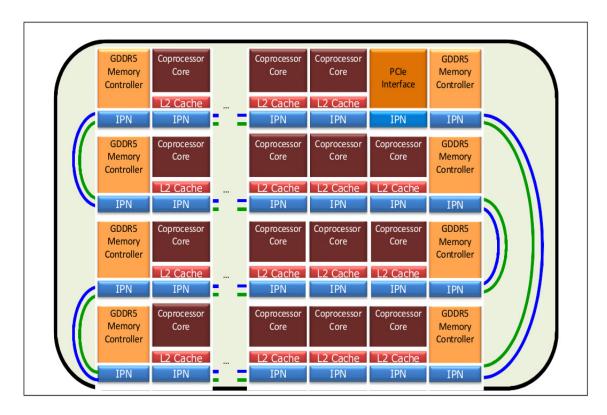

Figure 1.8: The Manycore Integrated Core (MIC) architecture on Xeon Phi [11]

Intel announced in 2012 a new processor product family named Intel Xeon Phi. This new processor features the Many Integrated Core(MIC) architecture. The cores of this architecture are Pentium based (version P54C) and use the x86 instruction set. The MIC architecture targets applications that require highly parallel processing in order to utilize a high degree of parallelism in its simple Pentium based processor cores.

In Figure 1.8 the general structure of the Xeon Phi coprocessor architecture is displayed. The cores, PCIe Interface logic and memory controllers are connected via a ring Interconnect, the Interprocessor Network (IPN) ring.

Regarding L2 caches, these are viewed as distributed across the cores, but can also be thought as a fully coherent cache with a total size equal to the sum of those attached to the cores. Data can be copied to individual cores to provide the fastest possible local access, but can also be found as a single copy for all cores to provide maximum cache capacity.

The Xeon Phi coprocessor can support up to 61 cores with a total of 30.5 MB L2 cache

and 8 memory controllers with 2 GDDR5 channels each.

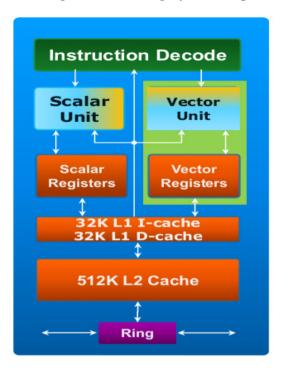

The core architecture of the processor is displayed in Figure 1.9. The scalar unit is

Figure 1.9: The Xeon Phi Coprocessor core [6]

based on the Pentium architecture, but Xeon Phi also has a vector unit implemented. L1 and L2 caches are fully-coherent. Another interesting feature is node Power and Thermal Management, which includes power capping support.

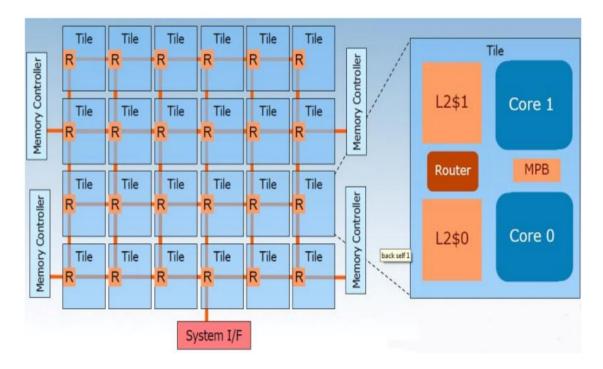

#### Intel SCC platform

The Intel SCC platform is a x86 48-core processor which provides a run-time and programming environment. In terms of architecture, the SCC platform features 24 tiles, each consisting of two blocks featuring a P54C core (second generation Intel Pentium processor), 16KB instruction and data L1 caches as well as a unified 256KB L2 cache. In addition, the platform features a A Mesh Interface Unit(MIU) allowing the mesh and the interface to operate at different frequencies, a 16KB Message Passing Buffer and two test-and-set registers. The architecture is illustrated in Figure 1.10.

Each tile also includes a router, which enables it to work with the Mesh Interface Unit (MIU) to integrate the tiles into a mesh. The MIU partitions data into packets to transmit them onto the mesh and puts together data received from the mesh using a round-robin scheme to arbitrate between the two cores on the tile. There is also a great number of off-chip memory which ranges from 16 to 64 GB of DDR3 RAM, controller by four memory controllers. Additionally, a router is connected to an off-package FPGA to translate the mesh protocol into the PCI express protocol, allowing the chip to interact with a PC serving as a management console.

Figure 1.10: Scematic of the Intel SCC platform architecture [30]

On each tile, a message passing buffer (MPB) is included, which provides a fast, on-die shared SRAM, as opposed to the bulk memory accessed through four DDR3 channels. This message passing buffer is 16KB in each tile. Its memory is shared among all the cores on the chip. With 24 tiles, the SCC provides 384KB of message passing buffer. When a message-passing program sends a message from one core to another, internally it is passing the data through the message passing buffers on the chip [27],[30].

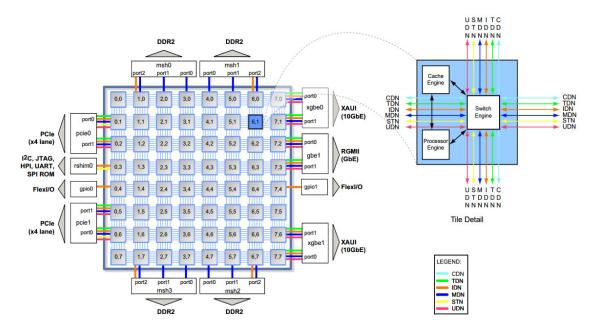

#### Tilera Tile Architecture

Tilera has introduced a multicore architecture that is based on the MIPS ISA and can currently scale up to 72 cores. The Tile Architecture is based on building a two-dimensional array of processor elements (given the name tiles) with a two-dimensional mesh network interconnect. This scalable architecture manages to provide low latency inter-tile communication and high bandwidth. All the tiles in the array are identical and include on-chip routers for data communication. As the tiles communicate with each other via point-to-point connections inside the Mesh interconnect, the tile array is energy efficient and offers significant scalability.

Each tile is a computing system that can support an entire Operating System. The Tile includes a 32-bit integer Processor Engine, a Cache Engine and a Switch Engine, which is the controller that coordinates all components of the tile into a powerful computing element. The Processor engine is a three-way VLIW processor that is capable of executing up to three operations per cycle and provides protection, support for memory management and Operating Systems. Moreover, the Cache Engine includes the TLBs, caches and

cache sequencers of the tile, as well as a DMA engine that coordinates data communication among tiles and between tiles and the external memory. Finally, the Switch Engine implements six different networks. Dynamic networks on the Processor facilitate the routing of packet-based data among tiles, tile caches, external memory and I/O contollers.

Figure 1.11 illustrates the TILEPro64 Processor organized in an eight by eight tile array [12].

Figure 1.11: Scematic of the Tile Processor Architecture [12]

### 1.3 Resource Management

Traditionally, processors consisted of one cores or a small set of cores. For these types of systems, the problem of scheduling the tasks was responsible for resource allocation. However, as we move towards Many-Core processors resource allocation has become more complex and involves taking the core position into account. This process that incorporates the spatial aspect of the cores, is called mapping.

#### 1.3.1 Scheduling

The history behind the evolution of schedulers as well as the state of the art is presented in [36]. Initially, schedulers were responsible for the execution time distribution of the processor among threads. Over time, the schedulers became responsible of establishing fairness, showing respect to priority, enabling real-time applications and of ensuring that all threads make progress. However, schedulers for single-core processors have reached a point, where there was not enough room for optimizations.

As processors evolved towards having multiple cores, schedulers needed to space share. In

other words, the Operating System scheduler needed to decide, to which core each thread -given an execution time interval- should be assigned. In multi-core processors, cores share resources that include caches and memory controllers. As a result, applications can display significant decrease in performance if they share resources with processes on neighboring cores.

To compensate for this performance loss, contention-aware schedulers have been introduced. This type of scheduler identify threads that share a lot of resources and threads that share minimal resources. In the sequence, it manages to schedule the threads with respect to minimizing the loss in performance due to shared resource contention.

Whereas threads from different applications might experience performance loss due to resource-sharing, threads of the same application might benefit for the same reason. Datasharing threads might be more productive if the share the last level cache. Improved performance is realized also by sharing the same prefetching mechanisms.

As processors grow in number and the on-chip resources become abundant, scheduling also needs to evolve in order to cope with the changes in hardware. Traditional schedulers have managed individual threads. However, the concept of application containers has been introduced. Following the need for increased parallelism, applications will be running on top of runtimes that will have their own thread or task schedulers. In this way, a modular and more scalable approach will be realized, one similar to the parallel programming frameworks use already by having their own thread scheduling.

A similar approach to the management of application containers has been used in hypervisors, where virtual machines as regarded as individual entities. Memory and CPU are assigned to them in a fixed manner and the virtual machine itself is responsible for the resource management. An example of resource management for application containers is the Tesselation Manycore OS [9], in which the Cell Model is proposed as the basis for scheduling. A Cell is a container for parallel applications that provides guaranteed access to resources, a behavior similar to the one hypervisors provide for their virtual machines discussed previously. Tesselation allocates resources to containers as space-time quantities, such as "4 processors for 10% of the time" or "2 GB/sec of bandwidth". Although Cells may be time-multiplexed, hardware thread contexts and resources are gang-scheduled such that Cells are unaware of this multiplexing. Resources allocated to a Cell are exclusively managed by that Cell until Tesselation requests the resources to be revoked. Once the Cell is mapped, a user-level scheduler is responsible for resource management within the Cell. Finally, Cells can communicate with each other via special channels.

#### 1.3.2 The mapping problem

An overview of the mapping problem as well as a taxonomy of the different mapping classes is presented in [30]. The concept of Many-core SoC introduces new challenges in allocating resources amongst the cores. To date, resource allocation was limited in scheduling the tasks in one core or a very small set of cores. In Many-core systems, re-

Figure 1.12: Inter-cell communication [9]

source allocation has a spatial aspect as well. An application comprises of tasks being executed in parallel and every task has to be assigned to a core. The choice of core has to take into account its position as well. This is the reason why we refer to this process as mapping. The idea of resource mapping is illustrated in Figure 1.13.

Calculating a cost efficient mapping for a given application in a short amount of time

Figure 1.13: The mapping/routing problem [20]

is crucial. Some common goals are to maximize performance, minimize distance between tasks or minimize energy consumption in case of heterogeneous platform. Since the mapping process is an intermediate step between the request for an application to start and the actual initialization of the application, the process must be as fast as possible. As always, there is a variety of design decisions to be made as far as the characteristics of the mapping are concerned. The most important are presented in the following sections.

#### Design-time vs Run-time mapping

In the case of Design-time mapping, the nodes an application can run on are designated before run-time. This designation cannot be altered during run-time. Apparently, this technique can be employed only when small amount of application can be run on such a processor and only for specific scenarios, which is not very common in modern systems. The alternative of design-time mapping is the run-time one, in which resources are allocated dynamically as applications enter and exit the system, providing the necessary flexibility for the platform to function properly. An interesting fact is that run-time mapping is the only way to tackle the unpredictability of the incoming applications. Another characteristic is that run-time mapping manages to adapt to the available resources. Those vary over time, due to applications running simultaneously. Run-time information can be incorporated to further reduce the cost of running an application. In addition, it enables unforeseeable upgrades after first product release time, e.g. new application and new or changing standards as well as to avoid defective parts of a SoC. Larger chips mean lower yield. The yield can be improved when the mapping algorithm is able to avoid faulty parts of the chip. Also, aging can lead to faulty parts that are unforeseeable at design-time. Finally, it can be used with reconfigurable hardware where the type of available processing elements can vary over time.

A downside of run-time mapping is the extra overhead it adds to the execution of an application, since it is executed between the request from the OS and the actual execution of the tasks. Hence, it is crucial that the mapping is calculated fast, so that it doesn't overburden the system.

#### Centralized vs Distributed mapping

Apart from defining the moment (run-time or design-time) the mapping occurs one must also define on which tiles the mapping algorithm will be executed. In this case the available design choices are to perform the mapping calculations either on a distributed or centralized manner [20]. Centralized mapping utilizes one or a small set of cores, Centralized Managers (CM), to perform the mapping for every application that arrives. These cores are burdened with the responsibility to calculate the mapping for the whole system. This mapping scheme can cause some problems [17].

Monitoring traffic is increased in volume, as the Centralized Manager needs to collect data from the whole chip during the mapping -performed at run-time-, which causes traffic on the wires, possibly stalling the execution of already running tasks. In addition, the computational cost to calculate the mapping for the whole chip at once is high. Another drawback is that it is prone to failure. If the Centralized Manager fails for some reason, the mapping can't be performed at all. Moreover, the Centralized Manager becomes a point of hot-spot as every tile sends the status of the Processing element to it. This increases the chance of bottleneck issues around the manager. Consequently, because of all these reasons scalability issues arise. As Many-core chip grow in size and more Processing

Elements will be added, the computational effort of mapping and the traffic it will create will increase exponentially, thus rendering the computation very expensive and the scheme ineffective.

On the distributed mapping scheme, the effort of the computation is distributed, as the name suggests, on several tiles across the chip, Local Managers (LM) as presented in [32], and they may even change from one mapping to the next. In this way, the problems of the Centralized mapping are solved.

First, monitoring traffic is decreased in volume, as the Processing Elements only need to send the data to their closest Local Manager, and this way they travel less on the chip. When mapping decisions have to be made involving different regions, the communication is limited only between Local Managers. In addition, Local Managers only need to perform the mapping computation for the area of the chip they are responsible for, or for some designated tiles. This way, the computation demanding problem is divided in less demanding ones. Apart from these, there are no issues of single point of failure or hot-spots, since the smaller portions of the computation can be performed on any tile. Finally, it scales very well with larger number of cores, since all that is needed is some more light-weight Local Managers, whose individual computation effort isn't increased.

With distributed mapping, two major downsides occur. First, there is the need for synchronization between the managers, so as to achieve a well-balanced and fair mapping. Secondly, it is reasonable that a centralized approach can provide a better mapping considering the fact that it has an overall view of what is going on in the platform. However, we can achieve results comparable to the optimum mapping with the distributed approach and taking into account its aforementioned advantages, distributed resource management seems to be the only option [4]. The following Figure (Figure 1.14) illustrates the principles of centralized and distributed mapping.

Figure 1.14: Processor tiles examples using centralized and distributed mapping [30]

#### 1.4 Economic principles

One of the fundamental models used in economics is the supply and demand model for a competitive market. A competitive market is one that has many buyers and sellers, none of which has the ability to individually influence the price of the market.

In addition, a market is defined in terms of a specific group of individuals who would potentially trade with each other. Markets can both have very broad or very narrow scope (e.g. internationally vs locally in a single community).

The basic components of the model (demand and supply curves, the market equilibrium and the factors that cause these to change) are presented below [18].

#### Demand

The definition for Demand is the following:

An individual's quantity demanded for a good specifies the amount an individual would choose to buy of a good over some time period given a particular price that must be paid for the good and all other constraints on the household (e.g., income).

The demanded quantity reflects a choice individuals make dependent on many factors and is also hypothetical and therefore independent of the availability of the good at a certain price. Additionally, the quantity demanded causes the price to stress.

The law that drives the behavior of the demand mentions that when the price of a good rises, and everything else remains the same, the quantity of the good demanded will fall. This law indicates that the demand curve has negative slope.

A graphical representation of the demand curve can be found on Figure 1.15. An approximation of that curve can be represented with a line with negative slope and positive offset.

There are several factors that can affect the demand. On the demand curve we can see a point  $(P_1,Q_1)$ . Factors that can shift that point on the demand curve are changes in wealth, in the number of consumers, in the prices of the good or related goods, in customer tastes as well as in customer (price) expectations. For example, if an increase in wealth is observed, an increase in the quantity demanded of the good at any given price would be expected.

#### 1.4.1 **Supply**

The definition for Supply is the following:

An individual's quantity supplied of a good is the specific amount its managers would choose to sell over some time period, given a particular price for the good and all other constraints on the firm.

The supplied quantity reflects a choice firms make regarding the quantity they would be willing to sell at a given price. The supplied quantity also hypothetical and therefore independent of the customers' willingness to pay for the supplied quantity a the given price. Similar to the demanded quantity, the supplied quantity causes the price to stress.

Figure 1.15: Demand Curve

The law that drives the behavior of the supply mentions that when the price of a good rises, and everything else remains the same, the quantity of the good supplied will increase. This law indicates that the supply curve has positive slope.

A graphical representation of the supply curve can be found on Figure 1.16. An approximation of that curve can be represented with a line with positive slope and positive offset.

There are several factors that can affect the supply. On the supply curve we can see a point  $(P_1,Q_1)$ . Factors that can shift that point on the supply curve are changes in the number of producers, changes in the prices of the good or related goods, changes in technology as well as changes in (price) expectations. For example, if an increase in the number of producers is observed, this will lead to an increase in supply. Then, the supply curve shifts rightwards.

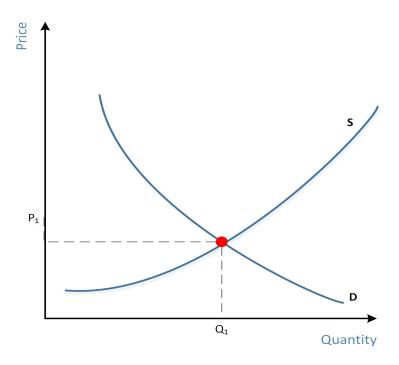

#### 1.4.2 Market equilibrium

One principle that is governing markets is that they tend to move towards an equilibrium. Changes can occur, but eventually the effects of the change will become partially compensated and the market will converge towards an equilibrium.

Competitive markets are in equilibrium when price has moved to a point where the quantity of the good demanded is equal to the quantity of the good supplied. This price at which we have an equilibrium point is called market-clearing price or equilibrium price and the quantity equilibrium quantity.

In Figure 1.17 we can see an equilibrium graphically. The equilibrium price and quantities in the graph indicate where the market will naturally settle down to given the current sup-

Figure 1.16: Supply Curve

ply and demand curves. If any of the quantities change, this can cause shifts in demand and shifts in supply. These changes have an impact on the equilibrium point, shifting it either across the demand or across the supply curve.

Figure 1.17: Market equilibrium

#### 1.4.3 Auctions

An auction is defined as a process of buying and selling goods or services by offering them for bid. After bids are taken the item is sold to the highest bidder.

An overview of auctions and the underlying theory can be found in [26]. An auction format is a mechanism to allocate resources among a group of bidders. The auction model consists of the description of the potential bidders, the set of possible resource allocations (describing the number of goods of each type, whether the goods are divisible, and whether there are legal or other restrictions on how the goods may be allocated) as well as the values of various resource allocations to each participant. The mechanism receives all information in the form of bids, as potential buyers express their willingness to pay in that way. Additionally, the auction outcome, which includes the highest bidder and the amount of the bid (market clearing price) is determined on the basis of the received information. Another characteristic of auctions is anonymity, which indicates that the identity of the bidder does not affect the outcome of the auction, both in terms of the amount paid and who the winner is. Some common forms of auction are the following:

#### - The English Auction

The English auction is the open ascending price auction. This type of auction is carried through by an auctioneer who begins with a low initial price and raises it, typically in small increments, as long as there are at least two interested bidders. The auction stops when there is only one interested bidder.

#### - The Dutch Auction

The Dutch auction is the open descending price auction. The auctioneer begins at a high price so that no bidder would be interested in buying the object at that price. The price is progressively lowered until a bidder expresses interest.

# - The Sealed-Bid First-Price Auction In this auction type, bidders conceal their bids and submit them. The person submitting the highest bid wins the object and pays what he bid.

- The Sealed-Bid Second-Price Auction

Bidders conceal their bids and submit them. The person that submits the highest

bid wins the object but pays the amount of the second highest bid.

At the time of the auction, the bidders have knowledge or no knowledge regarding the price of the object. If each bidder knows the value of the object to himself, then the auction is called one of private values. However, most often the worth of the object is unknown at the time of the auction to the bidder himself. This type is called of independent values, since each of the bidders can only make an independent and personal valuation of the object. To form this valuation, bidders sometimes use information, such as an expert's estimate to have an approximate of the true value and adjust their bid accordingly.

### Chapter 2

### Related Work

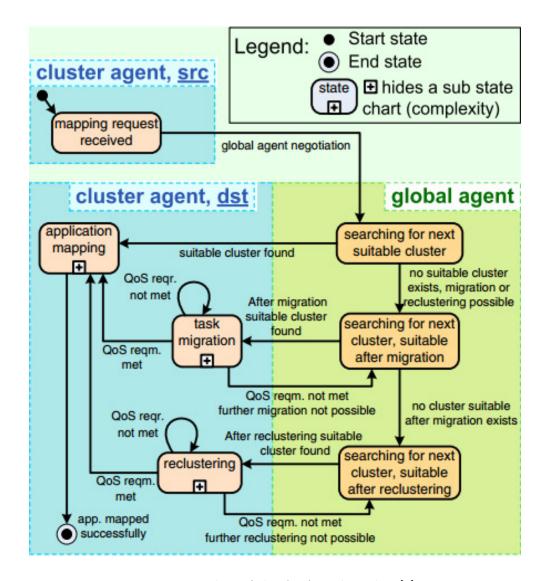

#### 2.1 ADAM: Run-time Agent-based Distributed Application Mapping for on-chip Communication [2]

Figure 2.1: Flow of the ADAM algorithm [2]

In this work, the authors present an agent-based distributed resource management algorithm for self-adaptive heterogeneous MPSoCs. The negotiation of cores takes place inside a virtual cluster. Such a cluster is an area of the platform that can be creates, resized and destroyed at run-time. Additionally, an agent is a computational entity acting on behalf of others. Its main characteristics are:

- 1. It is a small task close to the system.

- 2. It performs resource management.

- 3. It must be executable on any PE.

- 4. It must be migratable and recoverable.

5. It may be destroyed upon the destruction of the cluster.

A cluster agent is CA, is an agent responsible for mapping operations inside a cluster. A global agent GA is responsible for storing global information such as usage of communication and computation resources for each cluster and this information is used for selection and re- organization of the clusters. An overview of the mapping scheme is presented in Figure 2.1.

When a new mapping request is received from any tile, the Cluster Agent of the tile's

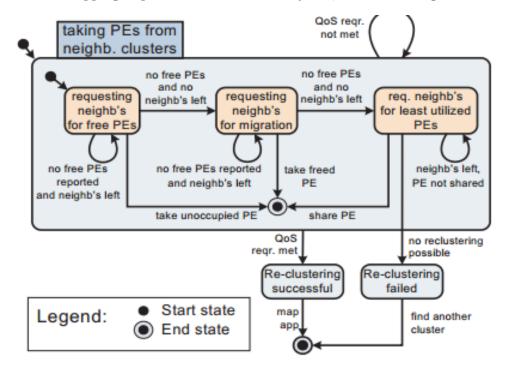

Figure 2.2: The re-clustering process of the ADAM algorithm. [2]

cluster communicates with the Global Agent, indicating the request. At this point, the Global Agent performs the Suitable Cluster Negotiation Algorithm, which finds a cluster capable to fit the whole application. The Suitable Cluster Negotiation Algorithm checks if there are enough free tiles in every PE type and resource requirement class for all the tasks in the application.

In case the algorithm fails to find a suitable cluster then a task migration is employed is the most suitable cluster. The point of this task migration is to rearrange the tasks within a cluster in a way that the mapping of the new application will be feasible in the cluster. Still there is a probability that this will fail to produce an appropriate mapping as well. Then the technique of re-clustering is employed. Clusters can be changed in shape, resulting to the probable creation and destruction of some them. This process can benefit running applications since resources can be redistributed in a better way. However, it is an elaborate process that takes into account many parameters of the applications such as the requested energy and memory of the application. The flow of the reclustering algorith is presented in Figure 2.2.

After a cluster that can host the application has been found, that cluster's agent is responsible to perform the Run-time Mapping algorithm to appoint every task to a tile to be executed on. The best tile for every task is calculated using a heuristics, checking the tile's position in the cluster (tiles near the center are preferred), the volume of communication on the tile before and after the mapping and the resource requirements for the task to run on any tile.

# 2.2 A Divide and Conquer based Distributed Run-time Mapping Methodology for Many-Core platforms [3]

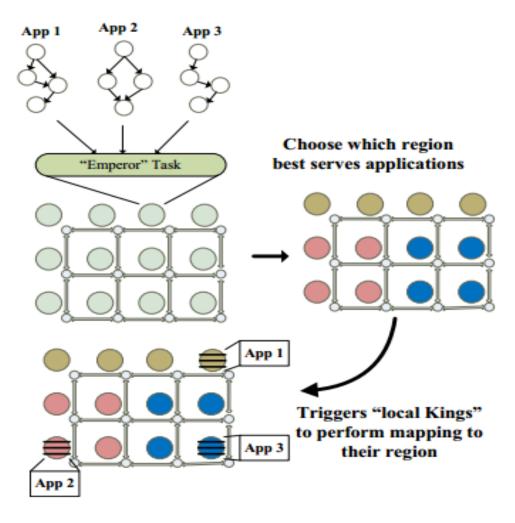

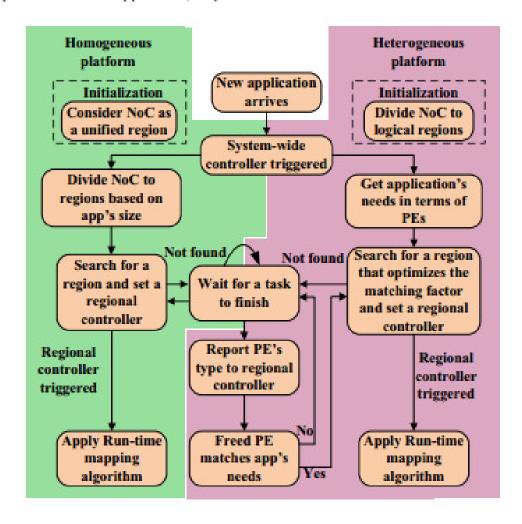

In this paper a distributed run-time resource management framework is presented for both homogeneous and heterogeneous platforms. The main idea of the proposed framework is illustrated in Figure 2.3.

The mapping is carried out in a distributed manner. In order to achieve that, the platform

Figure 2.3: Main idea of the run-time manager of [3].

is partitioned in regions. A region is a subset of the set of all the tiles on the NoC with no

fixed boundaries, and can be reshaped, created or abolished when necessary. The manner in which the partitioning is performed is different in homogeneous and heterogeneous platforms. The overall flow of the resource management algorithm for both homogeneous and heterogeneous platforms is presented in Figure 2.4.

Upon arrival of an application, a system-wide controller is invoked. This task is called

Figure 2.4: Flow of the run-time resource management of [3].

an "Emperor" task. It is a light-weight in terms of resource demands, it can be executed on any type of processing element of the platform and it is responsible for:

- 1. getting the requirements of the incoming application

- 2. selecting the appropriate region to map the application on

- 3. triggering other cores in the region to perform the run-time mapping algorithm. These regional controllers are referred to as "Local Kings".

In addition to the System-Wide Controller, in every region there is a specific node called a Regional Controller (RC). These tiles are responsible for any action involving the mapping

in their respective region. Their code can also be executed on any processing element of the platform. A Regional Controller is responsible for:

- Computing the mapping for the region for which the controller is responsible for.

- Collecting data for the region.

- Communicating and exchanging data with the System-Wide Controller.

The System-Wide controller is responsible for selecting the region on which the application will be mapped on. After that it is responsibility of the Regional Controller to calculate the actual mapping and inform the System-Wide controller. As far as the mapping is concerned, the goal of the algorithm is to compute a fast and efficient mapping that minimizes the energy consumption from the execution of an application. After an initial mapping has been performed an iterative application node swapping process is employed in order to further reduce the total communication cost.

Comparing the RTM algorithm for heterogeneous and homogeneous NoCs its major difference is the way the regions are initialized. On homogeneous platforms during the initialization no regions exist, and are created for each new application, and abolished when the execution finishes its execution. On the other hand on heterogeneous platforms, the NoC is partitioned in regions from the very beginning, with the selection of number and size of the regions left on the designer's judgment and Regional Controllers are appointed on these regions right away. Regions can be reshaped or created to better accommodate new applications, but they can only be abolished if they are an empty set.

Finally, the concept of matching factor is introduced. This designer specified percentage value dictates how strict the mapping is as far as the preferred processing elements of an application are concerned. An MF of 100% dictates that the application can accept only its most preferred processing element, while an MF of 0% dictates that an application can accept any of the processing elements it is able to work on.

#### 2.3 DistRM: Distributed Resource Management for On-Chip Many-Core Systems [25]

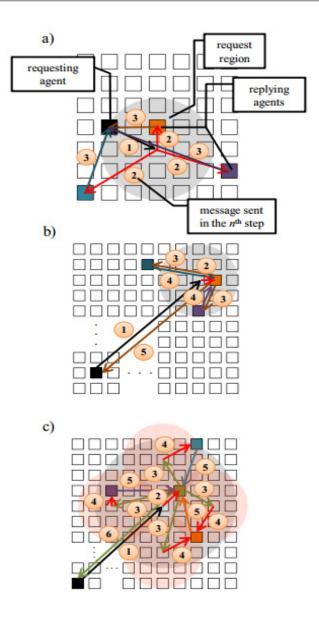

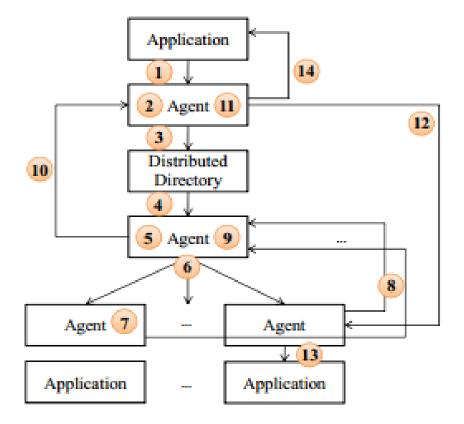

The authors of [25] present a distributed run-time resource management framework for malleable applications. As the name of the work suggests, the framework is called DistRM. The application model used for the examination of the proposed framework is the one proposed by Downey [15]. The framework is distributed in the sense that different cores, dispersed around the grid of cores, are responsible for performing mapping decisions and managing applications. These cores are called agents.

To manage regional information in a distributed way, the authors suggest that there is a directory service distributed to the entire platform. This directory service enables the agents to communicate with other agents without the need of broadcast communication. All available cores are split into evenly distributed clusters and each cluster contains one

Figure 2.5: Communication between agents for a) local and b) distant target regions; c) a display the divide-and-conquer behavior for larger target regions [25].

directory service running on one of the cores. The agents register themselves at the directories corresponding to the cores occupied by the own application.

When a new application arrives on the system a randomly chosen core is triggered to initiate its agent. This is a means of load balancing without the need for global system state knowledge. This core acts as a seed for searching resources and there is a probability that this core will not be chosen for the application. The agent determines the cores the application will eventually run on. The agent searches in randomly chosen areas on the system which are gradually moving away from the core if no suitable core for the application is found. When such a request has to be made in a region further from a specific threshold, then this is consider a far request and the core in the center of the far region is delegated to discover a far request manager. It utilizes the knowledge of the

distributed directory service and forwards the request to the agent with most cores in the desired area. Figure 2.5 illustrates the interplay of the resource management agents and applications. The figure shows that an agent can communicate with all other agent for

Figure 2.6: Interaction of components of the DistRM algorithm [25].

the bargaining of cores to take place. A core is offered to the requesting agent if its gain in speedup is greater than the loss in speedup of the agent offering it. To avoid constant trades of cores between two agents, a core trade takes place only if the gain of the receiver is significantly bigger compared to the loss of the offering agent. In any case of a core offer, the offering agent has to receive a reply dictating if its offer is accepted or not. The agents also communicate with the cores holding the regional information and with the cores of their application in order to reconfigure and resize it.

The unallocated cores of the platform are handled by a special category of agents called the idle ones. These agents handle cores when the platform is initialized or when an application has finished its execution and there is no need for its agent to exist anymore. They are located at fixed positions on the platform and form a regular grid distributed all over the system. When another agent asks an idle agent for a core, the latter always offers one provided that it handles at least one.

Finally the concept of self-optimization of an application is introduced. After an agent has discovered an initial set of cores for its application, it requests more cores in order to increase the speedup of the application. At some point at run-time, an agent sends request

for cores to its nearby regions. This idea helps to optimize the mapping of application over time. To ensure that requesting additional resources does not happen too often, the delay between two self-optimization processes is doubled after the completion of one.

# 2.4 A taxonomy of market-based resource management systems for utility-driven cluster computing [35]

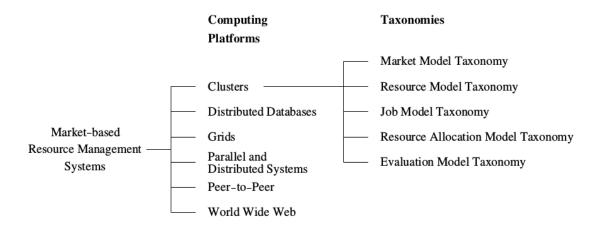

The aim of this paper is to develop a taxonomy that characterizes and classifies how market-based Resource Management Systems (RMS) can support utility-driven cluster computing in practice. A categorization of market-based RMSs is illustrated in Figure 2.7.

In utility-driven cluster computing, consumers have different requirements and needs

Figure 2.7: Classification of market-based RMSs [35].

for various jobs and thus specify their requirements and preferences for each respective job using Quality of Service (QoS) parameters during job submission to the cluster RMS. Market-based cluster RMSs need to support three requirements in order to enable utility-driven cluster computing:

- 1. Provide users with a means of generating their QoS needs and valuations.

- 2. Employ policies to create a translation of the valuations into resource allocations.

- Have mechanisms that enforce the resource allocations in order to achieve each individual user's perceived value or utility.

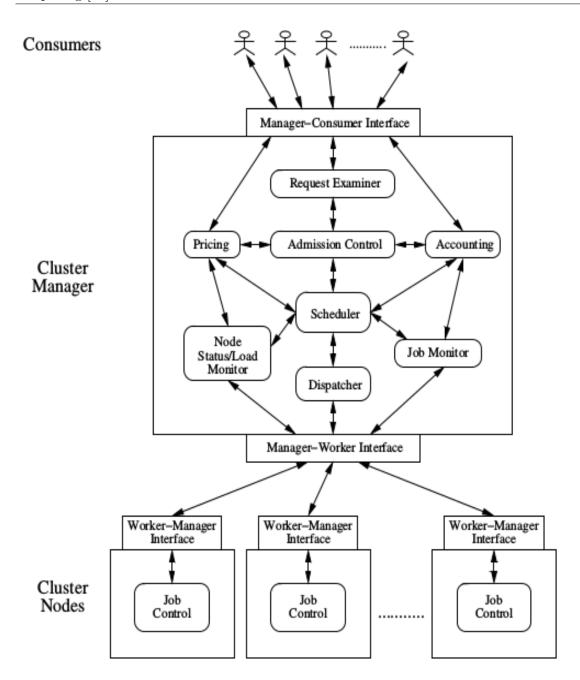

In Figure 2.8 an abstract model for the market-based cluster RMS is displayed. Its purpose is to identify generic components that are essential in a practical market-based cluster RMS and outline the interactions between these components. Thus, the abstract model can be used to study how existing cluster RMS architectures can be leveraged and extended to incorporate market-based mechanisms to support utility-driven cluster computing in

Figure 2.8: Abstract model for market-based cluster RMSs [35].

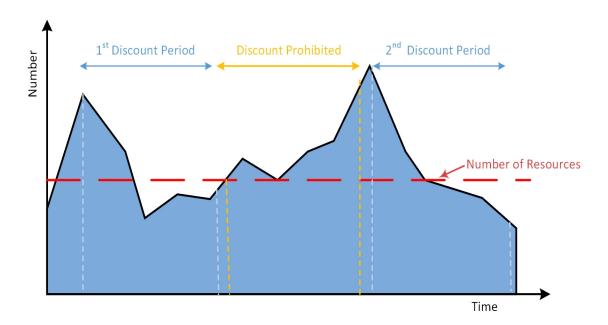

practice. The work in [35] also describes the models we will use and develop in chapter 3. It provides the economic models that establish how resources are allocated in a market-driven computing environment. In the commodity market model, producers specify prices and consumers pay for the amount of resources they consume. The pricing of resources can be determined using various parameters, such as usage time and usage quantity. In addition, the Posted Price model operates similarly to the commodity market with the difference that special offers are advertised openly so that consumers are aware of discounted prices and can thus utilize the offers. Finally, the auction model describes a way to allow multiple

consumers to negotiate with a single producer by submitting bids through an auctioneer. The auctioneer acts as the coordinator and sets the rules of the auction. Negotiation continues until a single clearing price is reached and accepted or rejected by the producer.

# 2.5 Economic models for resource management and scheduling in Grid computing [8]

#### 2.6 Motivation

As reliability becomes a more important factor in Many-core platforms, there is a need to manage the workload at run-time. By managing resources with reliability-aware methods, significant steps can be made towards prolonging the lifetime of Many-Core processors. Market-based resource management techniques have been developed in related work with the application field reaching to distributed systems, clusters and to the cloud. Our objectives regarding this diploma thesis are to propose models that will be evaluated with respect to reliability and to develop a resource management framework for Many-Core on-chip systems that will support these models under market principles. Besides that, the developed framework will provide a solid basis for further development in run-time resource management for Many-Core.

### Chapter 3

### Proposed Methodology

3.1 Introduction 49

#### 3.1 Introduction

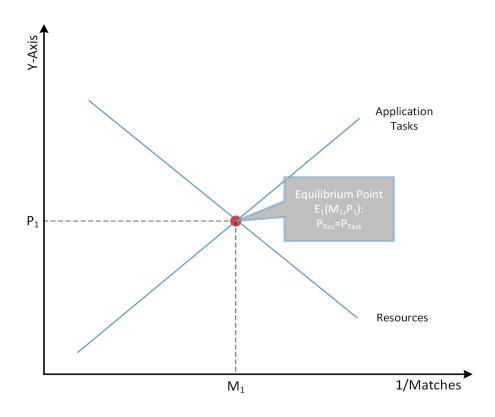

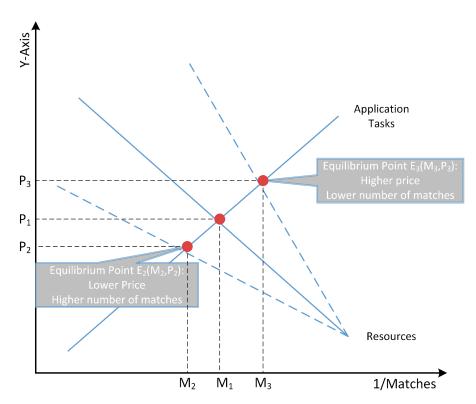

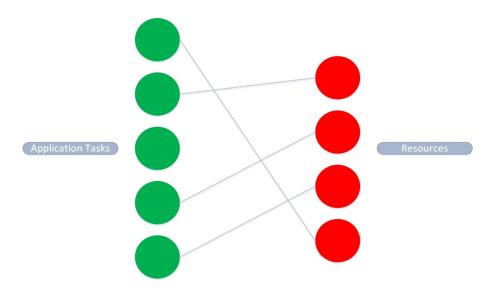

Our proposed methodology is a run-time, distributed resource management framework. Our interest is in applying different market-based models to enable resource management. The framework is responsible for providing a way that the incoming tasks are initially mapped to available resources as well as providing the infrastructure of managing the task throughout its execution lifetime. The market models developed view application tasks as buyers and resources as sellers and try to create matchings amongst them. This framework is developed with intention to minimize system reliability degradation and as a result to distribute workload accross the cores in a way that core reliability degradation is uniform. Our approach takes into account both its workload and the condition of the system resources. So, in essence we create a market where the products for sell are the various types of resources offered by the platform and the buyers are the various tasks that want to run on this platform.

#### 3.2 Resource Degradation Overview

Mean Time To Failure (MTTF) is a quantity that measures average time for failures to happen with the modeling assumption that the failed system is not repaired. Failures in complex, repairable systems are considered conditions not resulting from the design, that bring the system out of service or in need of repair. Any other failures that can be left or maintained in an unrepaired condition are not considered failures under this definition. Failures on Processor chips can be transistor circuit failures and delay faults caused by decreased transistor switching speeds due to NBTI-induced transistor aging [1].

In [13], it is demonstrated how system reliability is affected by the runtime phenomena on chip. More specifically, it is presented that an increase in the number of tasks with fixed execution time (i.e. an increase in system utilization) causes a decrease in MTTF as well as an increase in chip temperature. Consequently,

$$MTTF \propto \frac{1}{utilization}$$

The different models developed in the proposed framework will be evaluated with respect to the above relation, using MTTF as a metric.

#### 3.3 Resource Modeling

The gradual degradation and healing characteristics of some reliability mechanisms allow resources to extend their operational availability and lifetime by carefully managing their workload and operating conditions [1]. However, reliability degradation at the chip level is expected to become worse for future platforms, as chip technology continues to scale down.

The proposed framework uses a distributed way of evaluating the resource conditions. Processor cores can evaluate their condition and give out an indication, so that the run-time manager can make decisions regarding resource allocation. Individual resources would like to keep reliability degradation as low as possible, but this goal also leads to conflicts with the processing power of the platform. Therefore, the run-time resource management approach should deal efficiently with this tradeoff and be compatible with both the expectations of application tasks(i.e. timely execution) and the expectations of resources(i.e. prolonged lifetime).

To be able to evaluate the core condition, some performance counters are used. By being able to monitor each core's running idle time and running active time(time of workload execution up to the time of the measurement) we can calculate the core utilization and consequently have a quantitative result of MTTF, since they share proportionality with utilization, as explained in section 3.2.

Next, we will use market terms to create a price model which will define the resources' availability and ease of participation in the resource allocation process, as well as its behavior over time.

Resources behave as sellers in a market as they provide services to buyers (i.e. application tasks) in the form of execution time. The resource ask prices reflect their availability or capability to execute application tasks, which can be hindered by operating conditions, such as increased temperature, or by failures that happen due to performance degradation due to NBTI for example. By disregarding these factors resources might exhibit permanent failures and unavailability as well as critical degradation of the platform processing power. For this reason, resource ask price has a threshold  $P_t$ , above which the resource is forced to remain idle until the ask price returns to acceptable levels, in order to protect it against the risks mentioned above.

The resource price behavior is defined by the following function:

$$P_{R_U}(duration,idle,match,P_{R_O}) = \begin{cases} P_{R_O} + duration & \text{, if } P_{R_O} < P_t \\ & \text{and idle=1 and match=1} \\ P_{R_O} - duration \times \Delta Price_R & \text{, if idle=1 and match=0} \\ P_{R_O} & \text{, otherwise} \end{cases}$$

The Price Update function has the following domains for its inputs:

$$P_{R_{II}}: (\mathbb{N}_{>0}, \{0,1\}, \{0,1\}, \mathbb{N}_{>0}) \to \mathbb{N}_{>0}$$

Everytime the run-time manager runs to perform resource allocation, the Resource prices are recalculated. Therefore,  $P_{R_O}$  denotes the Price of the resource after the previous price calculation and the result of the function is the updated price.

In the first case a resource is under the price threshold, its state is idle and it getting allocated to an application task, after becoming matched to that. After the task execution, the resource price is incremented by the application task duration. In the next case, the

3.4 Task Modeling 51

task is idle and is not allocated to any application task. For this reason, during the time the resource remains idle, its price decreases as the resource goes through a period of relaxation. In, this case, the Relaxation is expressed in the form of duration. The  $\Delta Price_R$  is a fixed parameter that expresses the sensitivity of this price. Resources are given an initial starting price at power-up. Since resources are homogeneous (considering no workload has been executed) the initial price is identical in all resources. In the last case, the resource price remains unchanged, since the resource is either busy executing a job or above threshold and the resource is forced to become idle.

#### 3.4 Task Modeling

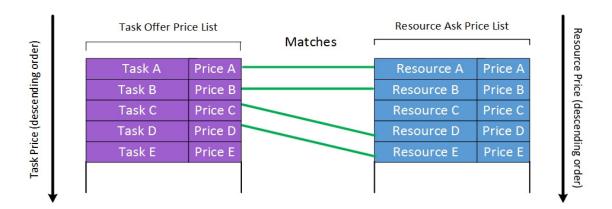

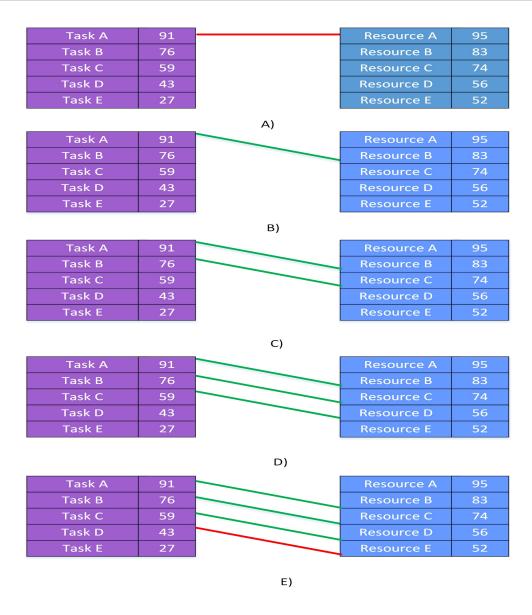

Application tasks enter the resource manager during run-time, in order for them to be executed. In our approach application tasks behave as buyers in a market. Individual tasks would like to be executed as soon as possible and for this reason each task has an offer price that makes available in the market. When the task's offer price is equal or greater than the ask price of a resource, the task is matched to the resource and ensures execution time.

Next, we will create a price model which will define the task's priority and ease of matching with an available resource in the resource allocation process, as well as its behavior over time. Application tasks behave as buyers in a market as they offer to pay a price to sellers in exchange for their services in the form of execution time. The task offer prices reflect their urgency to be executed, which is typically linked with approaching deadlines. Tasks set their offer prices based on their individual status and expectations.

The resource price behavior is defined by the following function:

$$P_{TASK}(waiting_time, P_{TASKO}) = P_{TASKO} + waiting - time \times \Delta Price_T$$

The Price Update function has the following domains for its inputs:

$$P_{TASK}: (\mathbb{N}_{>0}, \mathbb{N}_{>0}) \to \mathbb{N}_{>0} \tag{3.1}$$

Everytime the run-time manager runs to perform resource allocation, the Task prices are recalculated. Therefore,  $P_{TASK_O}$  denotes the Price of the task after the previous price calculation and the result of the function is the updated price.