## ΕΘΝΙΚΟ ΜΕΤΣΟΒΙΟ ΠΟΛΥΤΕΧΝΕΙΟ ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

#### ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΥΠΟΛΟΓΙΣΤΙΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# Τεχνικές συμπίεσης βαθέων νευρωνικών δικτύων σε πολυπύρηνο επεξεργαστικό περιβάλλον

### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

Παναγιώτης Παπαγεωργίου

Επιβλέπων: Γεώργιος Γκούμας

Επίκουρος Καθηγητής Ε.Μ.Π.

Αθήνα, Οκτώβριος 2020

# Τεχνικές Συμπίεσης Βαθέων Νευρωνικών Δικτύων σε πολυπύρηνο επεξεργαστικό περιβάλλον

#### ΔΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

#### Παναγιώτης Παπαγεωργίου

Επιβλέπων: Γεώργιος Γκούμας

Επίκουρος Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 22η Οκτωβρίου 2020 .

Αθήνα, Οκτώβριος 2020.

| <br>Παναγιώτης Παπαγεωργίου<br>Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανι | κός Υπολογιστών Ε.Μ.Π. |

|--------------------------------------------------------------------------------|------------------------|

|                                                                                |                        |

|                                                                                |                        |

|                                                                                |                        |

|                                                                                |                        |

|                                                                                |                        |

|                                                                                |                        |

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ' ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπο την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τη συγγραφέα.

Copyright © Παναγιώτης Παπαγεωργίου, 2020. Εθνικό Μετσόβιο Πολυτεχνείο.

Με επιφύλαξη κάθε δικαιώματος. All rights reserved.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τη συγγραφέα και δεν πρέπει να ερμηνευτεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

#### Περίληψη

Στη σημερινή εποχή έχει προκύψει η ανάγκη τα βαθιά νευρωνικά δίκτυα (DNN) να χρησιμοποιηθούν σε μια πληθώρα ενσωματωμένων συσκευών λόγω της πολύ καλής τους ακρίβειας. Τα DNN κατάφεραν να κυριαρχήσουν με την πολύ καλή τους ακρίβεια σε πολλούς τομείς της μηχανικής μάθησης, μεταξύ άλλων και στον τομέα της όρασης υπολογιστών. Το μειονέκτημά τους είναι πως έχουν μεγάλες ανάγκες από υπολογιστικούς πόρους. Ως αποτέλεσμα οι υπολογιστικές απαιτήσεις των DNN ξεπερνούν κατά πολύ τις δυνατότητες των συσκευών αυτών σε επίπεδο μνήμης, υπολογιστικής ικανότητας και ενεργειακής αυτονομίας. Έτσι ένα κομμάτι της έρευνας επικεντρώθηκε σε τεχνικές ώστε να μπορούν τα DNN να χρησιμοποιηθούν στις παραπάνω συσκευές.

Η διπλωματική αυτή επικεντρώνεται στη μελέτη της κβαντοποίησης (quantization) με ομαδοποίηση (clustering) ως μεθόδου συμπίεσης των DNN μοντέλων. Αρχικά μελετάμε πώς και σε ποιο βαθμό η κβαντοποίηση των συνελικτικών στρωμάτων επιτυγχάνει συμπίεση διατηρώντας την ακρίβεια των μοντέλων. Έπειτα εξετάζουμε πώς επηρεάζεται η υπολογιστική απόδοσή τους. Βελτιστοποιούμε την απόδοση βασιζόμενοι τόσο τεχνικές που υπάρχουν ήδη στην έρευνα όσο και τεχνικές που προτείνουμε εμείς. Η προσπάθεια αυτή αρχικά επικεντρώνεται στο να κρύψουμε τις καθυστερήσεις που εισάγουν τα μη κανονικά μοτίβα πρόσβασης στη μνήμη που εισάγει η κβαντοποίηση. Για να το πετύχουμε αυτό εξετάζουμε τεχνικές όπως loop optimizations καθώς και Just In Time compilation. Για να αυξήσουμε περαιτέρω την απόδοση, αναπτύσσουμε μια δική μας βιβλιοθήκη Just In Time compilation. Χρησιμοποιώντας τη βιβλιοθήκη αυτή προτείνουμε επίσης μια μέθοδο για την εξάλειψη των μη κανονικών μοτίβων. Τέλος συγκρίνοντας τις υλοποιήσεις μας με σύγχρονες βελτιστοποιημένες συνελίξεις παρατηρούμε πως πετυχαίνουν παρόμοια ή μερικές φορές καλύτερη απόδοση.

Λέξεις-Κλειδιά: Βαθιά Μάθηση, Συνέλιξη, Κβαντοποίηση, k-means, Just in Time compilation

#### **Abstract**

Nowadays the need has emerged to deploy deep neural networks (DNN) on a variety of embedded devices due to their high performance. DNNs have dominated, with their state-of-the-art accuracy, a variety of Machine Learning domains and among others, computer vision tasks. Their drawback is however their computational intensity. As a result their computational demands far surpass the capabilities of edge devices in terms of memory, computational power and energy autonomy. Therefore extensive research is being conducted in developing techniques to make DNNs deployable in such devices.

This thesis focuses on studying clustering quantization as a DNN compression technique. We first study the compression achieved with clustering convolution layers while retaining model accuracy. Then we study the effects of clustering on computational performance. We optimize the performance of the DNN models, with methods inspired from existing research as well as with methods we propose. First we focus on improving performance by hiding the latency from irregular memory access patterns that quantization introduces. To achieve that, we investigate loop optimization techniques, as well as Just In Time compilation. To further increase performance, we also develop a Just In Time compilation library. Using the above library we also propose a method to eliminate the irregular access patterns altogether. Finally by comparing our implementations with contemporary optimized convolutions we observe that they achieve similar and sometimes better levels of performance.

**Keywords**: Deep learning, Convolution, Quantization, k-means, Just in Time compilation

# Ευχαριστίες

Αρχικά θέλω να ευχαριστήσω τον Επίκουρο Καθηγητή Ε.Μ.Π. Γεώργιο Γκούμα που μου έδωσε την ευκαιρία να εκπονήσω την παρούσα διπλωματική εργασία στο Εργαστήριο Υπολογιστικών Συστημάτων της Σχολής Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου.

Θα ήθελα επίσης να ευχαριστήσω τους καθηγητές μου κ. Κοζύρη και κ. Πνευματικάτο για τη διδασκαλία τους και τις γνώσεις που μου προσέφεραν. Ευχαριστώ επίσης την υποψήφια διδάκτορα Αθηνά Ελαφρού για τη συννεισφορά της, την καθοδήγηση, την βοήθεια και τις συμβουλές που μου έδωσε σε όλα τα στάδια της εκπόνησης της διπλωματικής αυτής.

Αυτή η διπλωματική εργασία σηματοδοτεί την ολοκλήρωση των σπουδών μου. Είναι το τέλος ενός θεματικού κύκλου της ζωής μου και αποτελεί έναν επίλογο στις πολλές σελίδες των φοιτητικών μου χρόνων. Γι αυτό θέλω να ευχαριστήσω όλους όσους έκαναν αυτά τα χρόνια αξέχαστα. Όλους εκείνους που κάποτε περπατήσαμε στα ίδια μονοπάτια, τους φίλους και γνωστούς.

Ευχαριστώ όμως ξεχωριστά εκείνα τα παιδιά στα τραπεζάκια, τους ΑΝεξάρτητους Αριστερούς Φοιτητές Ηλεκτρολόγους. Μαζί ανακαλύψαμε τη συντροφικότητα, την αλληλεγγύη, την συλλογικότητα. Μάθαμε την αξία του να αγωνόμαστε για να φτιάχνουμε έναν κόσμο καλύτερο. Για να λεγόμαστε λίγο παραπάνω άνθρωποι.

Ευχαριστώ τους γονείς μου που παντα ήταν δίπλα μου, με βοηθούσαν και με στήριζαν. Χωρίς αυτούς δε θα είχα φτάσει ως εδώ.

Τέλος ευχαριστώ την Έλενα που με στήριξε και άντεξε τη γκρίνια μου όλο αυτό το διάστημα.

Παναγιώτης Παπαγεωργίου, Οκτώβριος 2020

# **Contents**

| 1                      | Εισο | ιγωγή 19                                                |  |  |

|------------------------|------|---------------------------------------------------------|--|--|

|                        | 1.1  | Συνελικτικά Νευρωνικά Δίκτυα                            |  |  |

|                        | 1.2  | Αλγόριθμος k-means                                      |  |  |

| 2                      | Κβο  | ντοποίηση 22                                            |  |  |

|                        | 2.1  | Κβαντοποίηση                                            |  |  |

|                        | 2.2  | Μεθοδολογία Κβαντοποίησης                               |  |  |

|                        | 2.3  | Αποτελέσματα                                            |  |  |

| 3                      | Βελ  | τιστοποίηση του inference για κβαντοποιημένα μοντέλα 27 |  |  |

|                        | 3.1  | Padding                                                 |  |  |

|                        | 3.2  | Loop order                                              |  |  |

|                        | 3.3  | Blocking                                                |  |  |

|                        | 3.4  | Just In Time Compilation                                |  |  |

|                        | 3.5  | Loop unrolling                                          |  |  |

|                        | 3.6  | Unique filters                                          |  |  |

|                        | 3.7  | Αποτελέσματα                                            |  |  |

| 4                      | Συμ  | περάσματα και μελλοντικές προεκτάσεις 47                |  |  |

| 5                      | Intr | oduction 49                                             |  |  |

|                        | 5.1  | DNN Quantization                                        |  |  |

|                        | 5.2  | Contribution of this Thesis                             |  |  |

| 6                      | Bac  | kground 56                                              |  |  |

|                        | 6.1  | Machine Learning                                        |  |  |

|                        | 6.2  | Neural Networks                                         |  |  |

|                        | 6.3  | Convolutional Neural Networks                           |  |  |

|                        |      | 6.3.1 Convolution layer                                 |  |  |

|                        |      | 6.3.2 Pooling layer                                     |  |  |

|                        |      | 6.3.3 Fully Connected Layer                             |  |  |

|                        |      | 6.3.4 Batch Normalization Layer                         |  |  |

| 6.4 K-means clustering |      |                                                         |  |  |

| 7 | DNI | N Quan        | tization                                    | 67  |

|---|-----|---------------|---------------------------------------------|-----|

|   | 7.1 | Quanti        | ization Methodology                         | 67  |

|   | 7.2 |               | ression rate                                | 68  |

|   | 7.3 | _             | ization noise                               | 69  |

|   | 7.4 | Experi        | imental Setup                               | 69  |

|   |     | 7.4.1         | Deep Learning Frameworks                    | 69  |

|   |     | 7.4.2         | Datasets                                    | 69  |

|   |     | 7.4.3         | CNN Models                                  | 70  |

|   |     | 7.4.4         | Data preprocessing                          | 72  |

|   |     | 7.4.5         | Performing k-means                          | 73  |

|   |     | 7.4.6         | Evaluating accuracy                         | 74  |

|   |     | 7.4.7         | Computer specifications                     | 75  |

|   | 7.5 | Evalua        | ation                                       | 76  |

| 8 | Opt | imizatio      | on of Inference for Quantized Models        | 79  |

|   | 8.1 | Paddir        | ng                                          | 79  |

|   | 8.2 | Loop          | order                                       | 81  |

|   | 8.3 | Blocki        | ing                                         | 82  |

|   | 8.4 |               | Time Compilation                            | 85  |

|   |     | 8.4.1         | Asmjit framework                            | 86  |

|   |     | 8.4.2         | Easy Jit framework                          | 88  |

|   |     | 8.4.3         | Generating C++ code at runtime              | 89  |

|   |     | 8.4.4         | Generating convolutions from template files | 91  |

|   | 8.5 | Loop ι        | unrolling                                   | 93  |

|   |     |               | e filters                                   | 93  |

| * |     | imental Setup | 95                                          |     |

|   |     | 8.7.1         | Computer specifications                     | 95  |

|   |     | 8.7.2         | Test benchmarks                             | 96  |

|   |     | 8.7.3         | Block size                                  | 97  |

|   |     | 8.7.4         | Compilers                                   | 98  |

|   |     | 8.7.5         | Vectorization                               | 98  |

|   |     | 8.7.6         | Metrics                                     | 99  |

|   |     | 8.7.7         | Implementation names                        | 100 |

|   | 8.8 | Evalua        | ation                                       | 101 |

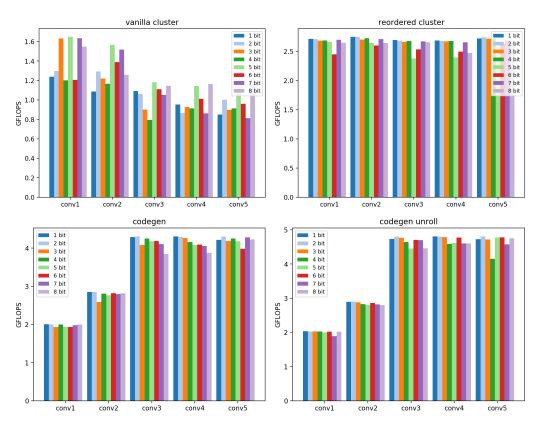

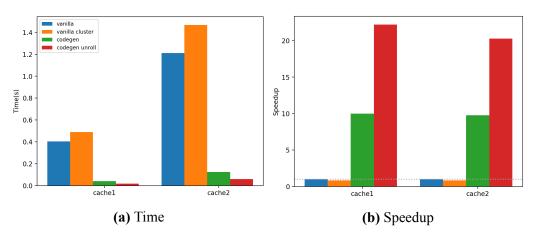

|   |     | 8.8.1         | Codebook length                             | 101 |

|   |     | 8.8.2         | Padding                                     | 102 |

|   |     | 8.8.3         | Reordered convolutions                      | 102 |

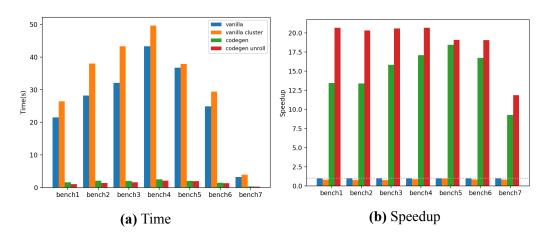

|   |     | 8.8.4         | Blocking                                    | 103 |

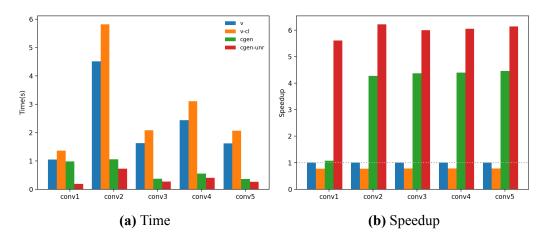

|   |     | 8.8.5         | Comparision of Jit implementations          | 105 |

|   |     | 8.8.6         | Loop unrolling                              | 106 |

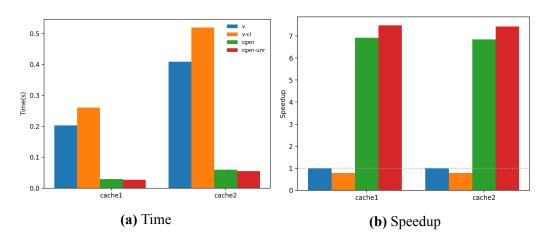

|   |     | 8.8.7         | Unique Filters                              | 110 |

|   |     | 8.8.8         | Total comparison with all compilers         | 112 |

|   |     | 8.8.9         | Parallel implementation                     | 121 |

9 Conclusions and Future Work

# **List of Figures**

| 1.1                                | Συνέλιξη ενός kernel με μια είσοδο [11]                                    | 20  |

|------------------------------------|----------------------------------------------------------------------------|-----|

| 1.2                                | Τα βήματα του k-means [24]. (a) Κάθε τιμή ανατίθεται σε ένα cluster.       |     |

|                                    | (b) Τα centroids επανυπολογίζονται. (c) Κάθε τιμή ανατίθεται σε ένα νέο    |     |

|                                    | cluster. (d) Τα centroids υπολογίζονται ξανά.                              | 21  |

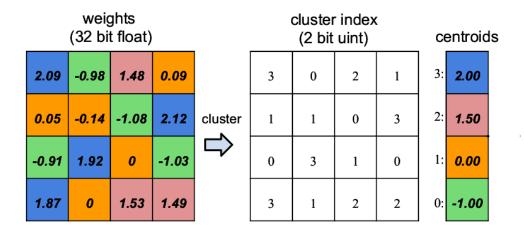

| 2.1                                | Παράδειγμα clustering βαρών με 2-bit codebook [18]                         | 23  |

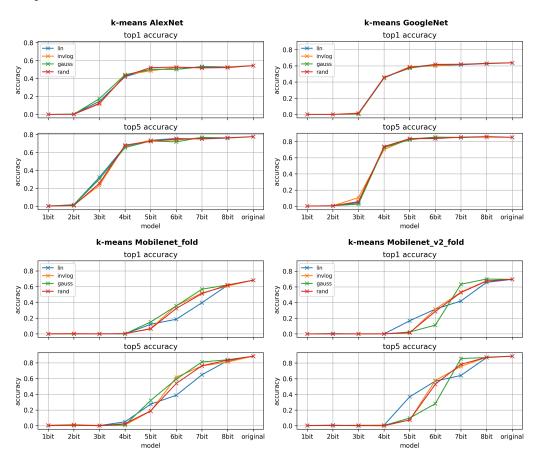

| 2.2                                | Επίδραση του kmeans με δίαφορες αρχικοποιήσεις στην ακρίβεια των μοντέλων. | 24  |

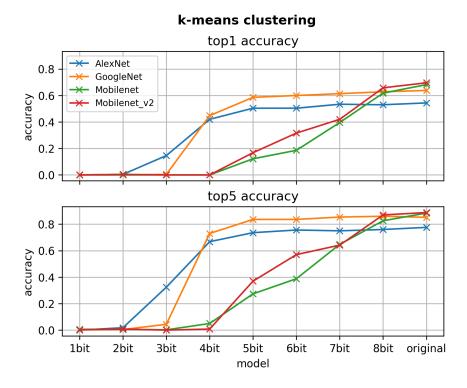

| 2.3                                | Ακρίβεια των clustered μοντέλων καθώς μικραίνει το μέγεθος του codebook    | 25  |

| 2.4                                | Τα βάρη του πρώτου επιπέδου του AlexNet καθώς χρησιμοποιούμε όλο           |     |

|                                    | και λιγότερα bit στην κβαντοποίηση                                         | 26  |

| 3.1                                | Δημιουργία- Compile- Εκτέλεση κώδικα                                       | 34  |

| 3.2                                | Σύγκριση τεχνικών padding στην απλή συνέλιξη και στη συνέλιξη με clusterin |     |

|                                    | (Benchmark 8.3 στο μηγάνημα Desktop)                                       | 37  |

| 3.3                                | Reordered εκδοχή συνέλιξης με και χωρίς clustering στο Desktop και Benchma | ark |

|                                    | 3.4                                                                        | 38  |

| 3.4                                | Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πί-      |     |

|                                    | νακας 3.5 στο μηχάνημα Desktop)                                            | 39  |

| 3.5                                | Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πί-      |     |

|                                    | νακας 3.5 στο μηχάνημα Server)                                             | 39  |

| 3.6                                | Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πί-      | 4.0 |

| 2.7                                | νακας 3.5 στο μηχάνημα Edge)                                               | 40  |

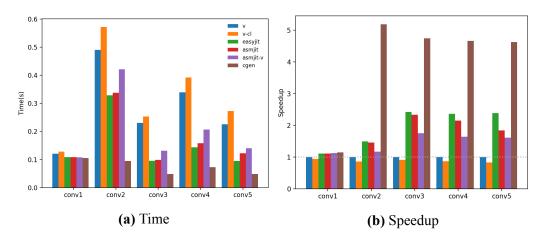

| 3.7                                | Απόδοση των vanilla, cluster asmjit and easyjit υλοποιήσεων στο Benchmark  | 41  |

| 2.0                                | 8.3 στο Desktop                                                            | 41  |

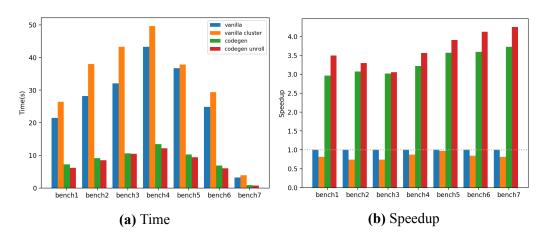

| 3.8                                | Σύγκριση των jit υλοποιήσεων με την βιβλιοθήκη μας στο benchmark 8.4       | 42  |

| 2.0                                | στο μηχάνημα Desktop                                                       | 42  |

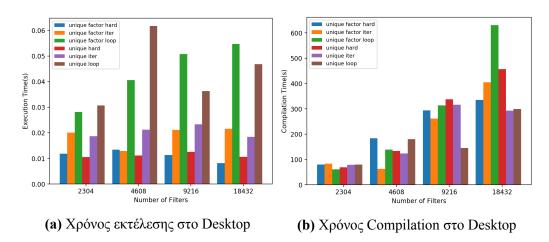

| <ul><li>3.9</li><li>3.10</li></ul> | Χρόνος συναρτήσει αριθμού kernel                                           | 42  |

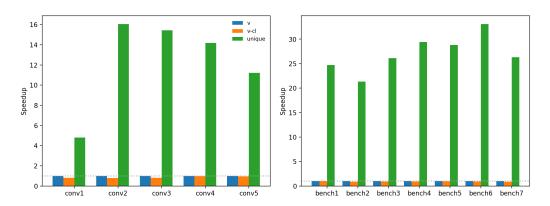

| 3.10                               | Συγκριση unique inters στα benchmark 8.5 και 8.4 στο Desktop               | 43  |

| 3.11                               | Συγκεντρωτικά η απόδοση στο Server για το benchmark 8.4                    | 44  |

| 3.12                               | Συγκεντρωτικά η απόδοση στο Edge μηγάνημα για το benchmark 8.4             | 44  |

| 3.14                               |                                                                            | 44  |

|                                    | Παράλληλη απόδοση του Server στο benchmark 8.4                             | 46  |

| 5.15                               | Traparation according to between the benefittation of                      | TU  |

| 5.1        | Example of image classification using CNN                                    | 50  |

|------------|------------------------------------------------------------------------------|-----|

| 5.2        | Performance of traditional computer vision vs Deep Learning                  | 51  |

| 5.3        | Train on powerful GPUs, compress and then deploy on embedded devices         | 52  |

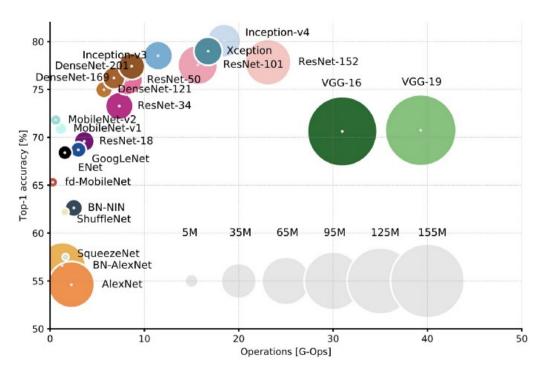

| 5.4        | Top1 accuracy vs operations. The size of the blobs is proportional to the    |     |

|            | number of network parameters [4]                                             | 52  |

| 5.5        | Deep compression pipeline [18]                                               | 53  |

| 6.1        | Model of a neuron                                                            | 57  |

| 6.2        | Multilayer perceptron with 2 hidden layers                                   | 58  |

| 6.3        | 2-D representation of local connections between convolution layers           | 59  |

| 6.4        | Lenet architecture [29]                                                      | 59  |

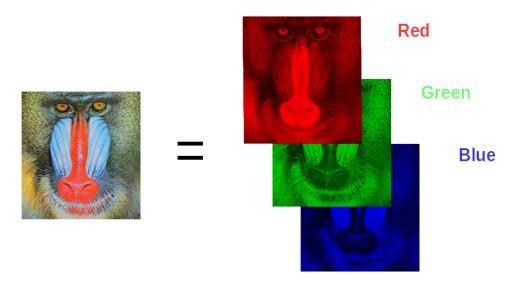

| 6.5        | An RGB image consists of 3 channels red, green and blue                      | 60  |

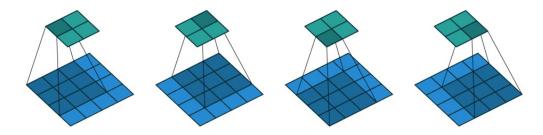

| 6.6        | Example of a convolution of a single kernel with a single channel input [11] | 60  |

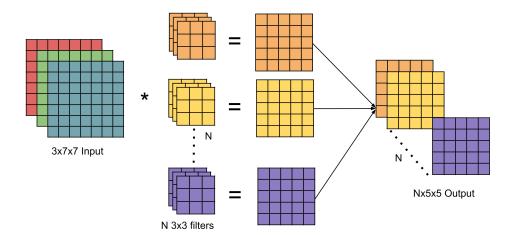

| 6.7        | Example of a convolution of N filters with a 3 channel input(rgb image)      | 61  |

| 6.8        | Example of convolution with zero padding [11]                                | 62  |

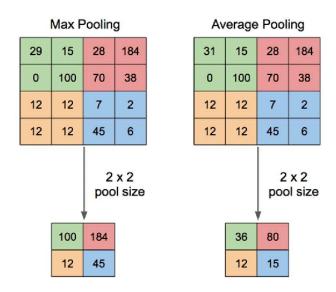

| 6.9        | Example of average and max pooling [52]                                      | 64  |

| 6.10       | Alternating steps of k-means [24]. (a) Each value is assigned to a cluster.  |     |

|            | (b) The cluster centers are calculated. (c) Each value is assigned to a new  |     |

|            | cluster. (d) The cluster centers are calculated again                        | 66  |

| 7.1        | Example of clustering kernel weights using 2-bits [18]                       | 68  |

| 7.2        | Example of clustering whole kernels [54]                                     | 68  |

| 7.3        | AlexNet architecture                                                         | 70  |

| 7.4        | GoogleNet architecture and inception module detail                           | 71  |

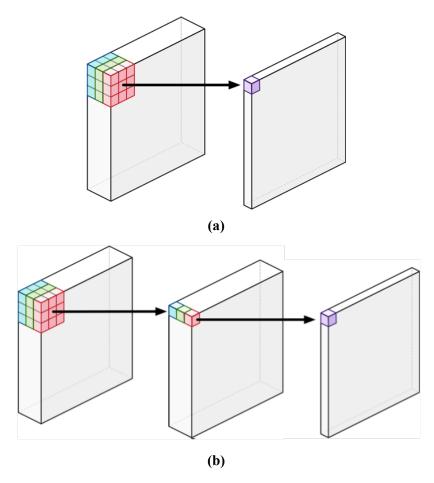

| 7.5        | (a) Normal convolution (b) Depthwise separable convolution                   | 72  |

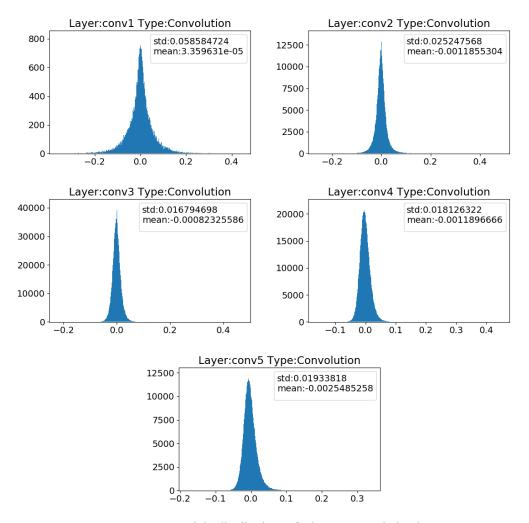

| 7.6        | Weight distributions of AlexNet convolution layer                            | 74  |

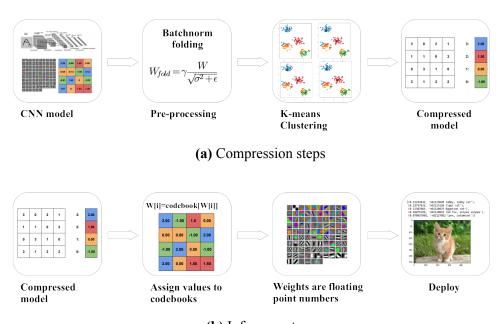

| 7.7        | Quantization pipeline (a) For compression. (b) For inference                 | 75  |

| 7.8        | kmeans effect on accuracy with linear, random, gaussian and inverse log-     |     |

| <b>-</b> ^ | arithmic centroid initializations                                            | 76  |

| 7.9        | Accuracy vs bits used for clustering                                         | 77  |

| 7.10       | Visualization of the effect of weight quantization on the first convolution  | 70  |

|            | layer of AlexNet                                                             | 78  |

| 8.1        | 8 fused multiply adds using Intel vfmadd instruction with 256bit vector      |     |

|            | registers                                                                    | 82  |

| 8.2        | Code generation pipeline                                                     | 92  |

| 8.3        | Comparing different codebook sizes for various clustering convolution        |     |

|            | *                                                                            | 101 |

| 8.4        | Comparing padding approaches on vanilla and clustering convolution im-       |     |

|            | 1                                                                            | 102 |

| 8.5        | Effects of clustering in vanilla and reordered convolution on Table 8.3 on   |     |

|            | 1                                                                            | 103 |

| 8.6        | Performance of blocking implementations and their non blocking coun-         |     |

|            | terparts on Table 8.4 on Desktop                                             | 104 |

| 8.7  | Performance of blocking implementations and their non blocking coun-          |

|------|-------------------------------------------------------------------------------|

|      | terparts Table 8.4 on Server                                                  |

| 8.8  | Performance of blocking implementations and their non blocking coun-          |

|      | terparts Table 8.4 on Edge                                                    |

| 8.9  | Performance of vanilla, cluster asmjit and easyjit implementations on Ta-     |

|      | ble 8.3 on Desktop                                                            |

| 8.10 | Comparing previous jit implementations with our code generation scheme        |

|      | on Table 8.3 on Desktop                                                       |

| 8.11 | Comparing jit implementations with our code generation scheme on Table        |

|      | 8.5 on Desktop                                                                |

| 8.12 | Comparing jit implementations with our code generation scheme on Table        |

|      | 8.4 on Desktop                                                                |

| 8.13 | Comparing jit implementations with our code generation scheme on Table        |

|      | 8.3 on Edge                                                                   |

| 8.14 | Comparing jit implementations with our code generation scheme on Table        |

|      | 8.5 on Edge                                                                   |

| 8.15 | Comparing jit implementations with our code generation scheme on Table        |

|      | 8.4 on Edge                                                                   |

| 8.16 | Execution and compilation time vs the number of filters                       |

| 8.17 | Comparison of unique filters on Table 8.3 and 8.4 on Desktop 111              |

| 8.18 | Comparison on Table 8.3 and 8.4 on Server                                     |

| 8.19 | Comparison on Table 8.3 and 8.4 on Edge                                       |

| 8.20 | Performance with all the compilers on Desktop Table 8.4                       |

| 8.21 | Performance with all the compilers on Server Table 8.4                        |

| 8.22 | Performance with all the compilers on Edge Table 8.4                          |

| 8.23 | Performance without vectorization with all the compilers on Edge Table 8.4117 |

| 8.24 | Parallel performance while threads increase on Desktop Table 8.4 121          |

| 8.25 | Parallel performance while threads increase on Server Table 8.4 122           |

# **List of Algorithms**

| 1  | Ο αλγόριθμος της συνέλιξης                                    | 20 |

|----|---------------------------------------------------------------|----|

| 2  | Συνέλιξη με έλεγχο συνοριακών τιμών                           | 28 |

| 3  | Συνέλιξη με αλλαγή διαστάσεων της εισόδου                     | 28 |

| 4  | Συνέλιξη με αλλαγή της σειράς των loop                        | 29 |

| 5  | Συνέλιξη με blocking στις χωρικές διαστάσεις                  | 30 |

| 6  | Συνέλιξη με blocking στις χωρικές διαστάσεις και στα channels | 31 |

| 7  | Συνέλιξη με αλλαγή της σειράς των loop και blocking           | 31 |

| 8  | Convolution algorithm                                         | 63 |

| 9  | Convolution with soft padding                                 | 80 |

| 10 | Convolution with physical (hard) padding                      | 80 |

| 11 | Reordered Convolution                                         | 82 |

| 12 | Convolution with blocking on spatial dimensions               | 84 |

| 13 | Convolution with blocking on spatial dimensions and channels  | 84 |

| 14 | Reordered convolution with blocking                           | 85 |

# **List of Tables**

| 2.1  | Μέγιστη συμπίεση χωρίς πτώση ακρίβειας.                                 | 25  |

|------|-------------------------------------------------------------------------|-----|

| 3.1  | Μεγέθη block                                                            | 30  |

| 3.2  | Machine specifications                                                  | 35  |

| 3.3  | CPU specifications                                                      | 35  |

| 3.4  | Benchmark με τις συνελίξεις του AlexNet                                 | 35  |

| 3.5  | Benchmark με μεγάλες συνελίξεις                                         | 35  |

| 3.6  | Benchmark που στοχεύει το τελευταίο επίπεδο cache στα μηχανήματα του    |     |

|      | Πίνακα 3.2                                                              | 36  |

| 3.7  | Υλοποιήσεις και ονόματα στα διαγράμματα                                 | 36  |

| 7.1  | Machine specifications                                                  | 75  |

| 7.2  | CPU specifications                                                      | 75  |

| 7.3  | Compression of models while retaining their accuracy                    | 77  |

| 8.1  | Machine specifications                                                  | 95  |

| 8.2  | CPU specifications                                                      | 96  |

| 8.3  | Benchmark with AlexNet convolutions                                     | 96  |

| 8.4  | Benchmark with large convolutions                                       | 96  |

| 8.5  | Benchmark targeting last level cache for each machine in Table 8.1      | 97  |

| 8.6  | Element bounds for efficient FMA                                        | 97  |

| 8.7  | Block sizes for blocking                                                | 98  |

| 8.8  | Compilers                                                               | 98  |

| 8.9  | Compiler options for vectorization                                      | 99  |

| 8.10 | Implementations and names in legends                                    | 100 |

| 8.11 | Existence of single and vector FMA instructions on the Desktop machine. | 118 |

| 8.12 | Existence of single and vector FMA instructions on the Server machine   | 119 |

| 8.13 | Existence of single and vector FMA instructions on the Edge machine     | 120 |

# Κεφάλαιο 1

# Εισαγωγή

Στη συνέχεια παρουσιάζουμε τα δύο πειράματα, τη διαδικασία που ακολουθούμε, τα αποτελέσματα καθώς και μελλοντικές επεκτάσεις.

# 1.1 Συνελικτικά Νευρωνικά Δίκτυα

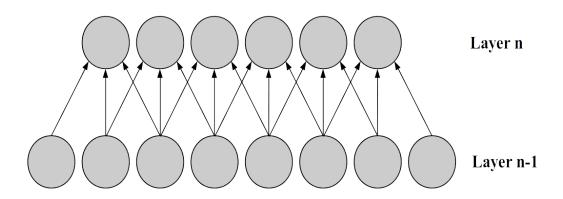

Τα Συνελικτικά Νευρωνικά Δίκτυα (CNN) είναι μια υποκατηγορία DNN που εξειδικεύονται στην αναγνώριση εικόνας. Όπως τα κανονικά νευρωνικά δίκτυα οι νευρώνες τους λαμβάνουν εισόδους, εκτελούν μια μαθηματική πράξη με τα βάρη και στη συνέχεια εφαρμόζουν μια συνάρτηση ενεργοποίησης. Τα βάρη αλλάζουν με τον ίδιο τρόπο κατά τη διάρκεια της εκπαίδευσης. Η διαφορά είναι ότι τα CNN αποδίδουν καλύτερα με εικόνες ως εισόδους, επειδή οι συνδέσεις μεταξύ δύο στρωμάτων (layers) περιορίζονται σε τοπικές περιοχές. Αυτό μειώνει δραστικά τον αριθμό των παραμέτρων.

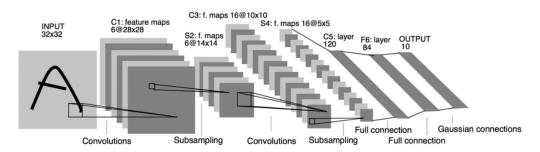

Η θεμελιώδης μαθηματική πράξη των CNN είναι η συνέλιξη. Οι συνελίξεις εφαρμόζονται μεταξύ μιας εισόδου και του πίνακα των βαρών. Τα βάρη κάθε συνελικτικού στρώματος είναι οργανωμένα σε πίνακες που περιέχουν 3-D φίλτρα. Κάθε φίλτρο αποτελείται από 2-D kernels κάθε ένα από τα οποία πολλαπλασιάζεται διαδοχικά με τμήμα του εκάστοτε καναλιού της εικόνας για να δώσει την έξοδο (Σχ. 1.1). Έπειτα οι επί μέρους έξοδοι των καναλιών αθροίζονται και το αποτέλεσμα είναι ένα κανάλι εξόδου. Αυτό επαναλαμβάνεται για όλα τα φίλτρα και έτσι σχηματίζεται η έξοδος. Ο αριθμός των φίλτρων είναι ίσος με τον αριθμό των επιθυμητών καναλιών της εξόδου.

Συγκεντρωτικά η διαδικασία της συνέλιξης φαίνεται στον αλγόριθμο 1. Όπου οι διαστάσεις της εξόδου υπολογίζονται ως εξής:

$$H_o = \frac{(H_i - H_k + 2 * pad)}{stride} + 1 \tag{1.1}$$

$$W_o = \frac{(W_i - W_k + 2 * pad)}{stride} + 1 \tag{1.2}$$

Όπου  $C_{out}$ ,  $H_o$ ,  $W_o$  είναι το κανάλι, το ύψος και το πλάτος της εξόδου,  $C_{in}$   $H_i$ ,  $W_i$  είναι το κανάλι, το ύψος και το πλάτος της εισόδου και  $H_k$ ,  $W_k$  είναι το ύψος και το πλάτος

του kernel. Stride ονομάζεται η απόσταση κατά την οποία μετακινείται το φίλτρο πάνω στην είσοδο σε κάθε επανάληψη του αλγορίθμου. Pad είναι μια τεχνική με την οποία η είσοδος "γεμίζει" με μηδενικά στις άκρες του ύψους και πλάτους της ώστε η είσοδος και η έξοδος να έχουν τις ίδιες διαστάσεις ύψους πλάτους.

Σχήμα 1.1: Συνέλιξη ενός kernel με μια είσοδο [11]

#### Algorithm 1 Ο αλγόριθμος της συνέλιξης

- 1: **for** i = 0 to Cin 1 **do**

- 2: **for** j = 0 to Cout 1 **do**

- 3: **for** k = 0 to  $H_o 1$  **do**

- 4: **for** l = 0 to  $W_o 1$  **do**

- 5: **for** m = 0 to  $H_k 1$  **do**

- 6: **for** n = 0 to  $W_k 1$  **do**

- 7:  $k_{in} = stride \times k + m pad$

- 8:  $l_{in} = stride \times l + n pad$

- 9:  $Output[j][k][l] + = Input[i][k_{in}][l_{in}] \times Kernel[i][j][m][n]$

## 1.2 Αλγόριθμος k-means

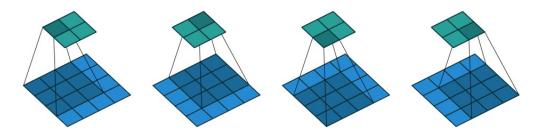

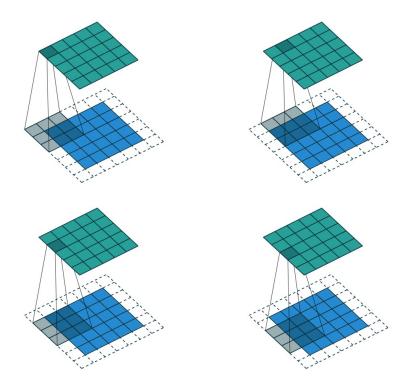

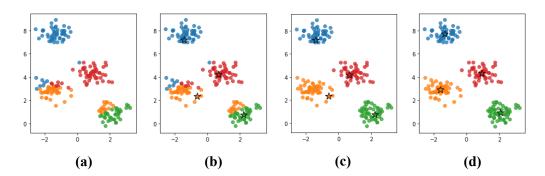

Ο αλγόριθμος k-means είναι ένας επαναληπτικός αλγόριθμος μη επιβλεπόμενης μητανικής μάθησης. Ομαδοποιεί ένα σύνολο παρατηρήσεων  $(X=\{x_1,x_2,...,x_n\})$  σε διακριτές μη εφαπτόμενες ομάδες (clusters)  $C=\{C_1,C_2,...,C_k\}$ . Κάθε cluster αντιπροσωπεύεται από μια τιμή που ονομάζεται centroid. Όλα τα centroids αποτελούν ένα codebook. Ο αλγόριθμός ελαχιστοποιεί το τετράγωνο της Ευκλείδειας απόστασης των στοιχείων κάθε cluster από τη μέση τιμή τους  $\mu_i$ .

Τα centroids αρχικοποιούνται σε κάποιες τιμές και έπειτα ακολουθούνται εναλλάξ τα εξής βήματα(Σχ. 1.2:

Κάθε παρατήρηση ανατίθεται στο cluster με το centroid του οποίου έχει το ελάχιστο τετράγωνο της Ευκλείδειας απόστασης.

$$C_i = \{x_k \in X : ||x_k - m_j||^2 \le ||x_k - m_i||^2 j, 1 \le j \le k\}$$

(1.3)

• Η τιμή του centroid κάθε cluster  $(m_i)$  επανυπολογίζεται ως η μέση τιμή όλων των παρατηρήσεων του cluster.

$$m_i = \frac{1}{n_i} \sum_{x_j \in C_i} x_j \tag{1.4}$$

Ο αλγόριθμος συνεχίζει μέχρι οι τιμές των centroids να μην αλλάζουν. Τότε έχει συγκλίνει. Ο αλγόριθμος δεν εγγυάται βέλτιστη λύση γιατί μπορεί να συγκλίνει σε τοπικά ελάχιστα. Γι αυτό και επαναλαμβάνεται πολλές φορές με τυχαίες αρχικοποιήσεις.

**Σχήμα 1.2:** Τα βήματα του k-means [24]. (a) Κάθε τιμή ανατίθεται σε ένα cluster. (b) Τα centroids επανυπολογίζονται. (c) Κάθε τιμή ανατίθεται σε ένα νέο cluster. (d) Τα centroids υπολογίζονται ξανά.

# Κεφάλαιο 2

# Κβαντοποίηση

# 2.1 Κβαντοποίηση

Η κβαντοποίηση είναι μια προσέγγιση για τη συμπίεση DNN. Η κβαντοποίηση χρησιμοποιεί λιγότερα bit για να να αναπαραστήσει τους αριθμούς. Αυτό προκαλεί απόκλιση από της αρχικές τιμές και έχει αντίκτυπο στην ακρίβεια του μοντέλου. Η κβαντοποίηση συνήθως επιτυγχάνεται με δύο τρόπους. Ο πρώτος είναι η μετατροπή των αριθμών κινητής υποδιαστολής σε αριθμούς σταθερής υποδιαστολής. Η θέση της υποδιαστολής καθορίζεται έτσι ώστε να υπάρχει το λιγότερο δυνατό σφάλμα από τις αρχικές τιμές. Ο δεύτερος είναι η ομαδοποίηση των βαρων βάσει κάποιου κριτηρίου. Κάθε ομάδα έχει μια αντιπροσωπευτική τιμή και έτσι τα βάρη καταλήγουν να ειναι λιγότερα.

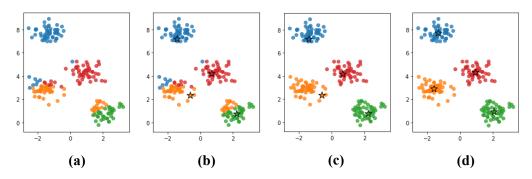

# 2.2 Μεθοδολογία Κβαντοποίησης

Πραγματοποιούμε την κβαντοποίηση ώστε να ομαδοποιήσουμε τις τιμές των βαρών σε ομάδες, με κάθε ομάδα να έχει μια αντιπροσωπευτική τιμή. Αφού πραγματοποιηθεί η κβαντοποίηση οι πίνακες των βαρών περιέχουν πλέον indexes στο πίνακα με τις αντιπροσωπευτικές τιμές που ονομάζεται codebook ( $\Sigma \chi$ . 2.1). Το μέγεθός του εξαρτάται από το πόσα bit επιθυμούμε να καταλαμβάνει σε μέγεθος, το οποίο υπολογίζεται ως  $2^{bits}$ .

Έτσι για να έχουμε πρόσβαση στις τιμές των βαρών πρέπει πρώτα να βρούμε την τιμή του index και βάσει αυτού να επιλέξουμε το κατάλληλο στοιχείο του codebook. Έτσι ο εσωτερικός υπολογισμός στον Αλγόριθμο 1 γίνεται:

$$Output[j][k][l] + = Input[i][k_{in}][l_{in}] \times Codebook[Kernel[i][j][m][n]]$$

(2.1)

Σχήμα 2.1: Παράδειγμα clustering βαρών με 2-bit codebook [18]

Μετά τη συμπίεση κάθε βάρος είναι ένα integer index στον πίνακα codebook. Έτσι κάθε βάρος έχει μειωθέι σε  $\log_2(k)$  (όπου k το μέγεθος του codebook) και ο λόγος συμπίεσης υπολογίζεται ως:

$$r = \frac{n * s}{n * \log_2 k + k * s} \tag{2.2}$$

Όπου η είναι ο αριθμός των βαρών και s=sizeof(float). Για μεγάλο αριθμό βαρών το μέγεθος του codebook μπορεί να θεωρηθεί αμελητέο. Δεδομένου επίσης ότι το μέγεθος του codebook είναι  $2^bits$  η προηγόυμενη σχέση γίνεται:

$$r = \frac{s}{bits} \tag{2.3}$$

Επομένως για float αριθμούς 32bit ο μεγιστος λόγος συμπίεσης είναι 32 με 1bit codebook.

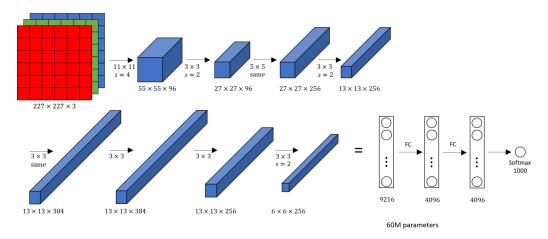

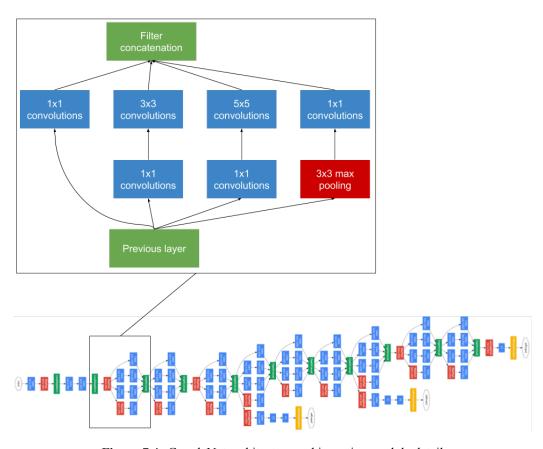

Για την αξιολόγηση της ακρίβειας επιλέγουμε το Caffe framework [26] για το πείραμά μας. Στο caffe υπάρχουν πολλά μοντέλα ήδη εκπαιδευμένα. Εμείς θα δοκιμάσουμε την κβαντοποίηση στο AlexNet [28], GooleNet [45], Mobilenet [23] και Mobilenet ν2 που έχουν εκπαιδευθεί πάνω στο Imagenet [10].

Πραγματοποιούμε τον αλγόριθμο k-means με την βιβλιοθήκη scipy της python [41] και συγκρίνουμε διαφορετικές αρχικοποιήσεις (γραμμική, ομοιόμορφη, αντίστροφη λογαριθμική). Επειδή το caffe δεν υποστηρίζει πράξεις με κβαντοποιημένα βάρη, αντικαθιστούμε τα βάρη με τις τιμές που δείχνουν στο codebook για να πάρουμε μετρήσεις. Δοκιμάζουμε μεγέθη codebook από 1 έως 8 bit.

## 2.3 Αποτελέσματα

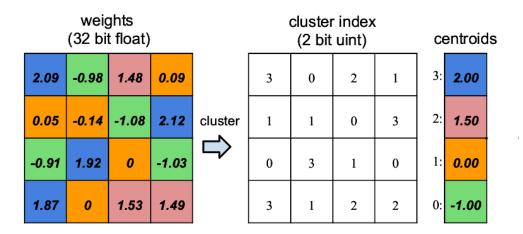

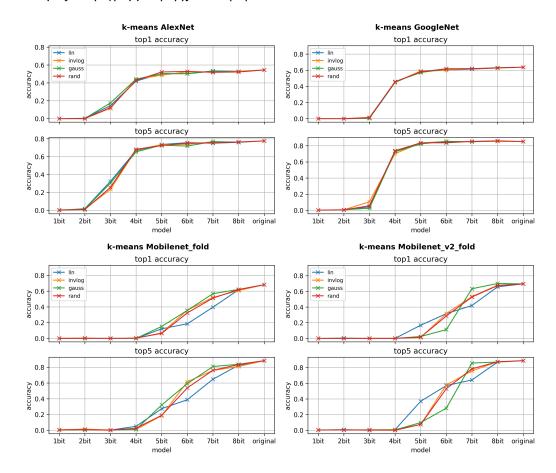

Από το Σχ. 2.2 βλέπουμε την επίδραση διαφορετικών αρχικοποιήσεων στην ακρίβεια των προβλέψεων. Παρατηρούμε ότι για τα μεγάλα μοντέλα GoogleNet και AlexNet η

επίδραση είναι αμελητέα. Για τα μικρότερα Mobilenets παρατηρούμε διακυμάνσεις αλλά καμία μέθοδος δεν είναι σταθερά πάντα η καλύτερη. Έτσι επιλέγουμε να τα συγκρίνουμε όλα μαζί στην γραμμική αρχικοποίηση.

Σχήμα 2.2: Επίδραση του kmeans με δίαφορες αρχικοποιήσεις στην ακρίβεια των μοντέλων.

Έπειτα στο Σχ. 2.3 συγκρίνουμε την επίδραση του k-means στην ακρίβεια καθώς τα codebook γίνονται μικρότερα. Παρατηρούμε πως τα μεγάλα μοντέλα GoogleNet και AlexNet μπορούν να κβαντοποιηθούν έως 5bit χωρίς να έχουν μεγάλη απόκλιση από την αρχική ακρίβεια. Αυτό συμβαίνει γιατί έχουν πολλά περιττά βάρη. Αντίθετα τα Mobilenet που είναι ήδη αρκετά μιρκότερα καταφέρνουν να κβαντοποιηθούν μέχρι 8bit χωρίς να χάσουν σημαντική ακρίβεια.

#### k-means clustering top1 accuracy AlexNet GoogleNet Mobilenet 9.0 4.0 4.0 Mobilenet\_v2 0.2 0.0 top5 accuracy 0.8 9.0 4.0 4.0 0.2 0.0 7bit 1bit 2bit 3bit 4bit 5bit 6bit original model

Σχήμα 2.3: Ακρίβεια των clustered μοντέλων καθώς μικραίνει το μέγεθος του codebook

Στα πειράματά μας χρησιμοποιούμε το ίδιο μήκος bit για τα codebooks όλων των layers. Έτσι η εξίσωση 2.3 περιγράφει τον λόγο συμπίεσης για όλο το μοντέλο. Βάσει αυτών υπολογίζουμε στον Πίνακα 2.1 την μέγιστη θεωρητική συμπίεση χωρίς πτώση της ακρίβειας των μοντέλων.

Πίνακας 2.1: Μέγιστη συμπίεση χωρίς πτώση ακρίβειας.

| Μοντέλο      | Αρχικό  | Τελικό  | Συμπίεση    | Μέγεθος  |

|--------------|---------|---------|-------------|----------|

|              | μέγεθος | μέγεθος | (Θεωρητική) | Codebook |

| AlexNet      | 233MB   | 36.4MB  | 6.4         | 5bits    |

| GoogleNet    | 51MB    | 7.9MB   | 6.4         | 5bits    |

| Mobilenet    | 17MB    | 4.25MB  | 4           | 8bits    |

| Mobilenet v2 | 14MB    | 3.5MB   | 4           | 8bits    |

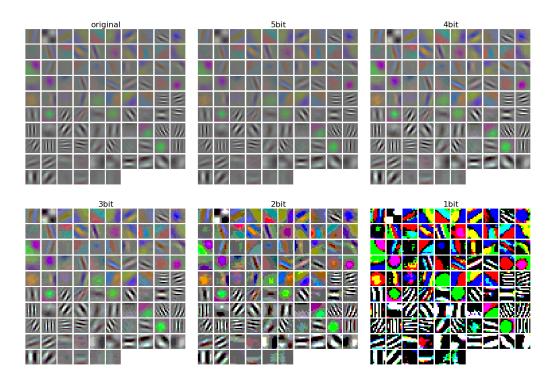

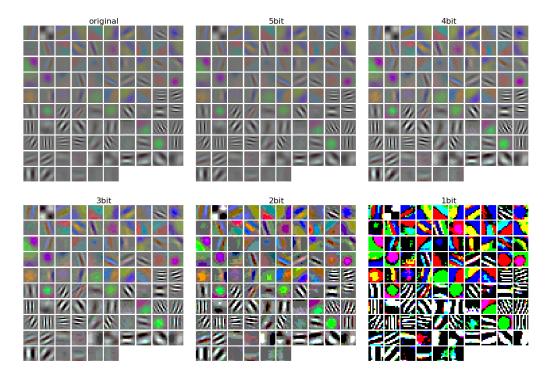

Πρακτικά η συμπίεση είναι μικρότερη. Αυτό γιατί το μικρότερο κομμάτι μνήμης που μπορεί να διευθυνσιοδοτηθεί είναι 8bits. Μια software λύση θα εισάγει παραπάνω καθυστέρηση στο σύστημα. Μια ουσιαστική λύση σε αυτό το πρόβλημα είναι υποστήριξη από ειδικό hardware (πχ. με fpga η asic) του sub byte indexing. Τέλος στο Σχ. 2.4 μπορούμε να δούμε πώς οι τιμές των βαρών αποκλίνουν σταδιακά από τις αρχικές τους τιμές.

**Σχήμα 2.4:** Τα βάρη του πρώτου επιπέδου του AlexNet καθώς χρησιμοποιούμε όλο και λιγότερα bit στην κβαντοποίηση.

# Κεφάλαιο 3

# Βελτιστοποίηση του inference για κβαντοποιημένα μοντέλα

Στο caffe δεν μπορούμε να αξιολογήσουμε τις επιπτώσεις στην απόδοση γιατί δεν υποστηρίζει πράξεις με κβαντοποιημένα βάρη. Έτσι δημιουργούμε κάποιες υλοποιήσεις του αλγορίθμου της συνέλιξης σε C++ για να τις μελετήσουμε. Το Clustering προκαλεί μη συνεχείς και μη κανονικές προσβάσεις στην μνήμη καθώς κάθε πρόσβαση είναι μία έμμεση αναφορά στην πραγματική τιμή του βάρους. Πρώτα βρίσκεται η τιμή που περιέχει το βάρος (που είναι index) και έπειτα βάση αυτής η κατάλληλη τιμή στο codebook. Αυτό καθιστά την πρόσβαση μνήμης τυχαία και είναι κακό τόσο για την επίδοση της cache όσο και για την δυνατότητα vectorization. Μελετάμε και προτείνουμε κάποιες νέες βελτιστοποιήσεις για να κρύψουμε ή να απαλείψουμε την καθυστέρηση που εισάγει το clustering.

## 3.1 Padding

Το padding μπορεί είτε να υλοποιηθεί όπως στον Αλγόριθμο 2, όπου με την συνθήκη "if" ελέγχεται εάν κάθε index είναι μέσα στα όρια του πίνακα εισόδου, είτε με πραγματική αλλαγή στις διαστάσεις της εισόδου όπως στον Αλγόριθμο 3.

#### Algorithm 2 Συνέλιξη με έλεγχο συνοριακών τιμών

- 1: **for** i = 0 to Cin 1 **do**

- 2: **for** j = 0 to Cout 1 **do**

- 3: **for** k = 0 to  $H_o 1$  **do**

- 4: **for** l = 0 to  $W_o 1$  **do**

- 5: **for** m = 0 to  $H_k 1$  **do**

- 6: **for** n = 0 to  $W_k 1$  **do**

- 7: **if**  $0 \le k_{in} < H_i$  and  $0 \le l_{in} < W_i$  then

- 8:  $k_{in} = stride \times k + m pad$

- 9:  $l_{in} = stride \times l + n pad$

- 10:  $Output[j][k][l] + = Input[i][k_{in}][l_{in}] \times Kernel[i][j][m][n]$

#### Algorithm 3 Συνέλιξη με αλλαγή διαστάσεων της εισόδου

- 1: **for** i = 0 to Cin 1 **do**

- 2: **for** j = 0 to Cout 1 **do**

- 3: **for** k = 0 to  $H_o 1$  **do**

- 4: **for** l = 0 to  $W_o 1$  **do**

- 5: **for** m = 0 to  $H_k 1$  **do**

- 6: **for** n = 0 to  $W_k 1$  **do**

- 7:  $k_{in} = stride \times k + m$

- 8:  $l_{in} = stride \times l + n$

- 9:  $Output[j][k][l] + = Input_{pad}[i][k_{in}][l_{in}] \times Kernel[i][j][m][n]$

## 3.2 Loop order

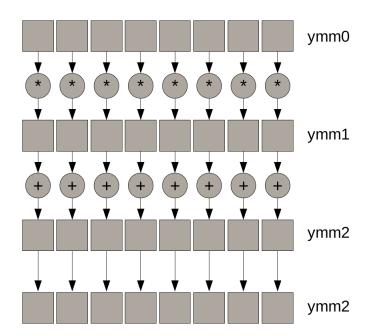

Ο αλγόριθμος της συνέλιξης δεν είναι πολύ αποδοτικός. Γι αυτό και τα δεδομένα της τροποποιούνται έτσι ώστε να μπορεί να υπολογιστεί με πολύ αποδοτικούς αλγορίθμους πολλαπλασιασμού πίνακα με πίνακα (GEMM). Αυτό για να επιτευχθεί πρέπει τα δεδομένα να αλλάξουν μορφή (μέθοδος im2col) κάτι που χρειάζεται παραπάνω μνήμη. Επίσης η απόδοση των GEMM με τις συνελίξεις δεν είναι η μέγιστη δυνατή λόγω των διαστάσεων των πινάκων. Σε αυτό το πρόβλημα μια λύση είναι η βελτιστοποίηση της αρχικής συνέλιξης τόσο ώστε η GEMM να μην είναι αναγκαία [56]. Αυτό το επιτυχγάνουν αλλάζοντας τη σειρά των loop στον αλγόριθμο, καθώς και τη σειρά των διαστάσεων των πινάκων. Αυτό φαίνεται στον Αλγόριθμο 4. Αυτή η σειρά εξασφαλίζει καλή επίδοση της cache καθώς έχουμε πολλές προσβάσεις σε συνεχείς θέσεις μνήμης. Επίσης δεν υπάρχουν εξαρτήσεις στο τελευταίο loop και επομένος μπορούν να χρησιμοποιηθούν Fused Multiply-Add(FMA) εντολές που κάνουν έναν πολλαπλασιασμό και μια πρόσθεση μαζί, και SIMD vectors που πραγματοποιούν πολλές εντολές ταυτόχρονα.

#### Algorithm 4 Συνέλιξη με αλλαγή της σειράς των loop

```

1: for k = 0 to H_o - 1 do

2: for m = 0 to H_k - 1 do

3: for n = 0 to W_k - 1 do

4: for i = 0 to Cin - 1 do

5: for l = 0 to W_o - 1 do

6: for j = 0 to Cout - 1 do

7: k_{in} = stride \times k + m

8: l_{in} = stride \times l + n

9: Output[k][l[j] + Input[i][k_{in}][l_{in}] \times Kernel[m][n][i][j]

```

## 3.3 Blocking

Όπως αναφέρθηκε πριν η συνέλιξη δεν είναι τόσο αποδοτική. Μια ακόμα πρόταση για την βελτίωσή της είναι η εφαρμογή blocking στα loops της ώστε να έχουμε αποδοτική επαναχρησιμοποίηση των δεδομένων και βέλτιστη χρήση των FMA SIMD εντολών [14] [56].

Βασιζόμενοι στα παραπάνω αναπτύξαμε τρεις εκδοχές blocking (αλγόριθμοι 12, 13 και 14). Η απόδοση μπορεί να βελτιωθεί αρχικά καθώς είναι εφικτό να καταφέρουμε να χωράει το working set στην cache. Για να κρύψουμε την καθυστέρηση  $L_{fma}$  των εντολών vector FMA με  $N_{vec}$  στοιχεία, πρέπει σε κάθε κύκλο να είναι διαθέσιμα και να εισάγονται τουλάχιστον  $L_{fma}N_{vec}$  ανεξάρτητα στοιχεία σε κάθε FMA unit. Παράλληλα πρέπει να εξασφαλίσουμε ότι τα διαθέσιμα στοιχεία δεν θα είναι τόσα πολλά ώστε να γεμίσουν όλοι οι SIMD καταχωρητές, για να αποφύγουμε το register spilling στη μνήμη. Βασιζόμενοι στα παραπάνω δοκιμάσαμε διάφορα μεγέθη και τελικά το κατάλληλο blocksize που

πληρεί τα παραπάνω και πειραματικά έχει την καλύτερη απόδοση φαίνεται στον Πίνακα 3.1

## Algorithm 5 Συνέλιξη με blocking στις χωρικές διαστάσεις

- 1:  $H_{ob} = H_o/Blocksize_H$

- 2:  $W_{ob} = W_o/Blocksize_W$

- 3: **for** i = 0 to Cin 1 **do**

- 4: **for** j = 0 to Cout 1 **do**

- 5: for  $k_b = 0$  to  $H_o 1$  step  $H_{ob}$  do

- 6: **for**  $l_b = 0$  to  $W_o 1$  step  $W_{ob}$  **do**

- 7: **for** m = 0 to  $H_k 1$  **do**

- 8: **for** n = 0 to  $W_k 1$  **do**

- 9: **for**  $k = k_b$  to  $H_{ob}$  **do**

- 10: **for**  $l = l_b$  to  $W_{ob}$  **do**

- 11:  $k_{in} = stride \times k + m$

- 12:  $l_{in} = stride \times l + n$

- 13:  $Output[j][k][l] + = Input_{pad}[i][k_{in}][l_{in}] \times Kernel[i][j][m][n]$

Πίνακας 3.1: Μεγέθη block

|        | $H_b$ | $W_b$ | $Cin_b$   | $Cout_b$    |

|--------|-------|-------|-----------|-------------|

| Αλγ. 5 | 16    | 16    | -         | -           |

| Αλγ. 6 | 8     | 16    | $N_{vec}$ | $N_{vec}$   |

| Αλγ. 7 | -     | 16    | 32        | $8*N_{vec}$ |

#### Algorithm 6 Συνέλιξη με blocking στις χωρικές διαστάσεις και στα channels

```

1: Cin_b = Cin/N_{vec}

2: Cout_b = Cout/N_{vec}

3: H_{ob} = H_o/Blocksize_H

4: W_{ob} = W_o/Blocksize_W

5: for i_b = 0 to Cin - 1 step Cin_b do

6: for j_b = 0 to Cout - 1 step Cout_b do

7: for k_b = 0 to H_o - 1 step H_{ob} do

8: for l_b = 0 to W_o - 1 step W_{ob} do

9:

for m=0 to H_k-1 do

10:

for = 0 to W_k - 1 do

11:

for i = i_b to N_{vec} do

12:

for j = j_b to N_{vec} do

for k = k_b to H_{ob} do

13:

for l = l_b to W_{ob} do

14:

15:

k_{in} = stride \times k + m

16:

l_{in} = stride \times l + n

17:

Output[j][k][l] += Input_{pad}[i][k_{in}][l_{in}] \times Kernel[i][j][m][n]

```

#### Algorithm 7 Συνέλιξη με αλλαγή της σειράς των loop και blocking

```

1: Cin_b = Cin/Blocksize_{Ci}

2: Cout_b = Cout/Blocksize_{Co}

3: W_{ob} = W_o/Blocksize_W

4: for j_b = 0 to Cout - 1 step Cout_b do

5: for i_b = 0 to Cin - 1 step Cin_b do

6: for k = 0 to H_o - 1 do

7: for l = 0 to W_o - 1 step W_{ob} do

for m=0 to H_k-1 do

8:

for n=0 to W_k-1 do

9:

10:

for i = i_b to Cin_b do

for l = l_b to W_{ob} do

11:

for j = j_b to Cout_b do

12:

13:

k_{in} = stride \times k + m

14:

l_{in} = stride \times l + n

15:

Output[k][l[j]] + = Input[i][k_{in}][l_{in}] \times Kernel[m][n][i][j]

```

## 3.4 Just In Time Compilation

Υπάρχουν περιπτώσεις που η απόδοση του προγράμματος εξαρτάται από παραμέτρους που γίνονται γνωστές αφού το πρόγραμμα ξεκινήσει να τρέχει (στο runtime). Για να μπορέσουμε να εκμεταλλευτούμε ότι γνωρίζουμε αυτές τις παραμέτρους και να βελτιστοποιήσουμε το πρόγραμμά μας χρησιμοποιούμε Just In Time (JIT) compilation. Το JIT compilation κάνει compile κομμάτια του προγράμματος, παράγει και εκτελεί εξειδικευμένο κώδικα βέλτιστο για τις συγκεκριμένες παραμέτρους.

Η συνέλιξη μπορεί να ωφεληθεί από την παραπάνω τεχνική καθώς μόλις γνωρίζουμε τις διαστάσεις και τις τιμές του πίνακα των βαρών καθώς και τα codebook αυτά δεν αλλάζουν καθ' όλη τη διάρκεια της εκτέλεσης και επομένως ο κώδικας μπορεί να βελτιστοποιηθεί. Χρησιμοποιούμε δύο ήδη υπάρχοντα framework για JIT και έπειτα επιχειρούμε μια δικιά μας υλοποίηση.

Χρησιμοποιούμε αρχικά το asmjit framework [27], το οποίο εκτελεί JIT με κώδικα x86-64 assembly. Βασιζόμενοι σε παρόμοια έρευνα με στόχο τους αραιούς πίνακες, [53] υλοποιούμε την συνέλιξη βγάζοντας κοινό παράγοντα τα codebook. Κάθε στοιχείο της συνέλιξης μπορεί να υπολογιστεί από τον εξής τύπο.

$$out[j][k][l] = \sum_{i=1}^{C_{in}} \sum_{m=1}^{W_k} \sum_{n=1}^{H_k} codebook[kernel[i][j][m][n]] \times Input[i][k_{in}][l_{in}]$$

(3.1)

Εάν ανοίξουμε τα αθροίσματα έχουμε το εξής:

$$out[j][k][l] = codebook[0] \times Input[1] + codebook[3] \times Input[2] + \\ + codebook[0] \times Input[6] \\ + codebook[2] \times Input[10] \\ +$$

Έπειτα βγάζοντας κάθε ένα codebook κοίνο παράγοντα:

$$out[j][k][l] = codebook[0] \times (Input[1] + Input[6] + ...)$$

$$+ codebook[1](Input[9] + ..)$$

$$+ ...$$

$$+ codebook[2^{bits} - 1](Input[14] + ..)$$

$$(3.3)$$

Τέλος για να μετατρέψουμε τον παραπάνω τύπο πάλι σε άθροισμα χρειάζεται να ξέρουμε ποια στοιχεία της εισόδου πολλαπλασιάζονται με ποιο codebook, ώστε να τα αθροίσουμε πρώτα όλα μαζί και να γλιτώσουμε πολλαπλασιασμούς. Αν αυτό υλοποιηθεί από έναν πίνακα m που περιέχει λίστες με τα στοιχεία που θα πολλαπλασιαστούν με κάθε codebook προκύπτει ο εξής τύπος.

$$out[j][k][l] = \sum_{i=0}^{2^{bits}-1} \left( codebook[i] \times \sum_{j=m[i].start}^{m[i].end} Input[j] \right)$$

(3.4)

Εμείς δημιουργούμε τέτοιο κώδικα στο runtime:

```

//add every input mapped to codebook[0]

xorps xmm1, xmm1 //sum=0

vaddss xmm1, xmm1, [rcx+4] //sum+=input[1]

vaddss xmm1, xmm1, [rcx+32] //sum+=input[8]

...

vfmadd231ss xmm2, xmm1, [rdx] //out[index]+=codebook[0]*sum

//add every input mapped to codebook[1]

xorps xmm1, xmm1 //sum=0

vaddss xmm1, xmm1, [rcx+8] //sum+=input[2]

vaddss xmm1, xmm1, [rcx+52] //sum+=input[13]

...

//perform scalar fused multiply add

vfmadd231ss xmm2, xmm1, [rdx+4] //out[index]+=codebook[1]*sum

...

//repeat for all codebook elements

```

Στη συνέχεια χρησιμοποιούμε το easyjit[3] framework το οποίο χρησιμοποιεί τον compiler clang ώστε να βελτιστοποιήσει μια συνάρτηση καθώς τρέχει το πρόγραμμα. Το μόνο που χρειάζεται είναι να του παρέχουμε τις παραμέτρους της συνάρτησης που θέλουμε να βελτιστοποιήσει. Αυτό μας επιστρέφει έναν function pointer στην βελτιστοποιημένη συνάρτηση από τον οποίο μπορούμε να την καλέσουμε με τις υπόλοιπες παραμέτρους.

Αυτή η υλοποίηση είναι πολύ εύκολη και δεν χρειάζεται πολλές γνώσεις πάνω στο θέμα για να χρησιμοποιηθεί.

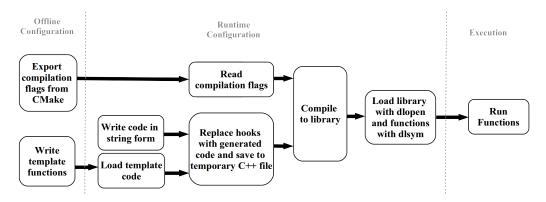

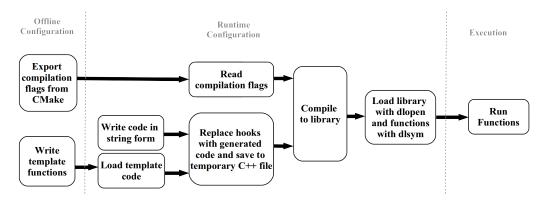

Τέλος επειδή οι δύο αυτές υλοποιήσεις δεν κάλυπταν τις ανάγκες μας σε επίπεδο ευκολίας χρήσης αλλα και ελευθερία επεξεργασίας του κώδικα υλοποιήσαμε μια βιβλιοθήκη που δημιουργεί, κάνει compile, και εκτελεί συναρτήσεις στο runtime. Αρχικά τα compiler options εξάγονται κατα το build. Έπειτα γράφουμε κώδικα C++ στο πρόγραμμά μας σε μορφή string ή/και χρησιμοποιούμε αποθηκευμένα templates για συντομία. Τα templates έχουν hooks τα οποία μπορούμε να αντικαταστήσουμε με stings στο runtime. Έπειτα το πρόγραμμα αποθηκεύεται σε ένα προσωρινό αρχείο για να γίνει compile. Τέλος το κάνουμε load με τη συνάρτηση dlopen και χρησιμοποιούμε τις συναρτήσεις του με την dlsym. Η διαδικασία αυτή φαίνεται σχηματικά στο Σχ. 3.1.

Σχήμα 3.1: Δημιουργία- Compile- Εκτέλεση κώδικα

## 3.5 Loop unrolling

Το loop unrolling μπορεί να βελτιώσει την απόδοση της συνέλιξης καθώς ελέγχεται πιο σπάνια η συνθήκη εξόδου από το loop. Επίσης ο compiler μπορεί να βελτιστοποιήσει καλύτερα τον κώδικα. Ο τρόπος δημιουργίας κώδικα στο runtime που αναφέραμε παραπάνω μας επιτρέπει να κάνουμε unroll όλο το kernel της συνάρτησης. Επίσης χρησιμοποιούμε ενδιάμεσες μεταβλητές ως παράλληλους accumulators κάτι που επιτρέπει στον compiler να κάνει ακόμα περισσότερες βελτιστοποιήσεις.

## 3.6 Unique filters

Μετά τον αλγόριθμο k-means είναι πιθανό πολλά kernels να επαναλαμβάνονται. Αυτό μπορούμε να το εκμεταλλευτούμε και να δημιουργήσουμε μία συνάρτηση για κάθε kernel. Καθώς μπορούμε να δημιουργήσουμε κώδικα στο runtime μπορούμε να τυπώσουμε τις τιμές των codebooks και έτσι να μην υπάρχουν πλέον έμμεσες αναφορές στα βάρη. Ακόμη μπορούμε να εκτελέσουμε τις πράξεις βγάζοντας κοινό παράγοντα στη λογική της εξίσωσης 3.4. Συγκρίνουμε τα αποτελέσματα με υλοποιήσεις με κανονικούς πολλαπλασιασμούς.

## 3.7 Αποτελέσματα

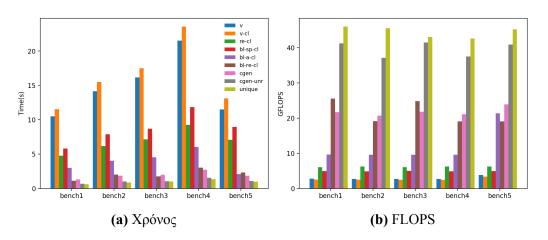

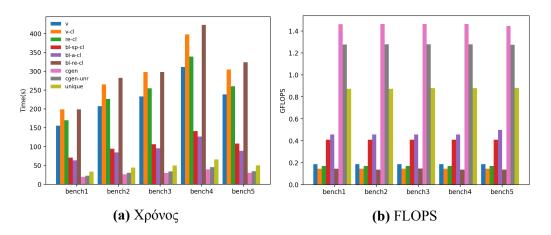

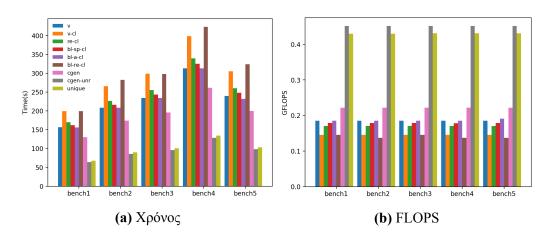

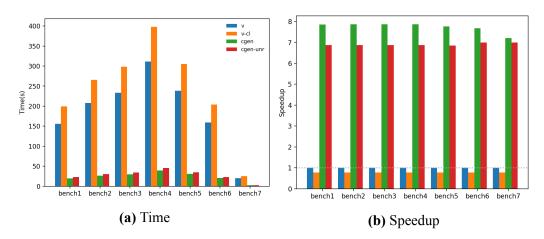

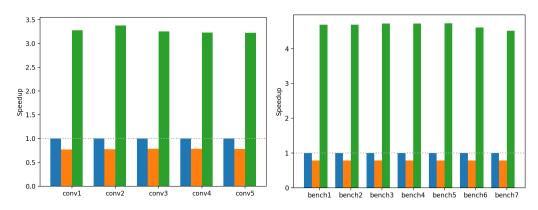

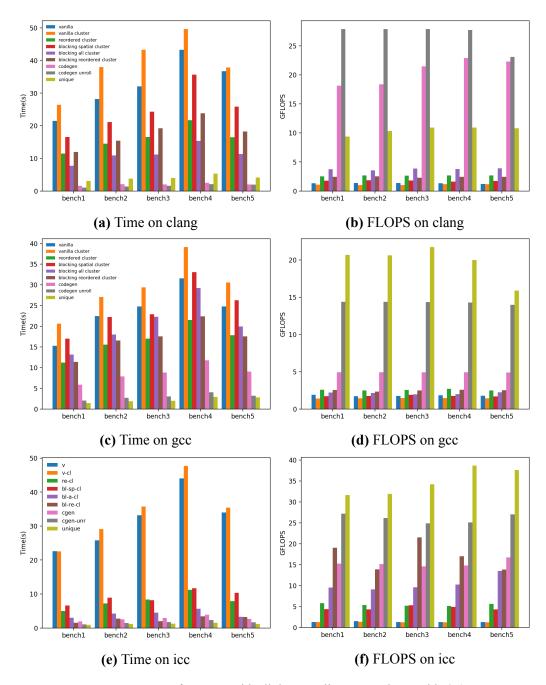

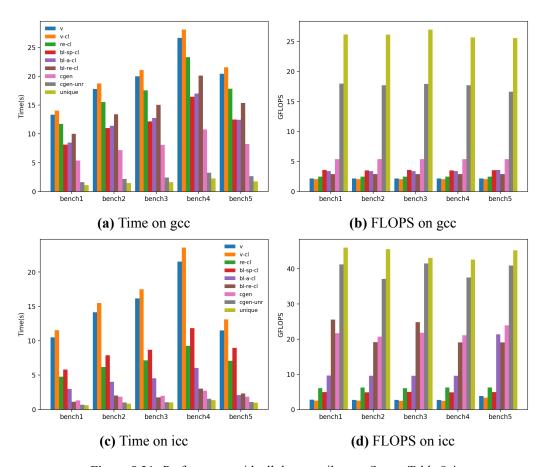

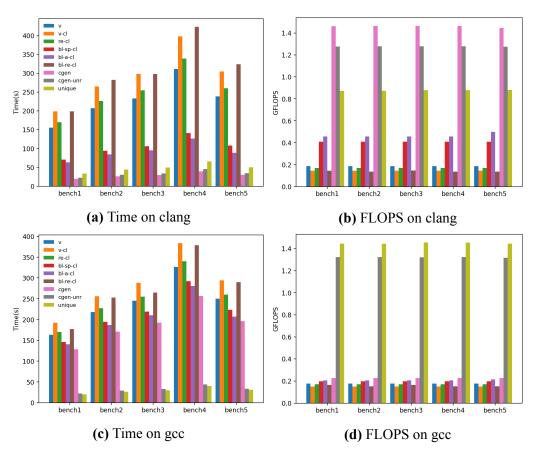

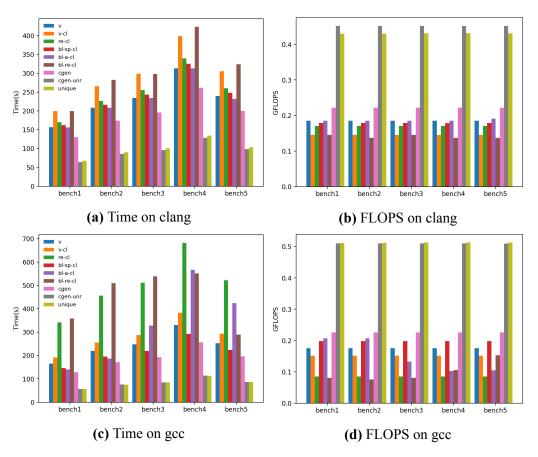

Φτιάξαμε benchmarks πάνω στα οποία θα αξιολογήσουμε τις υλοποιήσεις. Θα λάβουμε τα αποτελέσματα στα μηχανήματα του Πίνακα 3.2. Τα benchmarks περιγράφονται στους Πίνακες 3.4 3.5 και 3.6. 'Ως μετρικές θα χρησιμοποιήσουμε τον χρόνο εκτέλεσης, το Speedup και τα FLOPS. Φροντίσαμε επίσης να ενεργοποιήσουμε το vectorization αλλά και τα unsafe math optimizations.

Πίνακας 3.2: Machine specifications.

| Type    | Computer          | OS           | CPU               | RAM   |

|---------|-------------------|--------------|-------------------|-------|

| Server  |                   | Ubuntu 18.04 | 2x Xeon Gold 5218 | 314GB |

| Desktop | Ideapad 510-15ikb | Ubuntu 16.04 | i7-7500U          | 8GB   |

| Edge    | Raspberry Pi 3 B+ | Ubuntu 18.04 | Cortex A53        | 1GB   |

Πίνακας 3.3: CPU specifications.

| CPU            | arch    | speed  | cores/  | L1,L2,L3      | misc    |

|----------------|---------|--------|---------|---------------|---------|

|                |         |        | threads |               |         |

| Xeon Gold 5218 | x86-64  | 3.9GHz | 16-32   | 32K, 1M, 22M  | avx-512 |

| i7-7500U       | x86-64  | 3.5GHz | 2-4     | 32K, 256K, 4M | avx2    |

| Arm Cortex A53 | aarch64 | 1.4GHz | 4-4     | 16K, 512K     | neon    |

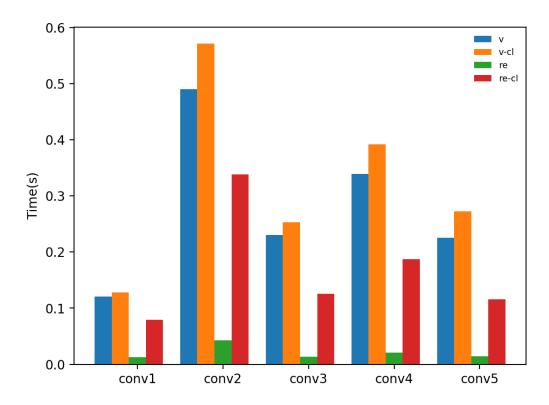

Πίνακας 3.4: Benchmark με τις συνελίξεις του AlexNet.

|       | $C_{in}$ | $H_{in}$ | $W_{in}$ | $C_{out}$ | $H_k$ | $W_k$ | stride | pad |

|-------|----------|----------|----------|-----------|-------|-------|--------|-----|

| conv1 | 3        | 227      | 227      | 96        | 11    | 11    | 4      | no  |

| conv2 | 96       | 27       | 27       | 256       | 5     | 5     | 1      | yes |

| conv3 | 256      | 13       | 13       | 384       | 3     | 3     | 1      | yes |

| conv4 | 384      | 13       | 13       | 384       | 3     | 3     | 1      | yes |

| conv5 | 384      | 13       | 13       | 256       | 3     | 3     | 1      | yes |

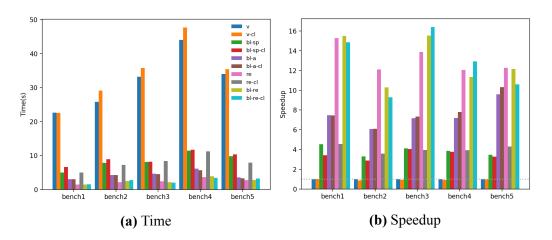

Πίνακας 3.5: Benchmark με μεγάλες συνελίξεις.

|        | $C_{in}$ | $H_{in}$ | $W_{in}$ | $C_{out}$ | $H_k$ | $W_k$ | stride | pad |

|--------|----------|----------|----------|-----------|-------|-------|--------|-----|

| bench1 | 256      | 128      | 128      | 384       | 3     | 3     | 1      | yes |

| bench2 | 256      | 128      | 128      | 512       | 3     | 3     | 1      | yes |

| bench3 | 384      | 128      | 128      | 384       | 3     | 3     | 1      | yes |

| bench4 | 384      | 128      | 128      | 512       | 3     | 3     | 1      | yes |

| bench5 | 384      | 112      | 112      | 512       | 3     | 3     | 1      | yes |

| bench6 | 512      | 56       | 56       | 1024      | 3     | 3     | 1      | yes |

| bench7 | 512      | 28       | 28       | 512       | 3     | 3     | 1      | yes |

**Πίνακας 3.6:** Benchmark που στοχεύει το τελευταίο επίπεδο cache στα μηχανήματα του Πίνακα 3.2

|         | $C_{in}$ | $H_{in}$ | $W_{in}$ | $C_{out}$ | $H_k$ | $ W_k $ | stride | pad | memory |

|---------|----------|----------|----------|-----------|-------|---------|--------|-----|--------|

| Server  | 512      | 32       | 32       | 512       | 3     | 3       | 1      | yes | 13MB   |

| (22MB)  | 512      | 32       | 32       | 1024      | 3     | 3       | 1      | yes | 24MB   |

| Desktop | 128      | 32       | 32       | 256       | 3     | 3       | 1      | yes | 2.5MB  |

| (4MB)   | 128      | 32       | 32       | 768       | 3     | 3       | 1      | yes | 7MB    |

| Edge    | 64       | 16       | 16       | 128       | 3     | 3       | 1      | yes | 481KB  |

| (512KB) | 64       | 16       | 16       | 256       | 3     | 3       | 1      | yes | 609KB  |

Πίνακας 3.7: Υλοποιήσεις και ονόματα στα διαγράμματα

| Implementation                | Name     | Implementation           | Name     |

|-------------------------------|----------|--------------------------|----------|

| Vanilla convolution           | V        | Block reordered Cluster  | bl-re-cl |

| Vanilla convolution (cluster) | v-cl     | Asmjit                   | asmjit   |

| Soft padding                  | sft      | Asmjit Vectorized        | asmjit-v |

| Soft padding cluster          | sft-cl   | Unique filters           | unique   |

| Reordered                     | re       | Unique filters hardcoded | hard     |

| Reordered cluster             | re-cl    | Unique filters iterator  | iter     |

| Block Spatial                 | bl-sp    | Unique filters loop      | loop     |

| Block spatial cluster         | bl-sp-cl | Codegenv vanilla         | cgen     |

| Block all dimensions          | bl-a     | Codegen unroll           | cgen-unr |

| Block all dimensions cluster  | bl-a-cl  | BLAS im2col              | im2col   |

| Block reordered               | bl-re    |                          |          |

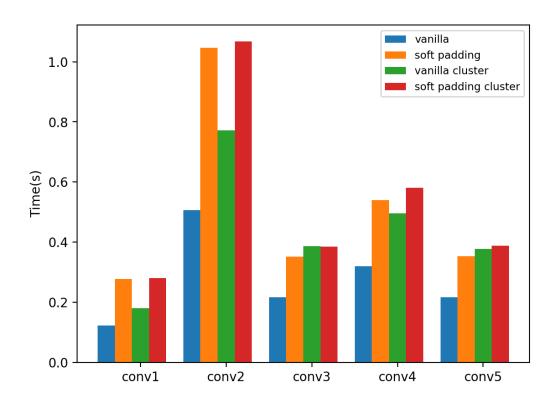

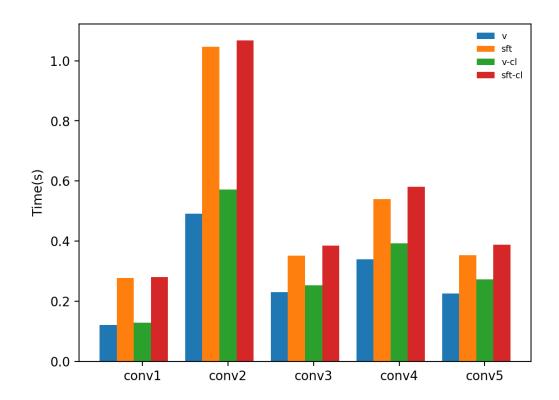

Το padding φαίνεται να επηρρεάζει την απόδοση. Από το Σχ. 3.2. Η μέθοδος του Αλγ. 2 φαίνεται να εισάγει περισσότερες καθυστερήσεις καθώς ελέγχει σε κάθε επανάληψη τις συνοριακές τιμές. Επομένως θα χρησιμοποιήσουμε τον Αλγ. 3 απο δω και στο εξής.

**Σχήμα 3.2:** Σύγκριση τεχνικών padding στην απλή συνέλιξη και στη συνέλιξη με clustering (Benchmark 8.3 στο μηχάνημα Desktop)

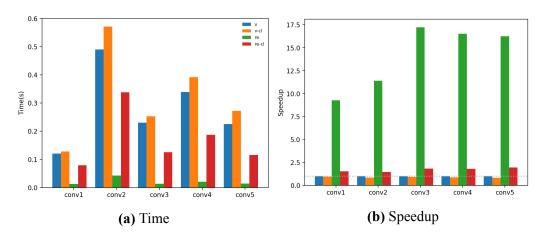

Παρατηρούμε στη συνέχεια πως ο Αλγ. 4 βελτιώνει την συνέλιξη. Βέβαια όπως μπορούμε να δούμε στο Σχ. 3.3 η cluster εκδοχή δεν βελτιώνεται τόσο, κάτι που μπορεί να αποδοθεί στις ακανόνιστες προσβάσεις μνήμης που προκαλεί το clustering.

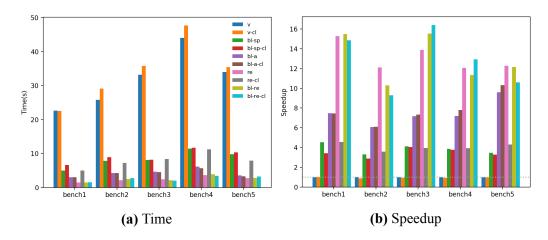

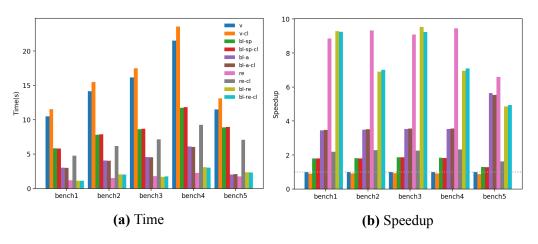

Στη συνέχεια αξιολογούμε τις blocking υλοποιήσει όπου παρατηρούμε πως στα μηχανήματα Server και Desktop η απόδοση βελτιώνεται αισθητά στις blocking εκδοχές. Το blocking απλά στις χωρικές διαστάσεις φέρνει μια μέτρια βελτίωση αλλά οι Αλγόριθμοι 6 και 7 επιφέρουν πολύ μεγαλύτερη. Αυτό είναι αναμενόμενο καθώς το blocking στα channels είναι που επιτρέπει την καλύτερη αξιοποίηση των FMA units καθώς έχουμε περισσότερη ελευθερία στην επιλογή block size. Η βελτίωση είναι τόσο σημαντική που η cluster και η non cluster εκδοχές έχουν την ίδια υψηλή απόδοση. Αυτό συμβαίνει ακόμα και στον Αλγ. 7 πράγμα που δεν συνέβαινε στον Αλγ. 4 όπως είδαμε παραπάνω.

Στο μηχάνημα Edge ναι μεν το blocking βελτιώνει την απόδοση αλλά όχι στον ίδιο βαθμό με τα προηγούμενα. Παρατηρούμε ότι σε αντίθεση με παραπάνω οι cluster και non cluster υλοποιήσεις δεν είναι κοντά σε επίπεδο απόδοσης. Αυτό μπορεί να οφείλεται στις διαφορές στον compiler καθώς και στο μικρότερο vector length που παρουσιάζει το

μηχάνημα. Παρατηρούμε επίσης από τα παραπάνω ότι καθώς αυξάνεται το vector length αυξάνεται και η απόδοση των blocking υλοποιήσεων.

Σχήμα 3.3: Reordered εκδοχή συνέλιξης με και χωρίς clustering στο Desktop και Benchmark 3.4.

**Σχήμα 3.4:** Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πίνακας 3.5 στο μηχάνημα Desktop)

Σχήμα 3.5: Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πίνακας 3.5 στο μηχάνημα Server)

**Σχήμα 3.6:** Επίδοση των blocking υλοποιήσεων και των αντίστοιχων μη blocking (Πίνακας 3.5 στο μηχάνημα Edge)

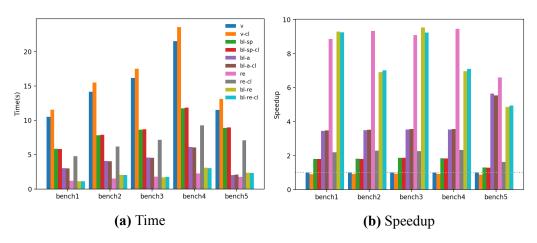

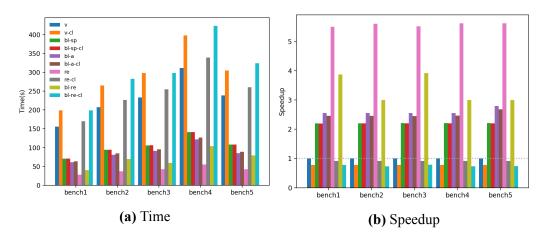

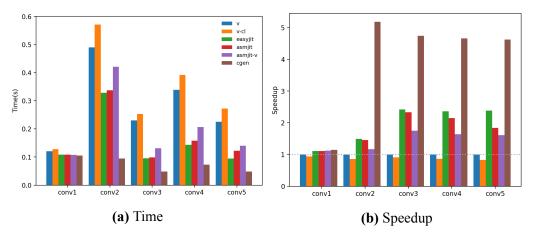

Στη συνέχεια αξιολογούμε και συγκρίνουμε τις JIT υλοποιήσεις με την αρχική συνέλιξη αλλά και μεταξύ τους. Από το Σχ. 3.7 παρατηρούμε πως η υλοποίηση του asmjit έχει περιορισμένη χρησιμότητα στην περίπτωσή μας. Επιτυγχάνει αποτελέσματα συγκρίσιμα με το easyjit αλλά με πολύ κόπο από τη πλευρά του προγραμματιστή. Παραπάνω βελτιστοποιήσεις και vectorization εξαρτώνται επίσης από τις ικανότητες του χρήστη. Τα παραπάνω σε συνδυασμό με την μεγάλη χρήση RAM για μεγάλα benchmarks δεν τη κάνει κατάλληλη για το πρόβλημά μας. Επίσης δεν φαίνεται να κερδίζουμε κάτι σε άποψη χρόνου από τους κοινούς παράγοντες της Εξ. 3.4. Αυτό μπορεί να ερμηνευθεί λόγω της διαφορετικής αρχιτεκτονικής του προβλήματός μας αλλά και από την χρήση από εμάς, νectorizes εντολών, όπου ο πολλαπλασιασμός και η πρόσθεση έχουν την ίδια καθυστέρηση. Το Easyjit αν και απλούστερο στη χρήση έχει τα μειονεκτήματά του. Μπορεί να βελτιστοποιήσει συναρτήσεις που έχουν αποκλειστικά C++ fundamental data types και δεν έχουμε έλεγχο στις βελτιστοποιήσεις.

Η απλή εκδοχή της δημιουργίας κώδικα (codegen) πρακτικά πραγματοποιεί ότι και το easyjit. Έχει όμως καλύτερη απόδοση γιατί μπορούμε να επέμβουμε πιο άμεσα στον κώδικα και να επιλέξουμε μόνοι μας τα κατάλληλα compilation flags. Επομένως καταλήγουμε στο ότι θα χρησιμοποιήσουμε την δική μας βιβλιοθήκη στις επόμενες συγκρίσεις. Την υλοποίηση αυτή συγκρίνουμε έπειτα με την πιο περίπλοκη unrolling εκδοχή της (Σχ 3.8). Οπως ήταν αναμενόμενο είναι καλύτερη, καθώς λόγω του unrolling ο compiler έχει περισσότερες ευκαιρίες για βελτιστοποιήσεις και παραλληλοποιήσεις.

**Σχήμα 3.7:** Απόδοση των vanilla, cluster asmjit and easyjit υλοποιήσεων στο Benchmark 8.3 στο Desktop

**Σχήμα 3.8:** Σύγκριση των jit υλοποιήσεων με την βιβλιοθήκη μας στο benchmark 8.4 στο μηχάνημα Desktop.

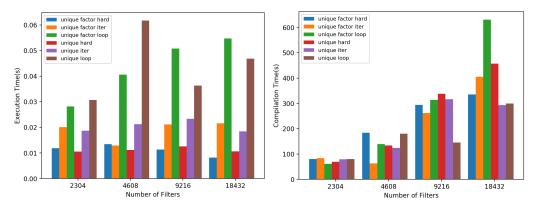

Κάθε unique filter έχει την δική του συνάρτηση. Καθώς ο αριθμός των φίλτρων αυξάνει περιμένουμε ο χρόνο για compile να αυξάνεται. Από το Σχ. 3.9 παρατηρούμε πως αν και όλες οι εκδοχές έχουν περίπου την ίδια απόδοση, η hard coded είναι ελαφρώς καλύτερη. Παρατηρούμε επίσης ξανά πως δεν κερδίζουμε κάτι από τον κοινό παράγοντα για τους λόγους που αναφέραμε παραπάνω.

Σχήμα 3.9: Χρόνος συναρτήσει αριθμού kernel

Σχήμα 3.10: Σύγκριση unique filters στα benchmark 8.3 και 8.4 στο Desktop

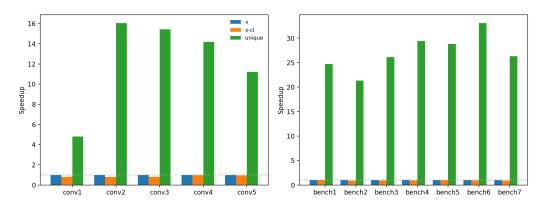

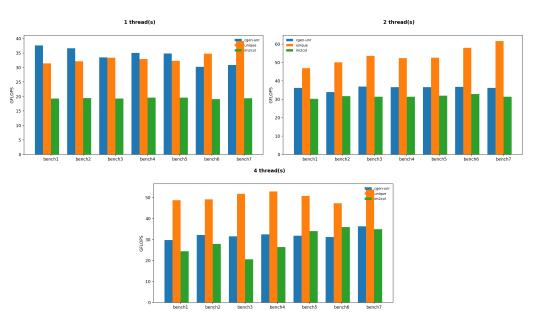

Αξίζει να σημειωθεί πως από τους compiler που δοκιμάσαμε ο icc παρήγαγε τον πιο αποδοτικό κώδικα. Στη συνέχεια ο clang και τέλος ο gcc. Αυτό οφείλεται στην ικανότητά τους να κάνουν vectorize η όχι κάθε υλοποίηση. Στη συνέχεια εξετάζουμε συγκεντρωτικά τα αποτελέσματα για τις παραπάνω υλοποιήσεις ώστε να εξάγουμε συμπεράσματα. Παρατηρούμε πως οι unique και unrolling υλοποιήσεις είναι οι πιο αποδοτικές στο Desktop και Server (Σχ. 3.11 και 3.12) Παρατηρούμε επίσης πως ο Server έχει ελαφρώς καλύτερη απόδοση πιθανών λόγω του ανχ-512 εναντι του ανχ2 του Desktop. Απο την άλλη στο μηχάνημα Edge παρατηρούμε από το σχήμα 3.13 πως η απλή codegen είναι καλύτερη. Αυτό είναι πολύ πιθανό να οφείλεται στο μικρότερο vector length του επεξεργαστή, καθώς και στη χρήση του clang compiler. Τέλος χωρίς vectorization στο ίδιο μηχάνημα (Σχήμα 3.14) οι unique και unroll αποδίδουν καλύτερα.

**Σχήμα 3.11:** Συγκεντρωτικά η απόδοση στο Desktop για το benchmark 8.4

**Σχήμα 3.12:** Συγκεντρωτικά η απόδοση στο Server για το benchmark 8.4

Σχήμα 3.13: Συγκεντρωτικά η απόδοση στο Edge μηχάνημα για το benchmark 8.4

Σχήμα 3.14: Απόδοση στο Edge μηχάνημα χωρίς vectorization για το benchmark 8.4

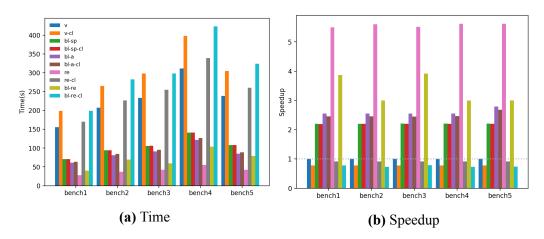

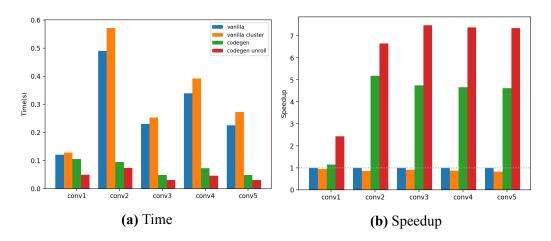

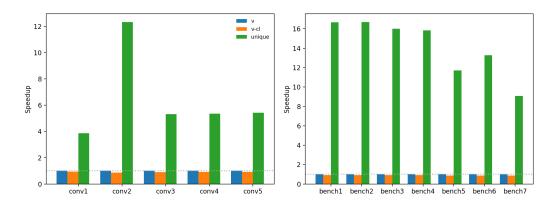

Τέλος για τις υλοποιήσεις με clustering που ξεχώρισαν με την απόδοσή τους, την codegen unrolling και την unique filters, εξετάζουμε τι απόδοση έχουν σε πολυπύρηνο περιβάλλον με μια απλή υλοποίηση OpenMP. Ταυτόχρονα τις συγκρίνουμε με την παραδοσιακή υλοποίηση για non clustering συνελίξεις, όπου πρώτα οι πίνακες μετασχηματίζονται σε 2-D ώστε να υπολογιστεί η έξοδος με πολλαπλασιασμό πινάκων από υψηλής απόδοσης GEMM functions. Παρατηρούμε αρχικά από το σχήμα 3.15 ότι η απόδοση των υλοποιήσεών μας είναι συγκρίσιμη με την GEMM υλοποίηση. καθώς τα threads αυξάνονται μεν υπάρχουν αυξομειώσεις αλλά η απόδοσή τους κλιμακώνει περίπου παρόμοια με την GEMM υλοποίηση. Επίσης παρατηρούμε πως η unrolling εκδοχή κλιμακώνει καλύτερα από την unique.

**Σχήμα 3.15:** Παράλληλη απόδοση του Server στο benchmark 8.4

## Κεφάλαιο 4

# Συμπεράσματα και μελλοντικές προεκτάσεις

Σε αυτή τη διπλωματική αρχικά μελετήσαμε τα αποτελέσματα το clustering ως μέθοδο συμπίεσης DNNs και διαπιστώσαμε πως επιφέρει καλά αποτελέσματα στην συμπίεση και ταυτόχρονα στη διατήρηση της ακρίβειας του μοντέλου. Παρ' όλ' αυτά εισάγει χρονικές καθυστερήσεις κάτι που οφείλεται στον ακανόνιστο τρόπο με τον οποίο προσπελάζεται η μνήμη. Οι έμμεσες αναφορές στη μνήμη είναι η κύρια πηγή για την κακή χρονική απόδοση καθώς μειώνει την τοπικότητα των δεδομένων και την δυνατότητα vectorization.

Στη συνέχεια επικεντρωθήκαμε στην ελαχιστοποίηση των καθυστερήσεων λόγω του clustering. Πειραματιστήκαμε με διάφορες τεχνικές βελτίωσης ώστε να κρύψουμε τις καθυστερήσεις. Χρησιμοποιήσαμε loop reordering και loop blocking. Τα αποτελέσματα δείχνουν πως με αυτές τις τεχνικές είναι εφικτό να πετύχουμε μια αρκετά μεγάλη αύξηση στην απόδοση. Οι τεχνικές αυτές στηρίζονται κυρίως στην ύπαρξη SIMD εντολών και είναι κατα συνέπεια χρήσιμες σε ισχυρούς υπολογιστές.

Στη συνέχεια πειραματιστήκαμε με Just In Time compilation. Προσαρμόσαμε τον αλγόριθμο της συνέλιξης και είδαμε αύξηση στην χρονική απόδοση. Χρησιμοποιήσαμε δύο framework για το παραπάνω, αλλά κάθε ένα είχε τους δικούς του περιορισμούς. Έτσι αναπτύξαμε μια δική μας βιβλιοθήκη παραγωγής και εκτέλεσης κώδικα στο runtime, που κάλυπτε τις ανάγκες μας και έτσι ήταν εφικτό να παράξουμε υλοποιήσεις που είχαν καλύτερη απόδοση από τα προηγούμενα framework. Οι υλοποιήσεις αυτές μπορούν να χρησιμοποιηθούν σε διάφορες πλατφόρμες αλλά συστήματα με λίγες υπολογιστικές ικανότητες θα ωφεληθούν περισσότερο.

Τέλος με την παραπάνω βιβλιοθήκη είχαμε την ελευθερία να απαλείψουμε όλες της έμμεσες αναφορές. Αυτό βελτίωσε σημαντικά την απόδοση σε όλα τα συστήματα. Το μειονέκτημα είναι πως χρειάζεται μικρός αριθμός kernels για να είναι κάτι τέτοιο εφικτό.

Συγκεντρωτικά σε αυτή τη διπλωματική καταφέραμε να συμπιέσουμε DNN μοντέλα έως και 6.4x χωρίς πτώση της ακρίβειάς τους. Ταυτόχρόνα, μέσω του JIT compilation, καταφέραμε να διατηρήσουν και την ταχύτητά τους χωρίς το memory overhead των GEMM convolutions

Τα αποτελέσματα της διπλωματικής αυτής μπορούν να προεκταθούν σε πολλές κατευθύνσεις. Αρχικά κάθε βελτιστοποίηση της συνέλιξης μπορεί να προσαρμοστεί για βήμα του back propagation της εκπαίδευσης των DNNs. Τα loops και στις δύο περιπτώσεις είναι παρόμοια και οι βελτιστοποιήσεις θα έχουν κατά πάσα πιθανότητα παρόμοια αποτελέσματα.

Η βιβλιοθήκη που αναπτύξαμε χρησιμοποιήθηκε για να κάνει compile κάποιες παραμέτρους μέσα στη συνέλιξη αλλά και για να κάνουμε unroll τα loops του kernel. Με την ελευθερία που παρέχει η βιβλιοθήκη αυτή μπορεί η βελτιστοποίηση να πάει ένα βήμα παραπάνω με πιο fine grained λύσεις στο πρόβλημα είτε στοχεύοντας συγκεκριμένα μεγέθη kernel, είτε με πιο περίπλοκα loop transformations. Ακόμα έχει ενδιαφέρων η χρήση αυτών των βελτιστοποιήσεων σε παράλληλα περιβάλλοντα όπως οι GPUs.

Τέλος τεχνικές που μειώνουν τα μοναδικά kernels ως μέθοδο συμπίεσης υπάρχουν ήδη και μπορούν να ωφεληθούν από τη δουλεία μας. Συγκεκριμένα αυτές οι δουλειές επικεντρώνονται στο να λύσουν το πρόβλημα των περιορισμών μνήμης των ενσωματωμένων συσκευών. Οι συσκευές αυτές συνήθως έχουν και χαμηλή υπολογιστική ικανότητα κάτι στο οποίο θα μπορούσε να βοηθήσει η υλοποίηση με τα μοναδικά kernel.

## Chapter 5

## Introduction

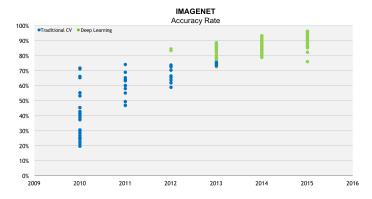

Machine Learning applications today are becoming widely used and integrated in products and services (e.g. recommendation algorithms for products or movies). In particular, Deep Learning has become one of the most researched technologies, achieving near equal or even better performance than humans for specific tasks. The architecture behind Deep Learning is called Deep Neural Networks (DNNs). Although they were invented in the 1980s, their breakthrough was in the 2000s. At that time, the advances on graphics processing units (GPUs) resulted in a huge increase of computational capabilities. Using GPUs allowed for fast implementations of the computationally intensive DNN training. In the recent years DNNs have shown significant improvements in many AI applications. A particular class of DNNs called Convolutional Neural Networks (CNNs) dominate the domain of computer vision by achieving state of the art accuracy on tasks such as image classification[28] (Fig. 5.1), object recognition [39] and image segmentation [32]. CNNs have already surpassed traditional computer vision techniques as seen (Fig. 5.2). The general tendency for improving the accuracy performance of such networks has been to design networks with more layers (deeper) and more sophisticated architecture. However, as the networks grow larger and larger, this improvement comes at the cost of high memory consumption, computational requirements and energy consumption. For example AlexNet [28], has 62.3 million parameters, and needs 1.1 billion operations for the inference of a single image.

The high performance of DNNs and CNNs in particular has created the demand for such applications to be integrated on various embedded devices such as smart phones, IoT devices, and self driving cars [48]. The high memory and computational requirements can be easily satisfied by server grade and even some consumer grade computers but such demands are way over the range of the capabilities of most embedded devices due to their low memory, limited computational power and energy constraints. Therefore the deployment of such DNNs, as they are, is prohibitive on such devices. The need to utilize such models on resource limited devices has sparked a research effort to overcome the above limitations .

One approach is to design compact model architectures from scratch. Examples of this is using more efficient convolution blocks such as multi branched convolutions [45]

```

'n02123045 tabby, tabby cat'),

[(0.31244642,

(0.23797025,

'n02123159 tiger cat'),

'n02124075 Egyptian cat'),

(0.12387885,

(0.10075199, 'n02119022 red fox, Vulpes vulpes'),

(0.070957005,

'n02127052 lynx, catamount')]

50

100

150

200

250

300

350

100

300

```

Figure 5.1: Example of image classification using CNN

[19], bottleneck convolutions[19] and depthwise separable convolutions [7] [23].

Another approach works by compressing existing models trained on powerful machines (e.g. GPU clusters) and then deploy them on resource limited devices with minimal accuracy loss (Fig. 5.3). This is based on the fact that contemporary big DNNs (Fig. 5.4) have significant redundancy in weights. This wastes both computational power and memory because not all of their numerous parameters are needed to correctly perform their tasks. Hence the the efforts on making the models smaller have been focused on having less weights and having less numerical accuracy. This is mainly achieved with connection pruning and quantization.

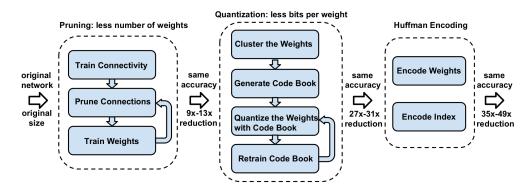

Quantization and pruning address different sources of redundancy on the models [55]. They are therefore complementary to each other and they even work better when combined, as first reported by Han et al. [18]. Their work is of the most thorough methods to compress DNNs for deployment on low resource devices. They propose a three stage compression pipeline consisting of pruning, quantization and Huffman encoding (Fig. 5.5). The three methods are complementary and can be used on top of each other. The combined techniques implemented, resulted in a 35x times reduction in size of the model.

Connection pruning removes less contributing neurons altogether to induce sparsity to a network. There are different approaches and criteria to determine which neurons are less important and therefore must be pruned. Some works prune individual weights [17] [2], others whole channels [49] [20] and others even whole filters [15] [49] [51].

Quantization is a process of converting a range of input values into a smaller set of output values that closely approximates the original data. Quantization uses fewer bits to represent each weight value of the neurons. This results in the quantized weights deviating from their original values. This deviation produces noise, which can be tolerated up to a point, since DNNs are trained to be robust against noise. Quantizaton is the main focus of

#### DEEP LEARNING FOR VISUAL PERCEPTION

Going from strength to strength

Figure 5.2: Performance of traditional computer vision vs Deep Learning

this thesis. A lot of research has focused on this subject which is mentioned in detail in the following section.

Figure 5.3: Train on powerful GPUs, compress and then deploy on embedded devices

**Figure 5.4:** Top1 accuracy vs operations. The size of the blobs is proportional to the number of network parameters [4]

Figure 5.5: Deep compression pipeline [18]

#### 5.1 DNN Quantization

Quantization focuses on using fewer bits to represent each the weight value of the neurons. The various quantization attempts mainly follow two paths to achieve reduced numerical precision and bit width of weights.

Some works focus on limiting the numerical precision of the parameters by converting floating point numbers to low precision fixed point number. These are called fixed point representations. To better represent the original numbers they take into account the distribution of the values being quantized by using dynamic fixed point. Fixed point quantization is a uniform quantization method. This means that the intervals between each quantized value are the same. Milde et al. [34] created a low-precision add-on for the Caffe framework [26] that rounds floating point values and represents them with integers for both the decimal and fractal part. They used this technique to quantize weights and activations. Shin et al. [42] optimizes fixed point representation by calculating iteratively the quantization step for better representing the dynamic range of weights. Miyashita et al. [36] used base-2 logarithmic representation of models. This way multiplications were replaced by cheaper shift operations. More aggressive attempts for quantization use even ternary [58] and binary weights [31] [8] [35] [21].

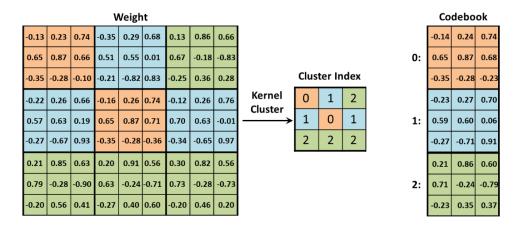

On the other hand some works achieve using fewer parameters by using indexed representations. The weights are grouped together by some criteria and each group represented by one value. These methods may not affect numeric precision, but they limit the available full precision numbers. Chen et al. [6] reduces the bitwidth needed to store the weights using a hash function to group weights into hash tables. The grouping is not optimal because it is random and thus doesn't take into account the weight values across the layer. This problem is addressed and overcome by Han et al. [18] by using k-means clustering to group weights together. In contrast with the previous work [6] this technique groups similar weight values together and therefore achieves better accuracy. For their experiments they achieve minimal accuracy loss while using as low as 5 bits for indexing. Other works experiment with k means clustering by using vector quantization and using vectors as cluster centers. In [50] they treat each weight row as a row vector and perform k means with these vectors as centroids. Other attempts [43] [54] even index whole filters with k means by utilizing k-means and 2D transformations.

De Prado et al. [9] observe that k-means quantization outperforms standard and dynamic fixed point quantization on both accuracy and compression rate. That is because k-means is a non uniform quantization method, meaning the intervals between the quantized values are different with each other. This way the fewer quantized values can more closely follow the original distribution of the weights.

Quantization introduces noise and that translates to reduced model accuracy. Most methods require training the models from scratch using the reduced precision weights. Others require or at least benefit from fine-tuning the models. This means retraining the network for a small number of iterations until the accuracy recovers from the drop that quantization introduced.

## 5.2 Contribution of this Thesis

In this thesis we focus specifically on quantization with indexed representations as a compression technique for CNNs. We investigate the effects of k-means clustering quantization on the weights of CNNs. We test their classification accuracy and performance. We then investigate the negative effects of irregular access patterns that clustering introduces on the performance of the convolution. In order to overcome the drawbacks of clustering we experiment with different approaches to first hide the latencies they introduce and we then create the necessary tools to eliminate them.

## Chapter 6

# **Background**

In this chapter we introduce some fundamental concepts that are mentioned throughout the thesis.

## 6.1 Machine Learning

Machine Learning (ML) is a subfield of Artificial Intelligence (AI). The domain of ML also intersects with Computer Science, Statistics and Information Theory. In general its aim is enabling computers to learn (or to be trained) from existing data to perform specific tasks automatically. The concept of learning in this context, means to gradually improve their performance on carrying out a task, without them being specifically programmed to do so.

The main Machine Learning algorithm subcategories are Supervised learning, Unsupervised learning, Semi-supervised learning and Reinforcement learning.

- Supervised Learning algorithms use existing data (train dataset) that consist of one or more inputs and an output or label to learn to predict the outputs of new data(test dataset) only from their inputs.

- Unsupervised learning algorithms are used when the data are unlabelled (are only

inputs). The goal is to find patterns and commonalities in the data, recognize them

in new data and organize similar data to clusters.

- Semi-supervised learning algorithms are somewhere in between the previous two

categories. They use both labeled and unlabeled data but usually more unlabeled

than labeled data. When unlabeled data are used with a small amount of labeled

data the accuracy is vastly improved. This method is used when labeling the data

requires skill and time, but unlabeled data are easy to obtain.

- Reinforcement learning algorithms interact with the environment with actions that have errors or rewards, with the goal being to maximize a reward function. This trial

and error method enables computers to find the ideal behaviour within a specific context in order to maximize reward.

#### **6.2** Neural Networks

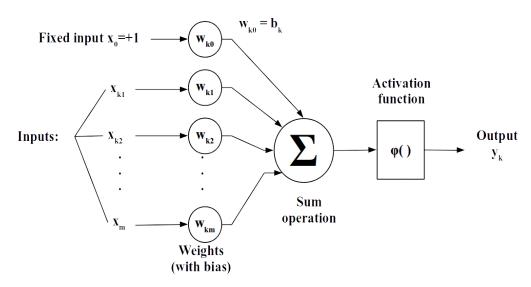

One of the supervised machine learning methods are neural networks. Neural networks are computational models inspired from the biological neurons of humans and other animals. In that sense they obtain an input and they give an output depending on the importance of the input relative to other neurons. Neural networks are nowadays used in a variety of classification tasks. The neuron is the fundamental component of neural networks. A neuron receives a number of inputs from previous neurons and produces one output as seen in Fig. 6.1

Figure 6.1: Model of a neuron

The output is the weighted sum of the inputs followed by the neuron's activation function. In mathematical form this is desribed as:

$$v_k = \sum_{j=0}^m w_{kj} x_j \tag{6.1}$$

$$y_k = \phi(v_k) \tag{6.2}$$

where  $x_j$  are the inputs and  $w_{kj}$  are the weights of the neuron.  $b_k$  is the bias.  $\phi()$  is the activation function and its purpose is to introduce non-linearity into the output of a neuron. This enables the neuron to describe different linear and non-linear functions.

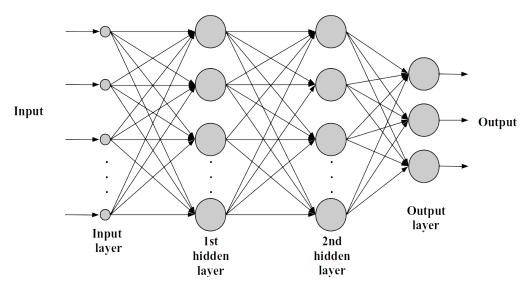

One of the most common arrangement of neurons is the multilayer perceptron (Fig 6.2). They consist of at least three layers of neuron nodes. Each neuron of one layer is