#### NATIONAL TECHNICAL UNIVERSITY OF ATHENS

SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

DIVISION OF COMPUTER SCIENCE

# From Circuits to SoC Processors: Arithmetic Approximation Techniques & Embedded Computing Methodologies for DSP Acceleration

Ph.D. Dissertation

Vasileios K. Leon

Athens October 2022

# From Circuits to System-on-Chip Processors: Arithmetic Approximation Techniques & Embedded Computing Methodologies for Digital Signal Processing Acceleration

#### Vasileios Leon

#### Examination Committee

Prof. Kiamal Pekmestzi (Supervisor), National Technical University of Athens

Prof. Dimitrios Soudris, National Technical University of Athens

Associate Prof. Georgios Goumas, National Technical University of Athens

Prof. Dionysios Reisis, National and Kapodistrian University of Athens

Prof. Apostolos Dollas, Technical University of Crete

Prof. Dimitris Gizopoulos, National and Kapodistrian University of Athens

Prof. Antonis Paschalis, National and Kapodistrian University of Athens

Submitted to National Technical University of Athens in partial fulfillment of the requirements for the degree of Doctor of Engineering (PhD in Engineering) in Computer Science.

National Technical University of Athens School of Electrical & Computer Engineering Division of Computer Science Microprocessors and Digital Systems Laboratory

# From Circuits to SoC Processors: Arithmetic Approximation Techniques & Embedded Computing Methodologies for DSP Acceleration

Ph.D. Dissertation of

ΟI

#### Vasileios Leon

Supervising Committee: Kiamal Pekmestzi

Dimitrios Soudris Georgios Goumas

Approved by the Examination Committee on October 10, 2022.

Kiamal Pekmestzi Professor NTUA Dimitrios Soudris Professor NTUA Georgios Goumas Assoc. Professor NTUA

Dionysios Reisis Professor NKUA Apostolos Dollas Professor TUC

Dimitris Gizopoulos

Professor NKUA

Antonis Paschalis Professor NKUA

The current Ph.D. Dissertation was partially supported by research activities of the European Space Agency (ESA).

The content of the Ph.D. Dissertation does not reflect the official opinion of National Technical University of Athens. All the reported information and views lie entirely with the author.

Content that is reused from publications that the author has (co-)authored, namely excerpts, figures, and tables, is under copyright with the respective paper publishers (IEEE, ACM, IET, Elsevier). These publications are explicitly stated in the abstract of each chapter.

Content that is reused from third-party publications appears with the appropriate copyright note. Reuse of any such content by any interested party requires the publishers' prior consent, according to the applicable copyright policies.

Content that has not been published before is copyrighted jointly as follows:

© 2022. All rights reserved.

Vasileios Leon, National Technical University of Athens

#### Vasileios K. Leon

PhD, Electrical & Computer Engineering, National Technical University of Athens Diploma, Computer Engineering & Informatics, University of Patras

Η παρούσα  $\Delta$ ιδακτορική  $\Delta$ ιατριβή υποστηρίχ $\vartheta$ ηκε μερικώς από ερευνητικές δραστηριότητες της European Space Agency (ESA).

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτή τη Διδακτορική Διατριβή εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

© 2022. Με επιφύλαξη παντός δικαιώματος. Βασίλειος Λέων, Εθνικό Μετσόβιο Πολυτεχνείο (Ε.Μ.Π.)

#### Βασίλειος Κ. Λέων

## **Abstract**

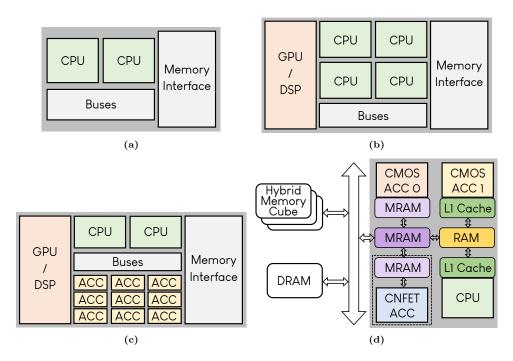

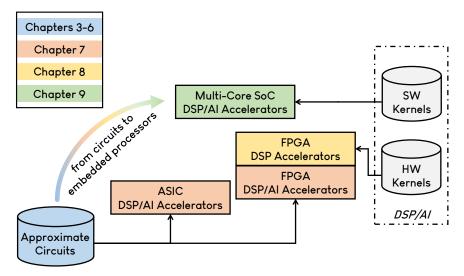

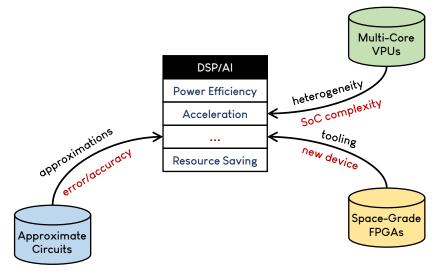

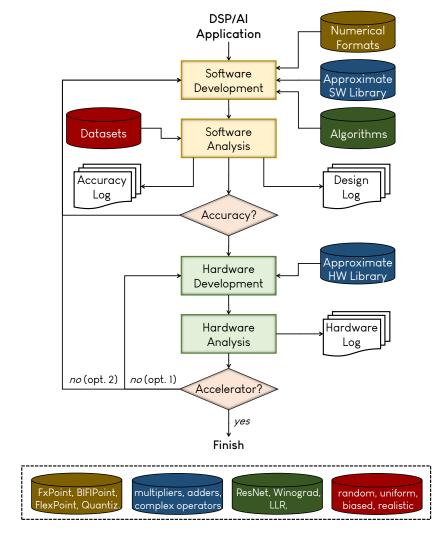

The recent end of Dennard's Scaling and the declining Moore's Law have signified a new era for the computing systems. Power efficiency has now become a critical factor for both cloud and edge computing. Concurrently, the rapid growth of compute-intensive applications from the Digital Signal Processing (DSP) and Artificial Intelligence (AI) domains challenges the resources of computing systems. As a result, the computing industry is forced to find alternative design approaches and computing platforms to sustain increased power efficiency, while providing sufficient performance. Among the examined solutions, Approximate Computing, Hardware Acceleration, and Heterogeneous Computing have gained great momentum. proximate Computing is a novel design paradigm that exploits the inherent error resilience of DSP/AI applications to deliver gains in power, area, and/or performance by reducing the quality of the results. Hardware Acceleration refers to the execution of demanding computational tasks on specialized hardware, such as the Application-Specific Integrated Circuits (ASICs) and the Field-Programmable Gate Arrays (FPGAs), rather than general-purpose processors. Finally, Heterogeneous Computing refers to versatile processing architectures, such as the Vision Processing Units (VPUs), which integrate more than one type of processor and various memory technologies.

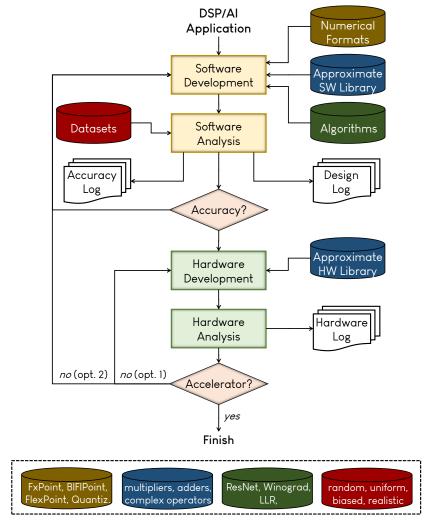

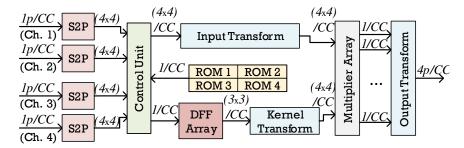

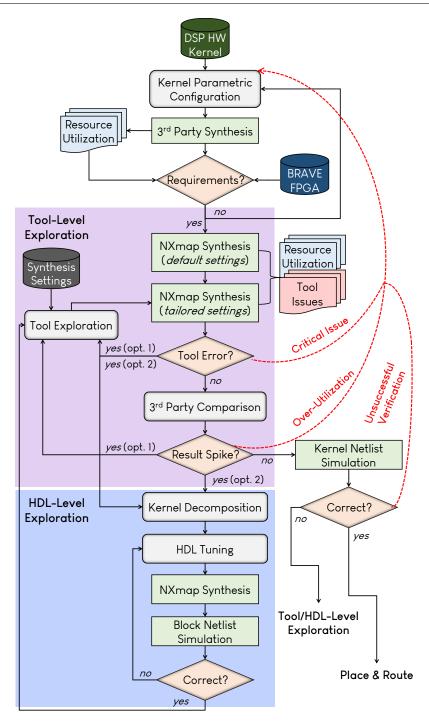

In this Dissertation, we introduce design solutions and methodologies, built on top of the preceding computing paradigms, for the development of energy-efficient DSP and AI accelerators. In particular, we adopt the promising paradigm of Approximate Computing and apply new approximation techniques in the design of arithmetic circuits. Based on our methodology, these arithmetic approximation techniques are then combined with hardware design techniques to implement approximate ASIC-and FPGA-based DSP and AI accelerators. Moreover, we propose methodologies for the efficient mapping of DSP/AI kernels on distinctive embedded devices, such as the new space-grade FPGAs and the heterogeneous VPUs. On the one hand, we cope with the decreased flexibility of the space-grade technology and the technical challenges that arise in new FPGA tools and devices. On the other hand, we unlock the full potential of heterogeneity by surpassing the increased hardware complexity and exploiting all the diverse processors and memories.

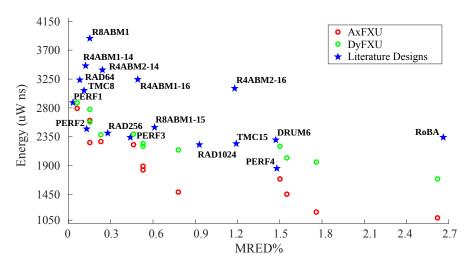

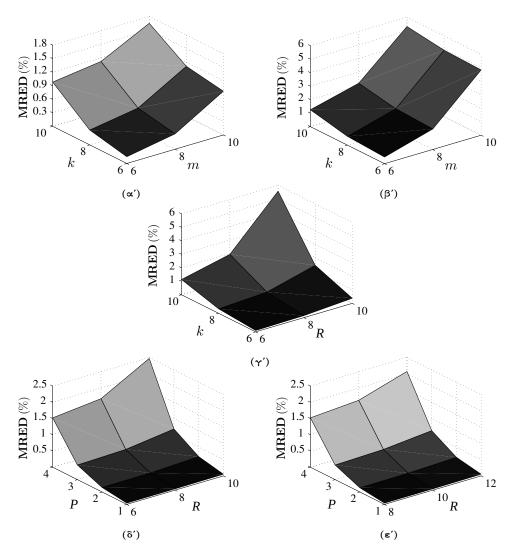

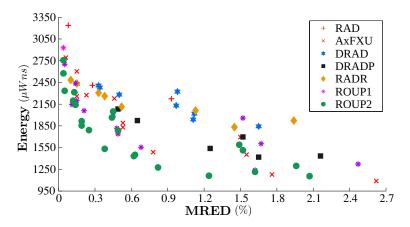

In more detail, the proposed arithmetic approximation techniques involve bit-level optimizations, inexact operand encodings, and skipping of computations, while they are applied in both fixed- and floating-point arithmetic. To increase the design space and extract the most efficient solutions, we also conduct an extensive exploration on

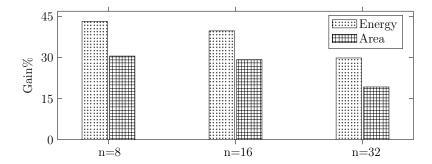

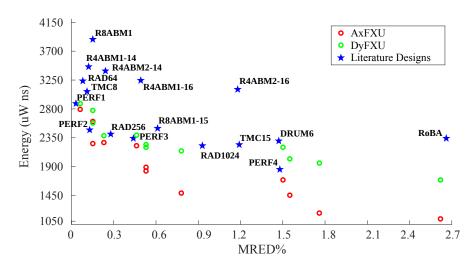

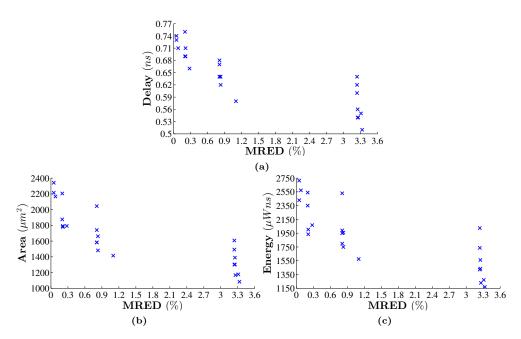

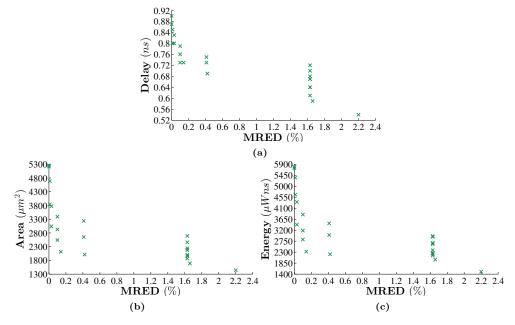

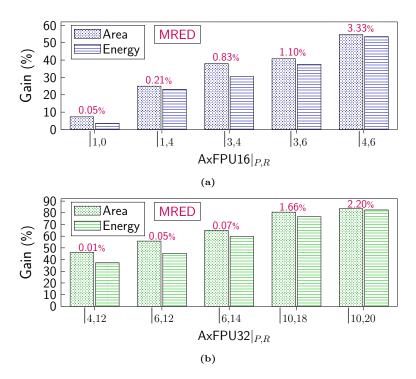

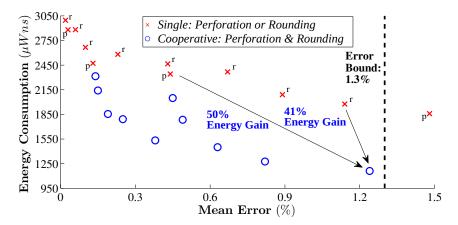

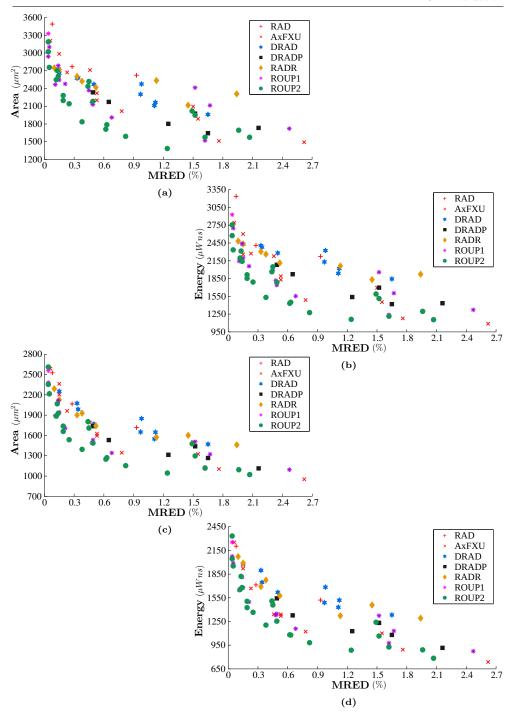

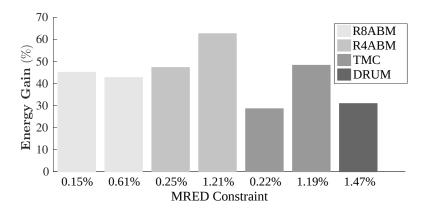

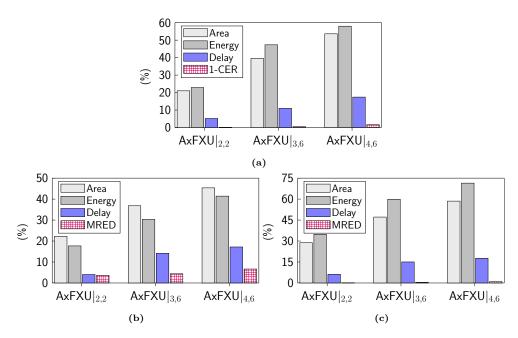

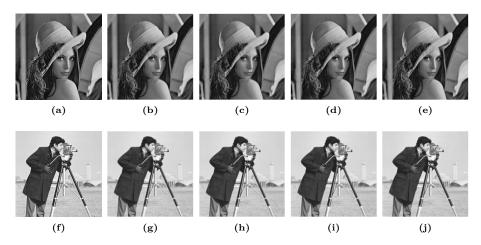

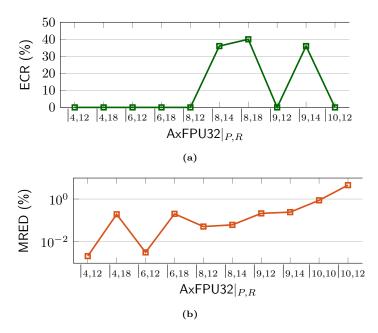

combinations among the approximation techniques. Furthermore, we propose a lowoverhead scheme for seamlessly adjusting the approximation degree of our circuits at runtime. In comparison with state-of-the-art designs, the proposed arithmetic circuits feature a very large approximation space, i.e., a wide range of approximation configurations, which enable to maximize the resource gains for a given error constraint. Our techniques induce a mean relative error of up to  $\sim 2\%$ , i.e., typical error values for approximate circuits. The most prominent approximate circuits of the Dissertation form a high-resolution Pareto front in a comparative evaluation involving state-of-the-art designs of the literature, and they deliver up to 63% better energy consumption. Finally, our runtime-configurable circuits exhibit a small area overhead of  $\sim 3\%$  compared to the accurate design, and they provide  $\sim 1.5 \times$  less energy gains than their respective design-time counterparts with fixed approximation. Nevertheless, they can dynamically change the approximation degree, namely, the accuracy of the calculations, while they still attain remarkable energy gains versus the accurate circuit and state-of-the-art approximate circuits. At the accelerator level, we develop a plethora of approximate kernels for 1D/2D signal processing and Convolutional Neural Networks (CNNs). The experimental results show that we achieve small relative errors for classic DSP calculations and 0%-5% accuracy loss in CNNs for various arithmetic formats, while providing up to 70% area and energy savings.

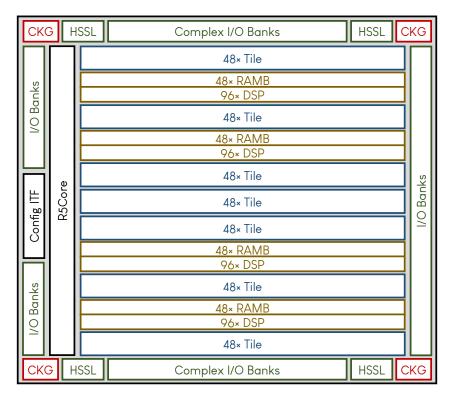

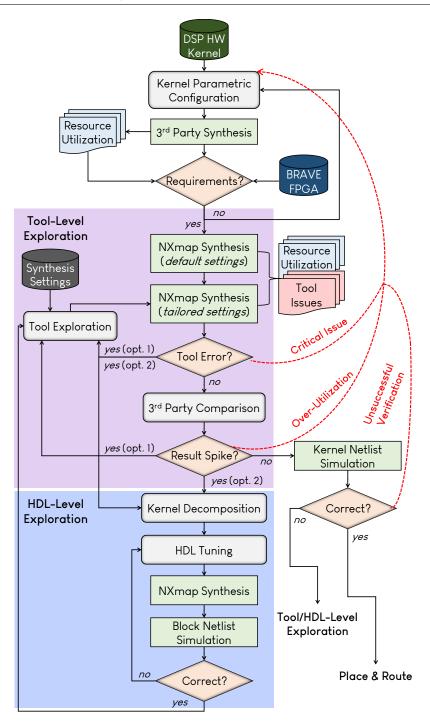

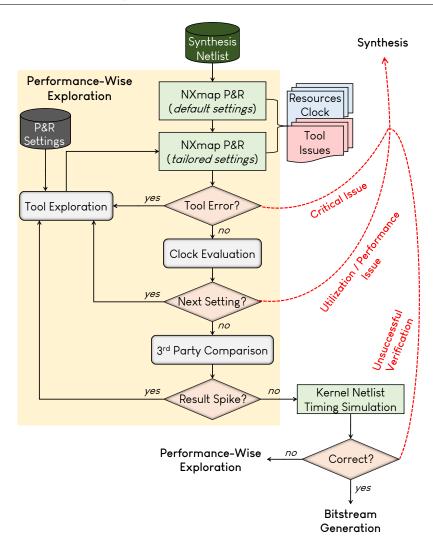

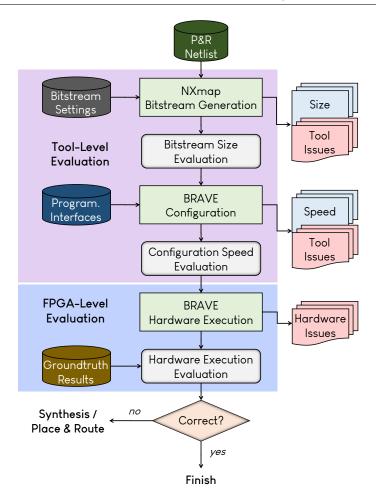

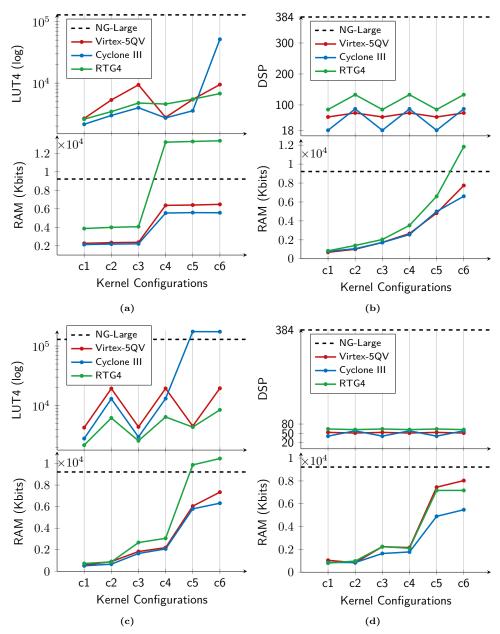

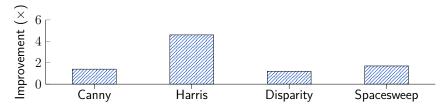

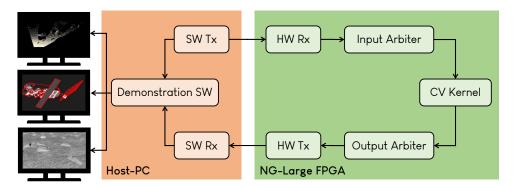

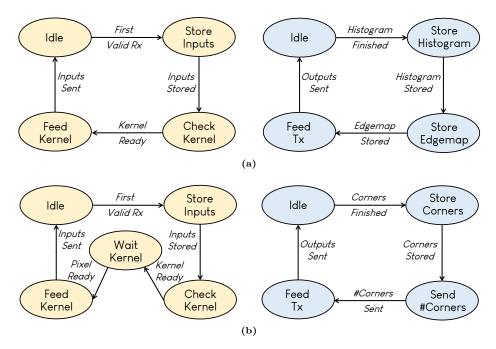

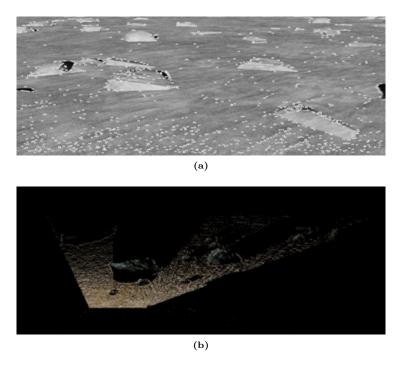

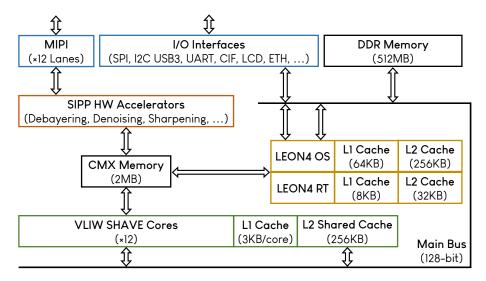

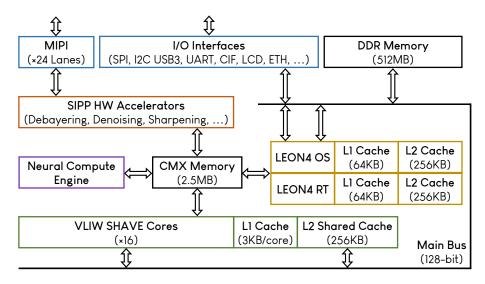

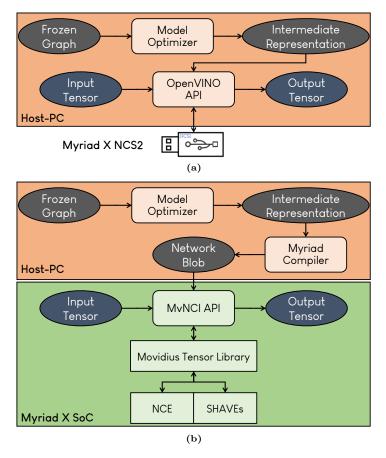

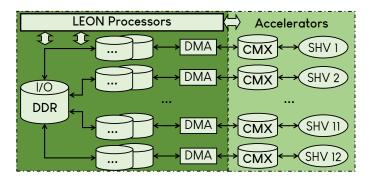

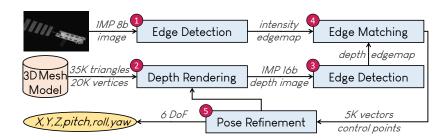

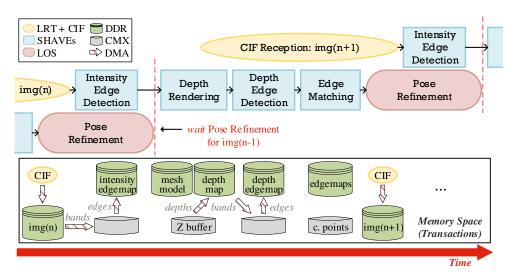

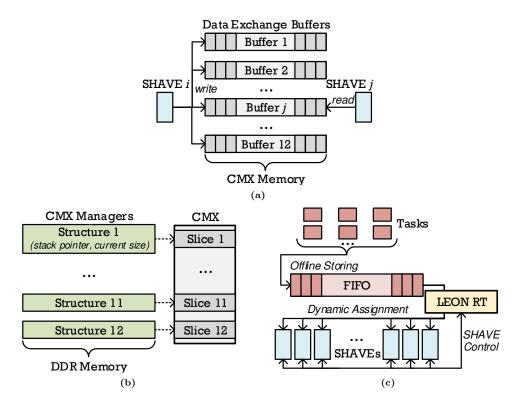

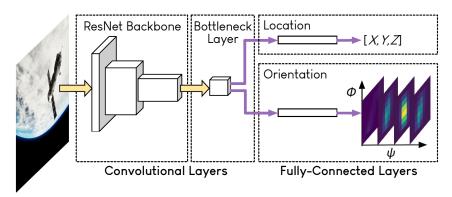

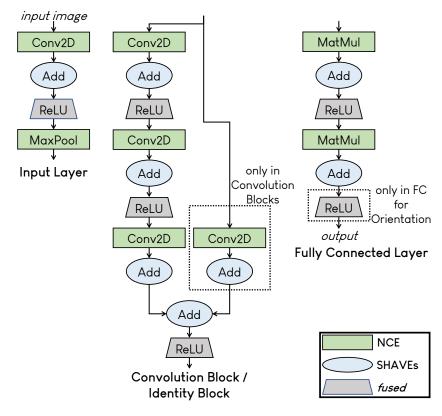

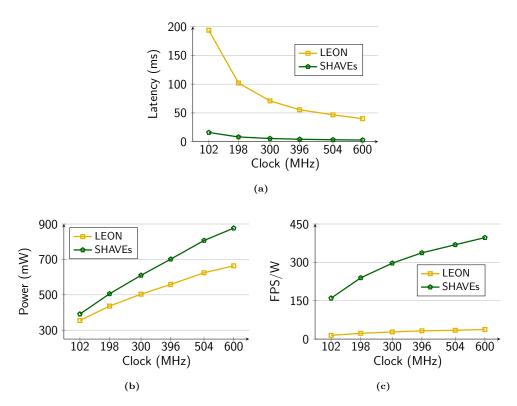

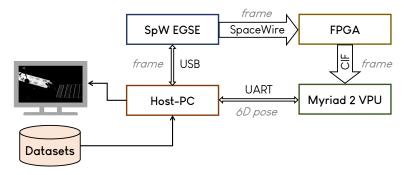

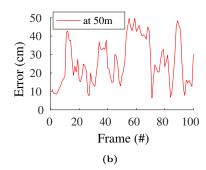

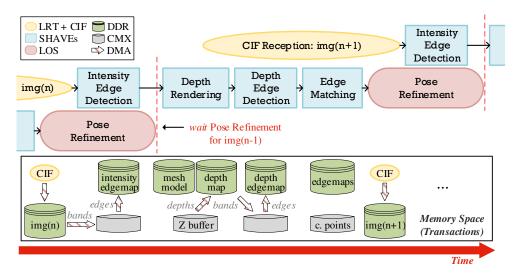

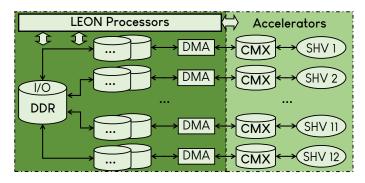

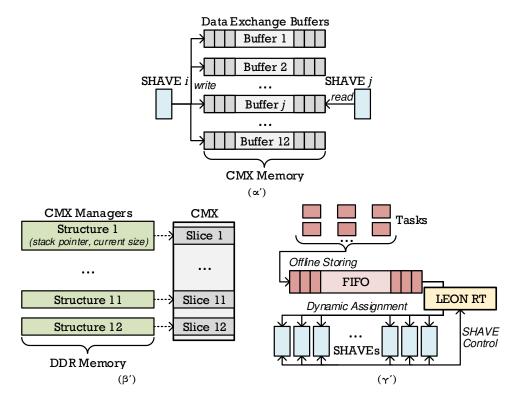

Regarding the DSP acceleration on new space-grade FPGAs, we apply our methodology to efficiently map computer vision algorithms onto the radiation-hardened NanoXplore's FPGAs. In the end, we achieve balanced resource utilization, which is comparable to that of well-established FPGA vendors. Moreover, the throughput is sufficient (e.g., up to 10 FPS for feature detection on MPixel images), considering the performance requirements of vision-based space applications. In terms of Heterogeneous Computing, we accelerate custom DSP kernels, a sophisticated computer vision pipeline, and a demanding CNN with ResNet-50 backbone on Intel's Myriad VPUs. The proposed methodology and embedded design techniques provide speedups up to  $20\times$  for classic DSP on Myriad 2, while the power lies around 1W. The CNN is accelerated on Myriad X with 2W, achieving  $\sim 8.5\times$  and  $\sim 1.7\times$  better performance-per-Watt than the ARM CPU and the Jetson Nano GPU, respectively.

**Keywords:** Approximate Computing, Approximation Techniques, Arithmetic Circuits, Computer Arithmetic, Hardware Design, Hardware Accelerators, ASIC, FPGA, VPU, SoC, Heterogeneous Computing, Embedded Systems, Space-Grade, Digital Signal Processing, Computer Vision, Convolutional Neural Networks.

# Περίληψη

Το πρόσφατο τέλος της Κλιμάχωσης του Dennard και η φθίνουσα πορεία του Νόμου του Moore έχουν σηματοδοτήσει μια νέα εποχή για τα υπολογιστικά συστήματα. Η κατανάλωση ισχύος αποτελεί πλέον έναν κρίσιμο παράγοντα, τόσο για το υπολογιστικό νέφος όσο και για υπολογισμούς στην άκρη του δικτύου. Ταυτόχρονα, η ταχεία ανάπτυξη απαιτητικών εφαρμογών από τους τομείς της Ψηφιακής Επεξεργασίας Σήματος (DSP) και της Τεχνητής Νοημοσύνης (ΑΙ) δημιουργεί προκλήσεις στους πόρους των υπολογιστικών συστημάτων. Ως αποτέλεσμα, η βιομηχανία των υπολογιστών υιοθετεί εναλλακτικές μεθόδους σχεδίασης κυκλωμάτων και συστημάτων, ώστε να διατηρήσει χαμηλή κατανάλωση ισχύος, παρέχοντας όμως και επαρκή ταχύτητα. Ανάμεσα στις λύσεις που εξετάζονται, ο Προσεγγιστικός Υπολογισμός εχμεταλλεύεται την εγγενή ανθεκτικότητα σε σφάλματα των DSP/AI εφαρμογών ώστε να προσφέρει κέρδη σε πόρους μειώνοντας την ποιότητα των αποτελεσμάτων. Η Επιτάχυνση Υλικού αναφέρεται στην εκτέλεση απαιτητικών υπολογιστικών εργασιών σε εξειδικευμένο υλικό, όπως τα Ολοκληρωμένα Κυκλώματα Ειδικής Εφαρμογής (ASICs) και οι Συστοιχίες Επιτόπια Προγραμματιζόμενων Πυλών (FPGAs). Τέλος, ο Ετερογενής Υπολογισμός αναφέρεται σε ευέλικτες αρχιτεκτονικές επεξεργασίας με πολλαπλούς τύπους επεξεργαστή και μνήμης, όπως οι Μονάδες Επεξεργασίας Όρασης (VPUs).

Στην παρούσα Διατριβή, εισάγουμε σχεδιαστικές λύσεις και μεθοδολογίες βασισμένες στα προαναφερθέντα πρότυπα σχεδίασης, με στόχο την ανάπτυξη ενεργειακά αποδοτικών επιταχυντών υλικού. Σχετικά με τον Προσεγγιστικό Υπολογισμό, εφαρμόζουμε νέες τεχνικές προσέγγισης στη σχεδίαση αριθμητικών κυκλωμάτων. Οι τεχνικές αυτές συνδυάζονται με βάση τη μεθοδολογία μας με κλασσικές τεχνικές σχεδίασης, ώστε να υλοποιήσουμε προσεγγιστικούς DSP και AI επιταχυντές σε ASIC και FPGA. Επιπλέον, προτείνουμε μεθοδολογίες για την αποτελεσματική αποτύπωση DSP/AI πυρήνων πάνω σε ιδιόμορφες ενσωματωμένες συσκευές, όπως τα νέα FPGAs διαστημικού βαθμού και οι ετερογενείς VPUs. Όσον αφορά τα FPGAs, αντιμετωπίζουμε τις τεχνικές προκλήσεις που προκύπτουν κατά τη χρήση νέων εργαλείων, ενώ για τις VPUs, ξεκλειδώνουμε όλες τις δυνατότητες της ετερογένειας, ξεπερνώντας την αυξημένη πολυπλοκότητα υλικού και αξιοποιώντας όλους τους διαφορετικούς πόρους.

Οι προτεινόμενες τεχνικές αριθμητικής προσέγγισης περιλαμβάνουν βελτιστοποιήσεις σε επίπεδο δυαδικού ψηφίου, μη ακριβείς κωδικοποιήσεις τελεστών, και παράλειψη υπολογισμών, ενώ εφαρμόζονται σε αριθμητική τόσο σταθερής όσο και κινητής υποδιαστολής. Για να αυξηθεί ο χώρος σχεδίασης και να εξάγουμε τις πιο αποτελεσματικές

λύσεις, πραγματοποιούμε επίσης μια εκτενή εξερεύνηση πάνω στους συνδυασμούς των τεχνικών. Επιπλέον, προτείνουμε ένα σχήμα χαμηλής επιβάρυνσης για την απρόσκοπτη ρύθμιση του βαθμού προσέγγισης των χυχλωμάτων κατά το χρόνο εκτέλεσης. Σε σύγχριση με σημαντικά κυκλώματα της βιβλιογραφίας, οι προτεινόμενες λύσεις διαθέτουν πολύ μεγαλύτερο χώρο προσέγγισης (ευρύτερο φάσμα προσεγγίσεων), επιτρέποντας τη μεγιστοποίηση των χερδών σε πόρους για έναν δεδομένο περιορισμό σφάλματος. Οι τεχνικές μας προκαλούν ένα μέσο σχετικό σφάλμα έως και ~2%, δηλαδή τυπικές τιμές σφάλματος προσεγγιστικών κυκλωμάτων. Τα πιο εξέχοντα προσεγγιστικά κυκλώματα της Διατριβής σχηματίζουν ένα σύνορο Pareto υψηλής ανάλυσης στη συγκριτική αξιολόγηση με σημαντικές εργασίες της βιβλιογραφίας, προσφέροντας έως και 63% καλύτερη κατανάλωση ενέργειας. Τέλος, τα κυκλώματα που μπορούν να ρυθμίσουν δυναμικά την προσέγγιση, έχουν αυξημένη επιφάνεια κατά  $\sim\!3\%$  σε σύγκριση με το ακριβές κύκλωμα, και παρέχουν  $\sim 1.5 \times$  λιγότερα κέρδη ενέργειας από τα αντίστοιχα κυκλώματα με σταθερή προσέγγιση. Όμως, έχουν τη δυνατότητα να αλλάζουν την αχρίβεια των υπολογισμών, ενώ εξαχολουθούν να προσφέρουν αξιοσημείωτα ενεργειαχά χέρδη έναντι του αχριβούς κυκλώματος και κυκλωμάτων της βιβλιογραφίας. Σε επίπεδο επιταχυντή, αναπτύσσουμε μια πληθώρα από προσεγγιστιχούς πυρήνες για επεξεργασία σημάτων/ειχόνων χαι Συνελικτικά Νευρωνικά Δίκτυα (CNNs). Με βάση την πειραματική ανάλυση, τα σφάλματα είναι μικρά σε κλασικούς DSP υπολογισμούς και η απώλεια ακρίβειας κυμαίνεται ως 5% στα νευρωνικά δίκτυα, ενώ επιτυγχάνεται έως και 70% εξοικονόμηση επιφάνειας και ενέργειας.

Σχετικά με τα νέα FPGAs διαστημικού βαθμού, εφαρμόζουμε τη μεθοδολογία μας για την αποτελεσματική απεικόνιση αλγορίθμων υπολογιστικής όρασης στα ανθεκτικά-σεακτινοβολία FPGAs της NanoXplore. Στο τέλος, επιτυγχάνουμε ισορροπημένη χρήση πόρων, η οποία είναι συγκρίσιμη με αυτή των καθιερωμένων προμηθευτών FPGAs. Επιπλέον, η ταχύτητα είναι επαρκής (π.χ., έως και 10 FPS για την ανίχνευση χαρακτηριστικών σε MPixel εικόνες), λαμβάνοντας υπόψη τις απαιτήσεις απόδοσης των διαστημικών εφαρμογών. Σχετικά με τον Ετερογενή Υπολογισμό, επιταχύνουμε DSP πυρήνες, μια ακολουθία αλγορίθμων υπολογιστικής όρασης, και ένα απαιτητικό CNN στις Myriad VPUs της Intel. Οι προτεινόμενες μεθοδολογίες και τεχνικές ενσωματωμένης σχεδίασης παρέχουν επιτάχυνση έως και  $20\times$  σε κλασικούς DSP υπολογισμούς στη Myriad 2 με κατανάλωση ισχύος 1W. Το CNN επιταχύνεται στη Myriad X με 2W, προσφέροντας  $\sim 8.5\times$  και  $\sim 1.7\times$  καλύτερη απόδοση-ανά-Watt από τον επεξεργαστή γενικού-σκοπού ARM και τον επεξεργαστή γραφικών Jetson Nano, αντίστοιχα.

**Λέξεις Κλειδιά:** Προσεγγιστικός Υπολογισμός, Τεχνικές Προσέγγισης, Αριθμητικά Κυκλώματα, Αριθμητική Υπολογιστών, Σχεδίαση Υλικού, Επιταχυντές Υλικού, Ετερογενής Υπολογισμός, Ενσωματωμένα Συστήματα, Τεχνολογία Διαστήματος, Ψηφιακή Επεξεργασία Σήματος, Υπολογιστική Όραση, Συνελικτικά Νευρωνικά Δίκτυα.

# **Contents**

| Αb  | strac  | ,                                                   | XIII |

|-----|--------|-----------------------------------------------------|------|

| Gr  | eek A  | ostract                                             | χV   |

| Lis | t of l | gures                                               | xxi  |

| Lis | t of   | ables                                               | ΧV   |

| Lis | t of   | bbreviations                                        | xix  |

| 1.  | Intro  | luction                                             | 1    |

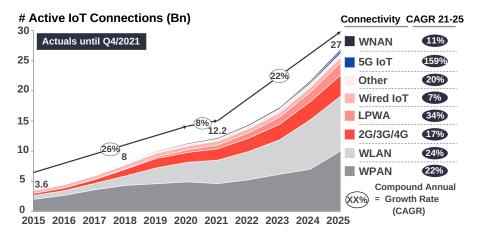

|     | 1.1.   | Γhe Landscape of Embedded Systems                   | 1    |

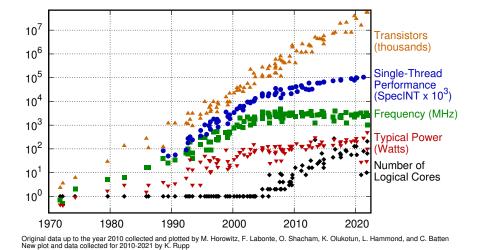

|     | 1.2.   | The Evolution of Integrated Circuits                | 2    |

|     | 1.3.   | Approximate Computing                               | 4    |

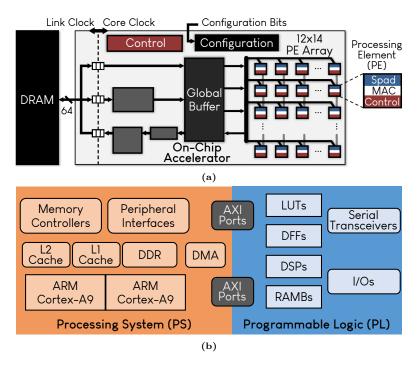

|     | 1.4.   | Hardware Acceleration                               | 6    |

|     | 1.5.   | Heterogeneous Computing                             | 8    |

|     | 1.6.   | Scope and Contribution of Dissertation              | 10   |

|     | 1.7.   |                                                     | 12   |

|     | 1.8.   | Overview of Technologies, Tools and Devices         | 15   |

| 2.  | The    | Approximate Computing Paradigm                      | 17   |

|     | 2.1.   | Introduction                                        | 18   |

|     | 2.2.   | The Terminology of Approximate Computing            | 18   |

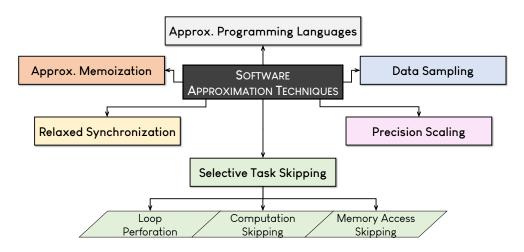

|     | 2.3.   | Classification of Software Approximation Techniques | 20   |

|     |        | 2.3.1. Selective Task Skipping                      | 21   |

|     |        | 2.3.2. Approximate Memoization                      | 24   |

|     |        | y .                                                 | 25   |

|     |        | 2.3.4. Precision Scaling                            | 27   |

|     |        | 2.3.5. Data Sampling                                | 28   |

|     |        | 2.3.6. Approximate Programming Languages            | 30   |

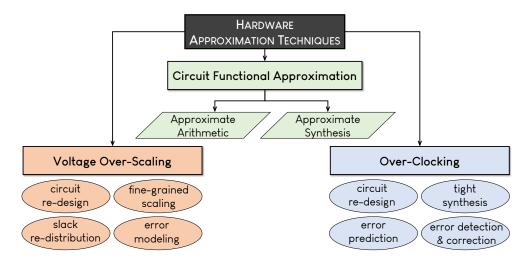

|     | 2.4.   | 11                                                  | 32   |

|     |        | 11                                                  | 34   |

|     |        | 2.4.2. Voltage Over-Scaling                         | 40   |

|     |        | 2.4.3. Over-Clocking                                | 42   |

| I. | Ar   | ithmetic Approximation Techniques for Circuit Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45  |

|----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3. | Arit | hmetic Optimization: Double-LSB Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 47  |

|    | 3.1. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48  |

|    | 3.2. | and the state of t | 50  |

|    | 3.3. | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 51  |

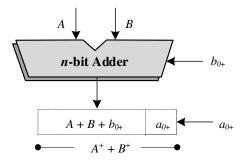

|    |      | 3.3.1. Straightforward DLSB Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 51  |

|    |      | 3.3.2. Sophisticated DLSB Design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 52  |

|    | 3.4. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 56  |

|    |      | 3.4.1. Theoretical Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 56  |

|    |      | 3.4.2. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 58  |

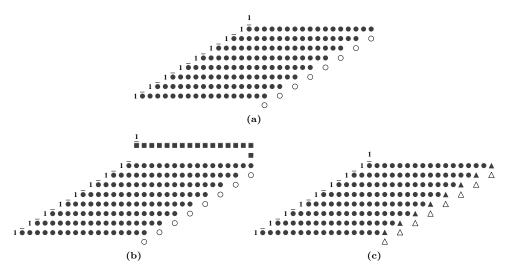

|    |      | 3.4.3. Case Study: DLSB for Large-Size Multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 59  |

|    | 3.5. | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 61  |

| 4. |      | hmetic Approximation: Hybrid High-Radix Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63  |

|    |      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 64  |

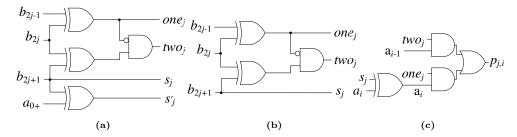

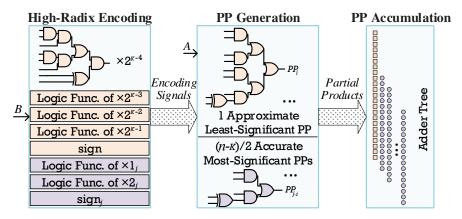

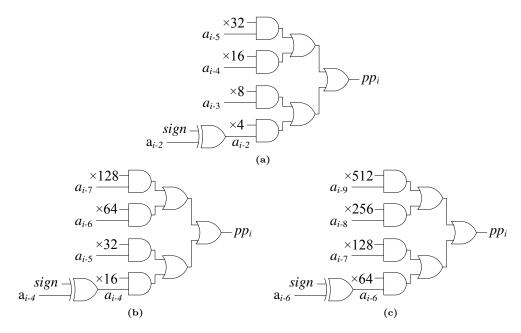

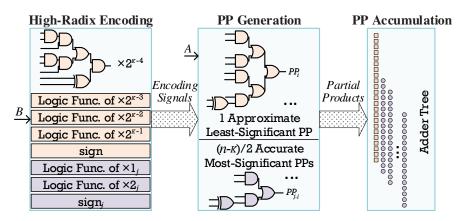

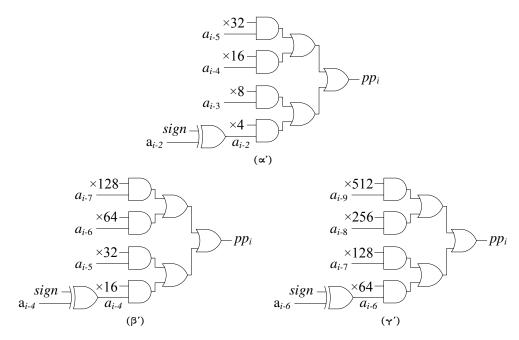

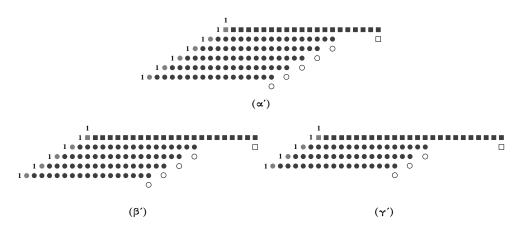

|    | 4.2. | Design of Approximate High-Radix Encodings and Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 66  |

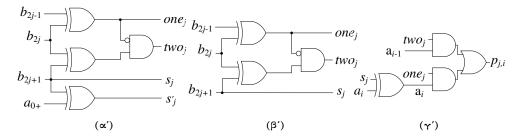

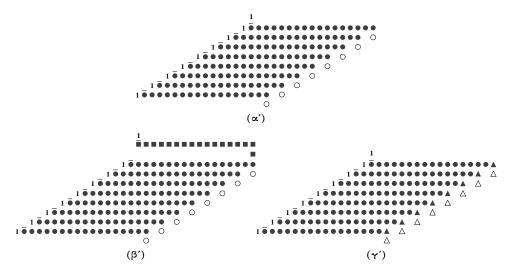

|    |      | 4.2.1. Approximate Operand Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66  |

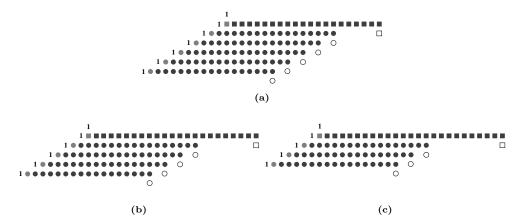

|    |      | 4.2.2. RAD: Approximate High-Radix Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 69  |

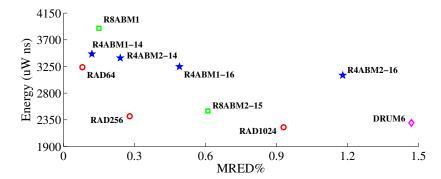

|    | 4.3. | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 71  |

|    |      | 4.3.1. Theoretical Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 72  |

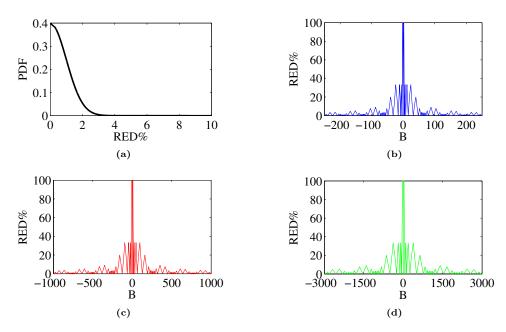

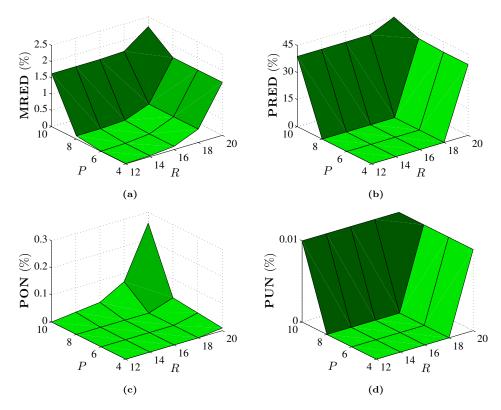

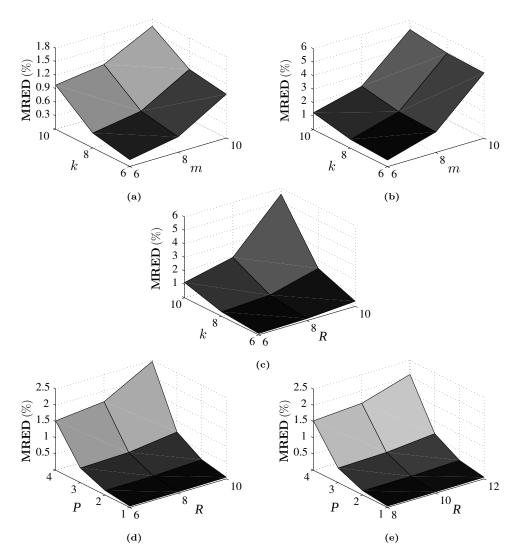

|    |      | 4.3.2. Error Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 74  |

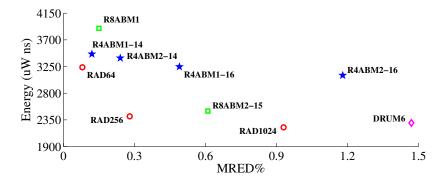

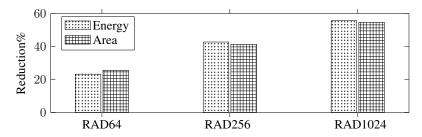

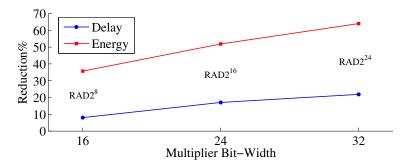

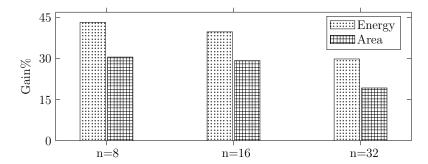

|    |      | 4.3.3. Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 75  |

|    | 4.4. | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 81  |

| 5. | Dyn  | amic Approximation: Runtime-Configurable Arithmetic Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83  |

|    | 5.1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 84  |

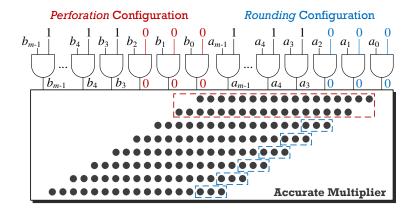

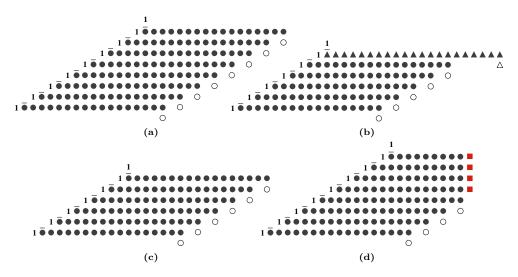

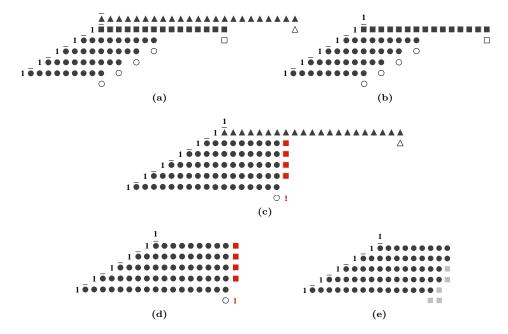

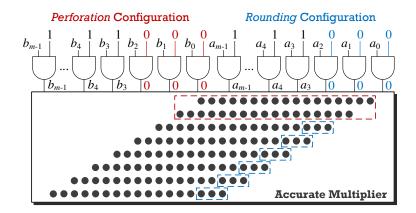

|    | 5.2. | Design of Runtime-Configurable Approximate Multipliers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 86  |

|    |      | 5.2.1. AxFXU: Approximate Fixed-Point Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 87  |

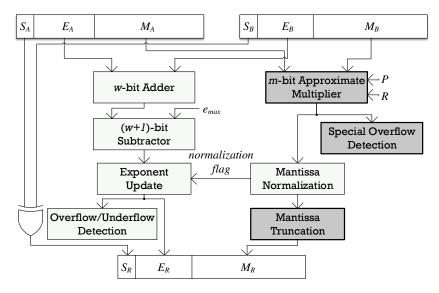

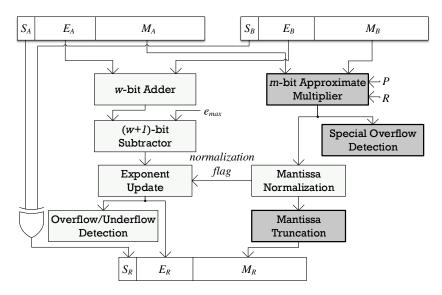

|    |      | 5.2.2. AxFPU: Approximate Floating-Point Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88  |

|    |      | 5.2.3. Dynamic Configuration of the Approximation Degree                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 92  |

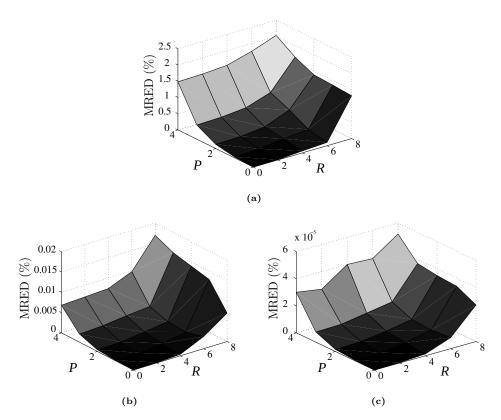

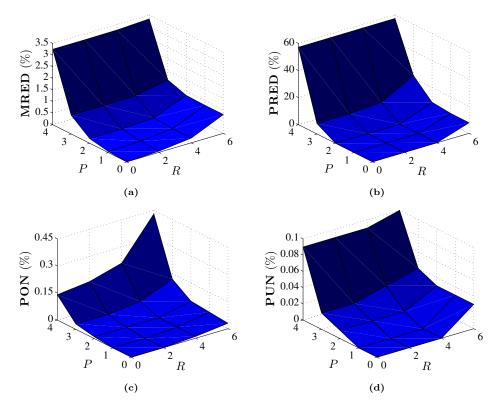

|    | 5.3. | Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 94  |