## National Technical University of Athens

School of Electrical and Computer Engineering Division of Communication, Electronic and Information Engineering

## Computational Methods for Automatic Analog Integrated Circuit Design

PhD Thesis

Konstantinos Touloupas

Supervisor

Paul Peter Sotiriadis, Professor, NTUA

Circuits & Systems Group Athens, December 2022

## Εθνικό Μετσόβιο Πολυτεχνείο

Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών Τομέας Επικοινωνιών, Ηλεκτρονικής & Συστημάτων Πληροφορικής

# Υπολογιστικοί Μέθοδοι για την Αυτόματη Σχεδίαση Αναλογικών Μικροηλεκτρονικών Κυκλωμάτων

$\Delta$ ιδακτορική  $\Delta$ ιατριβή του

Κωνσταντίνου Τουλούπα

Επιβλέπων

Παύλος Πέτρος Σωτηριάδης, Καθηγητής, ΕΜΠ

Circuits & Systems Group Αθήνα, Δεκέμβριος 2022

## National Technical University of Athens

School of Electrical and Computer Engineering Division of Communication, Electronic and Information Engineering

## Computational Methods for **Automatic Analog Integrated Circuit** Design

PhD Thesis by

#### Konstantinos Touloupas

#### **Advisory Committee:**

Paul Peter Sotiriadis

Nikolaos Maratos

Ioanna Roussaki

Professor, NTUA

Professor Emeritus, NTUA Assistant Professor, NTUA

Approved by the seven-member examination committee on 14/12/2022.

Paul Peter Sotiriadis

Professor NTUA

Ioanna Roussaki Assistant Professor

NTUA

Athanasios D. Panagopoulos

Professor

NTUA

Dimitra I. Kaklamani

Professor

NTUA

Nuno Calado Correia Lourenço

Researcher

Instituto de Telecomunicações

Giorgos Stamou

Professor

NTUA

Stefanos Kollias

Professor

NTUA

...... Κωνσταντίνος Τουλούπας Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright © Κωνσταντίνος Τουλούπας, 2022 Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς το συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν το συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

### Abstract

For decades, the semiconductor and electronics industry have seen great progress, fueled by the continuous scaling of transistor dimensions. Integrated circuits in the sub- $\mu$ m range have been extensively utilized in the electronics industry. Nowadays, with Moore's law coming to an end, transistors' gates have reached unprecedented lengths. The eventual power and speed gains, however, come with an increase in complexity and in design considerations; random variations in the manufacturing process induce variations in circuit device parameters and effectively lead to low-yield designs. Design verification is constantly becoming more cumbersome for circuit design, especially in the case of analog circuits.

Circuit designers have traditionally resorted to Electronic Design Automation (EDA) tools for complex circuit design. Given sets of device compact models, named Process Development Kits (PDKs), EDA tools can simulate complex circuits and can be used for verification purposes. In the case of digital circuitry, established EDA tools provide automation solutions for designers to avoid cumbersome, repetitive tasks and focus on the core design. Analog and Radio-Frequency (RF) circuit design, however, has no established means of automation.

This thesis presents methodologies for analog and RF circuit automatic sizing. From a high-level perspective, the contributions of this work lie in two factors; 1) The proposal of a family of black-box optimization algorithms, which take advantage of recent machine learning developments to accelerate and improve the exploration of the circuit's design space, and 2) the development of a framework for procedural simulation execution and optimization definition, based on commercial circuit simulators. The proposed framework exposes a user-friendly Application Process Interface (API) that can be used by designers to execute ad-hoc optimization problems and guide the sizing of their circuit.

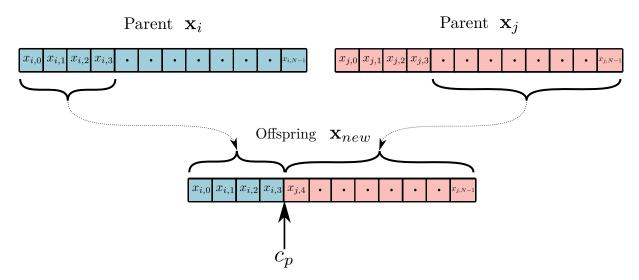

The first thrust of this thesis is the study of automatic circuit sizing in the context of black-box simulation-driven optimization. We apply and compare black-box optimization algorithms for the nominal sizing of analog and RF circuits, compare their performance and discuss their ability to provide feasible solutions within given evaluation budgets or time-frames. Taking into account that most black-box algorithms operate on continuous spaces, we define a new mutation and crossover operation for Evolutionary Algorithms (EAs) and apply it for circuit sizing. The aforementioned principles are studied for both the case of Single-Objective (SO) optimization and Multi-Objective

6 Abstract

(MO) one, when design-space exploration and feasible performance space needs to be found.

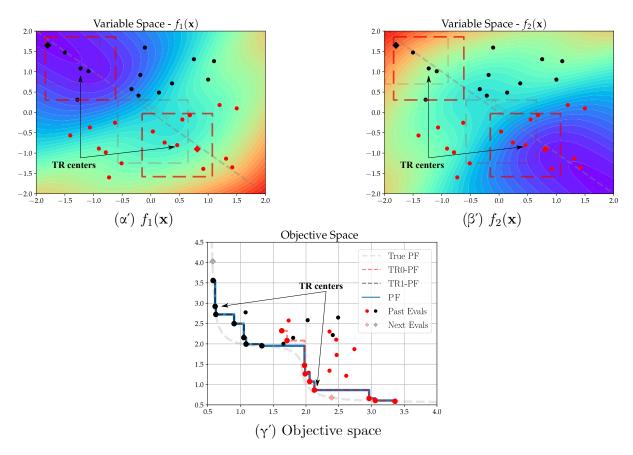

To reduce the cost of optimization in the sense of reducing the number of costly evaluations, we consider next the case of low budget optimization algorithms. In this setting, a new SO Bayesian Optimization (BO) algorithm is introduced. The use of Gaussian Processes (GPs) and a new, batched acquisition function relying on Thompson Sampling (TS) reduces the effective time for each optimization run. Taken into account the fact Gaussian Processes require  $\mathcal{O}(n^3)$  time for inference, kernel approximations are introduced to the GPs by using inducing points. In addition to the above, a new framework is proposed in which the GP models are restricted to model certain hypercubes of the design space. This approach, which is motivated by the concept of trust-regions in the EA literature, provides exquisite constraint-handling capabilities, is scalable in terms of input parameter space and proves favorable against other BO approaches as well as other EA algorithms.

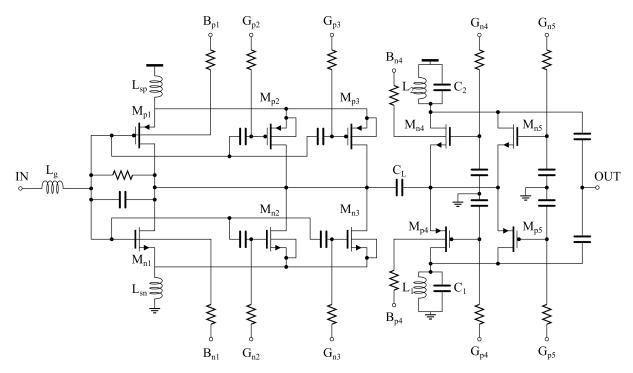

To extend the concept of local-based BO in the case of multiple objectives, a new, batched, Local Constrained Multi-Objective Bayesian Optimization (LoCoMOBO) approach is put forward. This MO optimization algorithm not only assists designers to size circuit-blocks, but also to assess the attainable performance metrics of a given topology. LoCoMOBO utilizes trust regions, and uses a Hypervolume-based acquisition function to define future query points for evaluation. In addition, TS is replaced with Random Fourier Features so as to ensure both that the design space is properly explored, in high-dimensional spaces.

To efficiently traverse mixed-variable input-spaces, where some parameters are continuous while others are integer-valued or categorical ones, a deep learning scheme that derives continuous representations of integrated devices is put forward. The core model is a Variational Autoencoder (VAE), which uses label guidance to transform the devices' input parameters to continuous-valued latent ones. The original device parameters are substituted by the VAE's latent variables in the optimization-based automatic sizing formulation, which is solved using the proposed local-based BO with satisfactory results.

In the final chapter, the conclusions of the conducted research are drawn, guidelines for future work are provided and potential impact on industry and society is discussed.

Index Terms Analog Integrated Circuits, automatic circuit sizing, black-box optimization, Evolutionary Algorithms, Bayesian Optimization, Gaussian Processes, Thompson Sampling, Random Fourier Features, Deep Learning, Variational Autoencoder.

## Περίληψη

Για δεκαετίες, η βιομηχανία ημιαγωγών και ηλεκτρονικών έχει επιδείξει μεγάλη ανάπτυξη, κυρίως λόγω της αδιάκοπης συρρίκνωσης των διαστάσεων των τρανζίστορ. Ολοκληρωμένα κυκλώματα σε τεχνολογίες κάτω του ενός μικρόμετρου έχουν χρησιμοποιηθεί ευρέως σε εμπορικές ηλεκτρονικές συσκευές. Στις μέρες μας, καθώς ο νόμος του Moore πλησιάζει στο τέλος του, η διάσταση των τρανζίστορ έχει φτάσει σε πολύ μικρά μεγέθη. Τα κέρδη σε ενεργειακή απόδοση και ταχύτητα που προκύπτουν, όμως, επιφυλάσσουν δυσκολίες στην σχεδίαση: οι μη ιδανικές συνθήκες κατά την διαδικασία κατασκευής προκαλούν διακυμάνσεις στις παραμέτρους των τρανζίστορ του κυκλώματος και οδηγούν ουσιαστικά σε κυκλώματα χαμηλής απόδοσης. Η επαλήθευση της λειτουργίας ενός κυκλώματος γίνεται συνεχώς πιο επίπονη για τους σχεδιαστές, ιδιαίτερα στην περίπτωση των αναλογικών ολοκληρωμένων κυκλωμάτων.

Οι σχεδιαστές κυκλωμάτων παραδοσιακά χρησιμοποιούν εργαλεία αυτοματοποίησης ηλεκτρονικού σχεδιασμού (Electronic Design Automation - EDA) για την σχεδίαση περίπλοκων κυκλωμάτων. Με δεδομένο ένα σύνολο από μοντέλα των διατάξεων ημιαγωγών, τα οποία αναφέρονται ως Process Development Kits (PDKs), τα εργαλεία αυτά μπορούν να προσομοιώνουν περίπλοκα κυκλώματα και να χρησιμοποιηθούν για επαλήθευση. Στην περίπτωση των ψηφιακών ολοκληρωμένων κυκλωμάτων, καθιερωμένα εργαλεία σχεδίασης EDA χρησιμοποιούνται από τους σχεδιαστές για να την εκπόνηση επαναλαμβανόμενων διεργασιών, γεγονός που διασφαλίζει την αποδοτική την εργασία τους και την ποιότητα του τελικού προϊόντος. Στην περίπτωση των αναλογικών και τηλεπικοινωνιακών κυκλωμάτων, όμως, παρόμοια εργαλεία δεν είναι διαθέσιμα.

Η διατριβή αυτή παρουσιάζει μεθοδολογίες για την αυτόματη διαστασιοποίηση αναλογικών και τηλεπικοινωνιακών κυκλωμάτων. Από γενικής άποψης, η συνεισφορά της δουλειάς που παρουσιάζεται εντοπίζεται σε δύο σημεία: 1) Την πρόταση μιας οικογένειας αλγορίθμων βελτιστοποίησης μαύρου κουτιού (black box), οι οποίοι χρησιμοποιούν πρόσφατες τεχνικές μηχανικής μάθησης για να επιταχύνουν και να βελτιώσουν την εξερεύνηση του χώρου λύσεων των προβλημάτων βελτιστοποίησης κυκλωμάτων και 2) την ανάπτυξη ενός εργαλείου για την διαδικαστική εκτέλεση προσομοιώσεων και τον ορισμό προβλημάτων βελτιστοποίησης, με χρήση εμπορικών προσομοιωτών. Το εργαλείο προσφέρει μία φιλική προς τον χρήστη διεπαφή διαδικασίας εφαρμογής (API) που μπορεί να χρησιμοποιηθεί από τους σχεδιαστές για την εκτέλεση προβλημάτων βελτιστοποίησης και να καθοδηγήσει την διαστασιοποίηση των στοιχείων του κυκλώματος.

Το πρώτο μέρος της διατριβής περιλαμβάνει την μελέτη της αυτόματης διαστασιοποί-

8 Περίληψη

ησης κυκλωμάτων με χρήση βελτιστοποίηση μαύρου κουτιού και εμπορικών προσομοιωτών. Εφαρμόζουμε και συγκρίνουμε αλγόριθμους μαύρου κουτιού για την τυπική, χωρίς διακυμάνσεις, διαστασιοποίηση αναλογικών και τηλεπικοινωνιακών κυκλωμάτων και σχολιάζουμε τις αποδόσεις τους ως προς την εύρεση εφικτών λύσεων μέσα σε χρονικά ή υπολογιστικά όρια. Δεδομένου ότι η πλειοψηφία των αλγορίθμων μαύρου κουτιού εφαρμόζεται σε συνεχείς χώρους αναζήτησης, ορίζουμε καινούριους τελεστές διασταύρωσης και μετάλλαξης για Εξελικτικούς Αλγόριθμους και τους χρησιμοποιούμε στη διαστασιοποίηση κυκλωμάτων. Οι τελεστές αυτοί εξετάζονται τόσο στα πλαίσια βελτιστοποίησης ενός όσο και πολλαπλών στόχων, όπου ισχύουν περιορισμοί για την απόδοση των κυκλωμάτων.

Για να μειωθεί το χόστος της βελτιστοποίησης όσον αφορά τον αριθμό των κοστοβόρων προσομοιώσεων, εξετάζουμε επίσης την κλάση των αλγορίθμων βελτιστοποίησης χαμηλής δειγματοληψίας του χώρου αναζήτησης. Σε αυτή την περίπτωση, ένας νέος αλγόριθμος Μπεϋζιανής βελτιστοποίησης ενός στόχου προτείνεται. Η χρήση Γκαουσιανών διαδικασιών και μιας νέας συνάρτησης απόκτησης που βασίζεται στην τεχνική Thompson Sampling μειώνει αποτελεσματικά τον χρόνο εκτέλεσης της βελτιστοποίησης. Δεδομένου ότι οι Γκαουσιανές διαδικασίες έχουν O(n3) πολυπλοκότητα για πρόβλεψη, περιλαμβάνουμε ένα προσεγγιστικό πυρήνα με χρήση σημείων επιρροής. Επιπρόσθετα, προτείνουμε μία καινούρια μεθοδολογία στην οποία οι Γκαουσιανές διαδικασίες περιορίζονται εντός υπερκύβων στον χώρο αναζήτησης. Αυτή η προσέγγιση, που αντλεί έμπνευση από την ιδέα της περιοχής εμπιστοσύνης στην βιβλιογραφία των Εξελικτικών Αλγορίθμων, παρουσιάζει εξαιρετική δυνατότητα στην εύρεση εφικτών λύσεων, κλιμακώνεται σε σχέση με την διάσταση του χώρου αναζήτησης και αποδεικνύεται προτιμιτέα σε σχέση με άλλους αλγόριθμους Μπεϋζιανής βελτιστοποίησης καθώς και άλλους Εξελικτικούς αλγόριθμους.

Για την επέχταση της ιδέας της τοπικής Μπεϋζιανής βελτιστοποίησης σε προβλήματα πολλαπλών στόχων, προτείνεται μία νέα, παράλληλη, τοπική Μπεϋζιανή Βελτιστοποίηση Πολλαπλών στόχων με περιορισμούς (Local Constrained Multi Objective Bayesian Optimization - LoCoMOBO). Ο αλγόριθμος αυτός πολλαπλών στόχων βοηθά τους σχεδιαστές όχι μόνο να διαστασιοποιήσουν τα κυκλώματά τους αυτόματα, αλλά και να έχουν εκτιμήσεις για τις εφικτές αποδόσεις διαφόρων κυκλωματικών τοπολογιών. Ο LoCoMOBO χρησιμοποιεί περιοχές εμπιστοσύνης και μια συνάρτηση απόκτησης που χρησιμοποιεί τιμές υπερόγκου για να ορίσει τα επόμενα σημεία που θα γίνουν προσομοίωση. Επιπλέον, η διαδικασία Thompson Sampling χρησιμοποιεί Τυχαία Χαρακτηριστικά Φουριέ έτσι ώστε να γίνεται καλύτερη εξερεύνηση του χώρου εισόδου, ακόμη και σε πολλές διαστάσεις.

Για την αποτελεσματική εξερεύνηση χώρων αναζήτησης με μικτού τύπου μεταβλητές, όπου ορισμένες παράμετροι είναι συνεχείς ενώ άλλες είναι ακέραιοι αριθμοί ή κατηγορικές μεταβλητές, προτείνεται μία μέθοδος βαθιάς μηχανικής μάθησης που παρέχει συνεχείς αναπαραστάσεις για τα κυκλωματικά στοιχεία. Το κυρίως μοντέλο είναι ένας εναλλασσόμενος

κωδικοποιητής που χρησιμοποιεί καθοδήγηση επιγραφής για να μετατρέψει τις παραμέτρους των στοιχείων σε συνεχείς μεταβλητές. Οι λανθάνουσες μεταβλητές του μοντέλου, που είναι συνεχείς, αντικαθιστούν τις μεταβλητές των στοιχείων στον ορισμό του προβλήματος βελτιστοποίησης. Η επίλυση του προβλήματος με τον νέο ορισμό γίνεται με την προτεινόμενη Μπεϋζιανή Βελτιστοποίηση και επιδεικνύει ικανοποιητικά αποτελέσματα.

Στο τελικό κεφάλαιο, τα συμπεράσματα της έρευνας που διεξήχθη διατυπώνονται, κατευθύνσεις για μελλοντικές εξελίξεις της δουλειάς αναφέρονται και συζητείται η πιθανή επιρροή της δουλειάς αυτής στην βιομηχανία και την κοινωνία.

**Λέξεις Κλειδιά** Αναλογικά ολοκληρωμένα κυκλώματα, αυτόματη διαστασιοποίηση κυκλωμάτων, βελτιστοποίηση μαύρου κουτιού, Εξελικτικοί Αλγόριθμοι, Μπεϋζιανή Βελτιστοποίηση, Γκαουσιανές Διαδικασίες, Thompson Sampling, Βαθιά Μάθηση, Εναλλασόμενος Κωδικοποιητής

## Εκτεταμένη Περίληψη

Η παρούσα διατριβή πραγματεύεται την διατύπωση της διαδικασίας διαστασιοποίησης ολοκληρωμένων αναλογικών και υψίσυχνων κυκλωμάτων ως πρόβλημα βελτιστοποίησης καθώς και την ανάπτυξη αλγορίθμων για την αυτόματη επίλυσή του.

Ολοκληρωμένα κυκλώματα, η αλλιώς τσιπ, είναι σύνολα από ηλεκτρονικά στοιχεία τα οποία κατασκευάζονται σε ένα μικρό, επίπεδο κομμάτι ημιαγωγού, συνήθως πυριτίου. Στις μέρες μας, μεγάλοι αριθμοί μικροσκοπικών MOSFET (τρανζίστορ πεδίου δράσης οξειδίου μετάλλου-ημιαγωγών) ενσωματώνονται σε μικρά τσιπ, οδηγώντας σε κυκλώματα που είναι τάξεις μεγέθους μικρότερα, ταχύτερα και λιγότερο ακριβά από αυτά που κατασκευάζονται από παραδοσιακά διακριτά ηλεκτρονικά εξαρτήματα. Στα πλεονεκτήματά τους συγκαταλέγεται η δυνατότητα μαζικής και αξιόπιστης παραγωγής, γεγονός που έχει διασφαλίσει την ταχεία υιοθέτηση τυποποιημένων τσιπ στη θέση των σχεδίων που χρησιμοποιούν διακριτά τρανζίστορ. Τα τσιπ χρησιμοποιούνται πλέον σχεδόν σε όλο τον ηλεκτρονικό εξοπλισμό και έχουν φέρει επανάσταση στον κόσμο των ηλεκτρονικών. Οι υπολογιστές, τα κινητά τηλέφωνα και άλλες οικιακές συσκευές αποτελούν πλέον αναπόσπαστα μέρη των σύγχρονων κοινωνιών, και γίνονται εφικτά από το μικρό μέγεθος και το χαμηλό κόστος ηλεκτρονικών συστημάτων, όπως οι σύγχρονοι επεξεργαστές υπολογιστών και οι μικροελεγκτές.

Η ενσωμάτωση πολύ μεγάλης κλίμακας (Very Large Scale Integration - VLSI), δηλαδή η κατασκευή ολοκληρωμένων κυκλωμάτων με εκατοντάδες χιλιάδες έως δισεκατομμύρια τρανζίστορ, είναι δυνατή χάρη στις τεχνολογικές εξελίξεις στην κατασκευή στοιχείων ημιαγωγών μετάλλου-οξειδίου-πυριτίου (MOS). Από την κατασκευή του πρώτου τσιπ την δεκαετία του 1960, η ταχύτητα και το μέγεθός τους βελτιώνονται σταθερά. Ο κύριος λόγος για αυτό το φαινόμενο είναι η συρρίκνωση της ελάχιστης διάστασης των τρανζίστορ που μπορούν να κατασκευαστούν. Εμπειρικά, τα στοιχεία που περιέχονται στα τσιπ συνεχώς γίνονται πιο μικρά, γεγονός που οδηγεί στον διπλασιασμό του αριθμού των τρανζίστορ που περιλαμβάνει ένα τσιπ κάθε διετία. Η πιο πυκνή ολοκλήρωση τρανζίστορ στα τσιπ οδηγεί σε πλεονεκτήματα όπως χαμηλή κατανάλωση και υψηλότερη ταχύτητα. Για την αγορά ημιαγωγών, όμως, η συρρίκνωση των διαστάσεων επέφερε σημαντική οικονομική ανάπτυξη, λόγω της δυνατότητας για ενσωμάτωση πολλών, διαφορετικών και πολύπλοκων λειτουργιών στα συγχρονα τσιπ και της υιοθέτησής τους από πολλές διαφορετικές βιομηχανίες.

Υπάρχουν δύο κύριοι τύποι ηλεκτρονικών κυκλωμάτων που μπορούν να ολοκληρωθούν σε τσιπ, τα αναλογικά και τα ψηφιακά κυκλώματα. Τα ψηφιακά κυκλώματα λειτουργούν σε σήματα που έχουν διακριτές τιμές, κυρίως δυαδικές. Αντίθετα, τα αναλογικά κυκλώματα λειτουργούν σε ηλεκτρικά σήματα με συνεχείς τιμές. Ο ρόλος των αναλογικών κυκλωμάτων

στα τσιπ είναι η υλοποίηση διεπαφών με το ψηφιακό κομμάτι και το εξωτερικό περιβάλλον. Αντιθέτως, τα ψηφιακά κυκλώματα υλοποιούν τις περισσότερες λειτουργίες και καταλαμβάνουν μεγαλύτερη επιφάνεια σε σχέση με τα αναλογικά. Όμως, τα αναλογικά κυκλώματα είναι ο δυσκολότερος και πιο απαιτητικός παράγοντας κατά το σχεδιασμό ολοκληρωμένων συστημάτων, γεγονός που οφείλεται στην φύση τους. Ενώ τα ψηφιακά κυκλώματα χρησιμοποιούν σήματα με δύο διακριτές τιμές και είναι πιο ανθεκτικά σε μη-ιδανικά φαινόμενα, η σχεδίαση αναλογικών κυκλωμάτων πρέπει να γίνεται με βάση τη φυσική που διέπει την κατασκευή των ολοκληρωμένων κυκλωμάτων και απαιτεί ειδικές δεξιότητες.

Η σχεδίαση των αναλογικών ολοκληρωμένων κυκλωμάτων είναι απαιτητική και για έναν επιπλέον λόγο. Ο χώρος σχεδίασης, δηλαδή το σύνολο των τιμών των διαστάσεων των ηλεκτρονικών στοιχείων που περιλαμβάνουν τα αναλογικά κυκλώματα καθώς και ο τρόπος με τον οποίο αυτά διασυνέδονται, είναι πρακτικά απεριόριστος. Στην πράξη, υπάρχουν πολλές τοπολογίες αναλογικών κυκλωμάτων που προσφέρουν παρόμοιες λειτουργίες, και η απόφαση για την επιλογή μιας έναντι των υπολοίπων δεν είναι προφανής, καθώς εξαρτάται από την φύση της εκάστοτε εφαρμογής. Επιπλέον, η διαστασιοποίηση των κυκλωματικών στοιχείων απαιτεί την επιλογή τιμών από ένα συνεχές εύρος, ενώ ο χώρος επίδοσης των κυκλωμάτων, δηλαδή το σύνολο των τιμών των μετρικών που περιγράφουν την λειτουργία των χυχλωμάτων, σχετίζεται άμεσα από την επιλογή των διαστάσεων των στοιχείων. Ηλεχτριχές ιδιότητες, όπως για παράδειγμα τιμές τάσεων και ρευμάτων, παίζουν σημαντικό ρόλο στην επίδοση του εκάστοτε κυκλώματος, γεγονός που δεν αφήνει περιθώρια για την υιοθέτηση ιερχικών μεθόδων σχεδίασης. Αντίθετα, συμπεριφορικά μοντέλα μπορούν να χρησιμοποιηθούν στην περίπτωση των ψηφιαχών χυχλωμάτων, αποχρύπτοντας από τον σχεδιαστή φαινόμενα ή λογικές χαμηλού επιπέδου. Τα παραπάνω συνηγορούν στο γεγονός ότι η σχεδίαση αναλογικών ολοκληρωμένων κυκλωμάτων απαιτεί σοβαρό αριθμό εργατο-ωρών, παρόλο που η λειτουργία τους στα ολοχληρωμένα χυχλώματα έχει περιοριστεί σημαντικά.

Οι σχεδιαστές ολοκληρωμένων κυκλωμάτων παραδοσιακά χρησιμοποιούν εξειδικευμένα εργαλεία λογισμικού, τα οποία βοηθούν στην διαχείριση σχεδίων με εξαιρετικά μεγάλο αριθμό στοιχείων. Τα εργαλεία αυτά αναφέρονται ως εργαλεία Ηλεκτρονικής Αυτόματης Σχεδίασης (Electronic Design Automation - EDA) και εισήχθησαν στην βιομηχανία την δεκαετία του 1980. Στις μέρες μας, τα εργαλεία EDA παρέχουν στους σχεδιαστές ψηφιακών κυκλωμάτων την δυνατότητα να ορίζουν κυκλώματα με τρόπο αφαιρετικό, που τους επιτρέπει να εστιάζουν στην λειτουργία του κυκλώματος και στον περιορισμό επαναλαμβανόμενων διαδικασιών με δομημένο τρόπο. Το αποτέλεσμα αυτής της δυνατότητας είναι η κατακόρυφη αύξηση στην αποδοτικότητα των σχεδιαστών, και η σχεδίαση ολοκληρωμένων ψηφιακών κυκλωμάτων με δισεκατομμύρια ενσωματωμένα στοιχεία.

$\Sigma$ την περίπτωση των αναλογικών κυκλωμάτων, όμως, τα εργαλεία EDA δεν έχουν προ-

σφέρει παρόμοιες δυνατότητες. Η χρήση αφαιρετικής λογικής για την σχεδίαση αναλογικών κυκλωμάτων δεν είναι δυνατή, καθώς παράγοντες όπως η φυσική σχεδίαση, η τοπολογία και η διαστασιοποίηση αλληλεπιδρούν και παίζουν ρόλο στην λειτουργία των κυκλωμάτων ταυτόχρονα. Η χειροκίνητη σχεδίαση, επομένως, αποτελεί τον μοναδικό τρόπο για την σχεδίαση και υλοποίηση αναλογικών λειτουργιών σε υλικό, ενώ τα EDA εργαλεία προσφέρουν μόνο δυνατότητες προσομοίωσης και επαλήθευσης των κυκλωμάτων. Αυτός ο περιορισμός έχει ως αποτέλεσμα η ροή σχεδίασης αναλογικών ολοκληρωμένων κυκλωμάτων να μην μπορεί να ανταποκριθεί σε σύγχρονα, πολύπλοκα συστήματα, τα οποία απαιτούν πολύ χρόνο και επαναλαμβανόμενες διαδικασίες για να υλοποιηθούν. Δεδομένου, λοιπόν, του περιορισμένου αυτοματισμού στη σχεδίαση αναλογικών ολοκληρωμένων κυκλωμάτων, απαιτούνται μέτρα για να διευκολυνθεί η δουλειά των αναλογικών σχεδιαστών.

Αυτή η εργασία επικεντρώνεται στην ανάπτυξη μεθόδων και αλγορίθμων για την εισαγωγή αυτοματισμών στον κλάδο της σχεδίασης αναλογικών ολοκληρωμένων κυκλωμάτων. Πιο συγκεκριμένα, μελετώνται τρόποι για την αυτόματη διαστασιοποίηση των στοιχείων που απαρτίζουν τα ολοκληρωμένα κυκλώματα, μέσω του ορισμού του προβλήματος διαστασιοποίησης ως πρόβλημα βελτιστοποίησης. Παρουσιάζονται μέθοδοι και αλγόριθμοι για την αυτοματοποίηση μιας σειράς από διαδικασίες που απασχολούν τους σχεδιαστές, όπως η βελτιστοποίηση της απόδοσης, η εξερεύνηση του σχεδιαστικού χώρου, η αυτόματη αλλαγή τεχνολογίας κατασκευής και η επαλήθευση της λειτουργίας των κυκλωμάτων.

#### Ορισμός του Προβλήματος Διαστασιοποίησης

Θεωρούμε ένα αναλογικό κύκλωμα με δεδομένη τοπολογία, τεχνολογία κατασκευής καθώς και ένα σύνολο παραμέτρων  $\mathbf{x}=[x_1,x_2,\ldots,x_N]$  που αντιστοιχούν στις γεωμετρικές διαστάσεις των στοιχείων του. Επιπλέον, θεωρούμε ως δεδομένα τα εύρη των τιμών που επιτρέπονται να λάβουν οι παράμετροι του  $\mathbf{x}$ , και τα συμβολίζουμε ως  $[\mathbb{S}_i]_{i=1}^N$ . Ο χώρος αναζήτησης (ή σχεδίασης)  $\mathbb{S}$  ορίζεται ως το υποσύνολο του  $\mathbb{R}^N$  από το οποίο μπορεί να παίρνει τιμές το  $\mathbf{x}$  και ισχύει  $\mathbb{S}=\mathbb{S}_1\times\mathbb{S}_2\times\cdots\times\mathbb{S}_N$ .

Για το δεδομένο κύκλωμα, θεωρούμε επίσης ένα σύνολο από k μετρικά  $Y=\{y_i(\mathbf{x})\}_{i=1}^k$  που καθορίζουν την λειτουργία και την απόδοση του κυκλώματος. Για παράδειγμα, στην περίπτωση ενός ενισχυτή χαμηλού θορύβου, αυτά θα μπορούσε να είναι η γραμμικότητα, το κέρδος μικρού σήματος, η θορυβική απόδοση, κλπ. Η σχεδίαση ενός αναλογικού κυκλώματος απαιτεί την εύρεση ενός καλού συμβιβασμού μεταξύ μετρικών που είναι αντικρουόμενα, δηλαδή η βελτίωση του ενός επιφέρει την χειροτέρευση του άλλου. Για αυτό τον λόγο, θεωρούμε σαν δεδομένο μια λίστα από προδιαγραφές, που ορίζουν περιορισμούς στις τιμές των μετρικών  $\mathbf{y}$ , καθώς και επιθυμητούς στόχους για μεγιστοποίηση ή ελαχιστοποίηση.

Με τα παραπάνω δεδομένα, μπορούμε να ορίσουμε τη διαστασιοποίηση του χυχλώματος

ως ένα πρόβλημα βελτιστοποίησης:

min

$$F(\mathbf{x})$$

,  $\mathbf{x} \in \mathbb{S}$

s.t.  $g_j(\mathbf{x}) \le 0$ ,  $j = 1, \dots, l$ . (1)

Ανάλογα με τις προδιαγραφές, η συνάρτηση  $F(\mathbf{x})$  μπορεί να είναι βαθμωτή ή διανυσματική, δηλαδή να περιλαμβάνει ένα ή και περισσότερα μετρικά από το Y. Οι l συναρτήσεις  $g_j(\mathbf{x})$  υλοποιούν τους περιορισμούς που επιβάλλουν οι προδιαγραφές στα μετρικά του Y ως ανισότητες. Η επίλυση του προβλήματος αυτού οδηγεί σε ένα βέλτιστο διάνυσμα παραμέτρων  $\mathbf{x}^*$ , που υποδηλώνει τις διαστάσεις των στοιχείων του κυκλώματος που ικανοποιούν βέλτιστα τις προδιαγραφές.

#### Αυτόματη Διαστασιοποίηση με Χρήση Προσομοίωσης

Για την επίλυση του προβλήματος (1), δύο παράγοντες παίζουν καθοριστικό ρόλο. Ο πρώτος είναι ο αλγόριθμος με τον οποίο θα προσεγγιστεί το βέλτιστο, ενώ ο δεύτερος είναι ο τρόπος με τον οποίο οι συναρτήσεις  $F(\mathbf{x})$ ,  $[g_i(\mathbf{x})]_{i=1}^l$ , και συνεπώς τα μετρικά Y, υπολογίζονται.

Η διαδικασία υπολογισμού των μετρικών του κυκλώματος μπορεί να γίνει με δύο κύριους τρόπους, με τη χρήση εξισώσεων κλειστού τύπου ή την χρήση προσομοιωτών. Οι κυκλωματικές εξισώσεις απαιτούν ανάλυση του κυκλώματος με το χέρι, συνυπολογισμό φαινομένων όπως παρασιτικά μεγαλύτερων τάξεων και σημαντική προσπάθεια από τον σχεδιαστή. Επιπρόσθετα, στις περιπτώσεις κυκλωμάτων με σεβαστό αριθμό από μετρικά, οι εξισώσεις καταλήγουν να είναι δυσεπίλυτες.

Αντιθέτως, με τη χρήση προσομοιωτών για τον υπολογισμό των χυχλωματιχών μετριχών μπορούμε να έχουμε 1) μεγάλη αχρίβεια, η οποία εξαρτάται από τα μοντέλα των ημιαγωγών που χρησιμοποιούνται κατά την προσομοίωση και όχι από τον ίδιο τον σχεδιαστή και, 2) ένα πιο εύχρηστο περιβάλλον αυτόματης διαστασιοποίησης που δεν απαιτεί σημαντιχές εισόδους από τους σχεδιαστές. Στην εργασία αυτή αναπτύχθηκε λογισμιχό που υλοποιεί διεπαφή με τον εμποριχό προσομοιωτή Cadence Spectre και είναι υπεύθυνο για την αυτόματη εκκίνηση προσομοιώσεων, την ανάγνωση και επεξεργασία των αποτελεσμάτων του προσομοιωτή, την ανανέωση των παραμέτρων των κυκλωμάτων πριν από κάθε προσομοίωση, τον ορισμό αναλύσεων που θα εφαρμοστούν από τον προσομοιωτή στο χύκλωμα καθώς και την παραλληλοποίησή τους. Η μοναδιχή είσοδος που απαιτείται από αυτή την προσέγγιση είναι παραμετροποιημένα σχηματικά του χυκλώματος (testbenches), καθώς και η λίστα με τις προδιαγραφές για το κύκλωμα. Με αυτή την προσέγγιση μαύρου κουτιού, ο σχεδιαστής μπορεί να εστιάσει στην επιθυμητή απόδοση του κυκλώματος, ανεξάρτητα από την τοπολογία ή τις εξισώσεις που το διέπουν, καθώς αυτές λαμβάνονται

εμμέσως υπόψη μέσω του σχηματικού και του προσομοιωτή.

#### Διαστασιοποίηση με Χρήση Εξελικτικών Αλγόριθμων

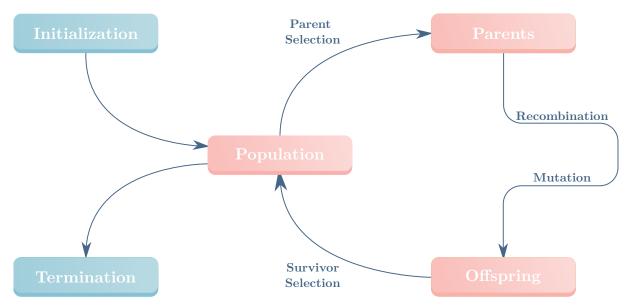

Ο κλάδος των Εξελικτικών Αλγορίθμων μιμείται φυσικές αρχές και φαινόμενα για να πετύχει μια μορφή αυτοματισμού κατά την επίλυση προβλημάτων όπως η βελτιστοποίηση. Οι Εξελικτικοί Αλγόριθμοι αντλούν έμπνευση από την θεωρία εξέλιξης του Δαρβίνου καθώς και από την γενετική, και θεωρούν δύο βασικές υποθέσεις. Πρώτον, υπάρχει ένα περιβάλλον που μπορεί να υποστηρίξει συγκεκριμένο αριθμό από οντότητες, και δεύτερον κάθε οντότητα στοχεύει στην αναπαραγωγή της. Οι οντότητες έχουν ξεχωριστά χαρακτηριστικά, τα οποία καθορίζουν την ικανότητά τους να προσαρμόζονται στο περιβάλλον και να αναπαράγονται. Η δυνατότητα αυτή ποσοτικοποιείται από το μετρικό της καταλληλότητας.  $\Sigma$ υνέπεια των παραπάνω είναι ότι οι οντότητες ανταγωνίζονται για να αναπαραχ $\vartheta$ ούν και να επιζήσουν, καθώς ο συνολικός πληθυσμός τους είναι περιορισμένος. Κατά την αναπαραγωγή, τα χαρακτηριστικά των απογόνων προκύπτουν από συνδυασμό των γονέων-οντοτήτων και ορισμένων τυχαίων παραλλαγών. Η εξελικτική διαδικασία που ακολουθούν οι αλγόριθμοι αυτοί, λοιπόν, βασίζεται τόσο στον ανταγωνισμό μεταξύ των οντοτήτων όσο και στην ποικιλία των χαρακτηριστικών που προκύπτουν κατά την αναπαραγωγή, έτσι ώστε να καταλήξουν σε οντότητες που προσαρμόζονται καλύτερα στο περιβάλλον και είναι διαφορετικές μεταξύ τους.

Υπάρχει μεγάλη ποιχιλία από Εξελικτιχούς αλγόριθμους που αχολουθούν την παραπάνω μεθοδολογία στην βιβλιογραφία. Ένας διαχωρισμός που μας είναι χρήσιμος στο πλαίσιο της διατριβής αυτής είναι με βάση τα προβλήματα που επιλύουν. Στην περίπτωση όπου οι προδιαγραφές για ένα χύχλωμα είναι σε μορφή επίτευξης ενός μοναδιχού στόχου, για παράδειγμα μεγιστοποίηση του εύρους ζώνης ενός ενισχυτή, το πρόβλημα ονομάζεται Μοναδιχού Στόχου και η συνάρτηση  $F(\mathbf{x})$  στην εξίσωση (1) είναι βαθμωτή. Αντίθετα, στην περίπτωση που οι προδιαγραφές για ένα χύχλωμα απαιτούν την εύρεση της χαλύτερης συμβιβαστιχής λύσης μεταξύ δύο ή περισσότερων στόχων, όπως για παράδειγμα το χέρδος χαμηλού σήματος χαι το εύρος ζώνης ενός ενισχυτή, η  $F(\mathbf{x})$  είναι διανυσματιχή συνάρτηση. Συνεπώς, το βέλτιστο ενδέχεται να μην είναι μοναδιχό χαι η χαταλληλότητα των οντοτήτων του αλγορίθμου ορίζεται με τρόπο ώστε να λαμβάνει υπόψη το πόσο χαλό συμβιβασμό μεταξύ των δύο μετριχών προσφέρουν, χαθώς χαι πόσο διαφορετιχά είναι από τον υπόλοιπο πληθυσμό. Τα προβλήματα αυτά αναφέρονται ως Πολλαπλών Στόχων χαι χρησιμοποιούνται στα πλαίσια της διατριβής για την εξερεύνηση του σχεδιαστιχού χώρου των χυχλωμάτων.

Για την επιτυχή έκβαση της διαστασιοποίησης μέσω του ορισμού (1), είναι σημαντικό ο σχεδιαστής να συμπεριλάβει μια σειρά από περιορισμούς που, όταν πληρούνται, εξασφαλί-

ζουν την ομαλή λειτουργία του κυκλώματος. Οι Εξελικτικοί Αλγόριθμοι, όμως, πρέπει να προσαρμοστούν στο νέο πρόβλημα για να διαχειρίζεται τους περιορισμούς αυτούς. Όταν υπάρχουν περιορισμοι, ο στόχος του αλγόριθμου γίνεται διπλός: να οδηγήσει την αναζήτηση, δηλαδή τις οντότητες, σε μια περιοχή του χώρου αναζήτησης όπου οι περιορισμοί ικανοποιούνται και εκεί να βρει τις βέλτιστες λύσεις. Για αυτόν τον λόγο, στην εργασία αυτή, οι Εξελικτικοί Αλγόριθμοι τροποποιούνται ώστε η επιβίωση ή μη μιας οντότητας να καθορίζεται από ένα σύστημα προτιμήσεων, το οποίο λαμβάνει υπόψη τόσο την καταλληλότητα της κάθε οντότητας όσο και τον βαθμό παραβίασης περιορισμών της.

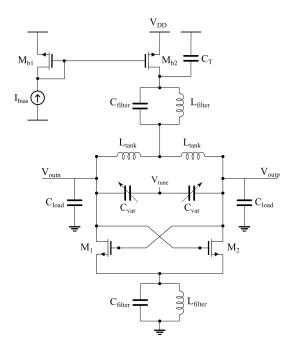

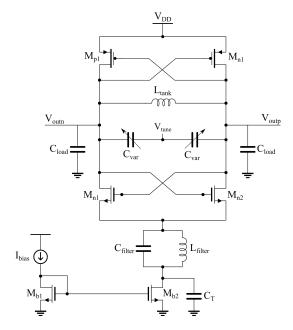

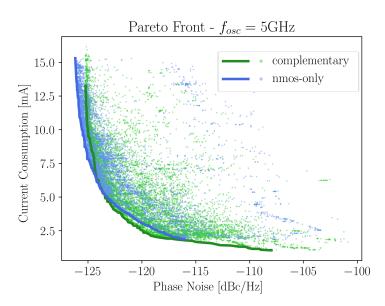

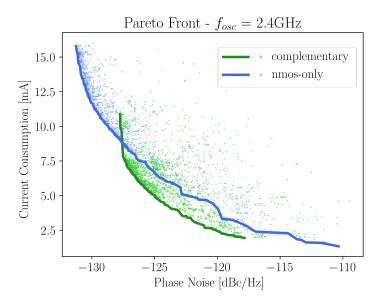

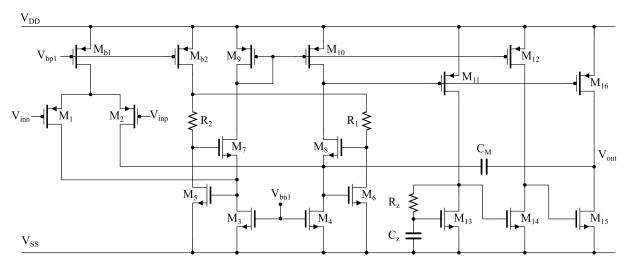

Στα πλαίσια της διατριβής, σχεδιάζονται δύο ταλαντωτές LC σε τεχνολογία κατασκευής TSMC 90nm και οι επιθυμητές προδιαγραφές τους ορίζονται με τρόπο που εξασφαλίζεται η επιθυμητή συχνότητα ταλάντωσης. Για την διερεύνηση των διαφορών μεταξύ των δύο τοπολογιών, εξετάζονται οι χώροι απόδοσης τους, όσον αφορά το συμβιβασμό μεταξύ θορύβου φάσης και κατανάλωσης ισχύος. Χρησιμοποιώντας Εξελικτικούς Αλγόριθμους, φτάνουμε στο συμπέρασμα ότι η μία τοπολογία υπερέχει της άλλης, όσον αφορά τον ελάχιστο εφικτό θόρυβο φάσης για παρόμοιες καταναλώσεις ισχύος.

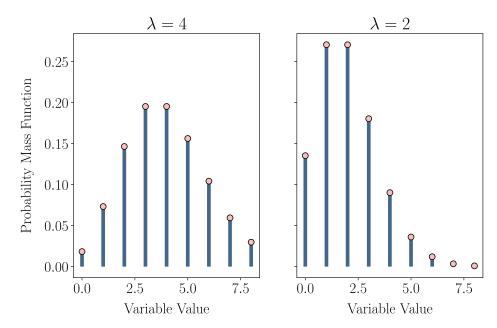

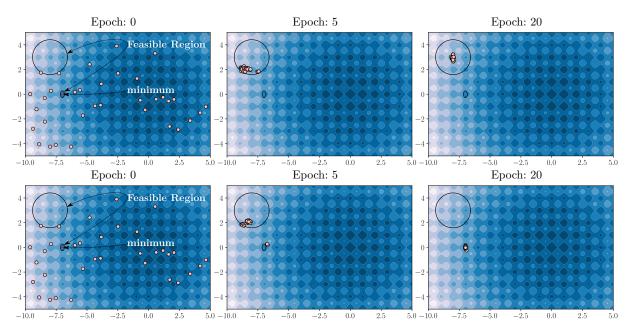

Για την περαιτέρω βελτίωση της απόδοσης των Εξελικτικών Αλγορίθμων, όσον αφορά τις λύσεις που αποδίδουν σε προβλήματα Πολλαπλών Στόχων με περιορισμούς, προτείνουμε μια παραλλαγή του Εξελικτικου Αλγορίθμου NSGA-II, ώστε να διαχειρίζεται χώρους αναζήτησης με μικτές συνεχείς-διακριτές μεταβλητές όταν υπάρχουν περιορισμοί. Ο μηχανισμός επιλογής οντοτήτων που επιβιώνουν τροποποιείται, ώστε να λαμβάνει υπόψη την καταλληλότητα λύσεων που δεν ικανοποιούν τους περιορισμούς. Η διαχείριση του χώρου αναζήτησης με μικτές μεταβλητές γίνεται με την υιοθέτηση ενός συστήματος παραλλαγής, όπου οι διακριτές μεταβλητές αλλαζουν τιμές ακολουθώντας μια κατανομή Poisson. Ο προτεινόμενος αλγόριθμος εφαρμόζεται σε έναν ενισχυτή χαμηλού θορύβου και έναν τελεστικό ενισχυτή, για την εξερεύνηση του χώρου απόδοσης τους. Και στις δύο περιπτώσεις καταφέρνουμε να πάρουμε καλύτερους συμβιβασμους μεταξύ των αντικρουόμενων μετρικών των κυκλωμάτων.

#### Διαστασιοποίηση με Χρήση Αλγόριθμων Χαμηλού Κόστους

Η αυτόματη διαστασιοποίηση πολύπλοκων κυκλωμάτων, με χώρους αναζήτησης πολλών διαστάσεων και αυστηρούς περιορισμούς ως προδιαγραφές, είναι ένα δύσκολο πρόβλημα που απαιτεί, στην περίπτωση των Εξελικτικών Αλγορίθμων, πολλές προσομοιώσεις για την αξιολόγηση των πληθυσμών των οντοτήτων. Στην πράξη, η προσομοίωση κυκλωμάτων ενδέχεται να είναι μια κοστοβόρα χρονικά διαδικασία, καθώς μια προσομοίωση μπορεί να χρειάζεται ώρες για να ολοκληρωθεί, γεγονός που καθιστά τις πληθυσμιακές μεθόδους, όπως τους Εξελικτικούς Αλγόριθμους, μη πρακτικούς. Για τους λόγους αυτούς, μια νέα

προσέγγιση στην αυτόματη διαστασιοποίηση αναλογικών προβλημάτων με χρήση αλγορίθμων χαμηλής δειγματοληψίας του χώρου αναζήτησης προτείνεται. Η προσέγγιση βασίζεται στην Μπεϋζιανή εκτίμηση και αναφέρεται ως Μπεϋζιανή Βελτιστοποίηση.

Η Μπεϋζιανή Βελτιστοποίηση είναι μια μέθοδος βελτιστοποίησης αποδοτικής δειγματοληψίας του χώρου αναζήτησης, που στοχεύει κυρίως σε υπολογιστικά ακριβά προβλήματα. Στην τυπική μορφή της, όπου δεν λαμβάνονται υπόψη περιορισμοί, της παρέχονται παρατηρήσεις από μια συνάρτηση f και αυτή δημιουργεί ένα γρήγορο στην αξιολόγηση μοντέλο. Τα σημεία του χώρου αναζήτησης για προσομοίωση, ή αλλιώς σημεία ερωτήματος, επιλέγονται σειριακά σε κάθε επανάληψη. Η Μπεϋζιανή Βελτιστοποίηση αποτελείται από δύο βασικά συστατικά: 1) ένα πιθανοτικό μοντέλο που προσεγγίζει την άγνωστη συνάρτηση f και 2) μια συνάρτηση απόκρισης  $a:\mathbb{S}\to\mathbb{R}$ , που ορίζει ένα μέτρο για την καταλληλότητα κάθε σημείου στο χώρο αναζήτησης, με βάση το πιθανοτικό μοντέλο. Συνήθως, το μοντέλο αυτό είναι μια Γκαουσιανή Διαδικασία, που εκπαιδεύεται και χρησιμοποιείται σε κάθε επανάληψη.

Για να προσαρμόσουμε την Μπεϋζιανή Βελτιστοποίηση στα προβλήματα βελτιστοποίησης που προχύπτουν κατά την αυτόματη διαστασιοποίηση αναλογικών χυχλωμάτων, προτείνουμε μια σειρά από τροποποιήσεις στη βασιχή της μορφή:

- 1. Οι Γκαουσιανές Διαδικασίες χρησιμοποιούν συναρτήσεις πυρήνα για να ορίσουν μια συνάρτηση πυκνότητας πιθανότητας στο χώρο των συναρτήσεων. Οι συναρτήσεις πυρήνα, όμως, χρησιμοποιούν την Ευκλείδεια απόσταση μεταξύ των σημείων παρατηρήσεων για να ορίσουν με την σειρά τους την συνδιακύμανση μεταξύ τιμών της άγνωστης συνάρτησης που μοντελοποιούν. Ο σημαντικός περιορισμός που προκύπτει είναι η απώλεια πληροφορίας σε χώρους με πολλές διαστάσεις, όπου η Ευκλείδεια απόσταση δεν παρέχει ιδιαίτερα χρήσιμες πληροφορίες. Για την εξομάλυνση του φαινομένου αυτού, προτείνεται μια τοπική προσέγγιση στο πρόβλημα της βελτιστοποίησης, όπου η Μπεϋζιανή Βελτιστοποίηση λειτουργεί και μοντελοποιεί την άγνωστη συνάρτηση σε περιφέρειες εμπιστοσύνης, αντί στο σύνολο του χώρου αναζήτησης.

- 2. Η σειριαχή φύση του τυπικού αλγορίθμου δεν είναι αποδοτική από την ακόλουθη σκοπιά: Σε κάθε επανάληψη, ένα μοναδικό σημείο ερωτήματος επιλέγεται, προσομοιώνεται και χρησιμοποιείται για την ανανέωση των Γκαουσιανών μοντέλων. Επομένως, το υπολογιστικό κόστος της εκπαίδευσης των μοντέλων μας επιβαρύνει για μία μοναδική παρατήρηση, ενώ επίσης δεν χρησιμοποιούνται στο έπακρο οι διαθέσιμοι πόροι που επιτρέπουν την παραλληλοποίηση πολλών προσομοιώσεων. Για αυτό τον λόγο, ορίζουμε μια νέα συνάρτηση απόκρισης, η οποία επιτρέπει την επιλογή πολλών σημείων ερωτήματος σε κάθε επανάληψη, με αποτέλεσμα να έχουμε στη διάθεσή μας περισσότερη πληροφορία στο ίδιο χρονικό παράθυρο.

- 3. Η τυπική Μπεϋζιανή Βελτιστοποίηση δεν λαμβάνει υπόψη περιορισμούς κατά την επίλυση προβλημάτων. Για να προσαρμοστεί στον ορισμό της σχέσης (1), επεκτείνουμε την προτεινόμενη συνάρτηση απόκτισης ώστε να συνυπολογίζει την πιθανότητα τα σημεία αναζήτησης να ικανοποιούν τους περιορισμούς.

- 4. Για να περιορίσουμε το κόστος εκπαίδευσης των Γκαουσιανών Διαδικασιών, όταν τα σημεία ερωτήματος είναι πολλά σε αριθμό, χρησιμοποιούμε μια μέθοδο από χαρακτηριστικά σημεία, τα οποία αντικαθιστούν μέλη από το αρχικό σύνολο δεδομένων που θα έπρεπε διαφορετικά να χρησιμοποιηθεί.

- 5. Προτείνουμε την χρήση Τυχαίων Χαρακτηριστικών Φουριέ, ώστε να βελτιώσουμε την επίδοση της συνάρτησης απόκτισης σε προβλήματα μεγάλων διαστάσεων, αντικαθιστώντας την διαδικασία δειγματοληψίας από Γκαουσιανές διαδικασίες με μία νέα, όπου χτίζονται αναλυτικές συναρτήσεις ως δείγματα.

- 6. Προτείνουμε παραλλαγές Μπεϋζιανής Βελτιστοποίησης που μπορούν να λύσουν προβλήματα Μοναδικού και Πολλαπλών Στόχων.

Οι παραπάνω μέθοδοι εφαρμόζονται για την αυτόματη διαστασιοποίηση μια σειράς αναλογικών κυκλωμάτων, που περιλαμβάνουν τελεστικούς ενισχυτές πολλών σταδίων και ενισχυτές χαμηλού θορύβου. Τα προβλήματα διαστασιοποίησης λαμβάνουν υπόψη την επίδοση του εκάστοτε κυκλώματος τόσο σε τυπικές συνθήκες, όσο και σε συνθήκες με διακυμάνσεις τάσης, θερμοκρασίας και κατασκευής. Η χρήση της Μπεϋζιανής μεθόδου για την διαστασιοποίηση επιφέρει καλύτερα αποτελέσματα σε σχέση με μία σειρά άλλων μεθόδων στη βελτιστοποίηση και την εξερευνηση του χώρου επίδοσης, για παρόμοιο αριθμό προσομοιώσεων.

#### Εκμάθηση Αναπαραστάσεων Κυκλωματικών Στοιχείων

Για την εύρωστη μοντελοποίηση διακριτών χώρων αναζήτησης μέσω Γκαουσιανών διαδικασιών, προτείνεται μια μέθοδος αναπαράστασης κυκλωματικών στοιχείων με συνεχείς μεταβλητές, με χρήση Βαθιάς Μάθησης. Οι γεωμετρίες στοιχείων όπως τα ολοκληρωμένα πηνία παραμετροποιούνται τόσο με συνεχείς, όσο και με διακριτές μεταβλητές, γεγονός που καθιστά αδύνατη την μοντελοποίηση του χώρου αναζήτησης από Γκαουσιανές διαδικασίες με τυπικές συναρτήσεις πυρήνα. Για τον λόγο αυτό, προτείνουμε την εκμάθηση αναπαραστάσεων που λαμβάνουν συνεχείς τιμές, με χρήση δεδομένων από προσομοίωση. Με την αντικατάσταση των αρχικών πεδίων ορισμού, που αντιστοιχούν σε στοιχεία με μικτές συνεχείς-διακριτές μεταβλητές, από τις συνεχείς αναπαραστάσεις τους, καθιστούμε το πρόβλημα βελτιστοποίησης συνεχές.

Η μέθοδός μας περιλαμβάνει ένα γενετικό μοντέλο λανθανουσών μεταβλητών, το οποίο αντιστοιχεί σημεία από έναν χώρο  $\mathbb Z$  στον αρχικό χώρο αναζήτησης του προβλήματος,  $\mathbb S$ . Για να εξασφαλίσουμε ότι ο λανθάνων χώρος  $\mathbb Z$  είναι δομημένος με τρόπο που θα εξυπηρετεί την βελτιστοποίηση, περιλαμβάνεται ένα επιπλέον μοντέλο καθοδήγησης το οποίο εκπαιδεύεται παράλληλα με το γενετικό μοντέλο. Το μοντέλο καθοδήγησης εκπαιδεύεται ώστε να αντιστοιχεί σημεία από τον  $\mathbb Z$  σε πραγματικές διαστάσεις των στοιχείων που μοντελοποιούνται. Οι αναπαραστάσεις των κυκλωματικών στοιχείων φτιάχνονται με τρόπο τέτοιο ώστε να εξασφαλίζεται ότι λειτουργικά παρόμοιες γεωμετρίες είναι κοντά στον  $\mathbb Z$ . Αυτό επιτυγχάνεται με τη χρήση δεδομένων προσομοίωσης που αντικατοπτρίζουν τις επιδόσεις του εκάστοτε στοιχείου, ως εισόδους του γενετικού μοντέλου. Κατά την βελτιστοποίηση, ο αλγόριθμος αναζητά τιμές στον λανθάνων χώρο, οι οποίες περνούν από το δίκτυο καθοδήγησης για να μετατραπούν σε πραγματικές γεωμετρίες και έπειτα λαμβάνει χώρα η προσομοίωση.

Για την επαλήθευση της προτεινόμενης μεθόδου έγιναν τα εξής πειράματα: 1) Μοντελοποίηση ολοκληρωμένων σπειροειδών πηνίων και 2) μοντελοποίηση ολοκληρωμένων μεταλλιών πυκνωτών. Και τα δύο στοιχεία περιλαμβάνουν διακριτές μεταβλητές κατά τον ορισμό της γεωμετρίας τους. Μια σειρά από κυκλώματα έγιναν βελτιστοποίηση με χρήση των αναπαραστάσεων των προαναφερθέντων στοιχείων, με αποτελέσματα που υποδηλώνουν την ακριβή μοντελοποίηση και την βελτίωση της απόδοσης των Μπεϋζιανών μεθόδων σε πλήρης συνεχείς χώρους αναζήτησης.

## Acknowledgements

First and foremost, I would like to express my sincere gratitude to my supervisor, Professor Pavlos-Petros P. Sotiriadis. His assistance, insightful comments, suggestions and continuous support were crucial for the completion of my Ph.D. research. With his immense expertise, Professor Sotiriadis gracefully offered me his knowledge in Mathematics and Engineering and guided me through the paths of my research. What an amazing journey I was lucky and glad to have with him. It has been an honor to have worked under his supervision and to have received his support.

I would also like to deeply thank Professor Nikolaos Maratos and Professor Ioanna Roussaki for serving as members of my advisory committee. Also, I would like to express my gratitude to Professors Stefanos Kollias, Dimitra Kaklamani, Giorgos Stamou, Athanasios Panagopoulos and Nuno Lourenço, for participating in my examination committee.

I am also grateful to all my colleagues and students in the Circuits and Systems Group of Professor Sotiriadis, with whom I have shared many wonderful and memorable moments during the past years. Our collaboration and friendship were crucial in making the Ph.D. experience productive and enjoyable. Special thanks to my kind friends from the lab, Kostas Asimakopoulos, Dimitris Baxevanakis, Dr. Chris Dimas, Dr. Kostas Papafotis and Dr. Nikos Temenos.

Getting through my Ph.D. studies required more than academic support, and I have many, many people to thank for being next to me over the past years. For their support and for many memorable evenings and vacations, I would like to thank my friends from Highschool and the University and wish them the best in their endeavors.

My family was most important to me in my pursuit of the Ph.D. I would like to thank my parents, Thanasis and Vasiliki, whose love and guidance are always with me in whatever I pursue, and my beloved sister, Semina, who cares for me and supports me in my endeavors.

This research is co-financed by Greece and the European Union (European Social Fund-ESF) through the Operational Programme «Human Resources Development, Education and Lifelong Learning» in the context of the project "Strengthening Human Resources Research Potential via Doctorate Research" (MIS-5000432), implemented by the State Scholarships Foundation (IK $\Upsilon$ )

## Contents

| 1 | Intr | oducti | ion                                | 37 |

|---|------|--------|------------------------------------|----|

|   | 1.1  | Motiv  | ation                              | 38 |

|   | 1.2  | Thesis | s Contributions                    | 42 |

|   | 1.3  | Thesis | s Outline                          | 44 |

| 2 | Rel  | ated V | Vork                               | 47 |

|   | 2.1  | Know   | ledge-Based Approaches             | 47 |

|   | 2.2  | Optim  | nization-Based Approaches          | 49 |

|   |      | 2.2.1  | Model-Based Sizing                 | 49 |

|   |      | 2.2.2  | Simulation-Based                   | 51 |

|   | 2.3  | Other  | Approaches                         | 53 |

| 3 | Evo  | lution | ary Algorithm-based                |    |

|   | Sizi |        |                                    | 55 |

|   | 3.1  | Evolu  | tionary Computation Preliminaries  | 55 |

|   |      | 3.1.1  | Genetic Algorithms                 | 58 |

|   |      | 3.1.2  | Differential Evolution             | 59 |

|   |      | 3.1.3  | Covariance Matrix Adaptation       | 60 |

|   | 3.2  | Single | -Objective Sizing                  | 61 |

|   | 3.3  | Multi- | Objective Sizing                   | 61 |

|   | 3.4  | Const  | raint Handling                     | 62 |

|   | 3.5  | Applie | cation in Design Space Exploration | 63 |

|   |      | 3.5.1  | LC-VCO topologies                  | 64 |

|   |      | 3.5.2  | LC-VCO Optimization                | 65 |

|   | 3.6  | Propo  | sed Multi-Objective Variant        | 69 |

|   |      | 3.6.1  | Handling Integer Parameters        | 69 |

|   |      | 3.6.2  | Constraint Handling                | 70 |

|   |      | 3.6.3  | Example Applications               | 71 |

|   |      | 3.6.4  | Inductorless Wideband LNA          | 74 |

|   | 3.7  | Summ   | nary & Concluding Remarks          | 77 |

24 Contents

| 4 | San  | nple-Ef                | fficient Single-Objective             |            |

|---|------|------------------------|---------------------------------------|------------|

|   | Sizi | $\mathbf{n}\mathbf{g}$ |                                       | <b>7</b> 9 |

|   | 4.1  | Backg                  | round                                 | 79         |

|   |      | 4.1.1                  | Gaussian Processes                    | 79         |

|   |      | 4.1.2                  | Bayesian Optimization                 | 85         |

|   |      | 4.1.3                  | BO & Constraint Handling              | 88         |

|   | 4.2  | Propos                 | sed Approach                          | 90         |

|   |      | 4.2.1                  | Local Bayesian Optimization           | 90         |

|   |      | 4.2.2                  | Scaling Up Gaussian Processes         | 92         |

|   | 4.3  | Circui                 | t Design Applications                 | 94         |

|   |      | 4.3.1                  | Three-Stage Amplifier                 | 95         |

|   |      | 4.3.2                  | High Linearity LNA                    | 96         |

|   | 4.4  | Summ                   | ary & Concluding Remarks              | 99         |

| 5 |      | _                      | fficient Design Space                 |            |

|   |      | oloratio               |                                       | 101        |

|   | 5.1  |                        | ocal Based Approach                   | 102        |

|   |      | 5.1.1                  | Sampling Functions from GP posteriors | 105        |

|   |      | 5.1.2                  | Acquisition Function                  | 110        |

|   |      | 5.1.3                  | Implementation                        | 114        |

|   |      | 5.1.4                  | Summary                               | 115        |

|   |      | 5.1.5                  | MOP Example                           | 118        |

|   | 5.2  | Circui                 | t Design Applications                 | 124        |

|   |      | 5.2.1                  | Three Stage Amplifier                 | 124        |

|   |      | 5.2.2                  | Four Stage Amplifier                  | 130        |

|   |      | 5.2.3                  | Low Noise Amplifier                   | 135        |

|   | 5.3  | Summ                   | ary & Concluding Remarks              | 139        |

| 6 |      |                        | epresentation Learning                | 141        |

|   | 6.1  |                        | ation                                 | 141        |

|   | 6.2  |                        | t Space Optimization                  | 142        |

|   |      | 6.2.1                  | Autoencoders                          | 142        |

|   |      | 6.2.2                  | Variational Autoencoders              | 143        |

|   |      | 6.2.3                  | Proposed Approach                     | 147        |

|   |      | 6.2.4                  | Applications on Integrated Devices    | 151        |

|   | 6.3  | Circui                 | t Design Applications                 | 156        |

|   |      | 6.3.1                  | Inductively Degenrated LNA            | 157        |

|   |      | 6.3.2                  | Wideband LNA                          | 160        |

| Contents | 25 |

|----------|----|

|----------|----|

|              | 6.4   | Summary & Concluding Remarks  | • | 164 |

|--------------|-------|-------------------------------|---|-----|

| 7            | Cor   | nclusions & Future Directions |   | 169 |

|              | 7.1   | Thesis Contributions          |   | 169 |

|              | 7.2   | Future Work                   |   | 170 |

| R            | efere | nces                          |   | 175 |

| $\mathbf{A}$ | ′ Арј | pendix A: Publications        |   | 193 |

26 Contents

| 1.1  | Historic evolution of the smallest manufacturing node [2]                         | 38 |

|------|-----------------------------------------------------------------------------------|----|

| 1.2  | Graphical illustration of the analog design gap [2]                               | 41 |

| 1.3  | A sample analog IC design flow. This work focuses on device sizing selection.     | 42 |

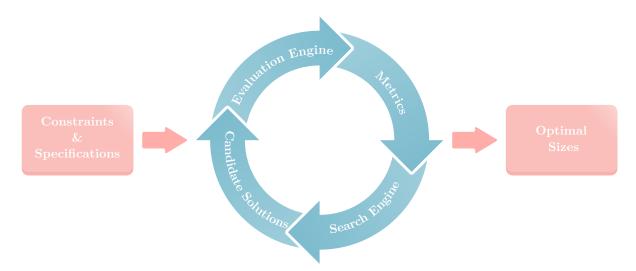

| 2.1  | An illustration of the optimization-based approach to analog circuit sizing.      | 49 |

| 3.1  | A flowchart depicting the general operation of EC-based optimization              |    |

|      | algorithms. Figure adapted from [76]                                              | 57 |

| 3.2  | A depiction of the single-point crossover operation in GAs                        | 59 |

| 3.3  | nMOS cross-coupled LC-VCO                                                         | 66 |

| 3.4  | Complementary nMOS-pMOS cross-coupled LC-VCO                                      | 66 |

| 3.5  | Acquired Pareto Fronts for both LC-VCO topologies, with $f_{osc}=5\mathrm{GHz}$   | 68 |

| 3.6  | Acquired Pareto Fronts for both LC-VCO topologies, with $f_{osc}=2.4\mathrm{GHz}$ | 69 |

| 3.7  | The probability mass function of two sample Poisson distributions with            |    |

|      | $\lambda = 2$ and $\lambda = 4$                                                   | 70 |

| 3.8  | Top row: Optimization run for a multimodal constrained function, using            |    |

|      | the feasibility rule. Bottom row: Optimization run using the constrained          |    |

|      | handling method proposed. Initial candidate vectors are identical                 | 72 |

| 3.9  | Nested Current Mirror amplifier proposed in [90]. Half-circuit instance           |    |

|      | names are shown, since the circuit is symmetric                                   | 73 |

| 3.10 | Pareto fronts for the NSGA-II algorithm with the proposed constraint              |    |

|      | handling method, and the typical NSGA-II with feasibility rule                    | 74 |

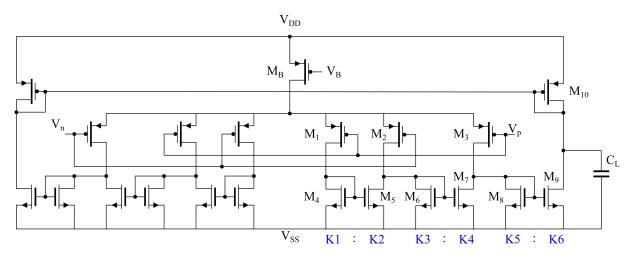

| 3.11 | Inductorless, wideband low noise amplifier proposed in [92]                       | 75 |

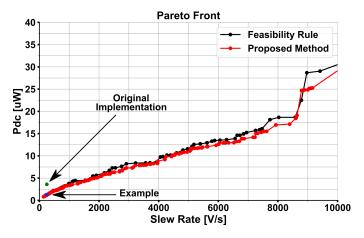

| 3.12 | Pareto fronts for the wideband LNA experiment                                     | 76 |

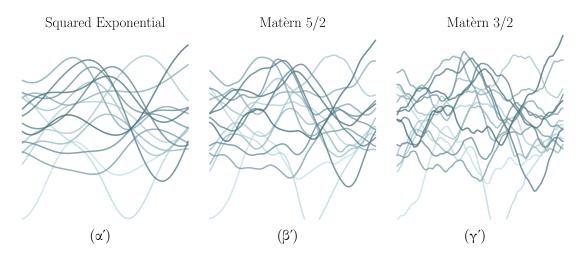

| 4.1  | Sampled functions from different GP priors                                        | 82 |

| 4.2  | A depiction of GP regression to a set of sinewave measurements. The               |    |

|      | measurements are shown as black stars, the actual sinewave is shown in            |    |

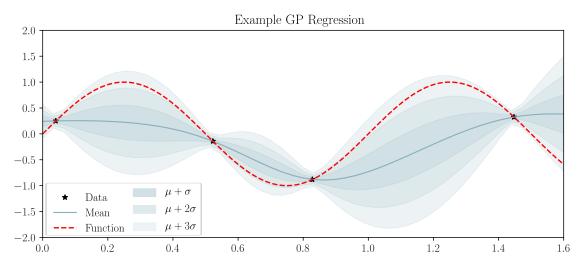

|      | red and the GP mean and confidence bounds are shown in blue                       | 84 |

| 4.3  | Example BO execution using the LCB acquisition function on an 1D                  |    |

|      | Ackley function.                                                                  | 89 |

| 4.4  | A GP's pointwise predictions on a test function (mean and 95% confidence bounds shown), along with 3 samples from a joint predictive distribution. Past queries are shown as black dots, while next queries are marked in |     |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

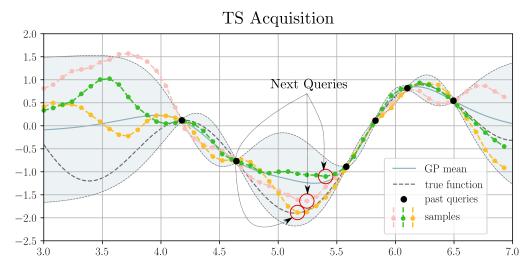

|      | red circles                                                                                                                                                                                                               | 92  |

| 4.5  | Three stage amplifier proposed in [106]                                                                                                                                                                                   | 95  |

| 4.6  | High Linearity LNA proposed in [107]                                                                                                                                                                                      | 97  |

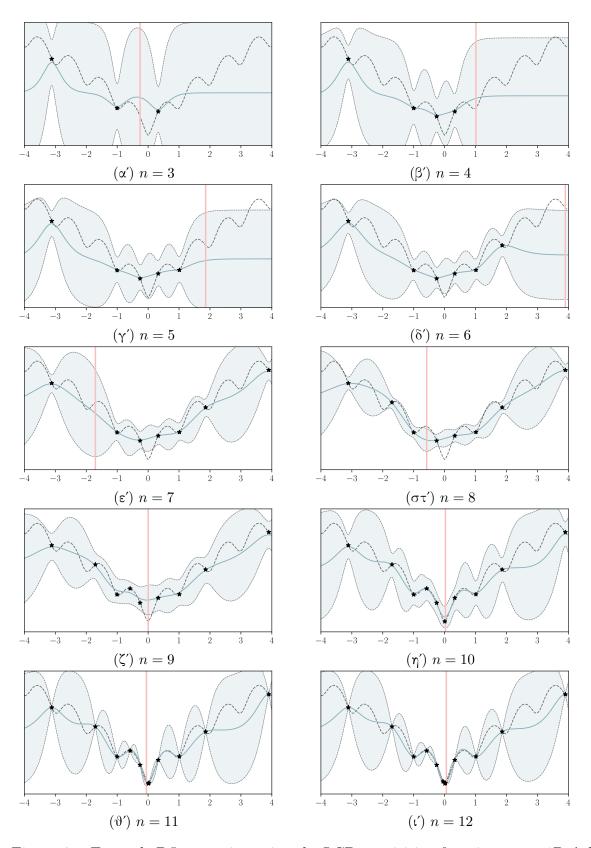

| 5.1  | A demonstration of the local based approach for minimizing $F(\mathbf{x}) =$                                                                                                                                              |     |

|      | $[f_1(\mathbf{x}), f_2(\mathbf{x})]$ in a $2D$ space                                                                                                                                                                      | 104 |

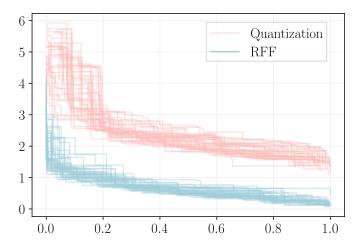

| 5.2  | Matèrn kernel approximation using RFF samples. The $x$ axes depict the                                                                                                                                                    |     |

|      | quantity $\tau = x - x'$                                                                                                                                                                                                  | 109 |

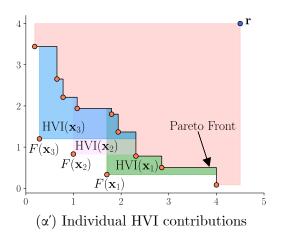

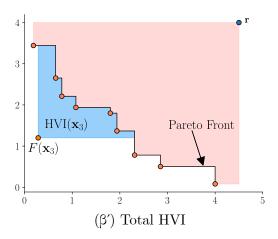

| 5.3  | Illustration of the Hypervolume and Hypervolume Improvement concepts.  Minimization is assumed here. The light-orange area is the dominated                                                                               |     |

|      | HV. Out of three candidates, $\mathbf{x}_3$ provides the largest HVI                                                                                                                                                      | 112 |

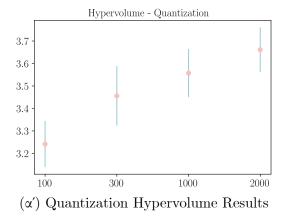

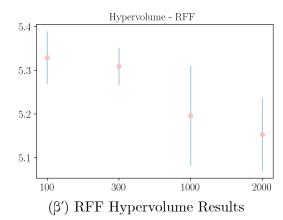

| 5.4  | Illustration of the mean and standard deviations of the resulting Hyper-                                                                                                                                                  |     |

|      | voolume metrics on the zdt1 experiment                                                                                                                                                                                    | 114 |

| 5.5  | The PFs from the zdt1 experiment. The RFF results in better trade-offs.                                                                                                                                                   | 115 |

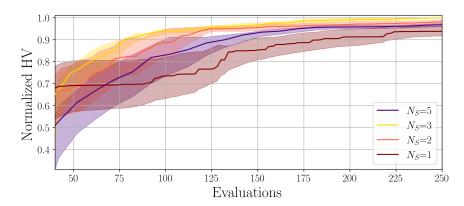

| 5.6  | The evolution of HV attained by the proposed approach using different                                                                                                                                                     |     |

|      | batch sizes. The values in the $y$ axis are normalized to the largest HV                                                                                                                                                  | 110 |

| E 7  | value attained                                                                                                                                                                                                            | 118 |

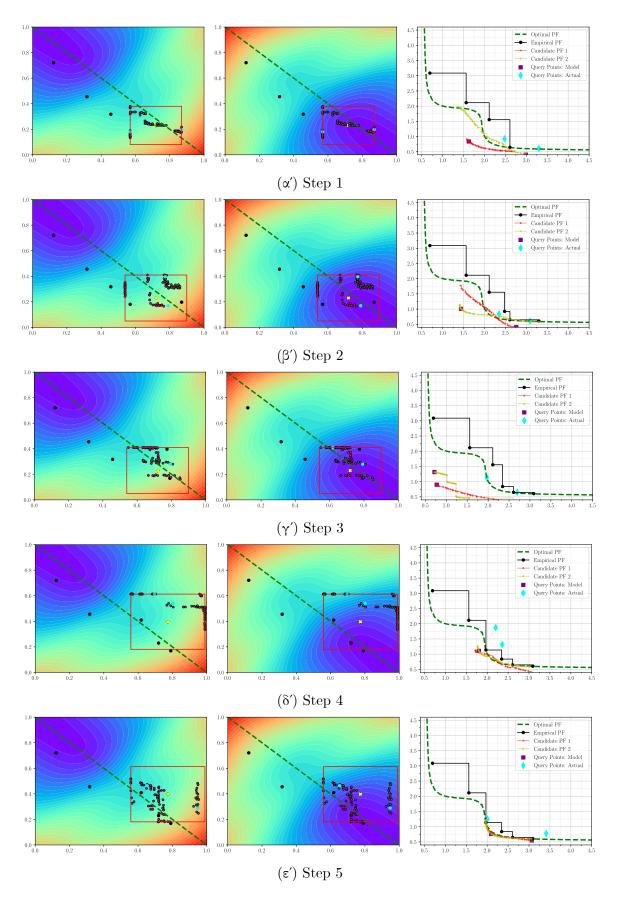

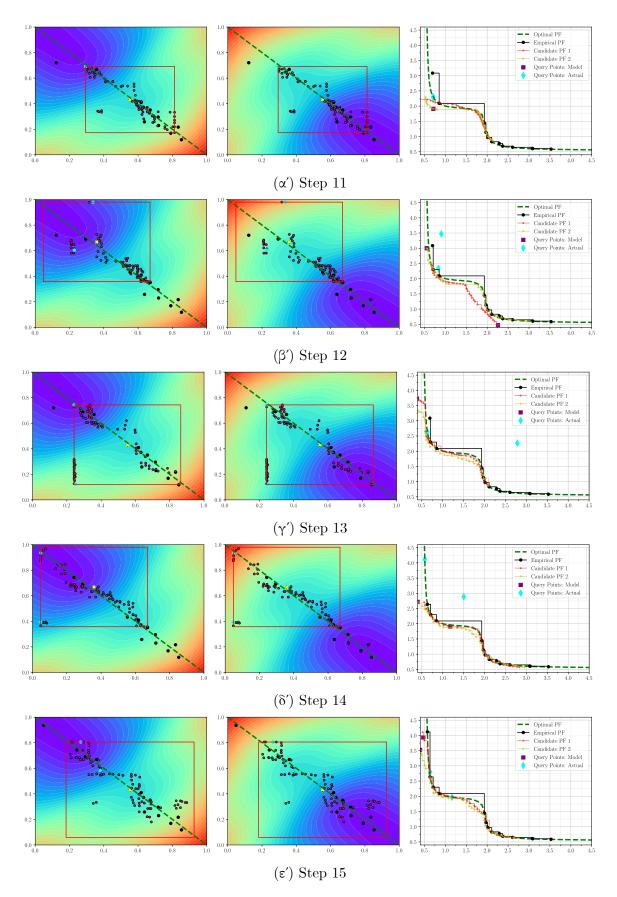

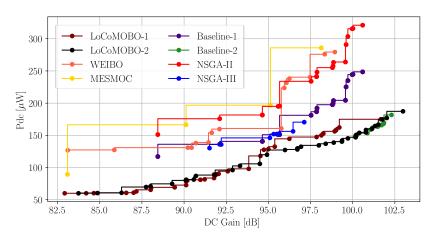

| 5.7  | Illustration of the operation of LoCoMOBO for optimizing the MOP of Eq. 5.28                                                                                                                                              | 120 |

| 5.8  | Illustration of the operation of LoCoMOBO for optimizing the MOP of                                                                                                                                                       | 120 |

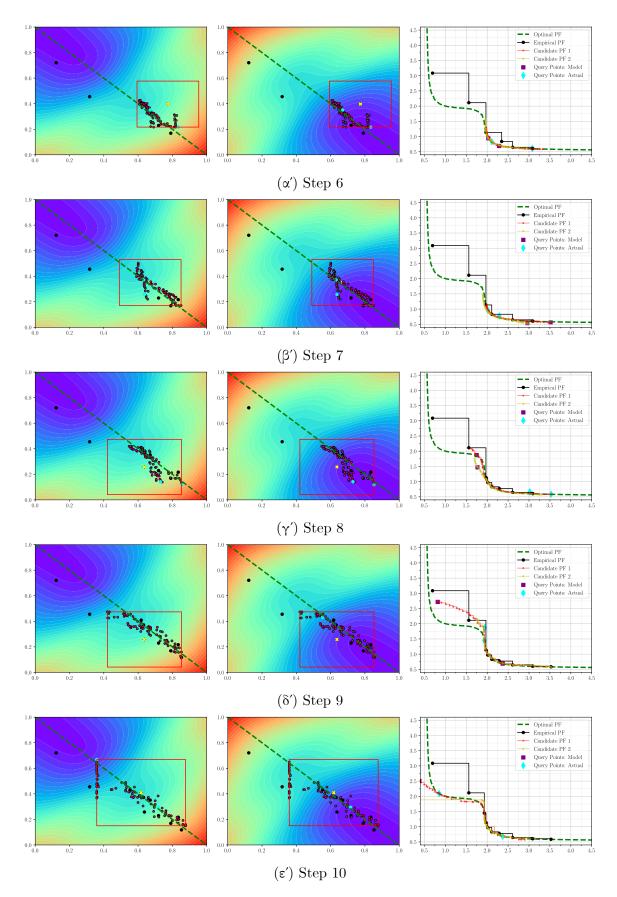

| 0.0  | Eq. 5.28                                                                                                                                                                                                                  | 121 |

| 5.9  | Illustration of the operation of LoCoMOBO for optimizing the MOP of                                                                                                                                                       | 141 |

| 0.0  | Eq. 5.28                                                                                                                                                                                                                  | 122 |

| 5.10 | Illustration of the operation of LoCoMOBO for optimizing the MOP of                                                                                                                                                       |     |

|      | Eq. 5.28                                                                                                                                                                                                                  | 123 |

| 5.11 | Three stage amplifier proposed in [106]                                                                                                                                                                                   | 124 |

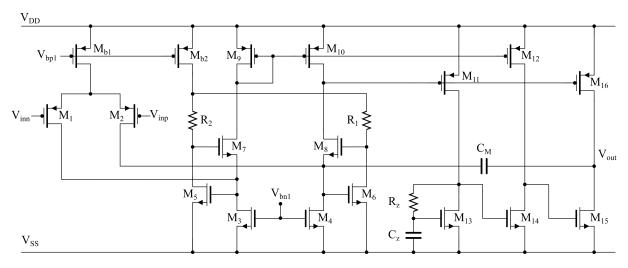

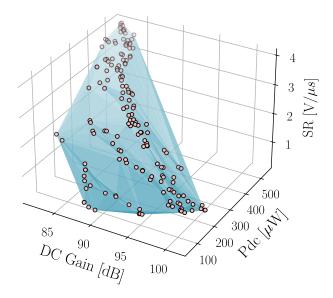

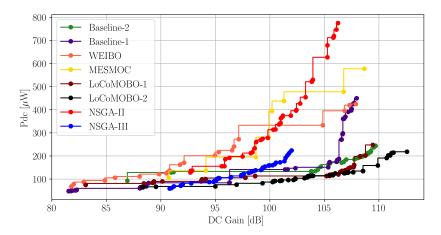

|      | Pareto Fronts for the Three Stage Amplifier. Bottom-right values result                                                                                                                                                   |     |

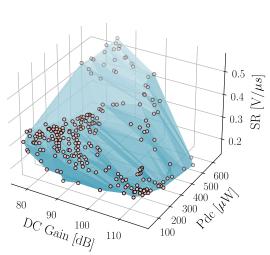

|      | in better DC Gain vs Pdc trade-off                                                                                                                                                                                        | 127 |

| 5.13 | A pareto front for the Three Stage Amplifier.                                                                                                                                                                             | 129 |

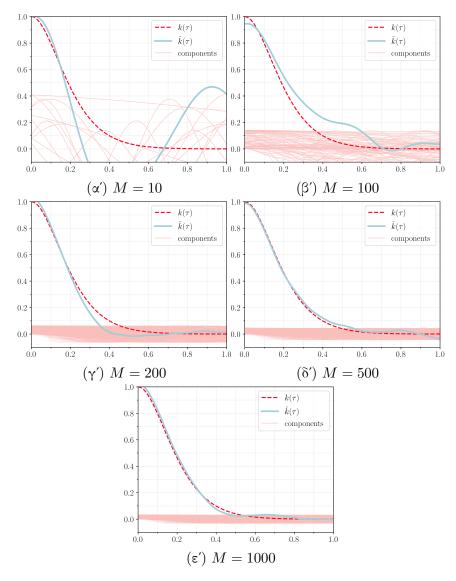

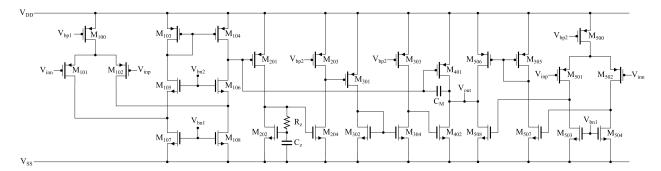

| 5.14 | Four stage amplifier proposed in [116]                                                                                                                                                                                    | 130 |

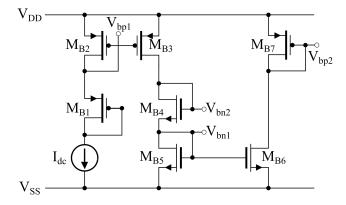

| 5.15 | Biasing sub-circuit for the considered four stage amplifier                                                                                                                                                               | 130 |

| 5.16 | Pareto Fronts for the Four Stage Amplifier. Bottom-right values result in                                                                                                                                                 |     |

|      | better DC Gain vs Pdc trade-off                                                                                                                                                                                           | 132 |

| 5.17 | A pareto front for the Four Stage Amplifier                                                                                                                                                                               | 135 |

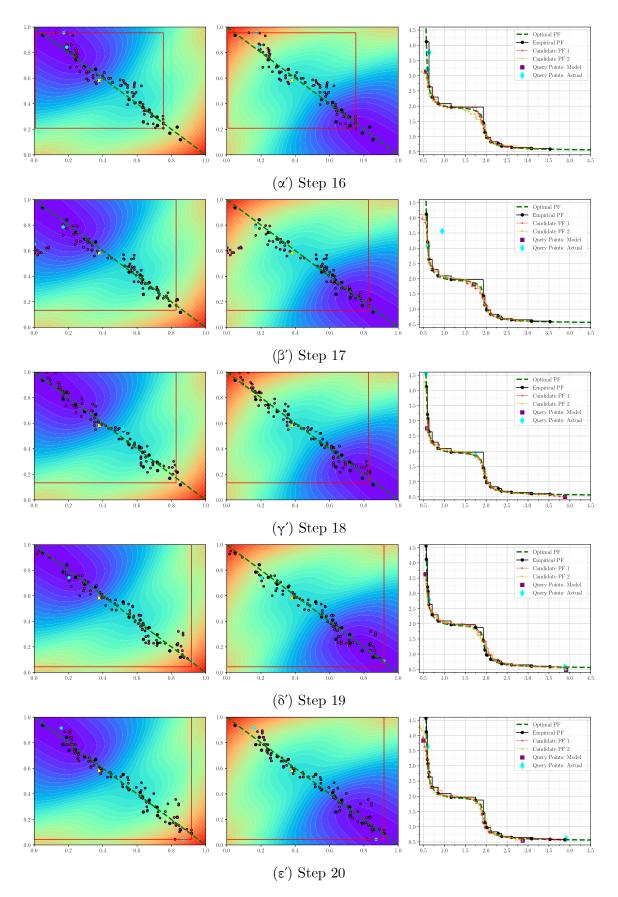

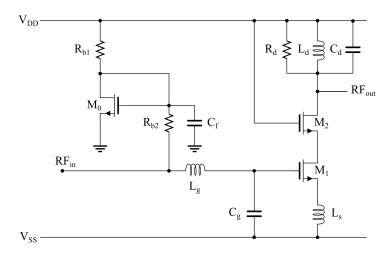

| 5.18 | Low Noise Amplifier examined in this subsection                                                                                                                                                                           | 135 |

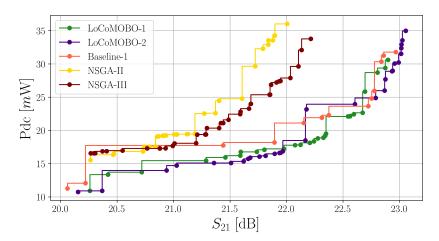

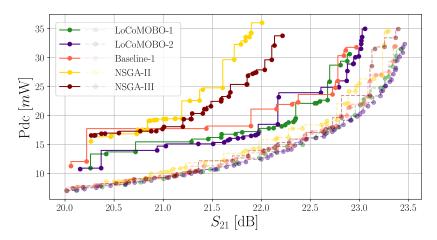

| 5.19 | Pareto Fronts for the Low Noise Amplifier. Bottom-right values result in                            |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | better $S_{21}$ vs Pdc trade-off                                                                    | 138 |

| 5.20 | A comparison between the Pareto Fronts derived accounting for PVT                                   |     |

|      | variations and only for nominal conditions. Nominal sizing results are                              |     |

|      | depicted using light dotted lines and PVT-aware results using solid lines.                          | 138 |

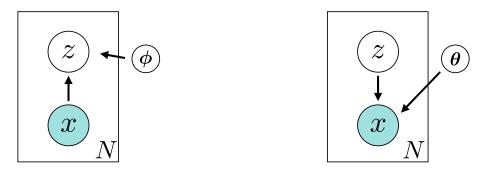

| 6.1  | Directed graphical models for (a) the approximate posterior $q_{\theta}(\mathbf{z} \mathbf{x})$ and |     |

|      | (b) the probabilistic decoder $p_{\phi}(\mathbf{x} \mathbf{z})$ . The coloured node indicates the   |     |

|      | observable random variable and the nodes outside the box are model                                  |     |

|      | parameters                                                                                          | 145 |

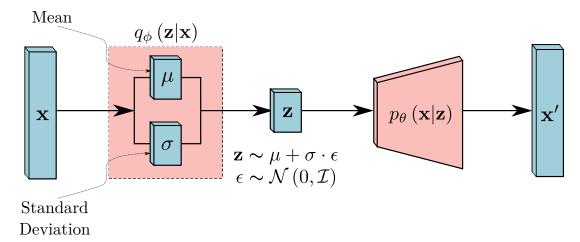

| 6.2  | An illustration of the VAE model, along with its constituent parts                                  | 147 |

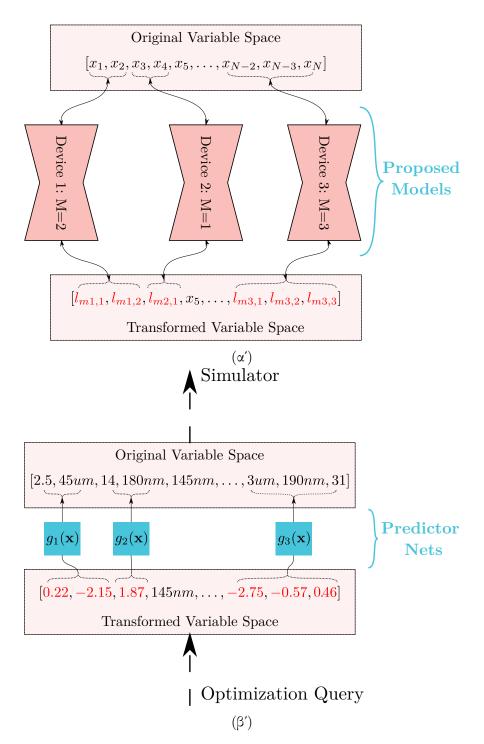

| 6.3  | The proposed device representation learning scheme within a sizing prob-                            |     |

|      | lem, where the latent variables are shown in red. a) The original variable                          |     |

|      | space of the sizing problem is changed into a transformed one, by map-                              |     |

|      | ping sets of variables that belong to devices into continuous latent ones.                          |     |

|      | b) During the optimization, a query from the optimization algorithm is                              |     |

|      | transformed back to the original variable space using the predictor net-                            |     |

|      | works, prior to simulation                                                                          | 149 |

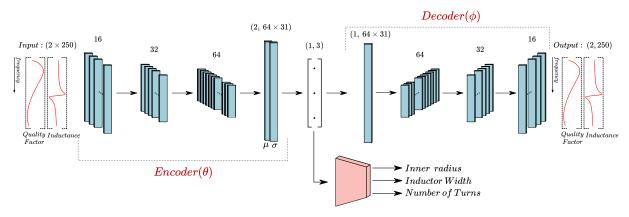

| 6.4  | A depiction of the proposed architecture. 1D vectors of inductors' Quality                          |     |

|      | Factor and Inductance frequency behavior are inputs to the 1D convolu-                              |     |

|      | tional filters of the architecture. The filter sizes are shown as well. The                         |     |

|      | predictor FCNN gets as input the latent representation of the inductor's                            |     |

|      | frequency characteristics and yields its geometric sizes                                            | 152 |

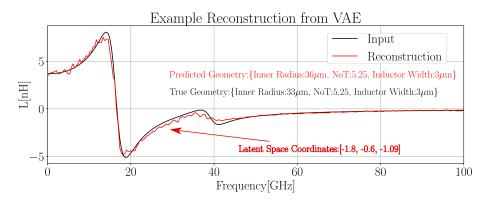

| 6.5  | A reconstruction of inductor's inductance across the frequency range of interest.                   | 154 |

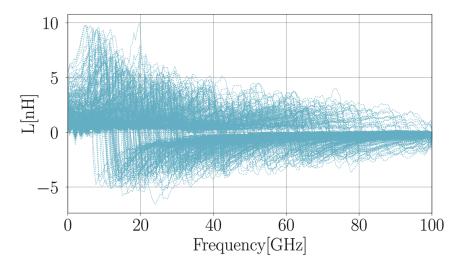

| 6.6  | 500 samples of inductance curves sampled from the generative model. $$ .                            | 154 |

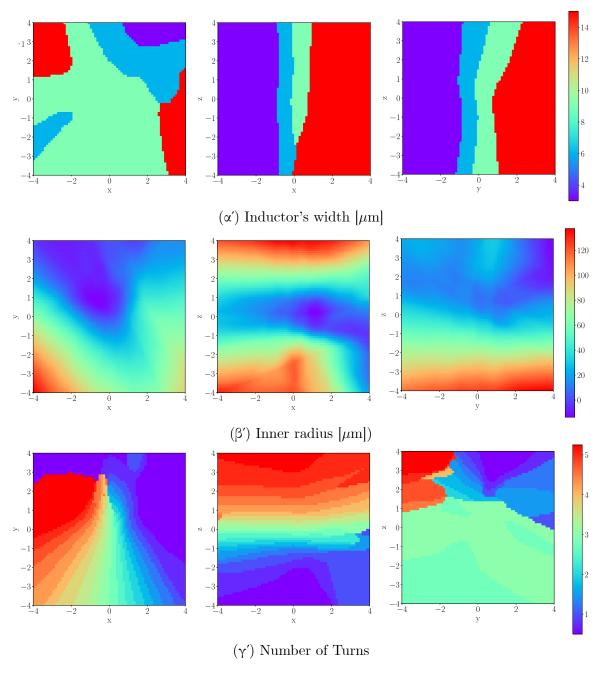

| 6.7  | Slices of the 3D latent space across the xy, yz and xz planes. The three                            |     |

|      | geometric variables for the spiral inductors are shown                                              | 155 |

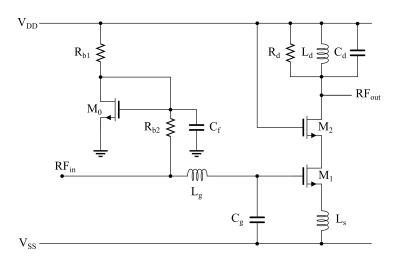

| 6.8  | The Inductively Degenrated LNA considered as a case study                                           | 157 |

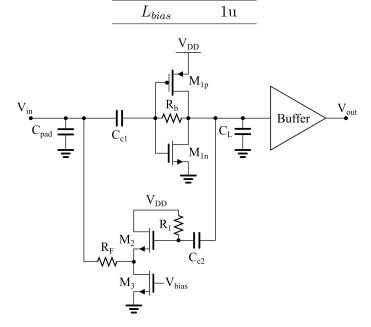

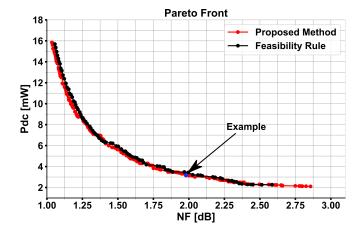

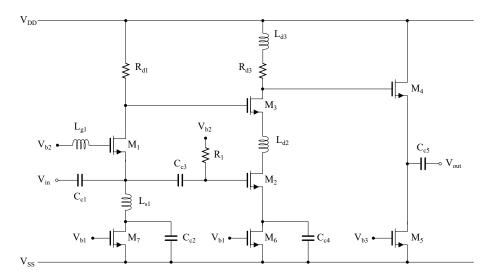

| 6.10 | The wideband, noise canceling LNA [128] considered in this subsection.                              | 160 |

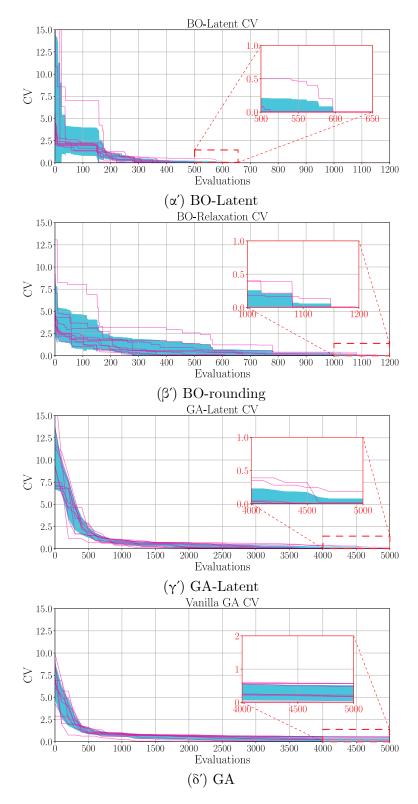

| 6.9  | The LNA's CV for the discussed formulations. The blue are indicates the                             |     |

|      | confidence region of $\pm$ std, while the purple lines are the curves of each                       |     |

|      | repetition                                                                                          | 161 |

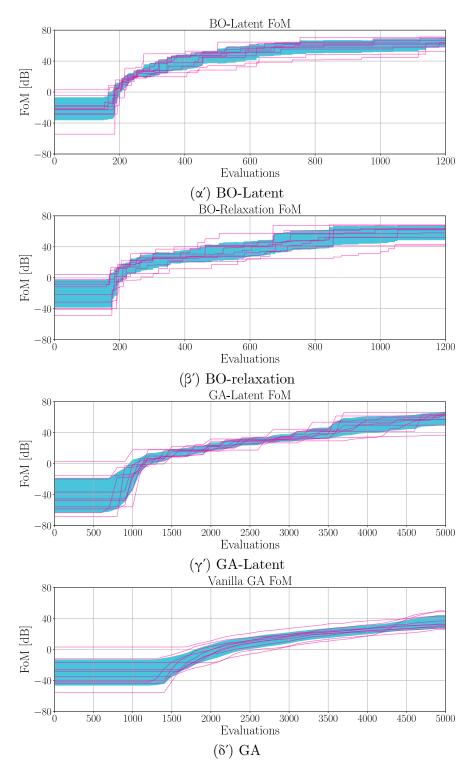

| 6.11 | The evolution of the LNA's FoM during the automatic sizing, using the                               |     |

|      | four discussed formulations. The blue are indicates the confidence region                           |     |

|      | of $\pm$ std, while the purple lines are the curves of each repetition                              | 165 |

## List of Tables

| 3.1  | Evolution and Problem Solving Equivalence                   | 57  |

|------|-------------------------------------------------------------|-----|

| 3.2  | VCOs variable ranges                                        | 67  |

| 3.3  | NCM Specifications                                          | 73  |

| 3.4  | NCM Variable Ranges                                         | 74  |

| 3.5  | NCM Example Solution                                        | 75  |

| 3.6  | Wideband LNA Specifications                                 | 75  |

| 3.7  | Wideband LNA Variable Ranges                                | 76  |

| 3.8  | Wideband LNA Example Solution                               | 77  |

| 4.1  | GP Training and sampling runtimes for Rosenbrock Function   | 94  |

| 4.2  | Three Stage Amplifier Specifications                        | 96  |

| 4.3  | Optimization Results for the Three Stage Amplifier          | 97  |

| 4.4  | High Linearity LNA Specifications                           | 98  |

| 4.5  | Optimization Results for the High Linearity LNA             | 98  |

| 5.1  | HV Results (mean $\pm$ std) on Benchmark Functions          | 117 |

| 5.2  | Runtime Comparison (s)                                      | 117 |

| 5.3  | Specifications for Three Stage Amplifier - Two Objectives   | 125 |

| 5.4  | Three Stage Amplifier HV Results - Two Objectives           | 126 |

| 5.5  | Three Stage Amplifier Cover Matrix - Two Objectives         | 127 |

| 5.6  | Specifications for Three Stage Amplifier - Three Objectives | 128 |

| 5.7  | Three Stage Amplifier HV Results - Three Objectives         | 128 |

| 5.8  | Three Stage Amplifier Cover Matrix - Three Objectives       | 129 |

| 5.9  | Specifications for Four Stage Amplifier - Two Objectives    | 131 |

| 5.10 | Four Stage Amplifier HV Results - Two Objectives            | 131 |

| 5.11 | Four Stage Amplifier Cover Matrix - Two Objectives          | 133 |

| 5.12 | Specifications for Four Stage Amplifier - Three Objectives  | 133 |

| 5.13 | Four Stage Amplifier HV Results - Three Objectives          | 134 |

| 5.14 | Four Stage Amplifier Cover Matrix - Three Objectives        | 134 |

| 5.15 | Specifications for Low Noise Amplifier                      | 136 |

| 5.16 | Low Noise Amplifier HV results                              | 137 |

| 5 17 | Low Noice Amplifier Cover Matrix                            | 127 |

| 32 | List of Tables |

|----|----------------|

|    |                |

| 6.1 | LNA Variable Ranges          | 158 |

|-----|------------------------------|-----|

| 6.2 | LNA Sizing Results           | 159 |

| 6.3 | Wideband LNA Variable Ranges | 163 |

| 6.4 | Wideband LNA Sizing Results  | 164 |

# List of Algorithms

| 1 | BO Algorithm                              |

|---|-------------------------------------------|

| 2 | Inducing Point Initial Location Selection |

| 3 | LoCoMOBO Acquisition Function             |

| 4 | LoCoMOBO Algorithm                        |

# Abbreviations

AE Autoencoder

ANN Artificial Neural Network

API Application Process Interface

BBMM BlackBox Matrix-Matrix Inference

BO Bayesian Optimization

CIM Compute-in-Memory

CMA Covariance Matric Adaptation

CV Constraint Violation

DE Differential Evolution

EA Evolutionary Algorithm

EC Evolutionary Computation

EDA Electronic Design Automation

EI Expected Improvement

EIC Expected Improvement with Constraints

ELBO Evidence Lower Bound

EM Expectation Maximization

FCNN Fully Connected Neural Network

FoM Figure of Merit

GA Genetic Algorithm

GP Gaussian Process

HLS High Level Synthesis

HV Hypervolume

HVI Hypervolume Improvement

IC Integrated Circuit

LCB Lower Confidence Bound LNA Low Noise Amplifier

LOVE Lanczos Variance Estimates

MC Monte Carlo

ML Machine Learning

MO Multi Objective

MOP Multi-Objective Optimization Problem

MSE Mean Squared Error NCM Nested Current Mirror

NSGA Non-dominated Sorting Genetic Algorithm

PCA Principal Component Analysis

PDK Process Development Kit

PES Predictive Entropy Search

PF Pareto Front

PI Probability of Imporvement

PS Pareto Set

PVT Process, Voltage, Temperature

RFRadio Frequency Rectified Linear Unit ReLU RFF Random Fourier Features RTLRegister Level Transfer Stochastic Gradient Descent SGDSVMSupport Vector Machine TSThompson Sampling VAE Variational Autoencoder VCO Voltage Controlled Oscillator

VLSI Vaery Very Large Scale Integration

# Chapter 1

# Introduction

Since the fabrication of the first integrated circuit in the 1960s [1], the semiconductor industry has seen tremendous advances and has effectively altered the way people interact and behave in their everyday lives. By providing the ability to integrate logic circuits in small pieces of semiconductors, it became the enabling factor for modern computing systems which dominate our world.

The driving force for the semiconductor's advancements has been the continuous miniaturization of integrated circuits; device sizes are constantly being reduced, effectively leading to faster, less power-hungry and more compact Integrated Circuits (ICs). Besides these rather obvious benefits, device miniaturization has been the key factor for the flourishing of the semiconductor market. While moving to newer, smaller devices for manufacturing requires more sophisticated manufacturing processes that in turn raise the cost for IC development, the ability to embed multiple logic functions in the same chip area not only evens out the cost but produces further financial gains. Besides this 'more functionality for the same price' [2] benefit, miniaturizing devices in chips has lead to more reliable systems, by reducing the number of solder points and dispensing with many discrete devices.

There are two types of circuitry embedded in an IC design nowadays; analog circuits and digital ones. Digital circuits operate on discrete-valued signals, which are most of the times binary. In this case, voltage signals can be interpreted as having one of two distinct values, a logic low '0' and a logic high '1'. To distinguish between these two values, all nodes should converge to a voltage value that belongs in the range of logic low or logic high. On the other hand, analog circuitry operates on continuous valued signals. Analog circuits' role in ICs is mainly to implement an interface between the digital domain and the external 'real-world', as well as to perform signal processing tasks. With technologies such as Complementary Metal-Oxide Semiconductor (CMOS) and BiCMOS [3], which enable the implementation of both digital and analog functionalities on the same chip, modern ICs often combine analog and digital operations. The idea behind the combination of both domains in the same IC stems from the need to further miniaturize electronics systems, as described previously.

To further leverage the capabilities of CMOS technologies, the semiconductor industry has seen a trend to integrate complete systems in a single chip. These Systems-on-

38 Introduction

a-Chip (SoCs) include of course analog, digital and even radio-frequency (RF) circuit blocks and have been in the forefront of the modern electronics market for more than a decade. In this context, digital circuitry has replaced analog blocks in operations such as signal processing, in order to reduce the non-ideal effects rising from the operation of transistors in the continuous regime. However, analog circuit will always be indispensable to perform some typical functions such as sensor interfaces, voltage references, analog-to-digital converters, etc.

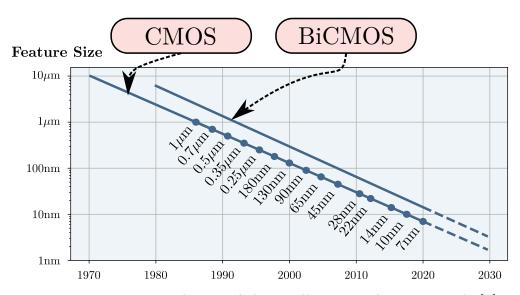

Manufacturing these integrated circuits is tedious undertaking and requires well studied, established procedures. These are often referred to as technology or process nodes and are characterized by the minimum size of a device that can be manufactured using them. Typically, the smallest length of a unipolar transistor is used for this purpose. Transistor miniaturization does involve arbitrary scaling factors. Rather, newer technology nodes are scaled by a factor of  $1/\sqrt{2}$  in comparison to their predecessors. This transistor shrinking has been approximately predicted by Gordon Moore, whose famous heuristic stated the number of devices in ICs would double every two years [4]. In fact, by observing the actual shrinking history of the semiconductor industry, shown in Fig. 1.1, *Moore's Law* seems to be an accurate prediction about the state of the semiconductor manufacturing process.

Figure 1.1: Historic evolution of the smallest manufacturing node [2].

#### 1.1 Motivation

The economic and social impact of the device miniaturization described by Moore's Law is undeniable. Individuals harness the benefits of a interconnected world, with Motivation 39

computational devices being the enabling factor, and semiconductor investors claim considerable financial gains. However, the design of ICs in miniaturized technologies is becoming increasingly difficult, with designer's productivity constantly diminishing.

Miniaturization, however, has had more impact on the work of analog designers, compared to digital ones. In practice, although digital circuitry dominates the area of modern SoCs, analog blocks tend to be the design bottleneck, both in terms of time and budget. The fundamental reason behind this issue is the nature of the circuits themselves; digital circuitry that operates on signals with two levels and large tolerance levels are more robust to higher-order effects [5], compared to analog designs that must take into account the physics of each fabrication process and which requires expert handcraft skills.

Besides the aforementioned fundamental difference, analog design proves more cumbersome than digital since its design space is virtually infinite. In fact, there is a large variety of analog circuit topologies that may have the same functionalities and the choice of which one to design is a complex decision that depends on the exact application. In addition, the sizing of individual devices involves selecting values from a continuous range and the resulting performance metrics, which are closely correlated to the device sizes, are much more complicated both to reason with and to determine a beneficial comprise among. For instance, typical Operational Amplifiers have up to ten continuous-valued specification metrics [2], whereas digital standard cells have only two, timing and power. A further factor that makes analog design harder is hierarchy. Digital logic has established means of abstraction, meaning that low-level logic can be accurately represented by behavioral models, which is not the case of analog circuits. In fact, low-level properties such as voltages, currents and impedances must all be taken into account when designing an relatively large analog system. These depend highly on the manufacturing process that will be eventually used, thus preventing the reuse of existing designs in new technology nodes. Therefore, analog circuit technology node retargeting may require considerable man-hours, even though the core functionality remains the same.

Layout-induced effects, such as parasitics, are more prominent to newer technology nodes and must be taken into account when designing analog circuits. In addition, designing using newer technology nodes requires the evaluation of each design's yield, which is affected by process, temperature and voltage variations. In the case of large systems that implement both analog and digital functionalities, the analog design is even more difficult since it must take into account system-level interactions, like crosstalk effects. All these render the analog design an iterative procedure, where the steps of topology selections, sizing, layout design and verification take place in turns. In contrast, digital design has effectively become an 'one-pass' procedure, where once the logic is

40 Introduction

implemented using a register-transfer level (RTL) representation and some design scripts are configured, the whole design can be implemented automatically. This means that a different variation of the design can occur by only providing an updated RTL description.

The automation of digital design is achieved by leveraging dedicated software tools. These *Electronic Design Automation* (EDA) tools were introduced in the 1980s to help designers cope with the exponential growth of device density and relieve them from the manual design. Nowadays, EDA tools provide digital designers the ability to define logic circuits in high-level abstraction using High-Level Synthesis (HLS) and to focus on the actual design by performing repetitive tasks in a structured, formalized manner. By doing so, the productivity of designers, measured in devices per IC and man-years for design has increased exponentially over the decades. In fact, recent chips that hold tens of billions of transistors [2, 6] would not be possible without the use of custom EDA-based design flows.

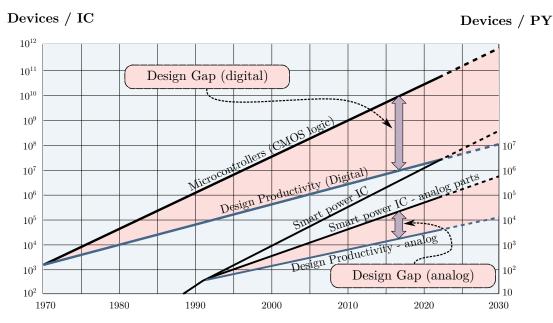

The case for analog EDA software, however, is not the same. As stated before, an analog circuit's performance is affected by a number of interleaved factors, ranging from manufacturing process properties, to topology selection and physical design. This complex interaction between different levels of abstraction in analog design does not favour formalized automation procedures. Manual analog design, therefore, has traditionally been the only choice to implement analog functionalities. Designers make use of standalone tools like circuit simulators, layout and verification tools as well as some software design suites that combine some basic functionalities. However, this kind of design flow fails to meet the requirements for modern, complex systems, since it does not allow neither for first-time-right designs nor for meeting time-to-market-constraints in general. A graphical illustration of this analog design gap is shown in Fig. 1.2, where the black line denotes the increase in transistor density in analog blocks over the years and the blue line depicts the designer's productivity, as defined previously. In fact, analog design has become the bottleneck in system design; even though analog blocks take up only 20% of the total area of a modern SoC [7], they require more effort and iterations to design.

Motivation 41

Figure 1.2: Graphical illustration of the analog design gap [2].

Despite the fact that analog design is cumbersome, it is also crucial for next-generation computing systems. Based on the 2020 International Roadmap for devices and systems [8], the *More-than-Moore* initiative aims to develop techniques for the increased integration of even more non-digital functionalities into the future SoCs. By incorporating sensory blocks, power management and RF communications on the chips, analog IC design will become even more important in the foreseeable future. In addition, two recent trends in computing require substantial effort in analog circuitry: the low-power Internet-of-Things (IoT) applications, requiring power-gated designs, sensor interfaces and subthreshold operation and the Compute-in-Memory (CIM) one [8]. CIM targets Artificial-Intelligence applications by implementing dot product and other non-linear functionalities by analog circuitry to reduce power-costs and increase area efficiency. CIM falls under the umbrella of the Analog-AI trend in unconventional computing design.

Given the aforementioned productivity gap in analog circuit design, and taking into account that analog circuits will be in greater demand in the near future, it is reasonable to conclude that steps must be taken to facilitate the job of analog designers. A step towards this can be the development of new, dedicated EDA tools that assist in analog design by providing insights on circuits and automating parts of the overall design procedure.

42 Introduction

#### 1.2 Thesis Contributions

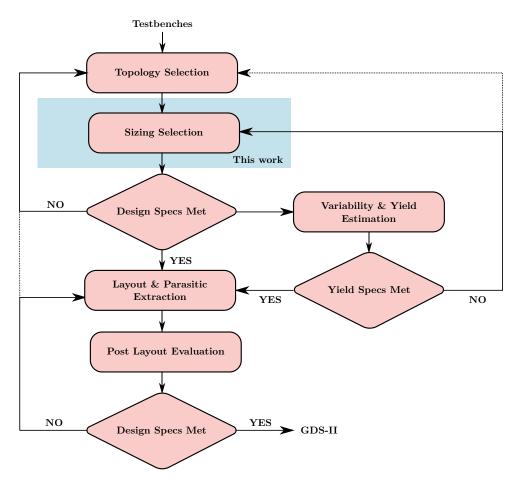

Figure 1.3: A sample analog IC design flow. This work focuses on device sizing selection.

An illustrative example of a typical analog IC design flow in shown in Fig. 1.3. It is shown that there are multiple steps and conditions that a design needs to fulfill in order to proceed to tape-out. In this thesis, we try to facilitate the whole procedure by attacking the problem of device *sizing selection*, which is highlighted in Fig. 1.3. This problem involves determining the sizes of each individual device for a particular topology, given a set of predefined performance metrics constraints. In particular, there are a number of research questions that we address:

- With circuits that have completely different applications, topologies and performance specifications, is there a universal manner in which their device sizes can be inferred in an structured, (semi)-automatic manner?