### National Technical University of Athens

School of Electrical and Computer Engineering Division of Communication, Electronic and Information Engineering

# **Stochastic Computing Architectures for Information Processing Systems**

by

#### **Nikolaos Temenos**

Supervisor Paul-Peter Sotiriadis, Professor, NTUA

A dissertation submitted to the Department of Electrical and Computer Engineering in partial fulfillment of the requirements for the degree of Doctor of Philosophy

### Εθνικό Μετσόβιο Πολυτεχνείο

Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών Τομέας Επικοινωνιών, Ηλεκτρονικής & Συστημάτων Πληροφορικής

# **Stochastic Computing Architectures for Information Processing Systems**

Διδακτορική Διατριβή

Νικόλαος Τέμενος

Υποβλήθηκε στο Τμήμα Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών σε μερική εκπλήρωση των απαιτήσεων για την απόκτηση διδακτορικού διπλώματος

#### National Technical University of Athens

School of Electrical and Computer Engineering Division of Communication, Electronic and Information Engineering

## **Stochastic Computing Architectures for Information Processing Systems**

#### PhD Dissertation

Nikolaos Temenos

**Advisory Committee:**

Professor, NTUA

Paul - Peter Sotiriadis Athanasios D. Panagopoulos Professor, NTUA

Kiamal Pekmestzi Professor Emeritus, NTUA

Approved by the seven-member examination committee on 13/12/2022.

Paul - Peter Sotiriadis

Athanasios D. Panagopoulos

Professor, NTUA

Professor, NTUA

Kiamal Pekmestzi

Professor Emeritus, NTUA

Theodora Varvarigou

Professor

Panayiotis Psarrakos

Professor

Anastasios Doulamis

Associate Professor

Nikolaos Doularnis

Professor

Athens, December 2022

The research work was supported by the Hellenic Foundation for Research and Innovation (HFRI) under the HFRI PhD Fellowship grant (Fellowship Number:1216).

•••••

Νικόλαος Τέμενος, Διδάκτωρ Ε.Μ.Π.

Copyright © Νικόλαος Τέμενος, 2022

Με επιφύλαξη παντός δικαιώματος. All rights reserved.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς το συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν το συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

## **Abstract**

Arithmetic operations on stochastic sequences is the basis of the unconventional computational approach known as Stochastic Computing (SC). Deviating from the standard binary arithmetic, SC encodes and processes the value of binary numbers in the form of stochastic sequences, making arithmetic operations and highly-complex functions realizable using a few simple standard logic gates and memory elements, having inherent natural robustness in soft-errors. SC's properties and advantages have been exploited in a plethora of fields characterized by massive parallelism requirements like Neural Networks and Image Processing. Beyond its strong points, SC introduces an accuracy-latency trade-off impacting the energy efficiency. Therefore, achieving low latency along with increased computational accuracy is the primary design goal is SC systems.

This dissertation presents novel SC architectures realizing essential arithmetic operations and non-linear functions, as well as realistic Neural Networks and Image Processing applications based on them.

In the first part of the dissertation, the operating principles of the architectures are introduced and their behavior is modeled based on Stochastic Finite-State Machines (SFSM) and analyzed using Markov Chains (MC). This leads to a deeper understanding of their stochastic dynamics and the verification of their proper operation. The MC modeling is further extended to a general methodology enabling the analytical derivation of the SFSMs' first and second moment statistical properties. The methodology is accompanied by overflow/underflow MC modeling, allowing to balance the accuracy-latency trade-off according to performance requirements, and to set the guidelines for the selection of the register's size.

In the second part of the dissertation, the proposed architectures are compared to existing ones, in the SC literature, in computational accuracy and hardware resources, including area, power and energy consumption as well as in terms of their advantages in the overall design flow. The efficacy of the architectures is demonstrated by using them as building blocks in the realization of several Digital Signal Processing (DSP) operations, including convolution, noise reduction and image down-sampling filters as well as Neural Networks. Finally, the results of the introduced architectures' performance in computational accuracy and hardware resources are compared to those achieved using standard binary computing methods highlighting the advantages of the first ones.

Keywords: Stochastic Computing, Stochastic FSM, Markov Chain Modeling, Digital Circuits

6 Abstract

# Περίληψη

Οι αριθμητικές πράξεις με στοχαστικές ακολουθίες είναι η βάση της μη συμβατικής τεχνικής που είναι γνωστή ως Στοχαστικός Υπολογισμός (ΣΥ). Αποκλίνοντας από την τυπική δυαδική αριθμητική, ο ΣΥ κωδικοποιεί και επεξεργάζεται την τιμή των δυαδικών αριθμών με τη μορφή στοχαστικών ακολουθιών, καθιστώντας δυνατή την πραγματοποίηση αριθμητικών πράξεων και εξαιρετικά πολύπλοκων συναρτήσεων με τη χρήση λίγων τυπικών λογικών πυλών και στοιχείων μνήμης. Μαζί με την φυσική ευρωστία του ΣΥ σε σφάλματα, οι ιδιότητες και τα πλεονεκτήματά του έχουν αξιοποιηθεί σε πληθώρα πεδίων με ανάγκες μαζικού παραλληλισμού και μικρή ανοχή σε σφάλματα, συμπεριλαμβανομένων των νευρωνικών δικτύων και της επεξεργασίας εικόνας μεταξύ πολλών άλλων. Πέρα από τα ισχυρά του σημεία, ο ΣΥ εισάγει ένα συμβιβασμό ακρίβειας-καθυστέρησης που επηρεάζει την ενεργειακή απόδοση και, ως εκ τούτου, για να αξιοποιηθεί με τον καλύτερο δυνατό τρόπο, η επίτευξη χαμηλής καθυστέρησης σε συνδυασμό με αυξημένη υπολογιστική ακρίβεια είναι πρωταρχικό μέλημα.

Στην παρούσα διατριβή παρουσιάζονται νέες αρχιτεκτονικές που υλοποιούν βασικές αριθμητικές πράξεις και μη γραμμικές συναρτήσεις σε ΣΥ. Οι εσωτερικοί καταχωρητές που χρησιμοποιούν καθιστούν την επεξεργασία της ακολουθίας εισόδου τους αιτιοκρατική, βελτιώνοντας έτσι το συμβιβασμό ακρίβειας-καθυστέρησης του ΣΥ. Για να αναδειχθούν οι ιδιότητες και η αρχή λειτουργίας των αρχιτεκτονικών, αναλύονται διεξοδικά με τη χρήση στοχαστικών μηχανών πεπερασμένης κατάστασης (ΣΜΠΚ) και μοντελοποιούνται με τη χρήση αλυσίδων Markov (ΑΜ).

Στο πρώτο μέρος της διατριβής, η αρχή λειτουργίας των αρχιτεκτονικών αναλύεται με τη χρήση ΣΜΠΚ και μοντελοποιείται με τη χρήση ΑΜ, η οποία επιτρέπει την καλύτερη κατανόηση της μακροπρόθεσμης στοχαστικής δυναμικής τους και την επαλήθευση της ορθής λειτουργίας τους. Η μοντελοποίηση της ΑΜ επεκτείνεται περαιτέρω σε μια γενική μεθοδολογία που επιτρέπει την αναλυτική εξαγωγή των στατιστικών ιδιοτήτων της πρώτης και της δεύτερης ροπής των ΣΜΠΚ. Η μεθοδολογία συνοδεύεται από μοντελοποίηση ΑΜ υπερχείλισης/υποχείλισης, επιτρέποντας την εκτίμηση του αριθμού των καταστάσεων που μειώνουν τα σφάλματα ψηφίων που προέρχονται από την εμφάνιση υπερχείλισης/υποχείλισης, θέτοντας έτσι τις κατευθυντήριες γραμμές για την επιλογή του μεγέθους του καταχωρητή που χρησιμοποιούν.

Στο δεύτερο μέρος της διατριβής, οι αρχιτεκτονικές συγκρίνονται εκτενώς με τις υπάρχουσες στη βιβλιογραφία των ΣΥ όσον αφορά την υπολογιστική ακρίβεια και τους πόρους υλικού, συμπεριλαμβανομένου του χώρου που καταλαμβάνουν τα κυκλώματα, την κατανάλωση ισχύος και ενέργειας, καθώς και τα οφέλη που εισάγουν στη συνολική ροή σχεδίασης. Η αποτελεσματικότητα των αρχιτεκτονικών αναδεικνύεται με τη χρήση τους ως δομικά στοιχεία στην υλοποίηση διαφόρων επεξεργαστικών μονά-

Περίληψη

δων, που περιλαμβάνουν συνέλιξη, φίλτρα μείωσης θορύβου και υποδειγματοληψίας εικόνας, καθώς και νευρωνικά δίκτυα. Τα αποτελέσματα των επιδόσεων των αρχιτεκτονικών όσον αφορά την υπολογιστική ακρίβεια και τους πόρους υλικού συγκρίνονται με εκείνα που επιτυγχάνονται με τη χρήση τυπικών δυαδικών μεθόδων υπολογισμού, προβάλλοντας τα πλεονεκτήματά του ΣΥ ως πολλά υποσχόμενη εναλλακτική μορφή επεξεργασίας σημάτων.

**Λεξεις Κλειδια:** Στοχαστικός Υπολογισμός, Στοχαστικά Αυτόματα, Αλυσίδα Markov, Ψηφιακά Κυκλώματα

# Εκτεταμένη Περίληψη

Στην παρούσα διατριβή παρουσιάζονται καινοτόμες ψηφιακές αρχιτεκτονικές που υλοποιούν βασικές αριθμητικές πράξεις και μη γραμμικές συναρτήσεις στον στοχαστικό υπολογισμό (Stochastic Computing - SC). Η ανάλυσή τους γίνεται διεξοδικά με τη χρήση στοχαστικών μηχανών πεπερασμένων καταστάσεων (Stochastic Finite-State Machines - SFSMs), ενώ για την κατανόηση της στοχαστικής δυναμικής συμπεριφοράς τους, μοντελοποιούνται μέσω αλυσίδων Markov (Markov Chains - MC). Τα πλεονεκτήματα και η αποτελεσματικότητα τους, επιδεικνύονται με την αξιοποίησή τους στην υλοποίηση δομικών μονάδων ψηφιακής επεξεργασίας σήματος (Digital Signal Processing - DSP).

Ο στοχαστικός υπολογισμός ανήκει στην κατηγορία των μη συμβατικών μεθόδων υπολογισμού, καθώς κωδικοποιεί και επεξεργάζεται την τιμή δυαδικών αριθμών με τη μορφή στοχαστικών ακολουθιών του ενός ψηφίου (bit). Η σειριακή επεξεργασία σε επίπεδο ψηφίου, επιτρέπει την υλοποίηση θεμελιωδών αριθμητικών πράξεων με τη χρήση μεμονομένων λογικών πυλών (logic gates), ενώ ιδιαίτερα πολύπλοκες συναρτήσεις, όπως για παράδειγμα μη γραμμικές, υλοποιούνται απλά με τη χρήση μηχανών πεπερασμένων καταστάσεων. Επιπλέον, δεδομένης της πιθανοτικής φύσης του, ο στοχαστικός υπολογισμός είναι εγγενώς ανεκτικός σε σφάλματα (soft errors), που σημαίνει ότι η αντιστροφή μερικών ψηφίων δεν είναι επιζήμια για την πληροφορία του ίδιου του σήματος. Πέραν των πλεονεκτημάτων του, ο στοχαστικός υπολογισμός εισάγει μία αντιστάθμιση (trade-off) μεταξύ του μήκους των στοχαστικών ακολουθιών προς επεξεργασία και της ακρίβειας του χρονικού μέσου όρου του στοχαστικού αριθμού. Ως εκ τούτου, για να αξιοποιηθεί με τον καλύτερο δυνατό τρόπο, η επίτευξη χαμηλής καθυστέρησης (latency) σε συνδυασμό με αυξημένη υπολογιστική ακρίβεια αποτελεί πρωταρχικό μέλημα σχεδιασμού σε συστήματα βασισμένα στο στοχαστικό υπολογισμό, ώστε να αποφευχθεί η συνολική κατανάλωση ενέργειας.

Τα πλεονεκτήματα και οι ιδιότητες του στοχαστικού υπολογισμού, ευνοούν κατά κόρον εφαρμογές που η υλοποίησή τους και οι απαιτήσεις τους συνδυάζουν ταυτόχρονα ανάγκες για μαζικό παραλληλισμό, περιορισμό σε έκταση και ανοχή σε μικρές αποκλίσεις από τους ακριβείς υπολογισμούς. Οι εφαρμογές αυτές περιλαμβάνουν τα τεχνητά νευρωνικά δίκτυα εμπρόσθιας τροφοδότησης (Artificial Neural Networks - ANNs) με έμφαση στα πολυεπίπεδα perceptron (Multi-Layer Perceptrons - MLPs) και τα συνελικτικά νευρωνικά δίκτυα (Convolutional Neural Networks - CNN) στον τομέα της τεχνητής νοημοσύνης, τις μηχανές διανυσμάτων υποστήριξης (Support Vector Machines - SVMs) στον τομέα της μηχανικής μάθησης (Machine Learning - ML) και των φίλτρων χωρικής βελτίωσης συμπεριλαμβανομένων των φίλτρων μείωσης θορύβου, διάμεσης τιμής, ενίσχυσης ευκρίνειας εικόνας και άλλων στον τομέα της ψηφιακής επεξεργασίας εικόνας (Digital Image Processing -DIP). Ωστόσο, ο στοχαστικός υπολογισμός δεν περιορίζεται μόνο στα ανωτέρω πεδία, καθώς έχει εφαρμοστεί με επιτυχία στο ελαστικό φιλτράρι-

σμα (soft filtering), που συμπεριλαμβάνει φίλτρα πεπερασμένης κρουστικής απόκρισης (Finite Impulse Response - FIR) και άπειρης κρουστικής απόκρισης (Infinite Impulse Response - IIR), στην κωδικοποίηση/αποκωδικοποίηση διόρθωσης σφαλμάτων (error correcting codes), στην επίλυση πολυωνύμων (polynomial solving) και σε άλλα.

Μια βασική λειτουργία που εκτελείται στους πυρήνες ψηφιακής επεξεργασίας σήματος σε όλες τις παραπάνω εφαρμογές, είναι αυτή του πολλαπλασιασμού και της πρόσθεσης (multiply-and-add). Στο στογαστικό υπολογισμό, η πράξη του πολλαπλασιασμού αποτελεί έναν από τους βασικότερους παράγοντες που τον καθιστούν ελκυστικό, καθώς υλοποιείται απλά με τη χρήση μίας πύλης AND ή XNOR, αναλόγως με την αναπαράσταση αριθμών που χρησιμοποιείται. Το κομμάτι της πρόσθεσης όμως, υλοποιείται τυπικά από έναν πολυπλέκτη (Multiplexer - MUX), ο οποίος απαιτεί μια επιπρόσθετη πηγή τυχαίων αριθμών για το σήμα επιλογής του, πέραν των δύο εισόδων του. Ωστόσο, η πηγή τυχαίων αριθμών αποτελεί από μόνη της ογκώδες δομικό κομμάτι, αφού σε σύγκριση με τις υπόλοιπες λογικές πύλες που χρησιμοποιούνται, καταλαμβάνει το μεγαλύτερο μέρος της επιφάνειας της σχεδίασης. Επιπλέον, η έξοδος του αθροιστή συνήθως κλιμακώνεται κατά το ήμισυ, που σημαίνει ότι για ένα δεδομένο μήκος ακολουθίας η ανάλυση μειώνεται στο μισό, ενώ η μείωση της ανάλυσης, εντείνεται περαιτέρω όταν υφίστανται αρκετοί κλιμακωτοί υπολογισμοί. Ως εκ τούτου, ο πολυπλέκτης είναι η λιγότερο ελκυστική επιλογή για άθροιση, αφού σε όλα τα παραπάνω προστίθεται και η αυζημένη κατανάλωση ενέργειας δεδομένης της ανάγκης για αύξηση της ανάλυσης της ακολουθίας εξόδου. Τα ίδια μειονεκτήματα παρουσιάζει και ο αφαιρέτης ο οποίος υλοποιείται με τη χρήση πολυπλέκτη, με τη μόνη διαφορά οτι περιορίζεται σε μόνο μία από τις δύο βασικές αναπαραστάσεις του στοχαστικού υπολογισμού.

Για την αντιμετώπιση των μειονεκτημάτων που εισάγει ο πολυπλέκτης, έγουν διερευνηθεί διάφοροι αθροιστές και αφαιρέτες, εστιάζοντας ταυτόχρονα στην υπολογιστική και σχεδιαστική αποδοτικότητα. Μία προσέγγιση βασισμένη στην αργή κλιμάκωσης που εισάγει ο πολυπλέκτης, αποφεύγει την επιπλέον πηγή τυχαίων αριθμών στο σήμα επιλογής, αντικαθιστόντας τη με ένα στοιχείο μνήμης T Flip-Flop, αυξάνοντας παράλληλα την ακρίβεια στους υπολογισμούς. Μια παρόμοια, κλιμακωτή προσέγγιση, επεκτείνει τη χρήση του ενός στοιχείου μνήμης Τ Flip-Flop σε παραπάνω, εφαρμόζοντας μία μηχανή πεπερασμένων καταστάσεων για να αυξήσει περαιτέρω την ακρίβειά του. Αναφορικά με τους μη-κλιμακωτούς αθροιστές, μία προσέγγιση βασίζεται στην αναπαράσταση ενός στοχαστικού αριθμού που φέρει την πληροφορία του σε δύο ακολουθίες, μία για το πρόσημό του και μία για την τάξη μέγεθους του. Αν και είναι μια πολλά υποσχόμενη προσέγγιση σε επίπεδο εφαρμογής, η κωδικοποίηση στοχαστικού αριθμού μέσω δύο ακολουθιών επιβάλλει περιορισμούς στη συνολική σχεδίαση, καθώς απαιτεί από τις υπόλοιπες πράξεις, π.χ. πολλαπλασιαστές, να ακολουθούν επίσης αυτή την αρχή λειτουργίας. Ομοίως με τον προηγούμενο αθροιστή, άλλη προσέγγιση κωδικοποιεί έναν στοχαστικό αριθμό χρησιμοποιώντας τον λόγο των λογικών μονάδων και μηδενικών μεταξύ των ακολουθιών εισόδου του. Ωστόσο, η αναπαράσταση αυτή είναι ασύμβατη με τις τυπικές αναπαραστάσεις που χρησιμοποιούνται στο στοχαστικό υπολογισμό, ενώ η παραγωγή δύο ακολουθιών για έναν μόνο στοχαστικό αριθμό, επηρεάζει τη συνολική αξιοποίηση των πόρων και του υλικού.

Όσον αφορά τους στοχαστικούς αφαιρέτες, μία προσέγγιση συσχετίζει τις ακολουθίες εισόδου. Αυτό, ωστόσο, απαιτεί προσοχή, καθώς ο στοχαστικός υπολογισμός είναι επιρρεπής σε σφάλματα που προκαλούνται από συσχετισμένες εισόδους. Επιπλέον, εάν η αφαίρεση είναι μια ενδιάμεση αριθμητική πράξη,

δηλαδή υφίσταται μεταξύ δύο άλλων υπολογισμών, η αναγέννηση συσχετισμένων εισόδων είναι απαραίτητη, αυξάνοντας την αξιοποίηση των πόρων και του υλικού. Μια άλλη προσέγγιση εφαρμόζει επιπλέον λογικές μονάδες για να βελτιώσει την ακρίβεια μιας πύλης XNOR η οποία προσεγγίζει την αφαίρεση, ανταλλάσσοντας πόρους υλικού και καθυστέρηση για ακρίβεια υπολογισμών, και τα δύο βασισμένα στον αριθμό των επιπλέον λογικών μονάδων που χρησιμοποιούνται.

Συνοψίζοντας από τα παραπάνω, οι περισσότερες προσεγγίσεις ανταλλάσσουν το χρόνο εκτέλεσης ή/και την επιφάνεια του υλικού για την ακρίβεια υπολογισμών. Επιπλέον, ορισμένες από αυτές εισάγουν περιορισμούς που μειώνουν την ευελιξία στο χώρο σχεδιασμού του στοχαστικού υπολογισμού. Με κίνητρο τα προαναφερθέντα, στην παρούσα εργασία προτείνονται αρχιτεκτονικές μη κλιμακωτών αθροιστών και αφαιρετών. Τα πλεονεκτήματα που προσφέρουν είναι πολυάριθμα: δεν απαιτούν καμία πηγή τυχαίων αριθμών, δεν κλιμακώνουν το αποτέλεσμα εξόδου, λειτουργούν με ανεξάρτητες και πανομοιότυπα κατανεμημένες ακολουθίες εισόδου, δηλαδή δεν απαιτούνται ειδικά συσχετισμένες είσοδοι, είναι συμβατές με τις τυπικές αναπαραστάσεις αριθμών του στοχαστικού υπολογισμού και επιτυγχάνουν υψηλή υπολογιστική ακρίβεια χρησιμοποιώντας μικρά μήκη ακολουθιών εισόδου.

Σε περιπτώσεις όπου χρειάζεται η πράξη του πολλαπλασιασμού και της πρόσθεσης να γίνει μαζικά, η χρήση μεμονομένων αθροιστών σε δομή δένδρου εισάγει προκλήσεις σε επίπεδο αύξησης υλικού και ταχύτητας σχεδίασης. Για να αντιμετωπιστούν αυτές, στον στοχαστικό υπολογισμό εξετάζεται ο συσσωρευτικός παράλληλος μετρητής (Accumulative Parallel Counter - APC), ο οποίος αθροίζει αιτιοκρατικά όλες τις ακολουθίες εισόδου, παράγοντας το αποτέλεσμα σε δυαδική μορφή. Ωστόσο, σε αλυσιδωτούς υπολογισμούς η δυαδικό έξοδος του APC εισάγει τις ακόλουθες προκλήσεις σχεδιασμού: 1) περιορίζει την εφαρμοσιμότητα των υφιστάμενων στοχαστικών μηχανών πεπερασμένων καταστάσεων που υλοποιούν ιδιαίτερα πολύπλοκες συναρτήσεις, συμπεριλαμβανομένων μη γραμμικών συναρτήσεων και 2) στην περίπτωση που απαιτούνται και άλλες αριθμητικές πράξεις, για παράδειγμα όταν οι πολλαπλασιασμοί ακολουθούν την έξοδο των στοχαστικών μηχανών πεπερασμένων καταστάσεων, η δυαδική έξοδος πρέπει να αναγεννηθεί ως στοχαστική ακολουθία προκειμένου να να χρησιμοποιηθούν λογικές πύλες.

Με κίνητρο τους ανωτέρω περιορισμούς του ΑΡC, η παρούσα εργασία εισάγει μια αρχιτεκτονική αθροιστή που χρησιμοποιεί έναν διαμορφωτή σίγμα-δέλτα πρώτης τάξης (SDM). Ο προτεινόμενος αθροιστής στοχαστικού υπολογισμού σίγμα-δέλτα (SCSD) αθροίζει τα ψηφία των ακολουθιών εισόδου σε ένα δίαυλο δεδομένων και στη συνέχεια χρησιμοποιεί ένα εσωτερικό σχήμα μετατροπής εύρους δεδομένων ώστε να εκμεταλλευτεί την ιδιότητα του Σ-Δ να μετατρέπει ένα σήμα υψηλής ανάλυσης σε σήμα του ενός ψηφίου. Προσφέρει τα ακόλουθα πλεονεκτήματα: 1) λειτουργεί με ανεξάρτητες εισόδους, 2) η πρόσθεση γίνεται αιτιοκρατικά χωρίς επιπρόσθετες πηγές τυχαίων αριθμών, 3) επιτυγχάνει γρήγορη σύγκλιση με μικρά μήκη ακολουθίας εισόδου, 4) επιτρέπει να γίνουν αποτελεσματικά αλυσιδωτές πράξεις με τα υπάρχοντα αριθμητικά κυκλώματα και 5) επιτρέπει τη χρήση οποιασδήποτε στοχαστικής μηχανής πεπερασμένων καταστάσεων διευρύνοντας έτσι τη σχεδίαση νευρωνικών δικτύων και μη στο χώρο σχεδίασης του στοχαστικού υπολογισμού.

Όσο αναφορά τις μη γραμμικές συναρτήσεις που χρησιμοποιούνται στον στοχαστικό υπολογισμό, μεταξύ αρκετών όπως της υπερβολικής εφαπτομένης, του γραμμικού κέρδους, την εκθετική, του μεγίστου και του ελαχίστου, οι τελευταίες δύο είναι οι πιο δημοφιλείς δεδομένης της χρήσης τους στο στρώμα μέγιστης συγκέντρωσης (max pooling layers) στα νευρωνικά δίκτυα και στα φίλτρα μείωσης θορύβου.

12 Εκτεταμένη Περίληψη

Μία πρώτη προσέγγιση για την υλοποίηση του μεγίστου και ελαχίστου, χρησιμοποιεί πολυπλέκτες και τη συνάρτηση υπερβολικής εφαπτομένης υλοποιημένης ως μηχανή πεπερασμένων καταστάσεων. Ωστόσο, ένας από τους δύο πολυπλέκτες χρησιμοποιεί μία επιπλέον γεννήτρια παραγωγής στοχαστικών ακολουθιών για το το σήμα επιλογής του πολυπλέκτη, αυξάνοντας έτσι τις απαιτήσεις του υλικού. Έχοντας ως βάση την προηγούμενη αρχή λειτουργίας, άλλη προσέγγιση αντικαθιστά τον μετατροπέα δυαδικού σε στοχαστικό με μία λογική πύλη ΧΟR για να μειώσει την επιβάρυνση υλικού, διατηρώντας την υπόλοιπη δομή επεξεργασίας. Μία παρόμοια προσέγγιση, αντικαθιστά τη μηχανή πεπερασμένων καταστάσεων με καταχωρητή μετατόπισης (shift register) για την αποθήκευση των λογικών μονάδων από τη μία εκ των δύο εισόδων του και το λιγότερο σημαντικό bit (Least-Significant Bit - LSB) παράγει λογική μονάδα μονο αν έχει κορεστεί μέχρι αυτό. Ένα βασικό μειονέκτημα όμως είναι το ακριβές μέγεθος του καταχωρητή μετατόπισης, το οποίο αν δεν επιλεγεί με σωστά, η υπολογιστική ακρίβεια της εξόδου μειώνεται δραματικά.

Παρακινούμενοι από τις σχεδιαστικές προκλήσεις των προηγούμενων μεθόδων σε συνδυασμό με την ανάγκη για υπολογισμούς με χαμηλή καθυστέρηση στο στοχαστικό υπολογισμό, στην παρούσα εργασία προτείνονται δύο διαφορετικές προσεγγίσεις για την υλοποίηση του μεγίστου/ελαχίστου. Σε αντίθεση με άλλες προσεγγίσεις, οι προτεινόμενες αρχιτεκτονικές χρησιμοποιούν έναν συσσωρευτή για την απευθείας αποθήκευση των προσημασμένων διαφορών των ψηφίων μεταξύ των δύο ακολουθιών εισόδου τους, χωρίς πρόσθετες πηγές παραγωγής τυχαίων αριθμών, καθιστώντας τη λειτουργία τους αιτιοκρατική. Αυτό έχει ως αποτέλεσμα τη μείωση της καθυστέρησης και ταυτόχρονα την επίτευξη υπολογισμών υψηλής ακρίβειας με τη χρήση μικρού μήκους ακολουθιών εισόδου.

Σχετικά με τη χρήση στοχαστικών μηχανών πεπερασμένης κατάστασης για την υλοποίηση μη γραμμικών συναρτήσεων, για να είναι εφικτή η προσέγγιση τους, θα πρέπει να ικανοποιούν ταυτόχρονα ορισμένες συνθήκες. Συγκεκριμένα, θα πρέπει να αποτελούνται από έναν πεπερασμένο αριθμό καταστάσεων με την πρώτη και την τελευταία να είναι κορεσμένες, δηλαδή να μην μπορούν να ξεπεραστούν, θα πρέπει οι μεταβάσεις εντός των καταστάσεών τους να οδηγούνται από ακολουθίες εισόδου, με στοχαστικές ιδιότητες και πεπερασμένο μήκος και τέλος όλες οι καταστάσεις να επικοινωνούν μεταξύ τους. Οι προηγούμενες ιδιότητες περιγραφούν τις μηχανές πεπερασμένων καταστάσεων ως εργοδικές αλυσίδες Μαrkov, επιτρέποντας τη σύνθεση συναρτήσεων μέσω της εκτέλεσης λογικών πράξεων μεταξύ των πιθανοτήτων των καταστάσεων.

Παρά τα πολλαπλά πλεονεκτήματα τους, οι στοχαστικές μηχανές πεπερασμένων καταστάσεων έχουν και τις δικές τους αδυναμίες. Η κυριότερη από αυτές, είναι η εισαγωγή συσχετίσεων μεταξύ των ψηφίων της ακολουθίας εξόδου, γεγονός που είναι λογικό, δεδομένων των στοιχείων μνήμης που απαιτούνται για την υλοποίηση των μηχανών κατάστασης. Στην πρώτη προσέγγιση που έγινε για τη μοντελοποίησή τους, ο υπολογισμός της αυτοσυσχέτισης (autocorrelation) της εξόδου καθώς και της μέσς τιμής, επαληθεύτηκε με αριθμητικά πειράματα. Σε μία δεύτερη προσέγγιση, χρησιμοποίηθηκαν αλυσίδες Markov για να αποδείξουν την αρχή λειτουργίας αρκετών μη γραμμικών συναρτήσεων, χωρίς ωστόσο να διερευνώνται οι στατιστικές ιδιότητες της εξόδου. Στο γενικό πλαίσιο της συσχέτισης, αυτή προσεγγίζεται κυρίως από την οπτική γωνία της ακολουθίας εισόδου, στην οποία οι μετατροπείς δυαδικών σε στοχαστικούς αριθμούς μοιράζονται την πηγή τυχαίων αριθμών τους με σκοπό τη δημιουργία ακολουθιών εισόδου με μέγιστη επικάλυψη μεταξύ των θέσεων των λογικών τους μονάδων. Η τεχνική αυτή ενώ επιτρέπει

την αποδοτική υλοποίηση ορισμένων αριθμητικών πράξεων, όπως για παράδειγμα την αφαίρεση, είναι προσαρμοσμένη στην ίδια την πράξη.

Με αφορμή τις ανάγκες για βαθιά κατανόηση των στατιστικών ιδιοτήτων των εξόδων των στοχαστικών μηχανών πεπερασμένων καταστάσεων, στην παρούσα εργασία εισάγεται ένα μαθηματικό πλαίσιο για τη λεπτομερή ανάλυση και εξαγωγή τους, βασισμένο σε αλυσίδες Markov. Πρόκειται για μια γενική μεθοδολογία, υπό την έννοια ότι μπορεί να εφαρμοστεί σε οποιοδήποτε στοχαστική μηχανή πεπερασμένων καταστάσεων εκφρασμένη υπό τη μορφή Moore και μοντελοποιημένη ως αλυσίδα Markov. Η κύρια συνεισφορά της εργασίας είναι ο αναλυτικός υπολογισμός με τη χρήση κλειστού τύπου εκφράσεων των ακόλουθων στατιστικών ιδιότήτων που περιλαμβάνουν: την αναμενόμενη τιμή και τη μέση τιμή της εξόδου, την αυτοσυσχέτιση και την αυτοσυνδιακύμανση της εξόδου, την ετεροσυσχέτιση και η ετεροσυνδιακύμανση της εξόδου με τις εισόδους, της διακύμανσης και της τυπική απόκλισης του μέσου όρου της εξόδου, του μέσου τετραγωνικού σφάλματος του μέσου όρου της εξόδου, την πιθανότητα υπερχείλισης και υποχείλισης στις καταστάσεις κορεσμού και τέλος τον αναμενόμενο αριθμό βημάτων πριν από τις υπερχειλίσεις και τις υποχειλίσεις, ο οποίος κατά συνέπεια θέτει τις κατευθυντήριες γραμμές για την επιλογή του αριθμού των καταστάσεων που μειώνουν τα λανθασμένα ψηφία που προέρχονται από τις υπερχειλίσεις και τις υποχειλίσεις.

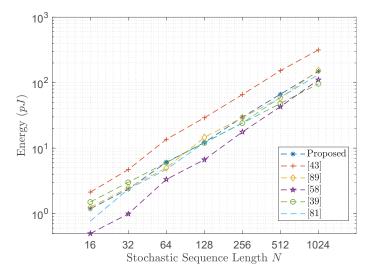

Για την αξιολόγηση της επίδοσης των προτεινόμενων αρχιτεκτονικών, γίνεται η σύγκρισή τους με υπάρχουσες προσεγγίσεις στη βιβλιογραφία του στοχαστικού υπολογισμού. Ειδικότερα, οι προτεινόμενες αρχιτεκτονικές συγκρίνονται σε υπολογιστή ακρίβεια χρησιμοποιώντας μετρικές σφαλμάτων για διαφορετικά μήκη ακολουθίας εισόδου καθώς και σε αξιοποίηση πόρων υλικού, συμπεριλαμβανομένων του χώρου που καταλαμβάνουν τα κυκλώματα, κατανάλωση ενέργειας και ισχύος σύμφωνα με την μέγιστη δυνατή συχνότητα λειτουργίας. Τα αποτελέσματα έδειξαν πως δεδομένης της αξιοποίησης των εσωτερικών καταχωρητών και μετρητών, οι προτεινόμενες αρχιτεκτονικές επιτυγχάνουν μεγαλύτερη υπολογιστική ακρίβεια με μικρά μήκη ακολουθιών εισόδου, αυξάνοντας ελάχιστα τους συνολικούς πόρους. Αξίζει να σημειωθεί πως λαμβάνοντας υπόψιν την αντιστάθμιση καθυστέρησης - αύξησης υπολογιστικής ακρίβειας, στην πραγματικότητα η συνολική κατανάλωση ενέργειας για τις προτεινόμενες αρχιτεκτονικές είναι παρόμοια ή και μικρότερη από τις υπάρχουσες προσεγγίσεις, αφού είναι περιττή η χρήση μεγάλου μήκους ακολουθιών εισόδου.

Σε επίπεδο εφαρμογής, οι προτεινόμενες αρχιτεκτονικές αξιοποιήθηκαν για την υλοποίηση διαφόρων διεργασιών που εκτελούνται από ψηφιακούς επεξεργαστές. Σε αυτές συμπεριλαμβάνονται: δομική μονάδα συνέλιξης, φίλτρα χωρικής ενίσχυσης (spatial enhancement filters) και τέλος νευρωνικό δίκτυο ΜLP. Σε επίπεδο αξιοποίησης υλικού, οι δομικές μονάδες συγκρίθηκαν με τις συμβατές δυαδικές υλοποιήσεις σε χώρο που καταλαμβάνουν τα κυκλώματα, κατανάλωση ενέργειας και ισχύος σύμφωνα με την μέγιστη δυνατή συχνότητα λειτουργίας.

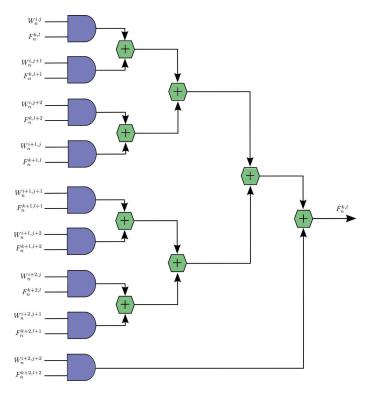

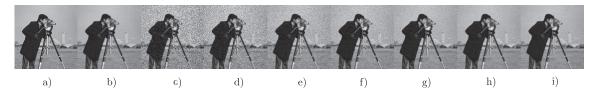

Ξεκινώντας με τον προτεινόμενο αθροιστή, για να γίνει αισθητή η αποτελεσματικότητα του σε αλυσιδωτούς υπολογισμούς δεδομένης της μη κλιμακωτής φύσης του, χρησιμοποιήθηκε παράλληλα με λογικές πύλες AND για την υλοποίηση δομικής μονάδας που εκτελεί την πράξη της συνέλιξης. Έπειτα, η δομική μονάδα χρησιμοποιήθηκε ως μάσκα για το φιλτράρισμα εικόνας με σκοπό την εξομαλύνση των εικονοστοιχείων (pixels) της έτσι ώστε να γίνει μείωση του θορύβου της εικόνας. Τα αποτελέσματα στην αξιολόγηση της ποιότητας εικόνας έδειξαν πως ο προτεινόμενος αθροιστής επιτυγχάνει αποδεκτές τιμές,

οι οποίες είναι εξαιρετικά βελτιωμένες συγκριτικά με τους κλιμακωτούς αθροιστές. Σε επίπεδο υλικού, ο χώρος που καταλαμβάνεται είναι εξαιρετικά μικρότερος από αυτόν του συμβατού δυαδικού, ωστόσο, η κατανάλωση ενέργειας ανέρχεται σε μέτριες τιμές, που είναι αναμενόμενο δεδομένης της φύσης του στοχαστικού υπολογισμού

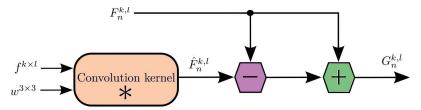

Συνεχίζοντας με τον προτεινόμενο στοχαστικό αφαιρέτη, η αξιοποίηση του γίνεται αισθητή στην υλοποίηση φίλτρου ενίσχυσης ευκρίνειας εικόνας (image sharpening filter). Αναλυτικότερα, το φίλτρο ενίσχυσης ευκρίνειας εικόνας διαχωρίζεται σε τρεις υπολογισμούς που περιλαμβάνουν το φιλτράρισμα, την εξαγωγή των λεπτομερειών της εικόνας και τέλος την ενίσχυσή της. Από τα παραπάνω, το φιλτράρισμα γίνεται μέσω συνέλιξης χρησιμοποιώντας τη δομική μονάδα που υλοποιείται μέσω του στοχαστικού αθροιστή, ο οποίος χρησιμοποιείται και για την τελική ενίσχυση. Η εξαγωγή των λεπτομερειών απαιτεί την αφαίρεση της φιλτραρισμένης εικόνας από την αρχική, μία διαδικασία που είναι κατάλληλη για τον προτεινόμενο στοχαστικό αφαιρέτη καθώς οι ήδη υπάρχουσες προσεγγίσεις αδυνατούν στην υλοποίηση μη κλιμακωτής αφαίρεσης. Αναφορικά με την αξιολόγηση της ποιότητας εικόνας, τα αποτελέσματα ήταν σχεδόν βέλτιστα, ενώ σε επίπεδο αξιοποίηση πόρων η μείωση του χώρου που καταλαμβάνει το κύκλωμα συγκριτικά με τη συμβατή δυαδική υλοποίηση ήταν αισθητή, ωστόσο, η κατανάλωση ενέργειας ανήλθε σε μέτριες τιμές.

Οι αρχιτεκτονικές μεγίστου/ελαχίστου, ήταν κατάλληλες για την υλοποίηση φίλτρου διαμέσου (median filter), το οποίο χρησιμοποιείται για τη βελτίωση εικόνας που έχει υποστεί αλλοίωση στα εικονοστοιχεία της, όπως για παράδειγμα αλλοίωση λόγω θορύβου. Η δομή της διάταξης του φίλτρου διαμέσου, βασίζεται σε αλγόριθμο αποδοτικής ταξινόμησης, δηλαδή συγκρίσεις μεγέθους μεταξύ των εισόδων. Συγκριτικά με το φίλτρο εξομάλυνσης, το φίλτρο διαμέσου έχει την ιδιότητα να διατηρεί τις ακμές της εικόνας (edge preservation), καθιστόντας το κατάλληλο για στάδια προ-επεξεργασίας εικόνας πριν την ανίχνευση ακμών (edge detection). Τα αποτελέσματα σε επίπεδο υπολογιστικής ακρίβειας έδείξαν πως και οι δύο προτεινόμενες αρχιτεκτονικές μεγίστου/ελαχίστου ήταν ικανοποιητικές για φιλτράρισμα εικόνας με θόρυβο. Σχετικά με την αξιοποίηση των πόρων, η δεύτερη αρχιτεκτονική μεγίστου/ελαχίστου αξιοποιεί παραπάνω κυκλωματικό χώρο από την πρώτη, όμως, και οι δύο καταλάμβαναν σχεδόν το μισό από αυτό της συμβατής δυαδικής υλοποίησης. Όπως και με τις άλλες δύο εφαρμογές, η κατανάλωση ενέργειας ανήλθε σε μέτριες τιμές συγκριτικά με τη συμβατή δυαδική, δεδομένου του συνολικό μήκος ακουλουθιών που επεξεργάζονται.

Η δεύτερη προτεινόμενη αρχιτεκτονική του μεγίστου, χρησιμοποιήθηκε για την υλοποίηση φίλτρου μέγιστης συγκέντρωσης (max pooling). Η λειτουργία του βασίζεται στην υποδειγματοληψία (undersampling) εικόνας καθώς μειώνει τη διάσταση της, ενώ αποτελεί αναπόσπαστο κομμάτι στα σύγχρονα νευρωνικά δίκτυα δεδομένου ότι επιτρέπει την εξαγωγή των σημαντικότερων χαρακτηριστικών της εικόνας εισόδου. Τα αποτελέσματα σε επίπεδο υπολογιστικής ακρίβειας έδειξαν πως η υποδειγματοληψία της εικόνας πραγματοποιείται με το βέλτιστο δυνατό τρόπο, το οποίο υποστηρίζεται από τις μετρικές που λαμβάνονται υπόψιν. Όσο αναφορά την αξιοποίηση των πόρων του υλικού, συγκριτικά με την δυαδική υλοποίηση παρατηρείται πως ο χώρος που καταλαμβάνει το κύκλωμα μειώνεται επαρκώς.

Τέλος, ο αθροιστής SCSD χρησιμοποιήθηκε μαζί με την πρώτη αρχιτεκτονική του μεγίστου για την υλοποίηση στοχαστικού νευρώνα, ο οποίος αποτέλεσε τη βάση για την υλοποίηση ενός MLP. Τα αποτελέσματα σε επίπεδο κατηγοριοποίησης για δύο διαφορετικές αρχιτεκτονικές δικτύου MLP σε ρεαλιστικό

σύνολο δεδομένων, έδειξαν πως η ακρίβεια που επιτυγχάνεται υπερβαίνει αυτήν που επιτυγχάνεται με την τυπική δυαδική αναπαράσταση αριθμών των οκτώ και των δεκαέξι ψηφίων. Επιπλέον, συγκριτικά με αυτές τις αναπαραστάσεις, μειώνεται δραματικά χώρος που καταλαμβάνει ο εκάστοτε νευρώνας. Συγκρίσεις με ήδη υπάρχοντα ΜLP στο πεδίο του στοχαστικού υπολογισμού, ανέδειξαν τη δυνατότητα για επεξεργασία με μικρά μήκη ακολουθιών εισόδου καθώς και την ευελιξία στη συνολική σχεδίαση.

# **Acknowledgements**

I am extremely grateful to my supervisor Professor Paul-Peter Sotiriadis for his invaluable help and support in making this dissertation possible. His teachings and immense scientific knowledge were of vital importance as they effectively guided me towards becoming a devoted research scientist. Having worked under his supervision is honorable for me to the greatest degree and for that I am deeply thankful.

I would like to express my appreciation to the honorable members of my advisory committee Professor Emeritus Kiamal Pekmestzi and Professor Athanasios Panagopoulos for their excellent feedback and support throughout the years of my PhD studies. My sincere thanks are extended to the honorable members of the examination committee Professor Panayiotis Psarrakos, Professor Theodora Varvarigou, Associate Professor Anastasios Doulamis and Professor Nikolaos Doulamis for their participation and their instructive comments. My special thanks to Professor Panayiotis Psarrakos for his important teachings in Linear Algebra.

I would like to thank from the bottom of my heart my fellow PhD students Baxevanakis Dimitrios, Konstantinos Papafotis, Konstantinos Touloupas, Konstantinos Asimakopoulos, Costas Oustoglou, Charis Basetas, Christos Dimas, Ioannis Georgakopoulos, Vassilis Alimisis, Neoclis Hadjigeorgiou as well as the rest NTUA Circuits & Systems Group members for the moments that we shared and the friendships we developed, hopefully lasting in the years to come. A special thanks goes to my friend Dr. Nikolaos Voudoukis for his life advices as well as to Konstantinos Touloupas and to Konstantinos Papafotis for their invaluable time they spent in carefully reviewing and improving my publications.

I am forever grateful to my teachers and mentors Professors Dimitrios Nikolopoulos and Panayiotis Yannakopoulos for introducing me to the scientific way of thinking, for their invaluable teachings and for supporting me throughout the years of my studies, in every possible way.

Many thanks towards the Hellenic Foundation for Research and Innovation (HFRI) for supporting financially this dissertation.

My wholehearted thanks go to my parents Eirini and Alekos Temenos, my aunt Despoina Driva, my brother Tasos and my friends for their continuous support, understanding, love and encouragement throughout the years of my studies. Finally yet importantly, my deepest gratitude goes to Mr. Panagiotis Sotiriadis, a generous and kind soul, for inspiring me and for his tremendous effort in helping me to further continue my studies to the advanced degrees. I will remember him forever.

18 Acknowledgements

# **Abbreviations**

SC Stochastic Computing

SNG Stochastic Number Generator

LFSR Linear-Feedback Shift Register

MC Markov Chain

**FSM** Finite-State Machine

SFSM Stochastic Finite-State Machine

DSP Digital Signal Processing/Processor

FPGA Field-Programmable Gate Array

ICIntegrated CircuitFxPFixed Point ArithmeticFPFloating Point Arithmetic

SCPB Stochastic Computing Processing Block

MAEMean Absolute ErrorMSEMean Squared Error

**PSNR** Peak Signal-to-Noise Ratio

SSIM Structural Similarity Index Measure

20 Abbreviations

# **Contents**

| 1 | 1.1<br>1.2 |           | nation and Scope                                       | 3:<br>3:<br>3: |

|---|------------|-----------|--------------------------------------------------------|----------------|

| 2 | Stoc       | hastic (  | Computing Principles                                   | 35             |

| I | The        | oretica   | l Analysis                                             | 3′             |

| 3 | Stoc       | hastic (  | Computing Architectures                                | 39             |

|   | 3.1        | Non-S     | caling Adder and Subtracter Architectures              | 39             |

|   |            | 3.1.1     | Non-Scaling Adder Architecture                         | 40             |

|   |            | 3.1.2     | Non-Scaling Subtracter Architecture                    | 44             |

|   | 3.2        | MAX       | and MIN Architectures                                  | 46             |

|   |            | 3.2.1     | Stochastic MAX Architecture                            | 47             |

|   |            | 3.2.2     | Stochastic MIN Architecture                            | 53             |

|   | 3.3        | Compa     | act MAX and MIN Architectures                          | 55             |

|   |            | 3.3.1     | Compact MAX Architecture                               | 56             |

|   |            | 3.3.2     | Compact MIN Architecture as a Variation of the MAX one | 60             |

|   | 3.4        | Stocha    | stic Computing Sigma-Delta Adder                       | 6              |

|   |            | 3.4.1     | SCSD High-Level Architecture                           | 62             |

|   |            | 3.4.2     | Markov Chain Modeling                                  | 6.5            |

| 4 | Stat       | istical P | Properties Of Stochastic Finite-State Machines         | 69             |

|   | 4.1        | Finite-   | State Machines in Stochastic Computing                 | 69             |

|   | 4.2        | Stocha    | stic Finite State Machines & Markov Chain Modeling     | 7              |

|   |            | 4.2.1     | Stochastic Finite State Machines                       | 7              |

|   |            | 4.2.2     | Markov Chain Modeling of a Stochastic FSM              |                |

|   | 4.3        | Statisti  | ical Modeling of Stochastic FSMs                       |                |

|   |            | 4.3.1     | Expected Value                                         | 7:             |

|   |            | 4.3.2     | Auto-Correlation & Covariance                          | 7:             |

|   |            | 4.3.3     | Cross-Correlation & Covariance                         | 70             |

22 Contents

| Re | eferen         | ces                                                                                | 139        |

|----|----------------|------------------------------------------------------------------------------------|------------|

| 7  | Con            | clusion                                                                            | 133        |

|    |                | 6.5.3 SCSD MLP Performance                                                         | 126        |

|    |                | 6.5.2 Forming a SC Multi-Layer Perceptron                                          |            |

|    |                | 6.5.1 SCSD Adder Artificial Neuron                                                 |            |

|    | 6.5            | Neural Network Design                                                              |            |

|    | 6.4            | MAX Pooling                                                                        |            |

|    |                | 6.3.2 Compact MAX and MIN                                                          |            |

|    |                | 6.3.1 MAX and MIN                                                                  |            |

|    | 6.3            | Median Filter                                                                      |            |

|    | 6.2            | Image Sharpening Filter                                                            |            |

| 6  | <b>App</b> 6.1 | lications Image Blurring                                                           | 115<br>115 |

| _  |                |                                                                                    |            |

|    | 5.4            | Comparison of Stochastic Compact MAX and MIN                                       |            |

|    | 5.3            | Comparison of Stochastic MAX and MIN                                               |            |

|    | 5.2            | Comparison of Stochastic Subtracters                                               |            |

| 5  | 5.1            | nparison with the Stochastic Computing Literature  Comparison of Stochastic Adders | 100        |

| _  |                |                                                                                    | 99         |

| П  | Pei            | rformance Results and Applications                                                 | 97         |

|    |                | 4.5.3 Execution Times Performance                                                  | 89         |

|    |                | 4.5.2 Modeling Example 2: Stochastic Adder                                         | 84         |

|    |                | 4.5.1 Modeling Example 1: Stochastic Tanh                                          | 81         |

|    | 4.5            | Modeling Examples                                                                  | 81         |

|    |                | 4.4.3 Guidelines to select the number of states                                    | 80         |

|    |                | 4.4.2 Expected number of Steps before Overflows/Underflows                         | 79         |

|    |                | 4.4.1 Stochastic Finite-State Machine Overflow/Underflow Modeling                  | 78         |

|    | 4.4            | Number of States Selection & Register Size Estimation                              | 78         |

|    |                | 4.3.5 Mean Squared Error Analysis                                                  | 77         |

|    |                | 4.3.4 Variance and Standard Deviation                                              | 77         |

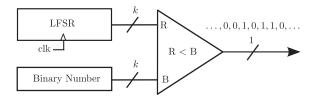

| 2.1  | Stochastic Number Generator                                                                                                                                                                 | 35 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

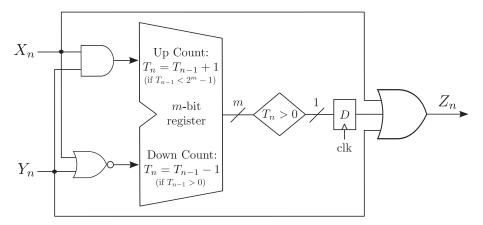

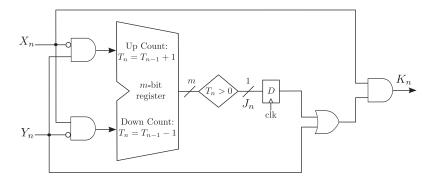

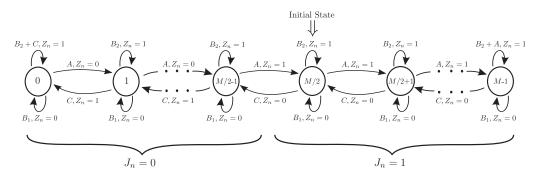

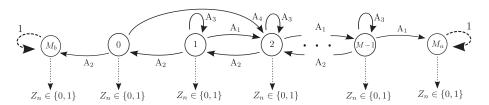

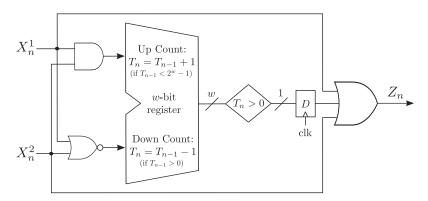

| 3.1  | Proposed stochastic adder Architecture. $T_n$ is the $m$ -bit register's state, updated accord-                                                                                             |    |

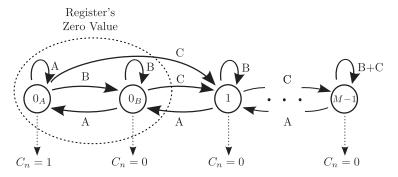

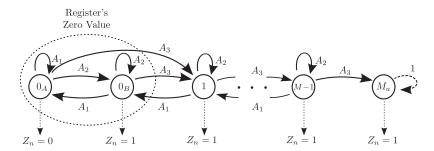

|      | ing to 3.1                                                                                                                                                                                  | 40 |

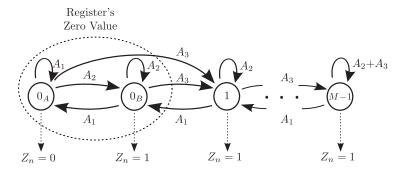

| 3.2  | Markov Chain model of the proposed stochastic adder. The register's zero state, is represented by two states in the model, $0_A$ and $0_B$ . Transition probabilities $A$ , $B$ and $C$ are |    |

|      | given by (3.3)                                                                                                                                                                              | 41 |

| 3.3  | Proposed stochastic subtracter architecture. $T_n$ is the $m$ -bit register's current state, up-                                                                                            |    |

|      | dated according to (3.17).                                                                                                                                                                  | 45 |

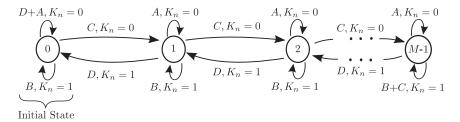

| 3.4  | Markov Chain model of the proposed stochastic subtracter. The register's zero state, is                                                                                                     |    |

|      | represented by two states in the model, $0_A$ and $0_B$ . Transition probabilities $A$ , $B$ and $C$                                                                                        |    |

|      | are given by (3.18)                                                                                                                                                                         | 45 |

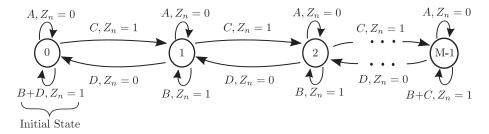

| 3.5  | Proposed stochastic MAX architecture. $T_n$ is the $m$ -bit register's state, updated according                                                                                             |    |

|      | to (3.23)                                                                                                                                                                                   | 47 |

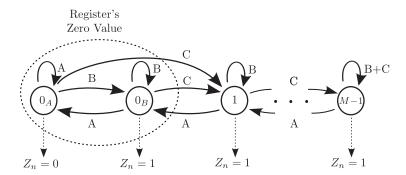

| 3.6  | Markov Chain model of the proposed stochastic MAX architecture. Output $\mathbb{Z}_n$ is deter-                                                                                             |    |

|      | mined by the state's transition according to transition probabilities $A,B,C,D$ given by                                                                                                    |    |

| 27   | (3.26)                                                                                                                                                                                      | 48 |

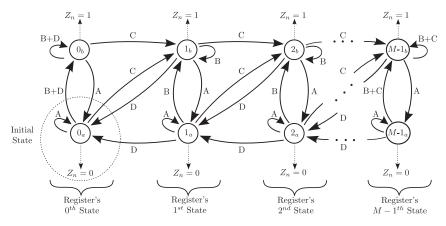

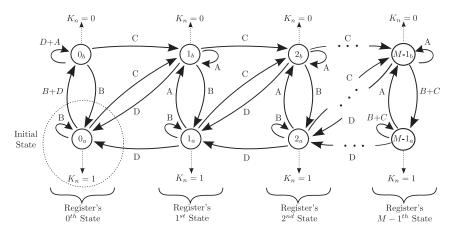

| 3.7  | sition probabilities given by (3.26). Each register state is represented by two states in                                                                                                   |    |

|      | the model and is classified into two subsets of states; upper ones outputting $Z_n = 1$ and                                                                                                 |    |

|      | lower ones outputting $Z_n = 0$ . Subscripts $a, b$ denote in which subset $\tilde{S}_n$ is currently                                                                                       |    |

|      | into. Transition probabilities $A, B, C, D$ are given by (3.26)                                                                                                                             | 50 |

| 3.8  | Proposed stochastic MIN architecture. $T_n$ is the $m$ -bit register's state, updated according                                                                                             | 50 |

| 3.0  | to $(3.23)$                                                                                                                                                                                 | 53 |

| 3.9  | Markov Chain model of the proposed stochastic MIN architecture. Output $K_n$ is deter-                                                                                                      |    |

| 3.7  | mined by the state's transition according to transition probabilities $A, B, C, D$ given by                                                                                                 |    |

|      | (3.26)                                                                                                                                                                                      | 54 |

| 3.10 | Extended Markov Chain model of the proposed stochastic MIN with transition probabil-                                                                                                        |    |

|      | ities given by (3.26). Each register state is represented by two states; upper one outputs                                                                                                  |    |

|      | $K_n = 0$ and lower one outputs $K_n = 1$ . Subscripts $a, b$ denote in which set $\tilde{S}_n$ is cur-                                                                                     |    |

|      | rently into                                                                                                                                                                                 | 54 |

|      |                                                                                                                                                                                             |    |

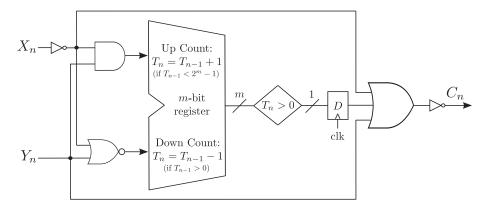

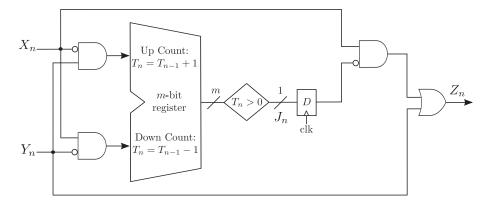

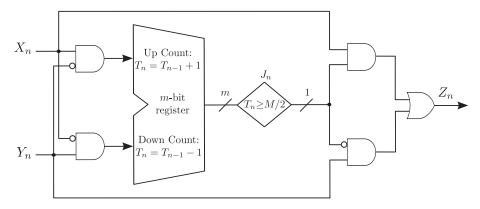

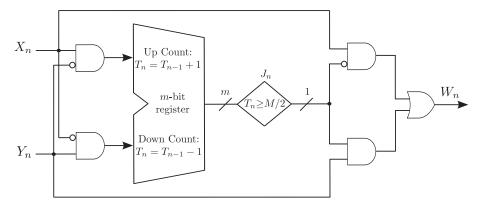

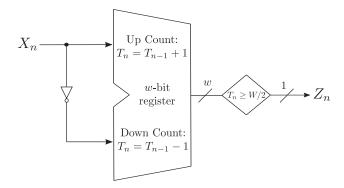

| 3.11 | Proposed compact stochastic MAX architecture where $M=2^{m}$ . $T_n$ is the register's                           |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | current value, updated according to (3.54)                                                                       | 56 |

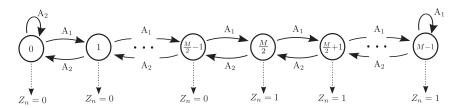

| 3.12 | Markov Chain model of the proposed compact stochastic MAX architecture. Transition                               |    |

|      | probabilities are given by $(3.58)$ . $J_n$ denotes the result of the comparison between the                     |    |

|      | register's current value with the initial one $M/2$                                                              | 57 |

| 3.13 | Proposed compact stochastic MIN architecture. $T_n$ denotes the $M=2^m$ register's cur-                          |    |

|      | rent value and is updated according to (3.54)                                                                    | 61 |

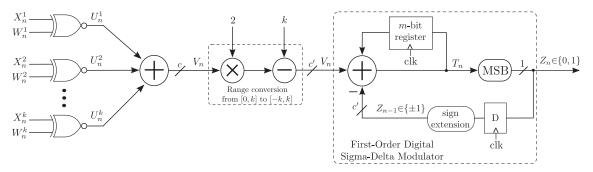

| 3.14 | Architecture of the proposed Stochastic Computing Sigma-Delta (SCSD) adder. The                                  |    |

|      | XNOR gates between the input sequences $\{X_n^j\}_{n=1}^N, \{W_n^j\}_{n=1}^N$ are used to multiply num-          |    |

|      | bers in bipolar format. The multiplication results are added to a single bus with the range                      |    |

|      | of its represented value converted from $[0, k]$ to $[-k, k]$ . The first-order digital SDM con-                 |    |

|      | verts a higher resolution signal into a single-bit one, outputting the average of its input                      |    |

|      | according to (3.80), realizing the sum-of-products                                                               | 62 |

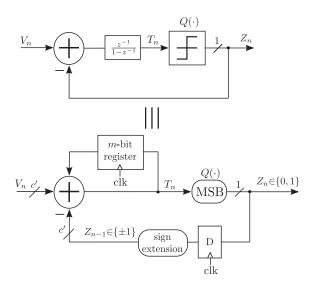

| 3.15 | Top: system level model of a first-order Sigma-Delta Modulator. Bottom: realization of                           |    |

|      | the first-order Digital Sigma-Delta Modulator. The quantizer block, is replaced by the                           |    |

|      | selection of the most significant bit.                                                                           | 64 |

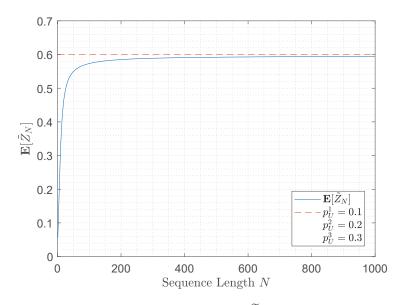

| 3.16 | Expected value of the output's time-average, $\mathbb{E}[\widetilde{Z}_N]$ , calculated using (3.88), estimating |    |

|      | the sums of three inputs with probability values $p_U^1 = 0.1, p_U^2 = 0.2, p_U^3 = 0.3$ , as the                |    |

|      | sequence length increases $N = 1, \dots, 1000.\dots$                                                             | 67 |

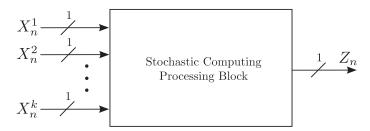

| 4.1  | A multi-input single-output stochastic computing processing block                                                | 71 |

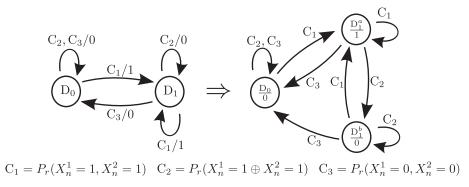

| 4.2  | Conversion example of a stochastic Mealy (left) to Moore (right) FSM. State $D_1$ in the                         |    |

|      | Mealy is separated into two states in the Moore $D_1^a$ , $D_1^b$ outputting 1 and 0 respectively. In            |    |

|      | this example, transition probabilities $C_1, C_2, C_3$ , are arbitrary selected, but, determined                 |    |

|      | by two stochastic input sequences $\{X_n^1\}, \{X_n^2\}, \dots, \dots$                                           | 72 |

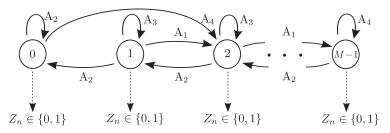

| 4.3  | Example of a Markov Chain model describing the operation of a stochastic FSM. Transi-                            |    |

|      | tion probabilities $A_j$ are defined by a boolean function and determine the state's transition                  |    |

|      | (see example below). The output $Z_n$ is related to the current state, expressing the FSM's                      |    |

|      | behavior as a Moore one, outputting 0 or 1                                                                       | 73 |

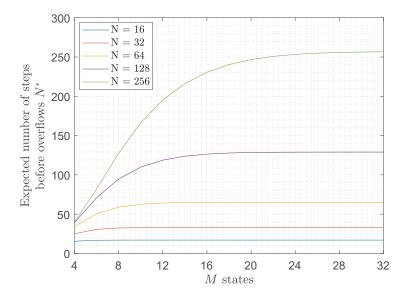

| 4.4  | Example of the Markov Chain overflow/underflow model with absorbing states $\mathcal{M}_a, \mathcal{M}_b$        |    |

|      | corresponding to that of Fig. 4.3                                                                                | 78 |

| 4.5  | Architecture of the stochastic tanh function                                                                     | 81 |

| 4.6  | Markov Chain model describing the operation of the stochastic tanh function. Transition                          |    |

|      | probabilities are given by (4.32)                                                                                | 82 |

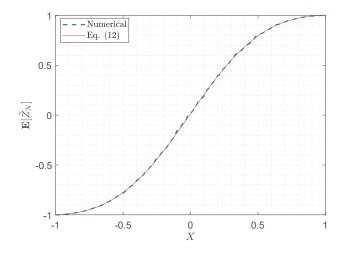

| 4.7  | Expected value of the stochastic tanh's output mean $\mathbb{E}[\tilde{Z}_N]$ calculated using (4.11), pa-       |    |

|      | rameterized with $M=4$ states and sequence length $N=64$ . For the numerical calcula-                            |    |

|      | tions, $10^4$ i.i.d. runs for each point are considered                                                          | 83 |

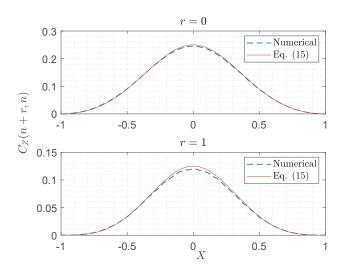

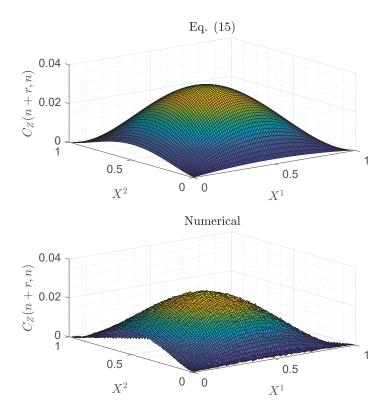

| 4.8  | Auto-Covariance $C_Z(n+r,n)$ of the stochastic tanh's output calculated using (4.14),                            |    |

|      | parameterized with $M=4$ states, sequence length $N=256$ and time lags $r=0,1.$ For                              |    |

|      | the numerical calculations, $10^4$ i.i.d. runs for each point are considered                                     | 84 |

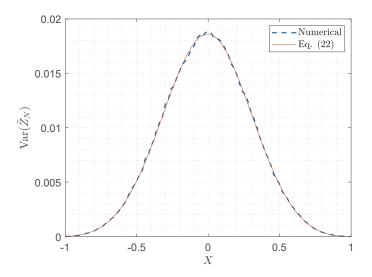

| 4.9  | Variance $Var(\tilde{Z}_N)$ of the stochastic tanh's output mean calculated using (4.21), parameterized with $M=4$ states and sequence length $N=64$ . For the numerical calculations, |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $10^4$ i.i.d. runs for each point are considered                                                                                                                                       | 85  |

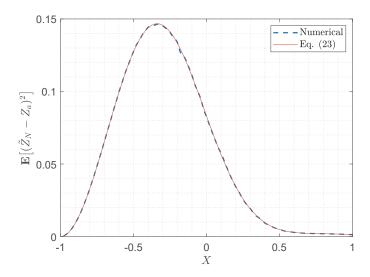

| 4.10 | Mean Squared Error of the stochastic tanh's output mean calculated using (4.22) for $M =$                                                                                              | 0.5 |

| 7.10 | 4 states and input sequence length $N = 64$ . For the numerical calculations, $10^4$ i.i.d. runs                                                                                       |     |

|      | for each point are considered                                                                                                                                                          | 86  |

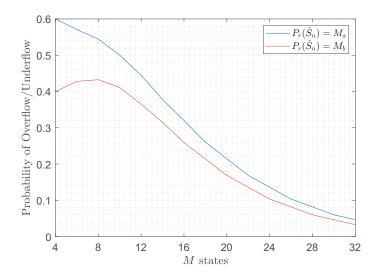

| 4.11 | Markov Chain overflow/underflow model of the stochastic tanh function. Transition                                                                                                      |     |

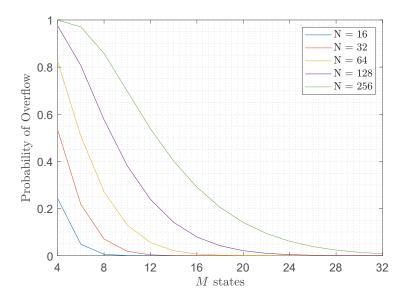

|      | probabilities are given by (4.32)                                                                                                                                                      | 86  |

| 4.12 | Probability of overflow/underflow of the stochastic tanh calculated using (4.27) for increasing number of states $M=4,\ldots,32$ , input $X=0.5$ and sequence length $N=64$ .          |     |

|      |                                                                                                                                                                                        | 87  |

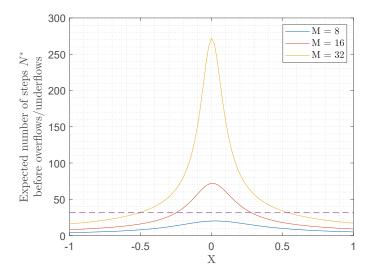

| 4.13 | Expected number of steps before overflows/underflows $N^*$ of the stochastic tanh calculated using (4.31), for $M=8,16,32$ states and sequence length $N=32$ (dashed line).            |     |

|      | The guideline $N^* \geq N$ allows for reduced overflow/underflow occurrence                                                                                                            | 88  |

| 4.14 | Architecture of the stochastic adder [80]                                                                                                                                              | 88  |

| 4.15 | Markov Chain model describing the operation of the stochastic adder. Transition proba-                                                                                                 |     |

|      | bilities are given by (4.36)                                                                                                                                                           | 89  |

| 4.16 | Expected value of the stochastic adder's output mean $\mathbb{E}[\tilde{Z}_N]$ . Top: calculated using                                                                                 |     |

|      | (4.11), parametrized with $M=8$ states and sequence length $N=64$ . Bottom: Nu-                                                                                                        |     |

|      | merical calculations for $10^4$ i.i.d. runs for each point                                                                                                                             | 90  |

| 4.17 | Auto-Covariance $C_Z(n+r,n)$ of the stochastic adder's output. Top: Calculated using (4.14), parametrized with $M=8$ states, sequence length $N=64$ and delay $r=1$ .                  |     |

|      | Bottom: Numerical calculations for $10^4$ i.i.d. runs for each point                                                                                                                   | 91  |

| 4.18 | Variance of the stochastic adder's output mean $Var(\tilde{Z}_N)$ . Top: calculated using (4.21),                                                                                      |     |

|      | parametrized with $M=8$ states and sequence length $N=64$ . Bottom: Numerical                                                                                                          |     |

|      | calculations for $10^4$ i.i.d. runs for each point.                                                                                                                                    | 92  |

| 4.19 | Mean Squared Error of the stochastic adder's output mean MSE( $\tilde{Z}_N$ ). Top: calculated                                                                                         |     |

|      | using (4.22), parametrized with $M=8$ states and input sequence length $N=64$ . Bot-                                                                                                   |     |

|      | tom: Numerical calculations for $10^4$ i.i.d. runs for each point                                                                                                                      | 93  |

| 4.20 | Markov Chain overflow model of the stochastic adder. Transition probabilities are given                                                                                                |     |

|      | by (4.36)                                                                                                                                                                              | 93  |

| 4.21 | Probability of overflow of the stochastic adder calculated using (4.40), for inputs $X^1 =$                                                                                            |     |

|      | $X^2=0.5$ , increasing number of states $M=4,\ldots,32$ and increasing sequence lengths $N$ .                                                                                          | 94  |

| 4.22 | Expected number of steps before overflows $N^*$ of the stochastic adder calculated using                                                                                               |     |

|      | (4.31), for $M=4,\ldots,32$ states, inputs $X^1=X^2=0.5$ and increasing sequences                                                                                                      |     |

|      | lengths $N.$ The guideline $N^* \geq N$ allows for reduced overflow occurrence                                                                                                         | 94  |

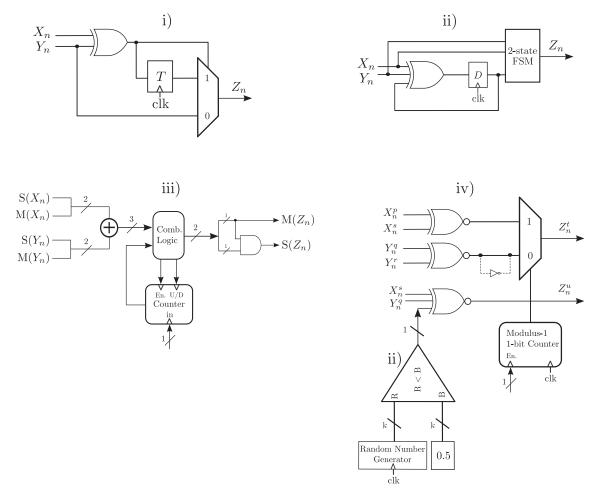

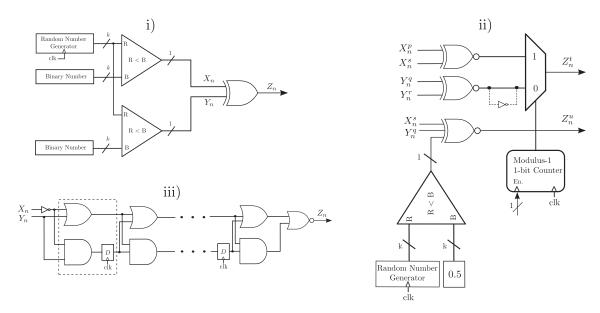

| 5.1  | Stochastic Computing adders. From top left to bottom right: i) Scaling adder in [41], ii)                                                                                              |     |

|      | Scaling adder in [84], iii) Non-scaling adder in [72] and iv) Scaling/Non-Scaling adder                                                                                                |     |

|      |                                                                                                                                                                                        | 100 |

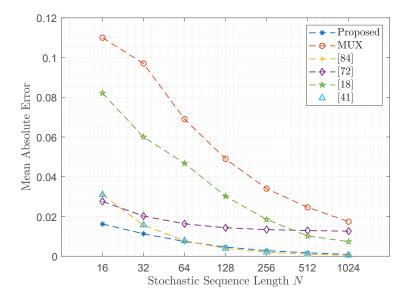

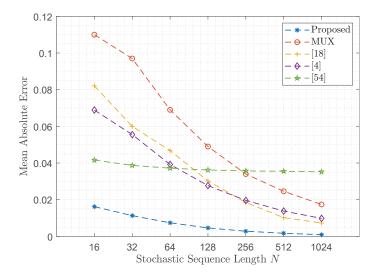

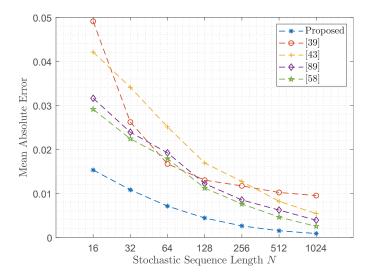

| 5.2  | Comparison of accuracy in MAE of stochastic adders for typical stochastic sequence                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | lengths $N$                                                                                                                                                                             |

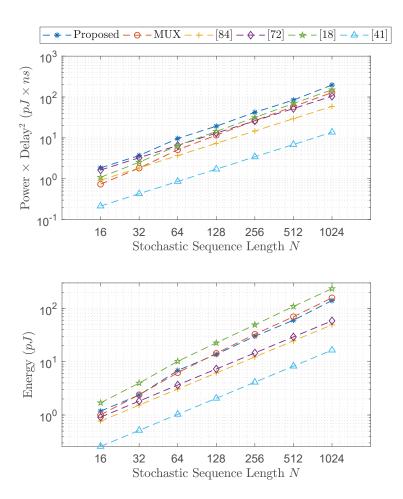

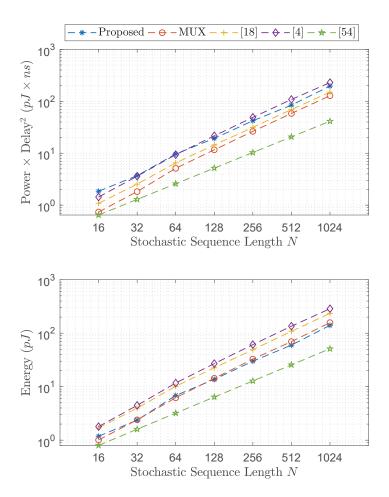

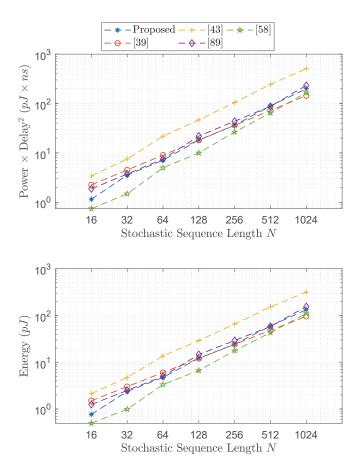

| 5.3  | Comparison of Power $\times$ Delay <sup>2</sup> $(pJ \times ns)$ (top) and Energy $(pJ)$ (bottom) consumption                                                                           |

|      | of stochastic adders for typical stochastic sequence lengths $N \dots $           |

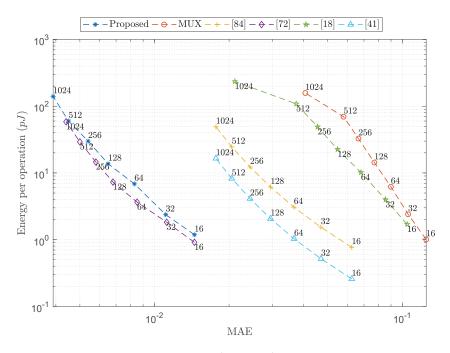

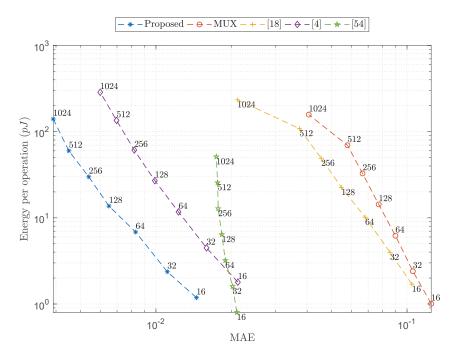

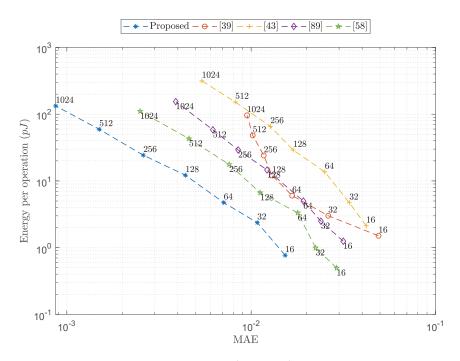

| 5.4  | Comparison of Energy per operation $(pJ \times ns)$ and MAE of stochastic adders for typical                                                                                            |

|      | stochastic sequence lengths $N$ . Sobol sequences are used                                                                                                                              |

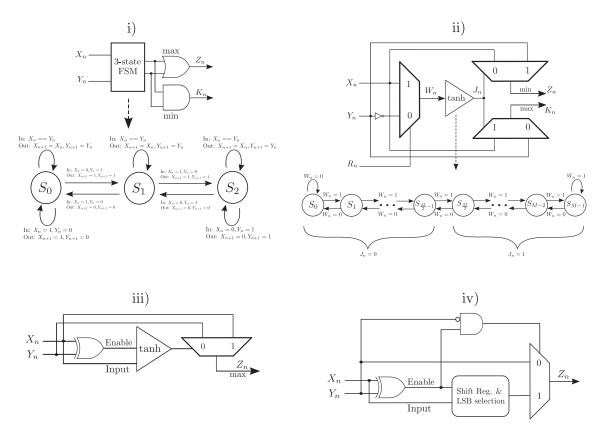

| 5.5  | Stochastic Computing subtracters. From top left to bottom right: i) Absolute correlated                                                                                                 |

|      | input subtracter in [4], ii) Scaling/Non-scaling subtracter in [18] and iii) Subtracter in [54].103                                                                                     |

| 5.6  | Comparison of accuracy in MAE of stochastic subtracters for typical stochastic sequence                                                                                                 |

|      | lengths $N$                                                                                                                                                                             |

| 5.7  | Comparison of Power $\times$ Delay <sup>2</sup> $(pJ \times ns)$ (top) and Energy $(pJ)$ (bottom) consumption                                                                           |

|      | of stochastic subtracters for typical stochastic sequence lengths $N \ldots \ldots \ldots 100$                                                                                          |

| 5.8  | Comparison of Energy per operation $(pJ \times ns)$ and MAE of stochastic subtracters for                                                                                               |

|      | typical stochastic sequence lengths $N$ . Sobol sequences are used                                                                                                                      |

| 5.9  | Stochastic computing max and min architectures. From top left to bottom right: 1) Cor-                                                                                                  |

|      | related MAX/MIN in [39], ii) Tanh MAX/MIN in [43], iii) Tanh MAX/MIN w/o RNG                                                                                                            |

|      | [89] and iv) Shift Register MAX/MIN in [58]                                                                                                                                             |

| 5.10 | Accuracy comparison in MAE of stochastic MAX/MIN architectures for typical sequence                                                                                                     |

|      | lengths $N$ . For each $N$ , the architectures' number of states is selected to result in the                                                                                           |

|      | highest computational accuracy. Corresponding register sizes are cited in 5.2 109                                                                                                       |

| 5.11 | Comparison of Power $\times$ Delay <sup>2</sup> $(pJ \times ns)$ (top) and Energy $pJ$ (bottom) consumption                                                                             |

|      | of stochastic MAX/MIN architectures. For each $N$ , the architectures' number of states                                                                                                 |

|      | is selected to result in the highest computational accuracy. Corresponding register sizes                                                                                               |

|      | are cited in 5.2                                                                                                                                                                        |

| 5.12 | Comparison of Energy per operation $(pJ \times ns)$ and MAE of stochastic MAX/MIN for                                                                                                   |

|      | typical stochastic sequence lengths $N$                                                                                                                                                 |

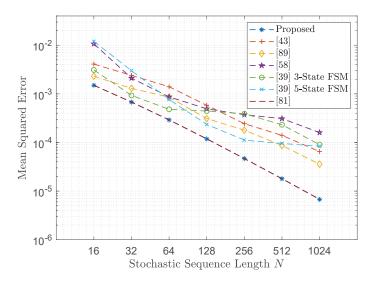

| 5.13 | Accuracy comparison in MSE of stochastic MAX architectures for typical sequence lengths                                                                                                 |

|      | N. For each $N$ , their register sizes are selected to result in the highest MSE and are cited                                                                                          |

|      | in Table 5.4                                                                                                                                                                            |

| 5.14 | Energy comparison in $pJ$ of stochastic MAX architectures for typical sequence lengths                                                                                                  |

|      | N. For each $N$ , their register sizes are selected to result in the highest MSE and are cited                                                                                          |

|      | in Table 5.4                                                                                                                                                                            |

| 6.1  | A $3 \times 3$ stochastic computing convolution kernel realized using 9 AND gates for multi-                                                                                            |

| 0.1  | plication and 8 proposed non-scaling stochastic adders. $W_n$ and $F_n$ denote the generated                                                                                            |

|      | sequences of weights and the input image pixel values respectively. $\dots \dots \dots$ |

| 6.2  | Image filtering using a $3\times3$ convolution kernel for various sequence lengths N. From left                                                                                         |

| 0.2  | to right cases: a) Original image b) MATLAB's blur calculation c) $N=16$ d) $N=32$                                                                                                      |

|      | e) $N = 64$ f) $N = 128$ g) $N = 256$ h) $N = 512$ i) $N = 1024$                                                                                                                        |

|      | -,                                                                                                                                                                                      |

| 6.3  | Image sharpening filter realized using the proposed non-scaling adder and subtracter. The                     |     |

|------|---------------------------------------------------------------------------------------------------------------|-----|

|      | convolution kernel is realized as shown in Fig. 6.1                                                           | 118 |

| 6.4  | Image Sharpening Filter. From left to right: a) MATLAB's Original Image, b) MAT-                              |     |

|      | LAB's Image Sharpening calculation, c) Image Sharpening Filter realized with the pro-                         |     |

|      | posed SC architectures. Sequence length $N=256$ and register size $m=4$ -bit                                  | 119 |

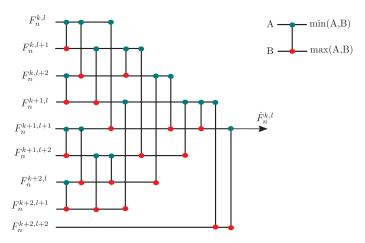

| 6.5  | Sorting network realizing a SC median filter. Each node is realized using the proposed                        |     |

|      | MAX and MIN architectures                                                                                     | 120 |

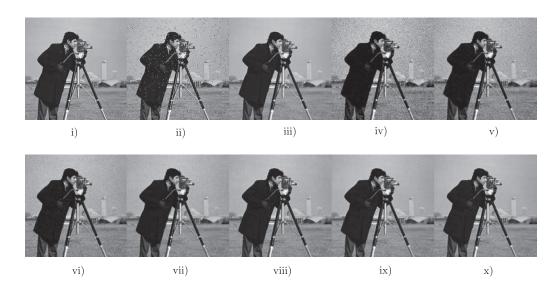

| 6.6  | Median Filtering with a $3\times3$ kernel, realized using the proposed MAX and MIN archi-                     |     |

|      | tectures for various sequence lengths $N$ . From upper left to lower right: i) MATLAB's                       |     |

|      | Original Image ii) MATLAB's Noisy Image with salt & pepper noise density 0.02 iii)                            |     |

|      | MATLAB's filtered image iv) $N=16$ v) $N=32$ vi) $N=64$ vii) $N=128$ viii)                                    |     |

|      | N=256 ix) $N=512$ x) $N=1024$ . Register size used is $m=2$ corresponding to                                  |     |

|      | $M=4 	ext{ states}$                                                                                           | 121 |

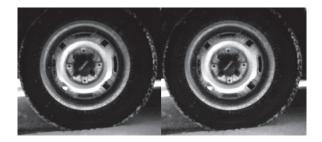

| 6.7  | Denoising using a $3 \times 3$ median filter. From left to right: I) MATLAB's 8-bit noisy                     |     |

|      | image with salt & pepper noise density 0.05, II) MATLAB's median filtered image, III)                         |     |

|      | Proposed stochastic median filter with sequence length ${\cal N}=256$ and register size $m=3$ -               |     |

|      | bits                                                                                                          | 122 |

| 6.8  | Down sampling using a $2 \times 2$ max-pooling kernel. Left: MATLAB's max pooling com-                        |     |

|      | putation for 8-bit pixel representation, Right: max pooling kernel realized using the pro-                    |     |

|      | posed compact MAX with sequence length $N=2^8$ and register size $m=4$ -bits                                  | 123 |

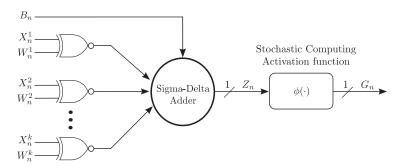

| 6.9  | SC neuron realized using the proposed SCSD adder architecture shown in Fig. 3.14.                             |     |

|      | The non-linear activation function is realized using any single-bit input/output Stochastic                   |     |

|      | Finite-State Machine.                                                                                         | 124 |

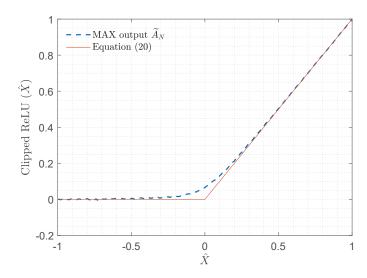

| 6.10 | Approximating the clipped ReLU of (6.3) using the Stochastic MAX architecture of Fig.                         |     |

|      | 3.5, for input values $\hat{X} \in [-1,1]$ , with $10^3$ i.i.d. runs on each input value, sequence            |     |

|      | length $N=256$ and register size $m=4$ -bits                                                                  | 125 |

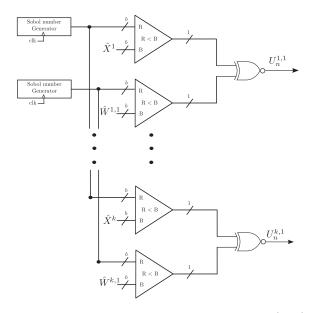

| 6.11 | Example of sequence generation in the input layer, with $\hat{X}^j$ , $\hat{W}^{j,1}$ , $j=1,\ldots,k$ corre- |     |

|      | sponding to the values of the inputs and the weights of a single neuron respectively. The                     |     |

|      | Sobol number generators are shared among the inputs and the weights respectively                              | 127 |

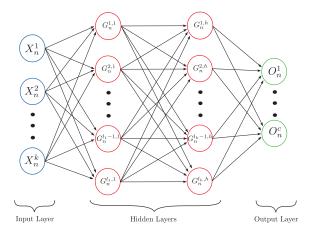

| 6.12 | Multi-Layer Perceptron network architecture. Each hidden layer is realized using the                          |     |

|      | proposed SC neuron of Fig. 6.9 containing the proposed SCSD adder architecture of Fig.                        |     |

|      |                                                                                                               | 128 |

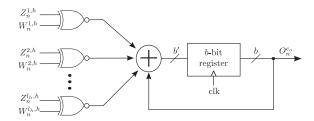

| 6.13 | A multiply-and-accumulate processing block realizing each unit $O_n^{c_o}$ existing in the out-               |     |

|      | put layer. The result is obtained after $N$ clock cycles                                                      | 128 |

# **List of Tables**

| 4.1 | Execution Times (s) for the Modeling of two SFSMs: the STanh and the Stochastic Adder 95                                                                                                                           |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5.1 | Hardware Resources Comparison between the Proposed Non-Scaling Adder and Subtracter and the State-of-the-Art in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power Consumption $(mW)$ and Energy $(pJ)$ per operation |

| 5.2 | Comparison of computational accuracy and corresponding register sizes of MAX/MIN architectures for typical sequence lengths $N$                                                                                    |

| 5.3 | Hardware Resources Comparison between the Proposed MAX/MIN and the State-of-the-Art in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power $(mW)$ and Energy $(pJ)$ Consumption per                                    |

|     | operation                                                                                                                                                                                                          |

| 5.4 | Register sizes resulting in the highest MSE based on $N$                                                                                                                                                           |

| 5.5 | Hardware Resources Comparison between the Proposed Compact MAX/MIN and the State-of-the-Art in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power $(mW)$ and Energy $(pJ)$ Con-                                       |

|     | sumption                                                                                                                                                                                                           |

| 6.1 | Accuracy and Image Quality Comparison in the Filtering with a 3×3 Convolution Kernel using the Proposed and State-of-the-Art Stochastic Adders                                                                     |

| 6.2 | Comparison of Hardware Resources for Implementing the $3\times3$ Convolution Kernel using the Proposed and State-of-the-Art Stochastic Adders in Area $(\mu m^2)$ , Critical Path $(ns)$ ,                         |

|     | Power $(mW)$ and Energy $(pJ)$ per operation                                                                                                                                                                       |

| 6.3 | Computational Accuracy & Image Quality for the Image Sharpening Filter Realized using the Proposed Architectures                                                                                                   |

| 6.4 | Comparison of Hardware Resources for the Implementation of the Image Sharpening Filter 120                                                                                                                         |

| 6.5 | Accuracy in PSNR of the realized 3 × 3 Median Filter using the Proposed Max and Min  Architectures                                                                                                                 |

| ( ( |                                                                                                                                                                                                                    |

| 6.6 | Hardware Resources for the Implementation of a $3 \times 3$ Median Filter using the Proposed MAX and MIN Architectures in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power $(mW)$ and En-                           |

|     | ergy $(pJ)$ per operation                                                                                                                                                                                          |

| 6.7 | Computational Accuracy in PSNR and SSIM of the realized $3 \times 3$ Median Filter using                                                                                                                           |

| 5.7 | the Proposed Max and Min Architectures                                                                                                                                                                             |

30 List of Tables

| 6.8  | Hardware Resources for the Implementation of a $3 \times 3$ Median Filter using the Proposed |

|------|----------------------------------------------------------------------------------------------|

|      | Compact MAX & MIN Architectures in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power $(mW)$    |

|      | and Energy $(pJ)$                                                                            |

| 6.9  | Computational Accuracy in PSNR and SSIM of the realized $2 \times 2$ Max Pooling kernel      |

|      | using the Proposed Compact MAX Architecture                                                  |

| 6.10 | Hardware Resources for the Implementation of a $2 \times 2$ Max Pooling kernel using the     |

|      | Proposed Compact MAX Architecture in Area $(\mu m^2)$ , Critical Path $(ns)$ , Power $(mW)$  |

|      | and Energy $(pJ)$                                                                            |

| 6.11 | Inference Accuracy in percentages (%) of the proposed SCSD, FxP and FP MLP realizations 12:  |

| 6.12 | Hardware resources required for the realization of a 784-input neuron                        |

| 6.13 | Performance Comparison of SC-based MLPs in inference accuracy and hardware re-               |

|      | sources efficiency for the realization of the computational units                            |

1

## Introduction

#### 1.1 Motivation and Scope

Efficient realization of digital systems in Integrated Circuits (ICs) and Field Programmable Gate Arrays (FPGAs) is of utter importance given the accelerated growth of emerging applications [75, 28, 22, 29]. The typical binary arithmetic representations used for their implementation, namely the Fixed-Point (FxP) and Floating Point (FP), can be hardware-demanding for the modern Digital Signal Processors (DSPs), especially when massive parallelization is necessary [22, 50, 12]. This is further intensified when non-linear functions are required in the processing, for instance the exponential and the hyperbolic tangent [50, 80, 76, 43]. To this end, unconventional computing paradigms are under extensive exploration [64, 10, 29, 36, 67], with Stochastic Computing being an effective approach among many [40, 28, 66, 29].