### National Technical University of Athens

# School of Electrical and Computer Engineering Division of Computer Science

Hardware and Software Co-Design for Efficient Memory Access

**Doctoral Dissertation**

**CHLOE ALVERTI**

Athens, 5 December 2022

#### Hardware and Software Co-Design for Efficient Memory Access

**Doctoral Dissertation**

#### **CHLOE ALVERTI**

| Advisors:                  | Georgios Goumas<br>Nectarios Koziris<br>Vasileios Karakostas |                     |

|----------------------------|--------------------------------------------------------------|---------------------|

| Georgios Goumas            | <br>Nectarios Koziris                                        | Vasileios Karakosta |

| Associate Professor        | Professor                                                    | Assistant Professor |

| National Technical         | National Technical                                           | University of       |

| University of Athens       | University of Athens                                         | Athens              |

|                            |                                                              |                     |

| Dionisios N. Pnevmatikatos | Dimitrios Tsoumakos                                          | Angelos Bilas       |

| Professor                  | Professor                                                    | Professor           |

| National Technical         | National Technical                                           | University of       |

| University of Athens       | University of Athens                                         | Crete               |

|                            |                                                              |                     |

|                            | Michael Swift                                                |                     |

|                            | Professor                                                    |                     |

|                            | University of Wisconsin-                                     |                     |

|                            | Madison                                                      |                     |

|                            |                                                              |                     |

Athens, 5 December 2022

| Chloe Alverti                                                                                         |

|-------------------------------------------------------------------------------------------------------|

| Διδάκτωρ Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.                                      |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

|                                                                                                       |

| Copyright © Chloe Alverti                                                                             |

| Διδάκτωρ Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π., 2022                                |

| Με επιφύλαξη παντός δικαιώματος. All rights reserved.                                                 |

| Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος       |

| αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, |

| εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να          |

| διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό       |

| πρέπει να απευθύνονται προς τον συγγραφέα.                                                            |

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

To my parents, Lena and Nikos, who have and always will be a core part of myself, my role models and an endless source of love and support.

I have been truly lucky.

Στους γονείς μου, Λένα και Νίκο, που είναι και θα είναι πάντα κομμάτι μου, μια τρομερή πηγή αγάπης και υποστήριξης. Έχω υπάρξει πολύ τυχερή.

#### Περίληψη

Η εικονική μνήμη είναι μια κρίσιμη υπολογιστική αφαίρεση που έχει αντέξει στη δοκιμασία του χρόνου. Διευκολύνει τον προγραμματισμό δημιουργώντας την ψευδαίσθηση ότι η φυσική μνήμη είναι τεράστια, γραμμική και ιδιωτική ανά διεργασία, επιτρέπει την πρόσβαση σε συσκευες Ε/Ε στο χώρο της μνήμης και βοηθά στην ευέλικτη διαχείριση πόρων. Ωστόσο, αυτές οι θεμελιώδεις ιδιότητες δεν παρέχονται δωρεάν. Η εικονική μνήμη προϋποθέτει ότι το Λειτουργικό Σύστημα (ΛΣ) δημιουργεί και διαχειρίζεται αυτήν την αφαίρεση της φυσικής μνήμης που αναγνωρίζει κάθε διεργασία, τον λεγόμενο εικονικό χώρο διευθύνσεων, και τον αντιστοιχεί σε πραγματικούς φυσικούς πόρους. Η εικονική μνήμη επίσης επιβάλλει ότι κάθε λειτουργία πρόσβασης στη μνήμη (του επεξεργαστή) περνάει από ένα βήμα μετάφρασης. Κανένας από τους παραπάνω μηχανισμούς δεν είναι φθηνός και, για την ακρίβεια, το κόστος τους συνεχώς αυξάνεται.

Υπάρχουν τέσσερις τάσεις που στρεσάρουν την απόδοση της εικονικής μνήμης σήμερα, (i) η μετεωρική άνοδος των απαιτήσεων χωρητικότητας μνήμης, (ii) η σεισμική μετατόπιση των χρηστών στη χρήση του υπολογιστικού νέφους (cloud), (iii) η ταχεία εξέλιξη των συσκευών αποθήκευσης με όρους απόδοσης και (iv) η αυξανόμενη ετερογένεια των συσκευών υπολογισμού και αποθήκευσης στα συστήματα μεγάλων δεδομένων. Οι δύο πρώτες ανεβάζουν σημαντικά τον πήχη απόδοσης της διαδικασίας μετάφρασης εικονικών διευθύνσεων σε φυσικές και οι δύο επόμενες μας προτρέπουν να ξανασκεφτούμε τη σημασιολογία και την υλοποίηση των διεπαφών της εικονικής μνήμης. Η παρούσα διατριβή συμβάλλει και προς τις δύο κατευθύνσεις.

Η εκθετική αύξηση του όγκου των παγκόσμιων δεδομένων και η αντίστοιχη αύξηση των απαιτήσεων μνήμης των εφαρμογών, οδήγησαν την κυρίαρχη υλοποίηση της εικονικής μνήμης –τη σελιδοποίηση– στο λεγόμενο Τείχος Μετάφρασης (Address Translation Wall) [53] περίπου μια δεκαετία πριν. Στην παρούσα διατριβή δείχνουμε ότι παρά το γεγονός ότι το υλικό μετάφρασης ανα επεξεργαστή τριαπλασσιάστηκε από τότε, π.χ. με την ενσωμάτωση μεγαλύτερων κρυφών μνημών αναζήτησης μετάφρασης (TLBs) η με την καλύτερη υποστήριξη των μεγάλων σελίδων, οι εφαρμογές μεγάλης έντασης δεδομένων (big data) μπορεί ακόμα να ξοδεύουν έως και το 30% του χρόνου εκτέλεσής τους στη μετάφραση

διευθύνσεων - ειδικά όταν εκτελούνται σε εικονικά περιβάλλοντα. Για την αντιμετώπιση της κακής αυτής κλιμάκωσης απόδοσης της σελιδοποίησης, η παρούσα διατριβή προτείνει συνεργιστικούς μηχανισμούς λογισμικού και υλικού που δημιουργούν και εκμεταλλεύονται την ύπαρξη γραμμικότητας στις αντιστοιχίσεις εικονικών σελίδων σε φυσικές. Στο λογισμικό, προτείνουμε την Σελιδοποίηση με επίγνωση γειτνίασης (CA paging), μια νέα τεχνική διαχείρισης μνήμης που βελτιώνει τον χειριστή σφαλμάτων σελίδας του ΛΣ με υποδείξεις για την δέσμευση κατάλληλων σελίδων για τη δημιουργία μεγάλων συνεχόμενων αντιστοιχίσεων εικονικών διευθύνσεων σε φυσικές ανά διεργασία. Η σελιδοποίηση CA εφαρμόζεται τόσο σε φυσικές όσο και σε εικονικές μηχανές και διατηρεί τις ευέλικτες τεχνικές διαχείρισης μνήμης ενός σύγχρονου ΛΣ, π.χ. τη σελιδοποίηση κατ'απαίτηση και την αντιγραφή κατά την εγγραφή (CoW), ενώ αποφεύγει κάθε είδους εκ των προτέρων δέσμευση μνήμης. Υλοποιήσαμε την σελιδοποίηση CA στο ΛΣ Linux και τη διαθέτουμε ως λογισμικό ανοικτού κώδικα. Στο υλικό, για την αξιοποίηση της παραγόμενης γραμμικότητας στις απεικονίσεις, προτείνουμε την κερδοσκοπική μετάφραση διευθύνσεων με βάση τη μετατόπιση (SpOT). Το SpOT είναι μια μικρο-αρχιτεκτονική επέκταση που εκμεταλλεύεται την υποκείμενη γραμμικότητα στις αντιστοιχίσεις για να προβλέψει τη μετάφραση διευθύνσεων σε περίπτωση αστοχίας στην ιεραρχία των κρυφών μνημών ΤΙΒ. Το SpOT μπορεί να εφαρμοστεί άμεσα και με διαφάνεια τόσο σε φυσικά όσο και σε εικονικά περιβάλλοντα - επειδή λειτουργεί εξ ολοκλήρου σε επίπεδο μικροαρχιτεκτονικής. Σε συνδυασμό με τη σελιδοποίηση CA, το SpOT μειώνει το κόστος μετάφρασης από ~16,5% σε ~0,9% κατά μέσο όρο για εφαρμογές μεγάλων δεδομένων που εκτελούνται σε εικονικές μηχανές, ανταλλάσοντας τις ισχυρές εγγυήσεις ασφάλειας (security) με εναν απλό αρχιτεκτονικό σχεδιασμό.

Η εικονική μνήμη, εκτός από προγραμματιστική αφαίρεση για τη φυσική μνήμη, είναι επίσης μια σημαντική διεπαφή για την πρόσβαση στις συσκευές εισόδου-εξόδου (Ε/Ε). Οι αντιστοιχίσεις αρχείων επιτρέπουν στις εφαρμογές να έχουν πρόσβαση σε μόνιμα δεδομένα μέσω αναφορών στη μνήμη. Ωστόσο, οι συσκευές αποθήκευσης υψηλής απόδοσης έχουν εξελιχθεί σημαντικά την τελευταία δεκαετία και στις μέρες μας προσφέρουν χρόνους απόκρισης μονοψήφιους ή ακόμα και μικρότερους του δευτερολέπτου, εκθέτοντας το λογισμικό συστήματος Ε/Ε του ΛΣ ως απαγορευτικά ακριβό. Στη παρούσα διατριβή, μελετάμε την περίπτωση συσκευών μη πτητικής μνήμης (PMem) και της διεπαφής αρχείων άμεσης πρόσβασης (DAX). Με το PMem και το DAX, η εικονική μνήμη μπορεί να απεικονίσει φυσικές διευθύνσεις αποθήκευσης μόνιμων δεδομένων απευθείας στο χώρο του χρήστη, επιτρέποντας τη πρόσβαση σε μόνιμα δεδομένα μέσω εντολών

load/store του επεξεργαστή. Ωστόσο, στη μελέτη μας διαπιστώνουμε ότι οι λειτουργίες της εικονικής μνήμης συχνά μειώνουν την απόδοση της άμεσης πρόσβασης, αποτυγχάνοντας να προσφέρουν αυτό που μπορεί να προσφέρει το υποκείμενο υλικό. Στη παρούσα διατριβή αναλύουμε όλες τις πηγές κόστους στη χρήση της μνήμης ως διεπαφής αρχείων και μελετάμε πως επηρεάζονται οι δαπανηροί μηχανισμοί της εικονικής μνήμης από νέες τεχνολογίες αποθήκευσης ή και εαν ακόμα γίνονται απαρχαιωμένοι. Με βάση την ανάλυσή μας, προτείνουμε μια νέα διεπαφή για γρήγορη και κλιμακώσιμη άμεση πρόσβαση σε μόνιμα δεδομένα (DaxVM). Το DaxVM είναι μια διεπαφή απεικόνισης αρχείων αποθηκευμένων σε μη-πτητικες μνήμες, που χαλαρώνει τη σημασιολογία POSIX, και υλοποιείται με επανασχεδιασμό των λειτουργιών της εικονικής μνήμης και με επέκταση των συστημάτων αρχείων για PMem - με όλες τις αλλαγές να καθοδηγούνται από τα μοναδικά χαρακτηριστικά της άμεσης πρόσβασης (dax). Το DaxVM υποστηρίζει (i) γρήγορες λειτουργίες αντιστοίχισης μνήμης (O(1)) μέσω μόνιμων πινάκων σελίδων ενσωματωμένων στα μεταδεδομένα του συστήματος αρχείων, (ii) τη νωχελική ακύρωση των TLB, (iii) την κλιμακώσιμη (σε πολλούς πυρήνες) διαχείριση του εικονικού χώρου διευθύνσεων για εφήμερες αντιστοιχίσεις, (iv) την εξάλειψη του κόστους δυνατότητας διαχείρισης της ανθεκτικότητας των μόνιμων δεδομένων από τον χώρο του πυρήνα όταν είναι υπεύθυνος ο χώρος χρήστη και (ν) τον ασύγχρονο μηδενισμό των μπλοκ αποθήκευσης από το σύστημα αρχείων. Υλοποιήσαμε το DaxVM στο ΛΣ Linux και στα συστήματα αρχείων ext4-DAX και NOVA και το διαθέτουμε ως λογισμικό ανοιχτού κώδικα. Το αξιολογούμε σε ένα πραγματικό σύστημα εξοπλισμένο με Intel Optane. Για εφαρμογές πολλαπλών νημάτων που επεξεργάζονται πολλά μικρά αρχεία για μικρά διαστήματα, π.χ. Apache, το DaxVM βελτιώνει την απόδοση της κλήσης συστήματος mmap έως και 4,9x. Αντιστρέφει επίσης την τάση που ευνοεί τη χρήση της κλήσης συστήματος read για τέτοιες εφαρμογές, ξεπερνώντας την έως και 1,5x. Το DaxVM αυξάνει επίσης τη διαθεσιμότητα του συστήματος, παρέχοντας γρήγορους χρόνους εκκίνησης για βάσεις δεδομένων και διατηρεί υψηλή απόδοση ακόμα και όταν οι συσκευές αποθήκευσης υποφέρουν απο εξωτερικό κατακερματισμό.

Συνοψίζοντας, η παρούσα διατριβή επανεξετάζει τη σχεδίαση και την υλοποίηση του μηχανισμού της εικονικής μνήμης στο σήμερα και προτείνει τεχνικές στο υλικό και στο λογισμικό που την επεκτείνουν ωστε να i) κλιμακώνει καλύτερα με τις συνεχώς αυξανόμενες χωρητικότητες της κύριας μνήμης μέσω ενός αποδοτικού μηχανισμού μετάφρασης διευθύνεσων και ii) προσφέρει μια ειδική διεπαφή αντιστοίχισης αρχείων που φέρνει την απόδοση στα όρια αυτού που μπορεί να παρέχει το υποκείμενο υλικό για άμεση πρόσβαση σε μόνιμα δεδομένα.

**Λέξεις κλειδιά:** εικονική μνήμη, διαχείριση φυσικής μνήμης, μη-πτητική μνήμη, συστήματα αρχείων, λειτουργικά συστήματα, αρχιτεκτονική υπολογιστών

#### **Abstract**

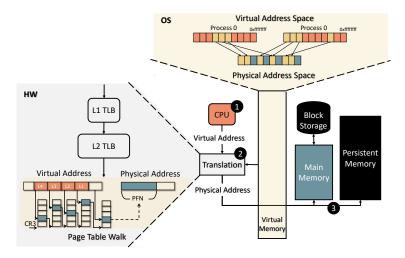

Virtual memory is a crucial computing abstraction that has stood the test of time. The level of indirection that it introduces, facilitates programming, i.e. creates the illusion that physical memory is vast, linear and private per application or enables the access of I/O devices in memory space, and assists agile resource management. However these fundamental properties do not come for free. Virtual memory assumes that the Operating System (OS) must maintain the abstraction of memory that each process acknowledges, the virtual address space indirection, and map it to actual physical resources. It also assumes that each CPU memory access operation must go through a translation step. None of the above mechanisms is cheap and, if anything, their costs are getting more and more profound.

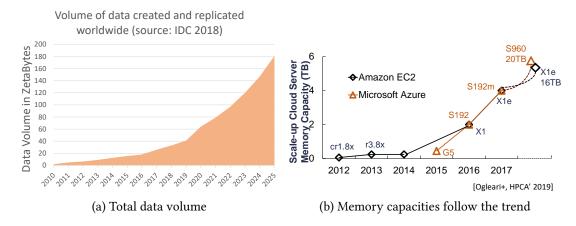

There are four trends that stress the performance of virtual memory today, (i) the meteoric rise in memory demands and capacities, (ii) the seismic shift of users from enterprise data centers to the cloud, (iii) the rapid evolution of high-performance storage devices and (iv) the increasing heterogeneity in both the compute and the store landscape of data-center systems. The first two considerably raise the efficiency bar for address translation and the second two urge us to re-visit the legacy virtual memory interfaces semantics and consecutively their design. This thesis contributes in both directions.

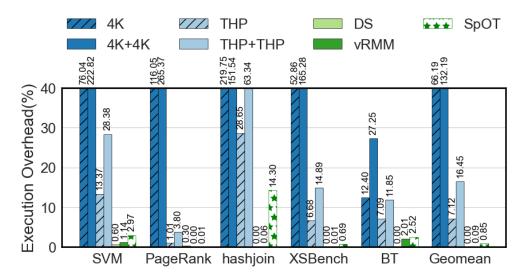

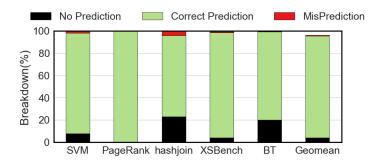

The exponential growth of global data and the corresponding increase in the memory demands of workloads led virtual memory's dominant implementation – paging – hit the Address Translation Wall [53] almost a decade ago. In this thesis we show that despite the fact that vendors tripled translation hardware budget since then, e.g. by incorporating larger TLBs and MMU caches or better huge page support, memory-intensive workloads can still spend up to 30% of their execution time in address translation – especially when they run in virtualized environments. To deal with paging's poor performance scaling, this thesis proposes synergistic software and hardware mechanisms that create and exploit linearity in mappings. We propose *Contiguity-Aware (CA) paging*, a novel memory management technique that enhances the Operating System's page fault handler with hints to allocate target pages and create vast contiguous virtual-to-physical mappings per process. CA paging is applicable to both native and nested paging and it maintains all lightweight

memory management techniques of a modern OS, i.e demand paging, Copy-On-Write etc, while avoiding any memory reservation or pre-allocation. We implement our proposal in stock Linux and make it publicly available. On the hardware side, to harvest the generated contiguity, we propose Speculative Offset Address Translation (SpOT). SpOT is a micro-architecture engine that exploits the underlying linearity in mappings to predict address translation on the TLB miss path. While most state-of-the-art hardware proposals fail to support virtualization, due to the architectural complexity of tracking and caching arbitrarily sized mappings in two-dimensional execution, SpOT is directly and transparently applicable to both native and virtualized environments – because it works entirely on the micro-architecture level. Combined with CA paging, SpOT reduces the translation overheads of nested paging from  $\sim 16.5\%$  to  $\sim 0.9\%$  on average for memory-intensive workloads, in a design that trades architectural complexity with strong security guarantees.

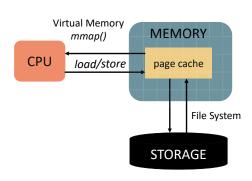

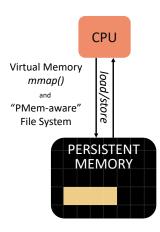

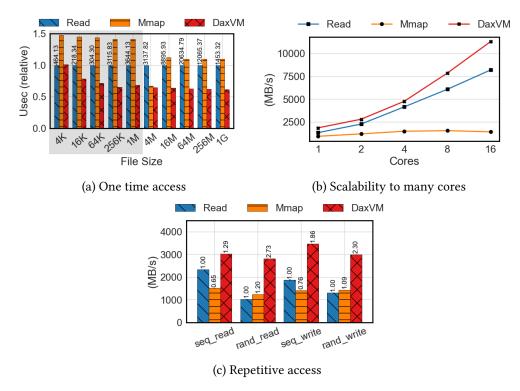

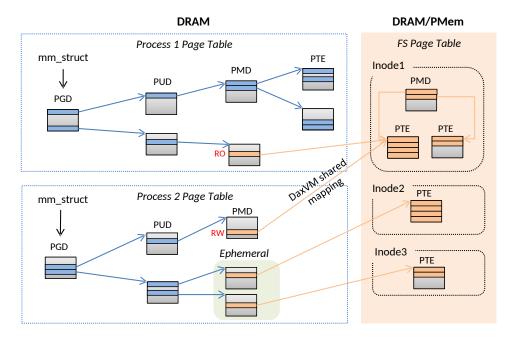

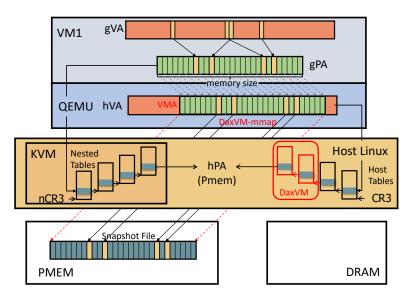

Apart from a physical memory abstraction, virtual memory is also an important interface towards IO devices; file mappings allow applications to access persistent data via memory dereference. However, high-performance storage has evolved significantly the past decade and nowadays devices offer single digit or even sub- microsecond latencies, exposing the kernel software IO stack as a prohibitively expensive data path. In this thesis, we study the case of persistent memory (PMem) and the direct access file interface (DAX). With PMem and DAX, virtual memory can map storage locations directly to user-space, enabling persistent data access via CPU load/store instructions; forming the shortest existing path to storage. Yet in our study we find that virtual memory operations often throttle direct access performance, failing to deliver what the underlying hardware can provide. In this thesis we break down all sources of overhead in using memory as a file interface. We study how the expensive mechanisms of virtual memory are affected by the new fast storage technology or if they even become obsolete. Based on our analysis, we propose a new interface for fast and scalable direct access to persistent data. DaxVM is a POSIX-relaxed file mapping interface for persistent memory, implemented by redesigning virtual memory operations and extending PMem-aware file systems all changes driven by direct access unique characteristics. DaxVM supports (i) O(1) memory mapping operations via persistent page tables integrated in file system's inode metadata, (ii) lazy invalidation of the TLBs, (iii) scalable address space management for ephemeral mappings, (iv) elimination of kernel-space durability management support when user-space is in charge and (v) asynchronous storage block pre-zeroing by the file system to accelerate DAX append operations. We implement DaxVM in stock Linux and the ext4-DAX and NOVA file systems and make it publicly available. We evaluate it on a real system equipped with Intel Optane. For multi-threaded workloads that process multiple small files for short intervals, e.g., Apache, DaxVM improves standard mmap performance up to 4.9x. It also reverses the trend that favors read for such setups, outperforming it by up to 1.5x. DaxVM also increases system availability, providing fast boot times for PMem databases, and sustains high throughput even when they run on fragmented file system images.

Overall, this thesis revisits today's virtual memory design and proposes hardware and software techniques that extend it to (i) scale better with the ever increasing memory capacities, through efficient address translation, and (ii) form a dedicated file mapping interface to push performance to the limits of what the underlying hardware can provide for direct access to persistent data.

**Keywords:** virtual memory, memory management, address translation, persistent memory, file systems, operating systems, computer architecture

### Ευχαριστίες

Η παρούσα εργασία είναι το απτό, τελικό αποτέλεσμα των διδακτορικών σπουδών μου των τελευταίων 5μιση ετών στο Εργαστήριο Υπολογιστικών Συστημάτων (CSLab) της Σχολής Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου. Στην ουσία όμως ειναι το αποτέλεσμα μιας πολύ μεγαλύτερης περιόδου η οποία ξεκινάει από το ίδιο ακριβώς εργαστήριο το 2014. Ολοκληρώνοντας αυτό το -τόσο σημαντικό για μένα - ταξίδι θα ήθελα να επιχειρήσω τη μερική καταγραφή του και κυρίως να ευχαριστήσω όλους τους ανθρώπους που συνάντησα στην πορεία του. Ο καθένας με το διακριτό του ρόλο με ενέπνευσε, με στήριξε και τελικά καθόρισε την πορεία της εργασίας μου. Δημιουργήθηκαν έτσι ισχυροί δεσμοί και σχέσεις ζωής που αποτελούν τελικά το σημαντικότερο επίτευγμα και όλη την ουσία. Ευχαριστώ λοιπόν από τα βάθη της καρδιάς μου:

#### • ..τους επιβλέποντες και τα μέλη της επιτροπής μου

#### Γεώργιο Γκούμα (επιβλέποντα καθηγητή)

Τον γνώρισα στο τέλος των προπτυχιακών μου σπουδών, το 2014, όταν εργάστηκα μαζί του στη διπλωματική μου εργασία στο CSLab. Του χρωστώ λοιπόν, πριν από όλα, την πρώτη μου επαφή με την ερευνητική διαδικασία και τον πρώτο ενθουσιασμό για το καινούργιο αυτό για μένα -τότε- σύμπαν. Μου έδειξε εμπιστοσύνη και έκτοτε η υποστήριξή του ήταν συνεχής σε όλα τα επίπεδα. Με το πέρας των προπτυχιακών μου σπουδών, με ενεθάρρυνε να ακολουθήσω διδακτορικές σπουδές, όπως ήθελα, και γράφτηκα ως ΥΔ στο εργαστήριο μας. Με παρότρυνε στην εμβόλιμη επιθυμία και επιλογή μου να φύγω για μερικά χρόνια στη Σουηδία και να εργαστώ ως ερευνητικό προσωπικό. Το 2017, ενίσχυσε την απόφασή μου να επιστρέψω και να ξεκινήσω τη διατριβή μου. Τα τελευταία 5μιση χρόνια έχει σταθεί

στο πλάι μου σε κάθε μου ερευνητική προσπάθεια και μου έχει χαρίσει απλόχερη ελευθερία, δίνοντάς μου μεταξύ άλλων και το χώρο να εξερευνήσω ερευνητικά μονοπάτια τα οποία δεν ήταν απαραίτητα εντός των άμεσων ερευνητικών του ενδιαφερόντων. Πέρα όμως από την συνεργασία και επίβλεψη, είμαι ευγνώμων, γιατί βρέθηκε κοντά μου και ως άνθρωπος. Δεν με πίεσε ποτέ, προσπάθησε πάντα να με καταλάβει και να με γνωρίσει, στάθηκε πάντα με διάθεση φροντίδας απέναντι σε κάθε δυσκολία. Έτσι μέσα στα χρόνια, έχει δημιουργηθεί ένας ισχυρός δεσμός –με όλη την ιδιαιτερότητα και μαγεία που έχει πάντα η σχέση δάσκαλου και μαθητή – ο οποίος εύχομαι να κρατήσει για πολύ, πολύ καιρό ακόμα.

#### - Βασίλειο Καρακώστα (συν-επιβλέποντα),

μεταδιδακτορικό ερευνητή στο εργαστήριο μας κατά τη διάρκεια των διδακτορικών σπουδών μου και καθηγητή σήμερα στο ΕΚΠΑ. Ο Βασίλης είναι από τους πιο σημαντικούς ανθρώπους αυτής της περιόδου. Συν-επέβλεψε το διδακτορικό μου και συνεργαστήκαμε πολύ στενά από τη πρώτη κιόλας μέρα, δουλεύοντας σε μια ερευνητική κατεύθυνση που προέκυψε από τη δική του ερευνητική εμπειρία. Κάθε εργασία, κάθε βήμα του διδακτορικού μου το κάναμε μαζί και αυτό είχε δύο εξίσου σημαντικά αποτελέσματα. Πρώτον, χάρη στο Βασίλη και την καθοδήγησή του έμαθα πάρα πολλά και απέκτησα δεξιότητες τόσο τεχνικές όσο και μεθοδολογικές για τη σωστή διεξαγωγή της έρευνας – γνώσεις πολύτιμες που θα με συντροφεύουν για πάντα. Δεύτερον, χάρη (και) στο Βασίλη ,το διδακτορικό μου έγινε μια φοβερά διασκεδαστική και ενθουσιώδης εμπειρία, καθώς μαζί του μοιράστηκα κάθε στιγμή της. Πάντα με θετική στάση απέναντι στα πράγματα, ακόμα και στις αναποδιές, με έναν πηγαίο ενθουσιασμό για την έρευνα, με μόνιμο ενδιαφέρον ο συνεργάτης του να τα καταφέρει, χωρίς να πιέζει και χωρίς να απαιτεί, με τεράστια υπομονή και επιμονή, με μια μόνιμη παρακίνηση και προτροπή για νέους και υψηλότερους στόχους, ήταν ο καλύτερος συνοδοιπόρος που θα μπορούσε κανείς να έχει. Η σχέση μας έγινε με τα χρόνια προσωπική. Με έχει ζήσει στις θετικές και στις αρνητικές διαθέσεις μου, έχει υπομείνει το άγχος και την ένταση μου, με έχει στηρίξει στις αναποδιές και στις προσωπικές ανηφόρες, έχει ξενυχτήσει μαζί μου σε κάθε προθεσμία.... Έτσι, πέρα από την εξαιρετική συνεργασία ,που ελπίζω να συνεχιστεί, νιώθω ότι έκανα και έναν φίλο ζωής. Ανυπομονώ, λοιπόν, για τα επόμενα.

#### - Νεκτάριο Κοζύρη (καθηγητή ΕΜΠ),

ο οποίος με την αγάπη του και το ενδιαφέρον του για την επιστήμη των υπολογιστών και τη σύγχρονη έρευνα φρόντισε να έχουμε πάντα στη διάθεση μας εξοπλισμό αιχμής – κάτι που έδρασε ως καταλύτης και για τη δική μου ερευνητική εργασία. Στις πολύτιμες συμβουλές του έχω ανατρέξει πολλές φορές όλα αυτά τα χρόνια, τόσο για τη δουλειά μου, όσο και για κάθε σημαντική επαγγελματική απόφαση που χρειάστηκε να πάρω.

#### - Διονύσιο Πνευματικάτο (καθηγητή ΕΜΠ),

τόσο για τα πολύτιμα σχόλιά του για τη διατριβή μου όσο και για τις επαγγελματικές του συμβουλές τις οποίες έχω επίσης πολλάκις ζητήσει.

- Δημήτριο Τσουμάκο και Άγγελο Μπίλα (καθηγητές ΕΜΠ και Πανεπιστημίου Κρήτης),

για το χρόνο τους και τα πολύτιμα σχόλιά τους ως μέλη της επταμελούς επιτροπής μου.

- τον Michael Swift (καθηγητής UWM),

από το University of Wisconsin-Madison (UWM) και τελευταίο μέλος της επιτροπής μου. Ο κύριος Swift εξελίχθηκε σε έναν άνθρωπο εξαιρετικής σημασίας για τη διατριβή μου και όχι μόνο. Το 2019 επισκέφθηκα για 3 μήνες το UWM για να δουλέψω μαζί του, μέσω μιας ευρωπαϊκής υποτροφίας (HiPEAC). Αυτό το ταξίδι στην Αμερική είναι μια από τις πιο ζωντανές και έντονες εμπειρίες του διδακτορικού μου. Έμαθα πολλά, ήρθα σε επαφή με πολλούς ερευνητές, διεύρυνα τους ερευνητικούς μου ορίζοντες και ξεκίνησα κάτι τελείως καινούργιο (μια νέα εργασία) στο πλαίσιο της διατριβής μου. Τότε ξεκίνησε μια μακρά συνεργασία, η οποία κράτησε για πάνω από δύο χρόνια και συνεχίζεται μέχρι και σήμερα. Υπό την καθοδήγηση του κ. Swift έμαθα πολλά για τη μέθοδο, την επιμονή, την υπομονή, τη λεπτομέρεια και την εμβάθυνση που απαιτεί η ερευνητική διαδικασία και αυτή η εμπειρία είναι ένα από τα πολυτιμότερα «εργαλεία» που απέκτησα τα χρόνια του διδακτορικού μου. Πέρα από την τεχνική και μεθοδολογική του καθοδήγηση, δεν θα ξεχάσω ποτέ την ευγένεια και την καλοσύνη του. Μέσα στις αντιξοότητες της πανδημίας και παρά την εξ αποστάσεως συνεργασία, η υποστήριξη του ήταν μεγάλη σε όλα τα επίπεδα. Με συγκίνησε και με τίμησε, ιδιαίτερα, που παρευρέθηκε δια ζώσης στην στην υποστήριξη της διατριβής μου.

#### • ...τους πολύτιμους στενούς συνεργάτες

#### - Στράτο Ψωμαδάκη,

ΥΔ στο εργαστήριο μας, κυρίως όμως ξεχωριστό και πολύ αγαπημένο άνθρωπο. Συνεργαστήκαμε πολύ στενά όλα τα χρόνια του διδακτορικού μου και είναι κι αυτός ένας από τους πολυτιμότερους ανθρώπους αυτής της περιόδου. Του οφείλω ειλικρινά πάρα πολλά. Πέρα από τις κοινές μας δουλειές, κάθε ιδέα μου τη συζήτησα μαζί του, σε κάθε τεχνική απορία/δυσκολία μου έτρεχα να με σώσει. Αλλά δεν είναι μόνο η συνεργασία και η πρακτική βοήθεια στην ερευνητική δουλειά, ο Στράτος υπήρξε πάνω και πέρα από όλα ένα τεράστιο ψυχολογικό στήριγμα. Σε κάθε απογοήτευση, κάθε ματαίωση, κάθε αναποδιά, που μοιραία ειναι μέρος μιας διατριβής, ο Στράτος με βοήθησε πολύ να ξανασταθώ όρθια. Επίσης ήταν και είναι έμπνευση. Η οξυδέρκειά του και η βαθειά γνώση του για το αντικείμενο μας, με κάνει πάντα να ενθουσιάζομαι και να κινητοποιούμαι. Τον ευχαριστώ απο καρδιάς για όλα.

#### - Κωσταντίνο Νίκα,

μεταδιδακτορικό ερευνητή στο εργαστήριο μας, με τον οποίο συνεργάστηκα στενά τόσο στο πλαίσιο της διατριβής, όσο και στα χρόνια των προπτυχιακών μου σπουδών για τη διπλωματική μου εργασία.

#### - Jayneel Gandhi,

ερευνητή στη Meta και στενό συνεργάτη των τελευταίων χρόνων. Πέρα από τη συνεργασία, θα ήθελα να τον ευχαριστήσω θερμά και για την ξεχωριστή ευκαιρία για πρακτική εργασία στην ομάδα του, τότε, στη Vmware Research, η οποία δυστυχώς δεν πραγματοποιήθηκε ποτέ λόγω της πανδημίας...

#### Χρήστο Κατσακιώρη,

ΥΔ στο εργαστήριο μας, με τον οποίο συνεργαστήκαμε στενά στο τέλος του διδακτορικού μου. Η εμπιστοσύνη που μου έδειξε και δείχνει με τιμά και με κινητοποιεί. Έμαθα πολλά από τον ίδιο, τεχνικά και μεθοδολογικά για το αντικείμενο μας, και ελπίζω να συνεχίσουμε να δουλεύουμε μαζι!

#### τον Sujay Yadalam,,

ΥΔ στο University of Wisconsin-Madison, με τον οποίο επίσης συνεργαστήκαμε τον τελευταίο χρόνο και είναι το προσωπικό μου βιωματικό παράδειγμα ότι στην έρευνα η απόσταση εκμηδενίζεται! Με έμαθε πολλά για τη πειραματική διαδικασία και η όρεξή του για τη δουλειά μου υπενθύμιζε πάντα ότι υπάρχει χαρά σε ό,τι κάνουμε. Του εύχομαι τα καλύτερα.

- τους προπτυχιακούς φοιτητές που έκαναν τη διπλωματική τους με την ομάδα μας, τον Παναγιώτη Μπάκο, τον Θωμά Τσαπράλη, τον Ιάσονα Μαρμάνη, την Ελένη Μιχαλάκη, τον Βασίλη Πολίτη, τον Χρήστο Λούρα και τον Φίλιππο Τόφαλο. Η συνεργασία με τον καθένα ήταν εξαιρετική και έμαθα κι εγώ πολλά -τεχνικά και μεθοδολογικά- που ήταν πολύτιμα για το διδακτορικό μου!

#### • ...τους αγαπημένους συνάδελφους του εργαστηρίου μας

Τη Νικέλα Παπαδοπούλου με την οποία καταλήξαμε να έχουμε γειτονικά γραφεία στο εργαστήριο μας, αλλά η φιλία μας ξεκινά από πολύ πιο πριν. Είναι από τους σημαντικότερους ανθρώπους στη ζωή μου και ανεκτίμητη συνάδελφος και συνεργάτης. Τον Δημήτρη Σιακαβάρα, τον οποίο γνώρισα στο εργαστήριο και εξελίχθηκε σε πολύτιμο φίλο – μια από τις μεγαλύτερες χαρές αυτών των χρόνων. Από τους ευγενέστερους και δοτικότερους ανθρώπους που έχω τη τύχη να ξέρω – μόνιμο στήριγμα για καθε ΥΔ στο εργαστήριο μας ως admin. Τον Κωστή Παπαζαφειρόπουλο, ο οποίος είναι πρώτα από όλα παλιός φίλος και δευτερευόντως συνάδελφος. Στα 15 χρόνια που τον γνωρίζω έχω μοιραστεί κάθε χαρά και κάθε λύπη μου μαζί του και σκοπεύω να συνεχίσω. Τον Ορέστη Λάγκα Νικολό, τον οποίο γνωρίζω από παλιά και στα

χρόνια του διδακτορικού μας μοιραστήκαμε σκέψεις και ανησυχίες –επαγγελματικές και μητόσο που τον θεωρώ φίλο ζωής. Τον Παναγιώτη Μπάκο, ο οποίος εκτός από εξαιρετικός και υποστηρικτικός συνεργάτης, είναι και απίστευτος άνθρωπος. Νιώθω τυχερή που τον γνώρισα και ανυπομονώ για τα επόμενα. Τον Ανδρέα Μπινίσκο, ο οποίος είναι αγαπημένος συνάδελφος, φίλος και σημείο αναφοράς για όλους μας. Τον Γιάννη Παπαδάκη, όπου εκτός των άλλων του χρωστάω –μαζί με τον Χρήστο και τον Παναγιώτη – ότι πέρασα τα περισσότερα μαθήματα του διδακτορικού! Την Ιωάννα Αλιφιεράκη, με την οποία γνωριστήκαμε κάνοντας τη διπλωματική μας εργασία και είναι κι αυτή μέλος αυτής της ισχυρής παρέας/οικογένειας. Τον Στέφανο Γεράγγελο και την Αθηνά Ελαφρού, που μοιραστήκαμε για χρόνια το ίδιο γραφείο και με βοήθησαν στη διατριβή μου. Τέλος, θέλω να ευχαριστήσω απο καρδιάς και όλους τους υπόλοιπους ΥΔ και συνάδελφους του εργαστηρίου μας, χάρη στους οποίους τα χρόνια της διατριβής ήταν τόσο όμορφα.

#### • ...τους συναδέλφους από τη Σουηδία

Τον καθηγητή Per Stenstrom, ο οποίος με μεγάλη φροντίδα επέβλεψε και καθοδήγησε την ερευνητική μου εργασία το διάστημα 2015-2017 στο Chalmers University of Technology της Σουηδίας. Αυτή η εμπειρία ήταν καταλύτης για την μετέπειτα επαγγελματική και όχι μόνο ζωή μου. Με γέμισε ενθουσιασμό για την έρευνα, με δίδαξε και επέκτεινε τους ακαδημαικούς μου ορίζοντες. Έμμεσα είναι κι αυτός κομμάτι αυτής της διατριβής, καθώς εκείνα τα χρόνια έθεσε πολύ ισχυρά θεμέλια.

Τον Άγγελο Αρελάκη και τον Γιάννη Νικολακόπουλο με τους οποίους συνεργάστηκα στενά και απέκτησα γνώσεις πολύτιμες για τη παρούσα διατριβή. Τον Πέτρο Βουδούρη, με τον οποίο μοιράστηκα αυτή την μοναδική εμπειρία των χρόνων στη Σουηδία (επαγγελματική και μη) και ήταν, είναι και θα είναι για μένα κάτι σαν οικογένεια (ακόμα και αν χανόμαστε). Τον Paul Renaud Goud, τον Aras Atalar, τον Ivan Walulya καθώς και κάθε άλλο φίλο που έκανα εκεί και θα θυμάμαι για πάντα.

#### • ...τους φίλους και την οικογένεια μου

τον Νίκο, τη Βάλια, την Έλλη, τον Λούζα, τον Παναγιώτη, τον Δημήτρη, τον Γιάννη, την Ελεάννα, την Κατερίνα, τον Άρη, την Κατερίνα, τη Σεμέλη, τον Λάμπρο, τη Χριστίνα, την Ιωάννα και όλους τους ανθρώπους που με άντεξαν (και) τα χρόνια του διδακτορικού και το πέρασαν όλο αυτό μαζί μου. Είμαι πολύ τυχερή που τους έχω στη ζωή μου και είναι για μένα η πιο ισχυρή πηγή χαράς και το κίνητρο μου να συνεχίζω. Τα παιδιά που δουλεύουν στον Ταρτούφο, το συνοικιακό μαγαζί των Ιλισίων, όπου κυριολεκτικά περάσαμε αμέτρητες ώρες με συνάδελφους και μη, φιλοσοφώντας επί παντώς επιστητού. Τον ξάδερφο μου Πέτρο και την Ευαγγελία, που είναι για μένα πηγή έμπνευσης και τεράστο στήριγμα. Το θείο μου που είναι πάντα εκεί για μένα. Τους γονείς μου στους οποίους χρωστάω τα πάντα.

Μέχρι τώρα στη ζωή οι άνθρωποι, με τους οποίους έχω δουλέψει στενά, έχουν αποδειχθεί υπέροχοι. Αυτό ήταν και είναι η μεγαλύτερη μου τύχη.

## Contents

| 1 | Łκτ  | εταμεν  | η περιληψη στην ελληνικη γλωσσα                                     | 1  |

|---|------|---------|---------------------------------------------------------------------|----|

|   | 1.1  | Σελιδο  | οποιημένη εικονική μνήμη                                            | 2  |

|   |      | 1.1.1   | Λειτουργικό Σύστημα                                                 | 2  |

|   |      | 1.1.2   | Υποστήριξη στην αρχιτεκτονική για τη μετάφραση διευθύνσεων          | 4  |

|   | 1.2  | Κίνητ   | ρο εργασίας                                                         | 5  |

|   |      | 1.2.1   | Μετεωρική αύξηση της ζήτησης μνήμης                                 | 5  |

|   |      |         | 1.2.1.1 Επέκταση μνήμης μέσω του διαύλου/πρωτοκόλλου CXL            | 6  |

|   |      |         | 1.2.1.2 Σελιδοποίηση 5 επιπέδων                                     | 7  |

|   |      | 1.2.2   | Κυριαρχία της εικονικοποίησης                                       | 7  |

|   |      | 1.2.3   | Η σύγχρονη ιεραρχία συσκευών αποθήκευσης και η άμεση πρόσβαση       |    |

|   |      |         | (direct access) σε μόνιμα δεδομένα                                  | 8  |

|   |      | 1.2.4   | Μια κοινή διεπαφή σε έναν ταχέως αναπτυσσόμενο και ετερογενή υπολο- |    |

|   |      |         | γιστικό χάρτη                                                       | 10 |

|   | 1.3  | Ορισμ   | ός του ερευνητικού προβλήματος                                      | 11 |

|   | 1.4  | Ερευν   | ητικές προτάσεις                                                    | 12 |

|   |      | 1.4.1   | Αποτελεσματική εικονικοποίηση της μνήμης μέσω συνεχόμενων αντιστοι- |    |

|   |      |         | χίσεων/απεικονίσεων                                                 | 13 |

|   |      | 1.4.2   | Στρεσάροντας τα όρια της μνήμης ως διεπαφής για την πρόσβαση σε     |    |

|   |      |         | αρχεία                                                              | 14 |

| 2 | Intr | oductio | on                                                                  | 1  |

|   | 2.1  | Paged   | Virtual Memory                                                      | 2  |

Contents xix

|   |      | 2.1.1            | Operating system                                                          | 2        |

|---|------|------------------|---------------------------------------------------------------------------|----------|

|   |      | 2.1.2            | Architectural support for address translation                             | 3        |

|   | 2.2  | Motiva           | ation                                                                     | 4        |

|   |      | 2.2.1            | Meteoric rise in memory demand                                            | 4        |

|   |      |                  | 2.2.1.1 Memory expansion via CXL                                          | 6        |

|   |      |                  | 2.2.1.2 5-level paging                                                    | 6        |

|   |      | 2.2.2            | Virtualization dominance                                                  | 7        |

|   |      | 2.2.3            | The evolving storage stack and direct access to persistent data           | 7        |

|   |      | 2.2.4            | A common interface in a rapidly growing heterogeneous world               | 10       |

|   | 2.3  | Proble           | m Statement                                                               | 11       |

|   | 2.4  | Propos           | sals                                                                      | 12       |

|   |      | 2.4.1            | Efficient Memory Virtualization via Contiguous Mappings                   | 12       |

|   |      | 2.4.2            | Stressing the Limits of Memory as a File Interface                        | 13       |

|   | 2.5  | Thesis           | Organization                                                              | 14       |

| 2 | Daal | l                |                                                                           | 16       |

| 3 |      | kgroun<br>The Wi |                                                                           | 16       |

|   | 3.1  |                  | rtual Memory Abstraction                                                  | 16       |

|   | 3.2  | 3.2.1            | g and Address Translation                                                 | 17       |

|   |      |                  |                                                                           | 18<br>22 |

|   |      | 3.2.2            | Contiguity in mappings can be exploited to accelerate address translation | 22<br>25 |

|   |      | 3.2.3            | Support for virtual machines                                              | 25<br>26 |

|   | 3.3  | 3.2.4            | Address Translation Coherence                                             | 26<br>27 |

|   | 3.3  |                  | le of the Operating System                                                | 27       |

|   |      | 3.3.1<br>3.3.2   | Virtual Address Space management                                          | 30       |

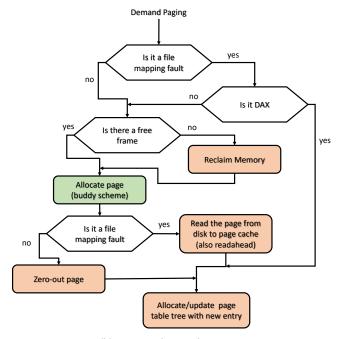

|   |      | 3.3.3            | The Page Fault Handler and Demand Paging I                                | 32       |

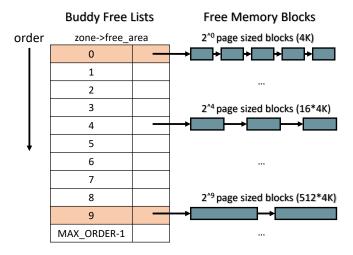

|   |      | 3.3.4            | Physical Memory Allocation and Contiguity                                 | 34       |

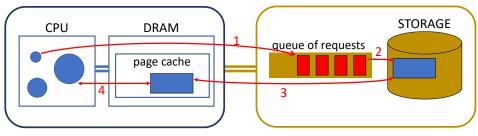

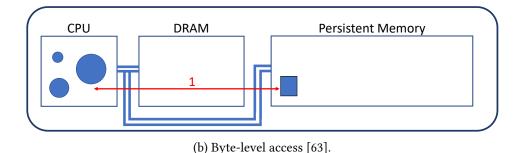

|   |      | 3.3.4            | Virtual Memory as a File Interface                                        | 35       |

|   |      |                  | 3.3.4.2 The Page Fault Handler and Demand Paging II                       | 35       |

|   |      |                  | 3.3.4.3 PMem-aware kernel file systems                                    | 36       |

|   |      |                  | •                                                                         | 36       |

|   |      |                  |                                                                           | 36<br>37 |

|   |      |                  | 3.3.4.5 User-space durability management                                  | 37       |

|   |      |                  | J.J.4.0 Oser-space me systems                                             | 3/       |

| 4 | Enh  | ancing           | and Exploiting Contiguity for Fast Memory Virtualization                  | 39       |

|   | 4.1  | Overv            | iew                                                                       | 39       |

|   | 4.2  | Softwa           | are Technique: Contiguity-aware Paging                                    | 42       |

XX Contents

|   |      | 4.2.1    | Key design concepts                                               |

|---|------|----------|-------------------------------------------------------------------|

|   |      | 4.2.2    | CA paging overview                                                |

|   |      | 4.2.3    | CA paging Mechanism                                               |

|   |      |          | 4.2.3.1 Virtualized execution                                     |

|   | 4.3  | Hardw    | vare Techniques: vRMM and SpOT                                    |

|   |      | 4.3.1    | Virtualized Redundant Memory Mappings                             |

|   |      |          | 4.3.1.1 vRMM overview                                             |

|   |      |          | 4.3.1.2 Nested Range Walk                                         |

|   |      |          | 4.3.1.3 vRMM design requires complex and redundant virtualization |

|   |      |          | extensions                                                        |

|   |      | 4.3.2    | Speculative Offset-based Address Translation                      |

|   |      |          | 4.3.2.1 SpOT Overview                                             |

|   |      |          | 4.3.2.2 SpOT Mechanism                                            |

|   | 4.4  | Discus   | sion                                                              |

|   |      |          | 4.4.0.1 SpoT Security Considerations                              |

|   |      |          | 4.4.0.2 CA paging Considerations                                  |

|   | 4.5  | Evalua   | tion 59                                                           |

|   |      | 4.5.1    | Results                                                           |

|   |      |          | 4.5.1.1 Software Results: Contiguity-aware Paging                 |

|   |      |          | 4.5.1.2 Hardware Results: vRMM and SpOT 66                        |

|   | 4.6  | Relate   | d Work                                                            |

| 5 | Stre | ssing tl | ne Limits of Memory as a File Interface 72                        |

|   | 5.1  | Overv    | iew                                                               |

|   | 5.2  | Backg    | round                                                             |

|   | 5.3  | Memo     | ry as File Interface                                              |

|   |      | 5.3.1    | Virtual Memory Overheads                                          |

|   |      |          | 5.3.1.1 Paging                                                    |

|   |      |          | 5.3.1.2 Virtual address space management                          |

|   |      |          | 5.3.1.3 Synchronous resource release                              |

|   |      |          | 5.3.1.4 Dirty page tracking for file syncing                      |

|   |      | 5.3.2    | Double writing for secure appends                                 |

|   |      | 5.3.3    | Micro-architectural performance                                   |

|   | 5.4  | DaxVN    | M                                                                 |

|   |      | 5.4.1    | O(1) mmap                                                         |

|   |      |          | 5.4.1.1 Pre-populated File Tables                                 |

|   |      |          | 5.4.1.2 Fast table (de)attachment                                 |

Contents xxi

|   |     |         | 5.4.1.3 Virtualization                                        | 86  |

|---|-----|---------|---------------------------------------------------------------|-----|

|   |     | 5.4.2   | Ephemeral mappings                                            | 86  |

|   |     | 5.4.3   | Optimized munmap                                              | 88  |

|   |     | 5.4.4   | Durability management                                         | 89  |

|   |     | 5.4.5   | Asynchronous block pre-zeroing                                | 89  |

|   |     | 5.4.6   | DaxVM forms a new relaxed interface                           | 90  |

|   |     | 5.4.7   | Discussion and summary                                        | 91  |

|   | 5.5 | Evalua  | tion                                                          | 92  |

|   |     | 5.5.1   | Experimental Setup                                            | 92  |

|   |     | 5.5.2   | Micro-benchmarks                                              | 92  |

|   |     | 5.5.3   | Real-world Applications                                       | 96  |

|   |     |         | 5.5.3.1 Small files and ephemeral access                      | 96  |

|   |     |         | 5.5.3.2 Large files and long-lived mappings                   | 99  |

|   |     | 5.5.4   | Summary                                                       | 102 |

|   | 5.6 | Discus  | sion: DaxVM beyond persistent memory                          | 103 |

|   |     | 5.6.1   | O(1) mmap and file tables                                     | 103 |

|   |     | 5.6.2   | Address Space Scalability                                     | 104 |

|   | 5.7 | Related | d Work                                                        | 104 |

|   |     |         |                                                               |     |

| 6 | Con | clusion | as I                                                          | 106 |

|   | 6.1 | Summa   | ary                                                           | 106 |

|   | 6.2 | Future  | Research Directions                                           | 107 |

|   |     | 6.2.1   | Address translation and Non-Uniform Memory Access performance | 108 |

|   |     | 6.2.2   | Efficient multiple page size support                          | 108 |

|   |     |         | 6.2.2.1 The case of ARMv8                                     | 109 |

|   |     | 6.2.3   | Virtual machine snapshotting                                  | 109 |

|   |     | 6.2.4   | Fast user-space access to low-latency SSDs                    | 110 |

# List of Figures

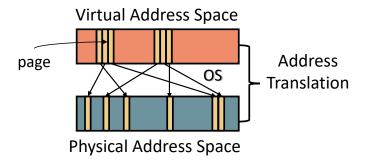

| 2.1 | Virtual Memory Overview                                                             | 2  |

|-----|-------------------------------------------------------------------------------------|----|

| 2.2 | Buffered File Mappings                                                              | 3  |

| 2.3 | Meteoric rise in memory demands                                                     | 5  |

|     | 2.3a Total data volume                                                              | 5  |

|     | 2.3b Memory capacities follow the trend                                             | 5  |

| 2.4 | Intel processors paging and TLB reach evolution                                     | 5  |

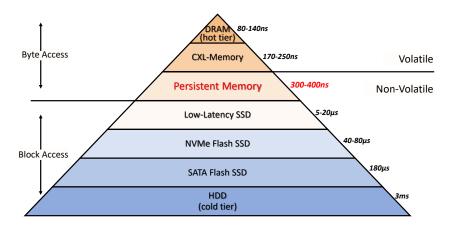

| 2.5 | Today's multiple tiers of store [132, 156, 218]                                     | 8  |

| 2.6 | Direct Access                                                                       | 8  |

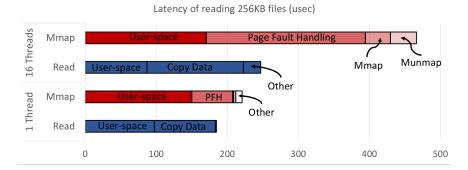

| 2.7 | Average latency of accessing once 256KB files. The reported latency if for a single |    |

|     | file. Direct access performs worse than syscalls (e.g. read) despite avoiding data  |    |

|     | copies. This is due to expensive virtual memory operations. We measure this on      |    |

|     | a machine with 384GB Intel Optane 5.5.1 and use bpftrace [108] to track average     |    |

|     | latency                                                                             | 9  |

| 2.8 | A common interface in a heterogeneous coherent world                                | 10 |

| 3.1 | Paged Virtual Memory.                                                               | 18 |

| 3.2 | The multi-level organization of the page table in x86-64 architecture with 4-level  |    |

|     | paging. Page walks access all levels of the table requiring an equal number of      |    |

|     | memory references.                                                                  | 19 |

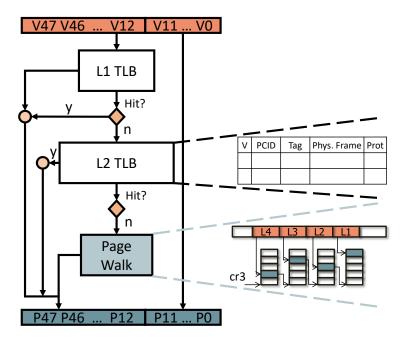

| 3.3 | Address Translation with hierarchical TLBs is performed entirely in HW              | 21 |

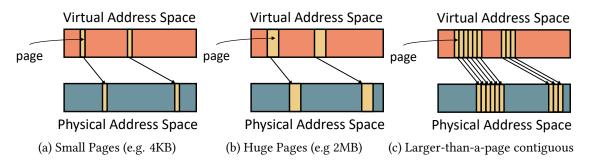

| 3.4 | Contiguity in Mappings and Address Translation.                                     | 23 |

|     | 3.4a Small Pages (e.g. 4KB)                                                         | 23 |

List of Figures xxiii

|      | 3.4b    | Huge Pages (e.g 2MB)                                                                                                                                                                                                                                                                             | 23 |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | 3.4c    | Larger-than-a-page contiguous                                                                                                                                                                                                                                                                    | 23 |

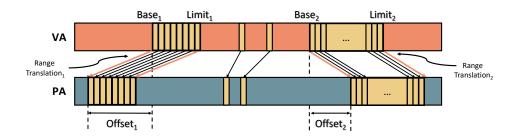

| 3.5  | Range   | Translations                                                                                                                                                                                                                                                                                     | 24 |

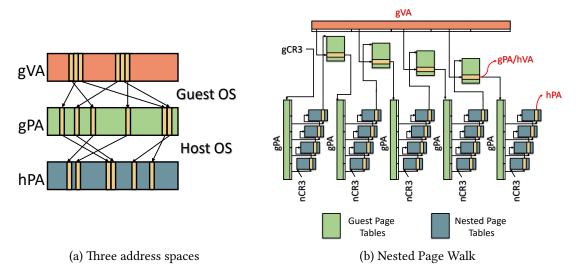

| 3.6  | Addres  | ss Translation in Virtualized Execution                                                                                                                                                                                                                                                          | 25 |

|      | 3.6a    | Three address spaces                                                                                                                                                                                                                                                                             | 25 |

|      | 3.6b    | Nested Page Walk                                                                                                                                                                                                                                                                                 | 25 |

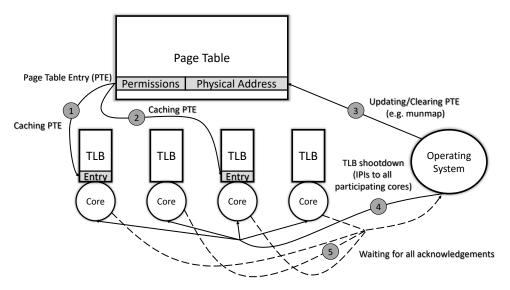

| 3.7  | TLB sh  | nootdowns [39]                                                                                                                                                                                                                                                                                   | 27 |

| 3.8  | Systen  | n calls related to virtual memory region creation, management and dele-                                                                                                                                                                                                                          |    |

|      | tion [5 | 8]                                                                                                                                                                                                                                                                                               | 28 |

| 3.9  | Virtua  | l Address Space in Linux [58, 144]                                                                                                                                                                                                                                                               | 29 |

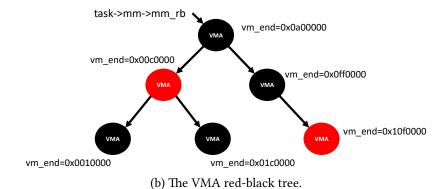

|      | 3.9a    | Virtual Memory Areas represent populated virtual ranges                                                                                                                                                                                                                                          | 29 |

|      | 3.9b    | The VMA red-black tree                                                                                                                                                                                                                                                                           | 29 |

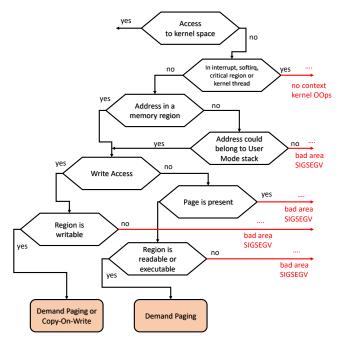

| 3.10 | The Pa  | ge Fault Handler [58]                                                                                                                                                                                                                                                                            | 31 |

|      | 3.10a   | Part I: checks if it is a valid user-space access [58]                                                                                                                                                                                                                                           | 31 |

|      | 3.10b   | Part II: demand paging                                                                                                                                                                                                                                                                           | 31 |

| 3.11 | The bu  | nddy allocator free block lists [58].                                                                                                                                                                                                                                                            | 32 |

| 3.12 | Block-  | level vs byte-level access.                                                                                                                                                                                                                                                                      | 34 |

|      | 3.12a   | Block-level access [63]                                                                                                                                                                                                                                                                          | 34 |

|      | 3.12b   | Byte-level access [63]                                                                                                                                                                                                                                                                           | 34 |

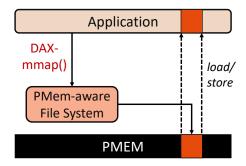

| 3.13 | DAX-r   | nmap                                                                                                                                                                                                                                                                                             | 35 |

| 3.14 | PMem    | Access: Software and Hardware layers [50]                                                                                                                                                                                                                                                        | 36 |

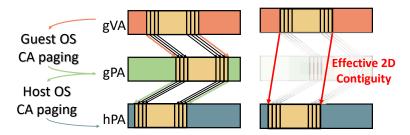

| 4.1  | used b  | al overview of our proposal for virtualized execution. (a) CA paging is y the guest and the host independently; seamlessly generating contiguity h dimensions; the intersection forms the desired 2D contiguity. (b) vRMM and SpOT (blue) are two orthogonal techniques to exploit the 2D conti- |    |

|      |         | and eliminate address translation overheads                                                                                                                                                                                                                                                      | 41 |

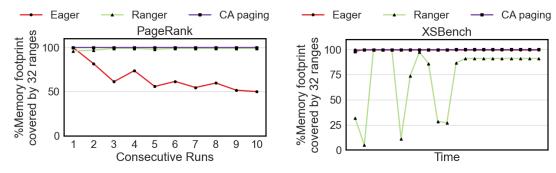

| 4.2  | Trade-  | offs between pre-allocation (eager paging), asynchronous defragmentation                                                                                                                                                                                                                         |    |

|      | (range  | r), and CA paging. Pre-allocation suffers from external fragmentation and                                                                                                                                                                                                                        |    |

|      | asynch  | nronous defragmentation delays contiguity generation                                                                                                                                                                                                                                             | 42 |

|      | 4.2a    | Pre-allocation suffers from external fragmentation                                                                                                                                                                                                                                               | 42 |

|      | 4.2b    | Asynchronous defrag delays contiguity generation                                                                                                                                                                                                                                                 | 42 |

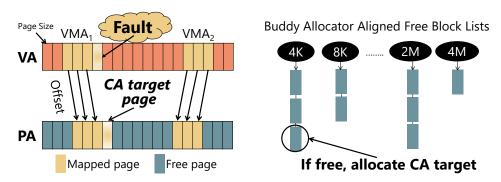

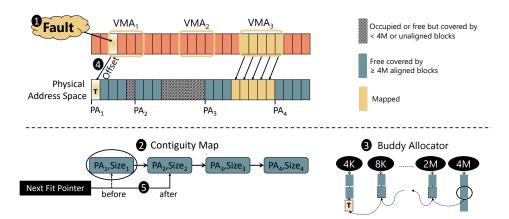

| 4.3  | Overv   | iew of contiguity-aware paging                                                                                                                                                                                                                                                                   | 44 |

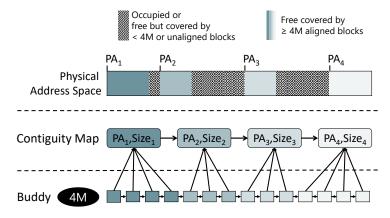

| 4.4  | The co  | ntiguity_map of CA paging                                                                                                                                                                                                                                                                        | 45 |

| 4.5  |         | g the first page: 1) first page fault 2) $contiguity\_map$ search for free region,                                                                                                                                                                                                               |    |

|      | 3) allo | cation, 4) Offset update, 5) next-fit rover pointer update                                                                                                                                                                                                                                       | 46 |

XXİV List of Figures

| 4.6  | CA paging is applied independently in the guest and host OS, generating guest        |    |

|------|--------------------------------------------------------------------------------------|----|

|      | and host contiguous mappings. Their intersection forms the effective 2D conti-       |    |

|      | guity exploited by the proposed hardware designs in Section 4.3                      | 48 |

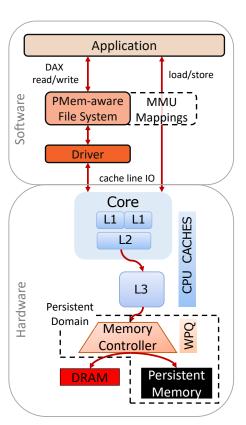

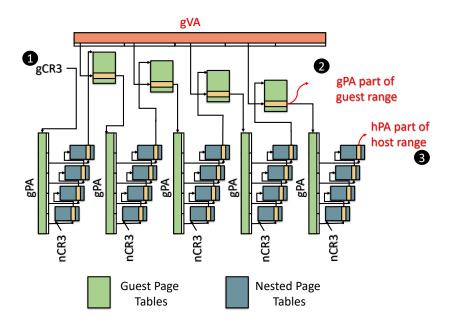

| 4.7  | vRMM caches effective 2D contiguous mappings in a range TLB, looked-up in            |    |

|      | parallel with the L2-page TLB. It requires complex architectural support; virtual-   |    |

|      | ization extensions over native RMM (nested ranges and a nested range walker).        |    |

|      | SpOT works entirely on the micro-architecture level, caching only 2DOffsets and      |    |

|      | using them to predict address translations on the L2-TLB miss path. It feeds the     |    |

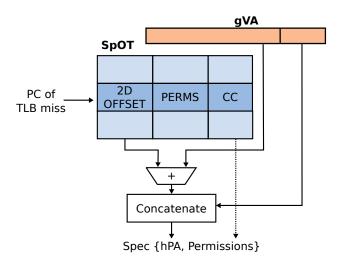

|      | predicted address to the CPU which continues execution on Speculative mode           | 48 |

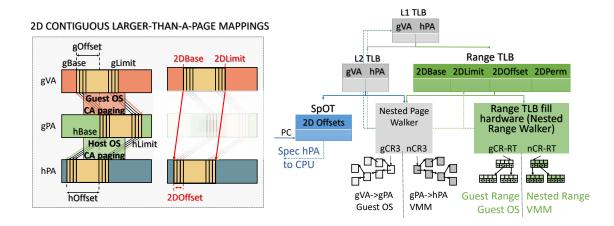

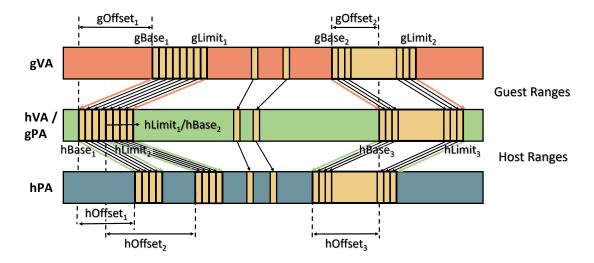

| 4.8  | Unaligned arbitrarily-sized contiguous mappings (ranges) in virtualized execution.   | 50 |

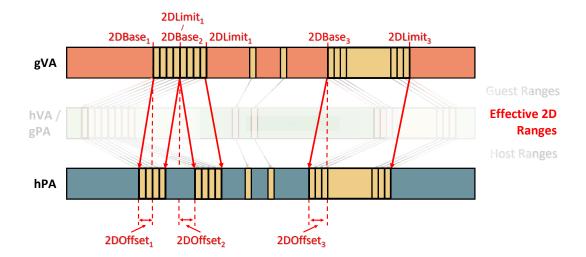

| 4.9  | The effective full 2D contiguous mappings (ranges). vRMM caches the 2D ranges        |    |

|      | in a range TLB. SpOT caches only the 2D Offsets to predict translations              | 51 |

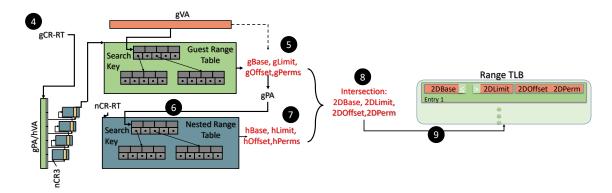

| 4.10 | Range TLB miss in vRMM. Part1: The nested page walker identifies the missing         |    |

|      | page translation and if the page is part of a guest and host range                   | 52 |

| 4.11 | Range TLB miss in vRMM. Part2: The nested range walker walks the guest and           |    |

|      | nested range tables, and generates the 2D range translation.                         | 53 |

| 4.12 | SpOT predicts the physical address of missing translations, inferring the offsets of |    |

|      | contiguous mappings. It consists of a micro-architectural prediction table track-    |    |

|      | ing the [offset,permissions] of recently missed translations                         | 56 |

| 4.13 | SpOT is integrated in the L2 TLB miss path and hides nested page walk latency        |    |

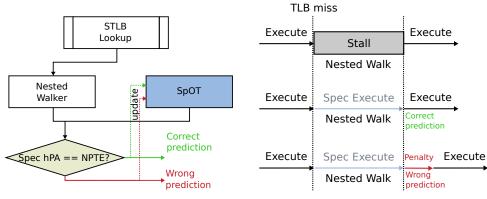

|      | under speculative execution                                                          | 57 |

|      | 4.13a SpOT predicts a physical translation on a TLB miss                             | 57 |

|      | 4.13b Speculative execution in parallel with nested walk                             | 57 |

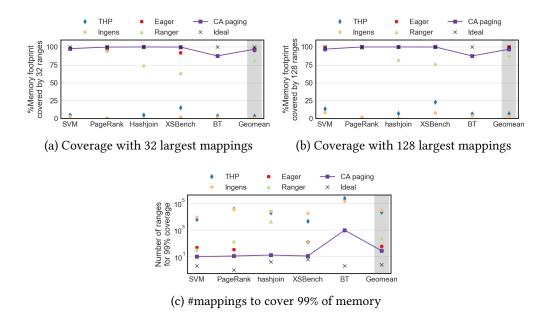

| 4.14 | Contiguity performance without memory pressure for native execution                  | 62 |

|      | 4.14a Coverage with 32 largest mappings                                              | 62 |

|      | 4.14b Coverage with 128 largest mappings                                             | 62 |

|      | 4.14c #mappings to cover 99% of memory                                               | 62 |

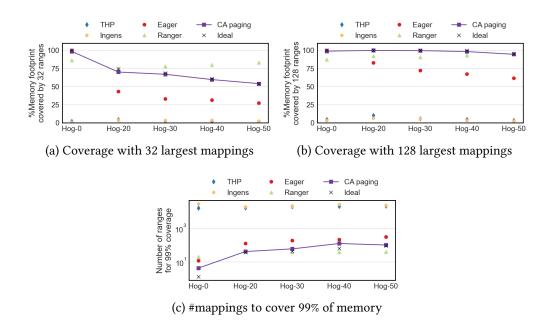

| 4.15 | Contiguity performance under memory pressure/external fragmentation. Ge-             |    |

|      | omean results for all benchmarks                                                     | 63 |

|      | 4.15a Coverage with 32 largest mappings                                              | 63 |

|      | 4.15b Coverage with 128 largest mappings                                             | 63 |

|      | 4.15c #mappings to cover 99% of memory                                               | 63 |

| 4.16 | Free block size distribution after benchmarks execution                              | 64 |

| 4.17 | 32 largest mappings coverage while running two instances of SVM (straight and        |    |

|      | dotted line for every method).                                                       | 65 |

| 4.18 | Software runtime overheads normalized to THP                                         | 65 |

| 4.19 | Contiguity performance without memory pressure for virtualized execution             | 67 |

List of Figures XXV

|      | 4.10 - C                                                                              | (7         |

|------|---------------------------------------------------------------------------------------|------------|

|      | 4.19a Coverage with 32 largest mappings                                               | 67         |

|      | 4.19b Coverage with 128 largest mappings                                              | 67         |

| 4.00 | 4.19c #mappings to cover 99% of memory                                                | 67         |

| 4.20 | Execution time overheads due to data TLB misses that trigger page walks in vir-       | <b>4 7</b> |

| 4.04 | tualized execution                                                                    | 67         |

| 4.21 | Percentage of TLB misses that SpOT made (i) correct predictions, (ii) mispredic-      |            |

|      | tions, and (iii) no predictions                                                       | 68         |

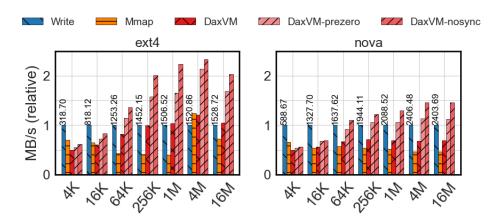

| 5.1  | DAX interfaces: (a) the latency of reading a file once via MM is worse than read      |            |

|      | system calls, especially for small file sizes (lower is better), (b) MM read-once ac- |            |

|      | cess does not scale to many cores (higher is better), (c) MM repetitive access on     |            |

|      | a large file can perform worse than read/write (higher is better). All results are    |            |

|      | from a system equipped with Intel's Optane DCPMM and an aged ext4-DAX [216]           |            |

|      | file system image (Section 5.5). DaxVM significantly reduces latency and im-          |            |

|      | proves scalability for MM, regardless of the file system fragmentation                | 76         |

|      | 5.1a One time access                                                                  | 76         |

|      | 5.1b Scalability to many cores                                                        | 76         |

|      | 5.1c Repetitive access                                                                | 76         |

| 5.2  | DaxVM maintains pre-populated shared file tables and attaches them to processes       |            |

|      | address spaces for O(1) mappings                                                      | 83         |

| 5.3  | DaxVM ephemeral VMAs                                                                  | 87         |

| 5.4  | Read-once (ephemeral) file access                                                     | 93         |

| 5.5  | Repetitive file access.                                                               | 93         |

| 5.6  | Kernel-space and user-space syncing operations                                        | 94         |

| 5.7  | Append operations                                                                     | 95         |

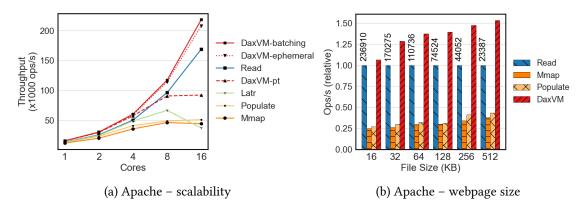

| 5.8  | DaxVM allows applications that issue many (un)map requests (e.g., web-servers)        |            |

|      | (b)) to scale to many cores and exposes the zero-copy advantage of MM over            |            |

|      | system call access on a setup that was previously considered prohibitive              | 97         |

|      | 5.8a Apache – scalability                                                             | 97         |

|      | 5.8b Apache – webpage size                                                            | 97         |

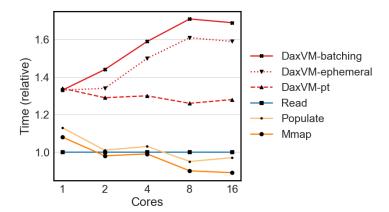

| 5.9  | Text search performance. DaxVM improves scalability of applications that never        |            |

|      | move data out of PMem (like text search)                                              | 98         |

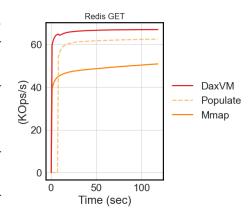

| 5.10 | Redis boot                                                                            | 99         |

| 5.11 | DaxVM O(1) mmap accelerates the restoration of a virtual machine state from           |            |

|      | a snapshot stored in PMem. In this unique set-up snapshot's read-only pages           |            |

|      | are never copied to DRAM, and thus the VM's physical memory gets essentially          |            |

|      | backed by PMem [132]                                                                  | 100        |

XXVİ List of Figures

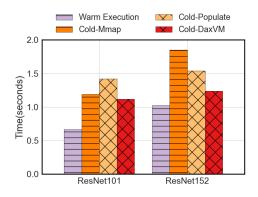

| 5.12 | Firecracker Cold-starts                                                           | 100 |

|------|-----------------------------------------------------------------------------------|-----|

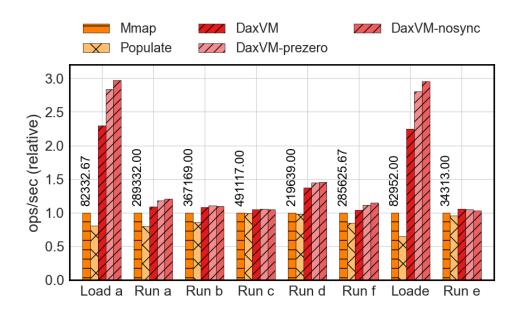

| 5.13 | YCSB on RocksDB. DaxVM sustains high operational throughput for databases         |     |

|      | on a fragmented ext4 images                                                       | 101 |

|      |                                                                                   |     |

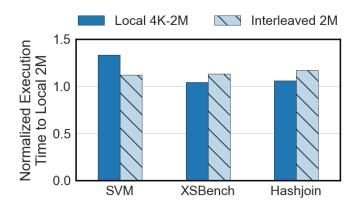

| 6.1  | Huge Pages and NUMA. Local NUMA placement may not always be the optimal           |     |

|      | choice in the presence of external fragmentation. We compare the total execution  |     |

|      | time of a workload when its memory is i) $100\%$ local but $50\%$ covered by huge |     |

|      | pages and ii) 100% covered by huge pages but interleaved. We observe that the     |     |

|      | latter is better for SVM                                                          | 107 |

# List of Tables

| 4.1 | Overview of our contributions with respect to state-of-practice (THP) and state- |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | of-the-art (DS,RMM) approaches for reducing virtualization overheads             | 40  |

| 4.2 | Number of ranges (vRMM), and anchor entries (vHC) to map 99% of the footprint    |     |

|     | of big-memory workloads, using (i) default THP, (ii) CA paging in virtualized    |     |

|     | execution.                                                                       | 55  |

| 4.3 | System Configuration                                                             | 60  |

| 4.4 | Performance model based on hardware performance counters and hardware em-        |     |

|     | ulation with BadgerTrap [100]                                                    | 61  |

| 4.5 | Workloads description and memory footprint                                       | 61  |

| 4.6 | Total number of page faults and 99th latency (us)                                | 66  |

| 4.7 | Bloat [memory (overhead%)] compared to 4KB                                       | 66  |

| 4.8 | Estimation of Unsafe Load Instructions (USL)                                     | 69  |

| 5.1 | Comparison of DaxVM with prior works that focus on memory mapping storage.       | 77  |

| 5.2 | Average page walk cycles measured when file tables are stored in PMem or DRAM.   |     |

|     | We consider sequential and random 4K access on a 10G memory-mapped file. $$ .    | 84  |

| 5.3 | DaxVM monitors the average TLB miss costs and MMU overheads to migrate file      |     |

|     | tables to DRAM if necessary.                                                     | 84  |

| 5.4 | Paths acquiring the mmap semaphore and their involvement in DAX and ephemeral    |     |

|     | mappings management                                                              | 88  |

| 5.5 | Summarizing observations                                                         | 103 |

| 6.1 | ARMv8 supported page sizes                                                       | 109 |

### CHAPTER 1

### Εκτεταμένη περίληψη στην ελληνική γλώσσα

Τα σύγχρονα υπολογιστικά συστήματα εξαρτώνται από τον μηχανισμό της εικονικής μνήμης – αφαίρεση που έχει αποδειχθεί κρίσιμη για την επιτυχία των υπολογιστών και έχει αντέξει στη δοκιμασία του χρόνου. Επιτρέπει στους προγραμματιστές να γράψουν κώδικα θεωρώντας τη διαθέσιμη μνήμη πάντα επαρκή, τεράστια, γραμμική και ιδιωτική για την εφαρμογή τους. Τους επιτρέπει επίσης να πρόσπελαύνουν τις συσκευές Ε/Ε στο χώρο μνήμης, χρησιμοποιώντας εντολές γλώσσας μηχανής (assembly) σαν να διαβάζουν και να γράφουν στη μνήμη (π.χ. load/store). Αυτό απλοποιεί περαιτέρω τον προγραμματισμό και δυνητικά επιτρέπει την εξάλειψη του πυρήνα του λειτουργικού συστήματος από τη στοίβα λογισμικού Ε/Ε, μια τεχνική που χρησιμοποιείται για καλύτερη απόδοση.

Ωστόσο, αυτή η ευελιξία έχει κόστος. Δεδομένου ότι το λογισμικό χρησιμοποιεί εικονικές διευθύνσεις για την πρόσβαση στα διάφορα επίπεδα της ιεραρχίας αποθήκευσης δεδομένων (κύρια μνήμη, συσκευές PCI-e, κ.λπ.), επικρατούν τρεις πηγές κόστους: (i) η διαχείριση των χώρων εικονικών διευθύνσεων των διεργασιών ενός συστήματος, (ii) η δημιουργία και η διαχείριση των αντιστοιχίσεων της εικονικής μνήμης στο υλικό και (iii) η μετάφραση που απαιτείται για κάθε εντολή load/store του επεξεργαστή. Τα δύο πρώτα περιορίζουν σημαντικά την κλιμακωσιμότητα της εικονικής μνήμης στην εποχή των πολλών πυρήνων [48, 72] ενώ πριν από μια δεκαετία οι υπολογιστές χτύπησαν στο Address Translation Wall [53] και δεν το ξεπέρασαν ποτέ πλήρως.

Οι σύγχρονες τάσεις στη σχεδίαση υπολογιστικών συστημάτων συνεχίζουν να πιέζουν την απόδοση της εικονικής μνήμης, δοκιμάζοντας και τους τρεις προαναφερθέντες μηχανισμούς.

Η μετεωρική αύξηση των απαιτήσεων σε μνήμη, η μαζική στροφή στο υπολογιστικό νέφος (cloud computing), η αυξανόμενη ετερογένεια στις στοίβες υπολογιστών και αποθήκευσης και η κυριαρχία των πολλών πυρήνων και του παράλληλου προγραμματισμού, επιβάλλουν να επανεξετάσουμε τόσο το λογισμικό συστήματος όσο και το υλικό του μηχανισμού της εικονικής μνήμης, μαζί με τη συνέργεια τους.

Στη παρούσα διατριβή εστιάζουμε στο κόστος μετάφρασης διευθύνσεων για εφαρμογές με μεγάλη ένταση σε δεδομένα και στην απόδοση της εικονικής μνήμης για εφαρμογές με έντονη δραστηριότητα Ε/Ε. Σε αυτό το κεφάλαιο εξετάζουμε αρχικά και εν συντομία τους βασικούς μηχανισμούς της εικονικής μνήμης, π.χ. τη σελιδοποίηση, όταν αυτή λειτουργεί σαν αφαίρεση μνήμης άλλα και σα διεπαφή για την πρόσβαση σε αρχεία. Στη συνέχεια, παρουσιάζουμε τα κίνητρα με τα οποία διαλέξαμε να εξετάσουμε συγκεκριμένα σημεία συμφόρησης της απόδοσης και της κλιμακωσιμότητας της εικονικής μνήμης και, τέλος, παρουσιάζουμε τις συνεισφορές της παρούσας διατριβής για την αντιμετώπισή τους.

#### 1.1 Σελιδοποιημένη εικονική μνήμη

Η εικονική μνήμη είναι ένας έντονα συ-σχεδιασμένος μηχανισμός (στο υλικό και στο λογισμικό) όπου i) το ΛΣ διαχειρίζεται τους εικονικούς χώρους διευθύνσεων των διεργασιών και τους αντιστοιχίζει σε φυσικά μέσα αποθήκευσης (π.χ. μνήμη), ενώ ii) προσαρμοσμένη αρχιτεκτονική υποστήριξη στο υλικό επιταχύνει το απαραίτητο βήμα μετάφρασης διευθύνσεων κατά την εκτέλεση κάθε εντολής load/store του επεξεργαστή. Εκτός αφαίρεση της φυσικής μνήμης, η εικονική μνήμη είναι επίσης μια πολύτιμη διεπαφή για την αποθήκευση μόνιμων δεδομένων (π.χ. μέσω αντιστοιχίσεων αρχείων).

#### 1.1.1 Λειτουργικό Σύστημα

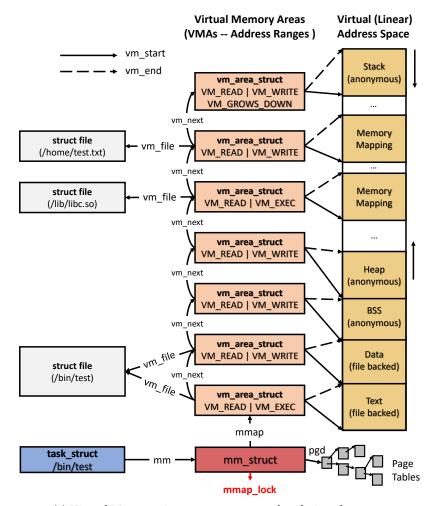

Διαχείριση του χώρου εικονικών διευθύνσεων. Κάθε διεργασία έχει έναν μεγάλο γραμμικό χώρο εικονικών διευθύνσεων που σχηματίζει την αφαίρεση μνήμης που εκτίθεται στον προγραμματιστή. Τον διαχειρίζεται το ΛΣ σε μεγέθη σελίδας. Τα διαθέσιμα μεγέθη σελίδας είναι συγκεκριμένα (κβαντισμένα) και εξαρτώνται από την αρχιτεκτονική, για την x86 αρχιτεκτονική μπορεί να είναι 4ΚΒ (μικρές σελίδες) ή 2ΜΒ/1GB (μεγάλες σελίδες). Το ΛΣ δεσμεύει εύρη εικονικών διευθύνσεων από αυτόν τον χώρο όταν οι διεργασίες ζητούν να δεσμεύσουν φυσική μνήμη ή να αποκτήσουν πρόσβαση σε αρχεία μέσω απεικονίσεων μνήμης.

Απεικονίσεις (αντιστοιχίσεις) μνήμης. Το λειτουργικό σύστημα αντιστοιχίζει/απεικονίζει τις δεσμευμένες εικονικές διευθύνσεις κάθε διεργασίας σε ένα μέσο αποθήκευσης, συνήθως στη φυσική μνήμη, για να επιτρέψει την πρόσβαση σε δεδομένα από το χώρο χρήστη μέσω αναφορών (memory references). Η διαχείριση της φυσικής μνήμης γίνεται επίσης σε μεγέθη

σελίδας (4KB) από το ΛΣ και το λειτουργικό σύστημα αντιστοιχίζει εικονικές σελίδες σε φυσικά πλαίσια ανά διεργασία. Με αυτόν τον τρόπο, οι διεργασίες έχουν μια απομονωμένη και προστατευμένη απεικόνιση της μνήμης, αλλά μπορούν ακόμα να μοιράζονται σελίδες μεταξύ τους (π.χ. αντιστοι-χίσεις σε κοινά φυσικά πλαίσια). Το λειτουργικό σύστημα αποθηκεύει τις αντιστοιχίσεις σελίδων εικονικής σε φυσική μνήμη σε μια ειδική δομή δεδομένων ανά διεργασία, συνήθως ένα δέντρο, το οποίο αποτελεί μέρος του περιβάλλοντος εκτέλεσης κάθε διεργασίας και ονομάζεται πίνακας σελίδων. Κάθε καταχώρηση του πίνακα σελίδων (PTE) περιέχει μια μετάφραση από εικονική σε φυσική σελίδα. Οι πίνακες σελίδων εξαρτώνται από την αρχιτεκτονική, όπως και τα μεγέθη σελίδων, καθώς χρησιμοποιούνται απευθείας από το υλικό (HW) της εικονικής μνήμης (θα συζητηθεί αργότερα). Το λειτουργικό σύστημα, στη κοινή περίπτωση, δημιουργεί τις αντιστοι-χίσεις/απεικονίσης νωχελικά ανά σελίδα – μέσω μιας διακοπής ΛΣ (trap) γνωστής ως σφάλμα σελίδας.

Διαχείριση φυσικής μνήμης. Αν και δεν συνδέεται αποκλειστικά με την εικονική μνήμη, η διαχείριση της φυσικής μνήμης διασταυρώνεται με πολλές λειτουργίες της. Στην κοινή περίπτωση, τα περισσότερα ΛΣ δεσμεύουν φυσική μνήμη κατ' απαίτηση –δηλαδή κατά τη διάρκεια των σφαλμάτων σελίδας– και σε μεγέθη σελίδας (ή αλλιώς πλαισίου). Τα σφάλματα σελίδας πυροδο-τούνται από κρύες (πρώτες/αρχικές) προσβάσεις σε εικονικές σελίδες (διευθύνσεις) από την εκάστοτε εφαρμογή. Το μέγεθος δέσμευσης (π.χ. μέγεθος σελίδας) επηρεάζει την απόδοση μετάφρασης διευθύνσεων της εικονικής μνήμης (υλικό) και θα συζητηθεί αργότερα.

Απεικονίσεις αρχείων. Η εικονική μνήμη μπορεί επίσης να χρησιμοποιηθεί ως διεπαφή για την πρόσβαση σε αρχεία. Η Είσοδος/ Έξοδος μέσω απεικόνισης στη μνήμη (memory-mapped IO) είναι η τεχνική που αντιστοιχίζει εικονικές διευθύνσεις σε σελίδες αρχείων και επιτρέπει την πρόσβαση αρχείων μέσω αναφοράς μνήμης. Το λειτουργικό σύστημα δεσμεύει ένα εύρος εικονικών διευθύνσεων για κάθε απεικόνιση αρχείου και, για μέσα αποθήκευσης που υποστηρίζουν μόνο πρόσβαση σε επίπεδο μπλόκ, αποθηκεύει τα αρχεία προσωρινά στη φυσική μνήμη για να τα αντιστοιχίσει έπειτα στο χώρο χρήστη. Μια προσωρινή μνήμη σε επίπεδο ΔΣ, διαχειρίσιμη από το λογισμικό συστήματος και γνωστή ως page cache, συσχετίζει τα μπλοκ αποθήκευσης των αρχείων με φυσικά πλαίσια μνήμης και, σε ενορχήστρωση με το σύστημα αρχείων, δημιουργεί αντίγραφα μεταξύ τους. Μόλις αντιγραφούν τα δεδομένα των αρχείων στη φυσική μνήμη, οι δεσμευμένες εικονικές σελίδες αντιστοιχίζονται στα αντίστοιχα πλαίσια φυσικής μνήμης χρησιμοποιώντας τους ίδιους μηχανισμούς σελιδοποίησης που συζητήθηκαν στην προηγούμενη παράγραφο. Με το memory-mapped ΙΟ, τα αρχεία αντιγράφονται από την συσκευή αποθήκευσης στη φυσική μνήμη για να προσπελαστούν.

Ο χώρος εικονικών διευθύνσεων είναι ένας εγγενώς κοινόχρηστος πόρος μεταξύ των νημάτων μιας διεργασίας και, ως εκ τούτου, καταλήγει να είναι σημείο έντονης συμφόρησης στην εποχή των πολλών πυρήνων. Δυστυχώς, τα περισσότερα λειτουργικά συστήματα σειριοποιούν τις

λειτουργίες του εικονικού χώρου διευθύνσεων [59,60,70,71,140], περιορίζοντας την κλιμακωσιμότητα της εικονικής μνήμης. Το κόστος της σελιδοποίησης (π.χ. καθυστέρηση λόγω σφαλμάτων σελίδας) είναι επίσης σημαντικό. Ιδιαίτερα για εφαρμογές με έντονη δραστηριότητα Ε/Ε και χρήση της τεχνικής απεικόνισης αρχείων στη μνήμη, τα σφάλματα σελίδας μπορούν να μειώσουν σημαντικά τη συνολική απόδοση [124,125,168,169,220]. Όλα τα παραπάνω κόστη οδήγησαν στην αμφισβήτηση της εφαρμογής της εικονική μνήμης ως διεπαφής αρχείων, ακόμη και για εφαρμογές με μεγάλη ένταση ΙΟ όπως βάσεις δεδομένων [84], παρά την ευκολία χρήσης της.

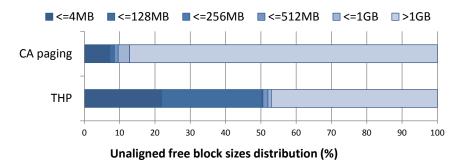

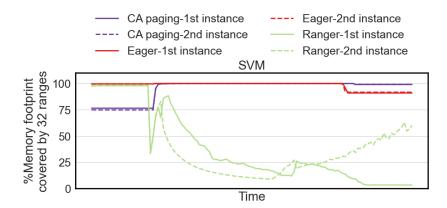

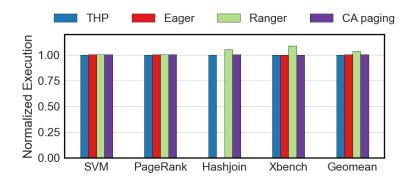

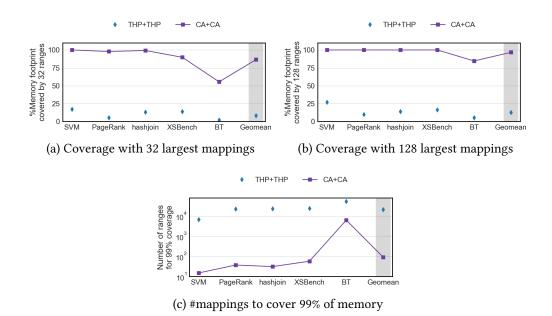

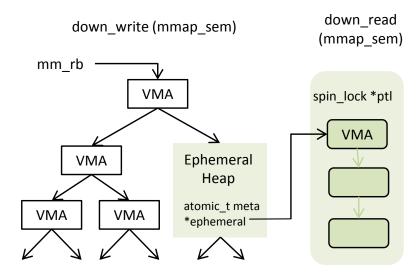

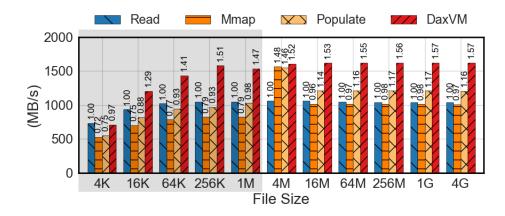

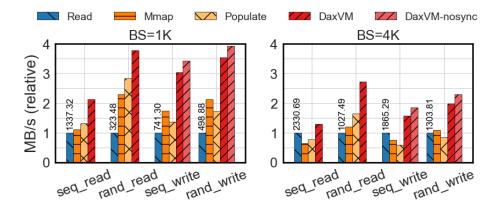

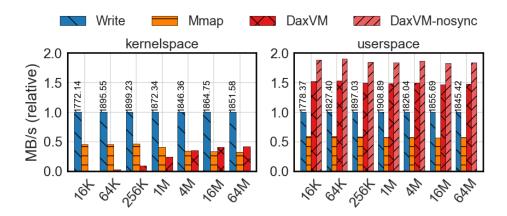

#### 1.1.2 Υποστήριξη στην αρχιτεκτονική για τη μετάφραση διευθύνσεων