**ARENBERG DOCTORAL SCHOOL** Faculty of Engineering Science

SCHOOL OF ELECTRICAL & COMPUTER ENGINEERING

Department of Computer Science

# Enabling Behavior-Based Energy Consumption and Memory Footprint Optimizations in Native Contexts

#### **Christos Lamprakos**

Supervisors:

Prof. dr. ir. Dimitrios Soudris

(NTUA)

Prof. dr. ir. Francky Catthoor Prof. dr. ir. Johan De Boeck Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

July 2025

### ENABLING BEHAVIOR-BASED ENERGY CONSUMPTION AND MEMORY FOOTPRINT OPTIMIZATIONS IN NATIVE CONTEXTS

Christos LAMPRAKOS

Supervisors:

Prof. dr. ir. Dimitrios Soudris

(NTUA)

Prof. dr. ir. Francky Catthoor

Prof. dr. ir. Johan De Boeck

Members of the

**Examination Committee:**

Prof. dr. ir. Hendrik Van Brussel, chair

Prof. dr. ir. Ioanna Roussaki

(NTUA)

Prof. dr. ír. Sotirios Xydis

(NTUA)

Prof. dr. ir. George Theodoridis

(University of Patras)

Dr. ir. Manu Perumkunnil

(IMEC)

Dissertation presented in partial fulfillment of the requirements for the degree of Doctor of Engineering Science (PhD): Electrical Engineering

© 2025 Christos Lamprakos Uitgegeven in eigen beheer, Christos Lamprakos, Lamprou Katsoni 67-69, 11471 Athens (Greece) Alle rechten voorbehouden. Niets uit deze uitgave mag worden vermenigvuldigd en/of openbaar gemaakt worden door middel van druk, fotokopie, microfilm, elektronisch of op welke andere wijze ook zonder voorafgaande schriftelijke toestemming van de uitgever. All rights reserved. No part of the publication may be reproduced in any form by print, photoprint, microfilm, electronic or any other means without written permission from the publisher.

KU LEUVEN

Εθνικό Μετσόβιο Πολυτεχνείο Σχολή Ηλεκτρολόγων Μηχανικών & Μηχανικών Υπολογιστών Τομέας Τεχνολογίας Πληροφορικής και Υπολογιστών Καθολικό Πανεπιστήμιο του Λέουβεν Σχολή Ηλεκτρολόγων Μηχανικών DOCT Επιστήμης Μηχανικής

# Συμπεριφοροχεντρική Βελτιστοποίηση Ενεργειακής Κατανάλωσης και Αποτυπώματος Μνήμης

Διδακτορική Διατριβή του Χρήστου Λαμπράκου

Επιβλέποντες: Δημήτριος Σούντρης (ΕΜΠ)

Francky Catthoor (EM $\Pi$ ) Johan De Boeck (KUL)

Αθήνα, Ιούλιος 2025

National Technical University of Athens School of Electrical & Computer Engineering Division of Communication, Electronic and Information Engineering KU Leuven Electrical Engineering Doctor of Engineering Science

#### Enabling Behavior-Based Energy Consumption and Memory Footprint Optimizations in Native Contexts

#### Ph.D. Thesis of Christos Lamprakos

Supervisory Committee: Dimitrios Soudris (Professor NTUA)

Francky Catthoor (Visiting Professor NTUA)

Johan De Boeck (Professor KUL)

Approved by the advisory committee on July 10th, 2025.

| Dimitrios Soudris<br>Professor NTUA        | Francky Catthoor<br>Visiting Professor NTUA      | Johan De Boeck<br>Professor KUL             |

|--------------------------------------------|--------------------------------------------------|---------------------------------------------|

| Dionisios Pnevmatikatos Professor NTUA     | Konstantinos Siozios<br>Associate Professor AUTH | Manu Perumkunnil<br>Senior Researcher IMEC  |

| Sotirios Xydis<br>Assistant Professor NTUA | Ioanna Roussaki<br>Professor NTUA                | George Theodoridis Associate Professor UPAT |

Athens, July 2025

.....

Christos Lamprakos Doctor of Philosophy in Engineering NTUA Doctor of Engineering Science KUL

Copyright © Christos Lamprakos, 2025. All rights reserved.

It is forbidden to copy, store, and distribute this work, in whole or in part, for commercial purposes. Reproduction, storage, and distribution are permitted for non-profit, educational or research purposes, provided that the source is referenced and this message is retained. Questions concerning the use of this work for profit should be addressed to the writer. Content that is reused from publications that the author has (co-)authored (excerpts, figures, tables, etc.) is under copyright with the respective paper publishers (IEEE, ACM, etc) and is cited accordingly in the current text. Content that reused from third-party publications appears with the appropriate copyright note. Reuse of such content by any interested party requires the publishers' prior consent, according to the applicable copyright policies. Content that has not been published before is copyrighted jointly as follows:

2025 - Electrical & Computer Engineering NTUA 2025 - Faculty of Engineering Science KUL

## **Acknowledgements**

The reason why I'm leaving academia is the constant need it imposes to prove myself in ways irrelevant to the work done. Thankfully I did not have to do that when it came to starting my graduate studies. My advisors, **Prof. Dimitrios** Soudris and Prof. Francky Catthoor, granted me with their ultimate trust from the very outset despite barely knowing me. In a world collapsing under absurdity, they gave me a straightforward and reasonable professional haven. I shall remain forever grateful to them, and all the wisdom that they so generously shared with me during the past six years. Speaking of teachers to whom I owe everything, here is a list that I have never stopped going through in my head and heart: my English tutor Kostas Galanis, for all the joyful hours he invested in shaping my speech, perception and self-esteem. My teacher during the final couple of years in elementary school, **Tasos Stamoulis**, for encouraging me to acknowledge and honor my strengths. My mentors from the Poreia Tutor School while preparing for the national university entrance exams: **Thodoris** Antonopoulos (greek language), Maria Vagia (mathematics), Tasos Melas (physics), Nikos Anastasopoulos (economics). My life has drawn me far from all of you, and I am sorry that I was not decent enough to keep contact. Please remember that your time with me was not for nothing. As for my friends and family, you know who you are and how much I love you. Individuals are an illusion, relationships are all that matters, I wish that our happy little tree of life never withers.

#### **Funding**

The research work presented in this text was financially supported by:

• the European Union's Horizon 2020 research and innovation programme under grant agreement No 780572 SDK4ED (www.sdk4ed.eu).

vi \_\_\_\_\_\_\_ ACKNOWLEDGEMENTS

• the European Union's Horizon 2020 research and innovation programme under grant agreement No. 101021274 PRAETORIAN (https://cordis.europa.eu/project/id/101021274).

- the European Union's Horizon Europe research and innovation programme under Grant Agreement No. 101096110 PRIVATEER (https://www.privateer-project.eu/).

- the European Union's Horizon research and innovation programme under grant agreement No 101070374 CONVOLVE (https://convolve.eu/).

- the Hellenic Foundation for Research and Innovation (HFRI) under the 3rd Call for HFRI PhD Fellowships (fellowship number: 61/512200).

## **Popularized Abstract**

Computers control a large part of modern life despite being a (very) small part of history. And while exotic new applications such as ChatGPT attract most of the interest from both consumers and practitioners, the first principles underlying our world's digital infrastructure remain timeless. This thesis studies the following such principles through the lens of energy consumption and memory footprint: (i) a central aspect of program behavior is its dynamic requests for memory, (ii) approximately optimal solutions to memory allocation can be computed offline and (iii) software is the result of iterative decision-making over source code transformations.

Along the way, we make a series of original contributions. We show the complex impact that specific dynamic memory allocation implementations have on the extremely popular Python programming language; we describe a principled methodology for capturing program-allocator interaction and quantifying memory fragmentation; we contribute a static memory planning implementation outperforming the SOTA in a wide range of heavyweight, challenging benchmarks; and we demonstrate a flexible, agnostic framework for improving software.

Join us in a thrilling intellectual adventure spanning several levels of abstraction, featuring arcane algorithms and data structures, and introducing an entire new interpretation to the term *deep learning!* At the end of this text, we promise to have enlightened you with a satisfying conclusion to the Holywood-scale story starting with:

Once upon a time, three allocators walked into a bar...

# **Gepopulariseerde Samenvatting**

Computers beheersen een groot deel van het moderne leven, ondanks dat ze slechts een (zeer) klein deel van de geschiedenis uitmaken. En hoewel exotische nieuwe toepassingen zoals ChatGPT de meeste interesse wekken bij zowel consumenten als professionals, blijven de basisprincipes die ten grondslag liggen aan de digitale infrastructuur van onze wereld tijdloos. Dit proefschrift bestudeert de volgende principes vanuit het perspectief van energieverbruik en geheugenvoetafdruk: (i) een centraal aspect van programmagedrag is de dynamische geheugenaanvraag, (ii) bijna-optimale optimale oplossingen voor geheugentoewijzing kunnen offline worden berekend en (iii) software is het resultaat van iteratieve besluitvorming over broncodetransformaties.

Onderweg leveren we een reeks originele bijdragen. We laten de complexe impact zien die specifieke implementaties van dynamische geheugentoewijzing hebben op de extreem populaire programmeertaal Python; we beschrijven een principiële methodologie voor het vastleggen van de interactie tussen programma's en geheugentoewijzers en het kwantificeren van geheugenfragmentatie; we een statische geheugenplanningsimplementatie die de bestaande literatuur overtreft in een breed scala aan zware, uitdagende benchmarks; en we demonstreren een flexibel, agnostisch raamwerk voor softwareverbetering.

Ga met ons mee op een spannend intellectueel avontuur dat verschillende abstractieniveaus beslaat, met mysterieuze algoritmen en datastructuren, en een geheel nieuwe interpretatie van de term *deep learning* introduceert! Aan het einde van deze tekst beloven we u te hebben geïnformeerd met een bevredigende conclusie van het verhaal op Holywood-schaal, beginnend met:

Er waren eens drie toewijzers die een bar binnenliepen...

#### **Abstract**

The fact that modern society depends on computers in order to function may obscure the fact that computer science, and consequently computer engineering, is a young discipline. Each decade since the 1990s has captivated the public's attention with yet another digital miracle, starting with the Internet, then social media, and now artificial intelligence. The ever growing impact of each aforementioned advancement on the economy has in return directed the respective research spotlights: the Web spawned parallel processing, Facebook spawned cloud computing, and though the dust has yet to settle, one cannot deny the push that LLMs have given to hardware accelerators and novel memory-centric technology such as CXL and compute-in-memory.

On the one hand, a scientific discipline being driven by its applications is a most natural phenomenon. It is after all the degree to which it benefits the public from where a breakthrough draws its value. On the other hand, we cannot help but wonder: *could this progress be happening too fast?* How can we be certain that all fruits have been reaped before moving on to the next paradigm? Intuition suggests we cannot. But each next paradigm is built on top of the previous one. This thesis is founded upon the belief that **meaningful work remains to be done in the fundamentals of computer systems**.

Let us begin with a definition of what we mean with the term "computer system". At the bottom of the abstraction hierarchy lies the "hardware", which we view as a compute unit interacting with a memory module. At the top we find a user application consisting of (i) source code that a developer wrote and (ii) third-party libraries imported as dependencies, written by other developers. Collectively, the application's source code is turned into executable binary instructions via the help of a compiler. In between the executable and the system's hardware lies the OS, which provides the illusion that this is a dedicated machine, hides the hardware's actual complexity behind interfaces, and takes care of running everything safely and efficiently.

xii \_\_\_\_\_\_ ABSTRACT

For a long time now, the above definition has been a comfortable fabrication: compute units are many and heterogeneous, memory could encompass address spaces in *other* machines and/or be heterogeneous itself, and so on. But a second necessary remark is that, nevertheless, the simplified computer system remains the model used (if any) by most developers. A reasonable means to resolve this tension is to incorporate in our view the specific effects that an application's execution brings upon aspects of the system that we care about; in other words, its *behavior*. Modern system architects should let laymen developers retain their simplified model, while working underground to deliver infrastructure that adapts to its tasks in real time. This idea may sound synonymous to that one of abstraction, which is as old as computing itself—and rightfully so. Our emphasis regards what aspects of the system should the aforementioned abstractions adapt toward.

Energy consumption and memory footprint are often overlooked in the race to minimize execution time, which is the chief concern of all users. To give a concrete example, consider the ubiquitous dynamic memory allocation interface comprising GNU's malloc family of functions. By first principles, memory fragmentation is the main enemy of any allocator. But little work on defining fragmentation has been conducted, and allocator designers prefer to focus on problems impacting latency or security. Another example stems from the deep learning domain, where workloads are facing a so-called "memory wall"—apart from excessive energy requirements. This is mostly about memory bandwidth but partly also about the massive storage capacity needed, especially for exploding demand for machine learning-powered services.

Thus, we are brought to the research objectives of this dissertation, all of whom can be viewed as operations at a relatively high abstraction level where application programmers do not want to "see" the complex synergy between their code, the OS and the physical hardware:

- Objective A: Conduct a principled, informed study of workload-allocator interaction and memory footprint.

- Objective B: Deliver a scalable SOTA implementation for static memory planning.

- Objective C: Provide application developers with assistance to better evaluate the impact of source-to-source transformations.

**Keywords:** static memory planning, dynamic storage allocation, memory management, energy accounting, software engineering

## **Beknopte samenvatting**

Het feit dat de moderne samenleving afhankelijk is van computers om te functioneren, kan het feit verhullen dat computerwetenschappen, en dus ook computertechniek, een jonge discipline is. Elk decennium sinds de jaren negentig heeft de aandacht van het publiek getrokken met weer een nieuw digitaal wonder, beginnend met het internet, vervolgens sociale media en nu kunstmatige intelligentie. De steeds grotere impact van elke bovengenoemde vooruitgang op de economie heeft op zijn beurt de respectievelijke onderzoeksspots in de schijnwerpers gezet: het web bracht parallelle verwerking voort, Facebook bracht cloud computing voort, en hoewel het stof nog moet neerdalen, kan men niet ontkennen dat LLM's hardwareversnellers en nieuwe geheugengerichte technologieën zoals CXL en compute-in-memory hebben gestimuleerd.

Aan de ene kant is het een heel natuurlijk fenomeen dat een wetenschappelijke discipline wordt gedreven door haar toepassingen. Het is immers de mate waarin het publiek er baat bij heeft, waaraan een doorbraak zijn waarde ontleent. Aan de andere kant kunnen we ons niet onthouden afvragen: gaat deze vooruitgang misschien te snel? Hoe kunnen we er zeker van zijn dat alle vruchten geplukt zijn voordat we naar het volgende paradigma gaan? Intuïtie suggereert dat dit niet mogelijk is. Maar elk volgend paradigma bouwt voort op het vorige. Deze these is gebaseerd op de overtuiging dat er nog zinvol werk verricht moet worden in de basisprincipes van computersystemen.

Laten we beginnen met een definitie van wat we bedoelen met de term "computersysteem". Onderaan de abstractiehiërarchie bevindt zich de "hardware", die we zien als een rekeneenheid die interageert met een geheugenmodule. Bovenaan vinden we een gebruikersapplicatie die bestaat uit (i) broncode die een ontwikkelaar heeft geschreven en (ii) bibliotheken van derden die als afhankelijkheden zijn geïmporteerd, geschreven door andere ontwikkelaars. Gezamenlijk wordt de broncode van de applicatie omgezet in uitvoerbare binaire instructies met behulp van een compiler. Tussen het uitvoerbare bestand en de hardware van het systeem bevindt zich het besturingssysteem, dat de illusie wekt dat het om een speciale machine gaat, de werkelijke complexiteit van de hardware achter interfaces verbergt en ervoor zorgt dat alles veilig en efficiënt

verloopt.

De bovenstaande definitie is al lange tijd een comfortabele constructie: rekeneenheden zijn talrijk en heterogeen, geheugen kan adresruimten in andere machines omvatten en/of zelf heterogeen zijn, enzovoort. Maar een tweede noodzakelijke opmerking is dat het vereenvoudigde computersysteem desalniettemin het model blijft dat de meeste ontwikkelaars (indien van toepassing) gebruiken. Een redelijke manier om deze spanning op te lossen, is om naar onze mening de specifieke effecten te integreren die de uitvoering van een applicatie heeft op aspecten van het systeem die ons belangrijk lijken; met andere woorden, het gedrag ervan. Moderne systeemarchitecten zouden onbekende ontwikkelaars hun vereenvoudigde model moeten laten behouden, terwijl ze ondergronds werken om infrastructuur te leveren die zich in realtime aanpast aan de taken. Dit idee klinkt misschien synoniem aan dat van abstractie, dat net zo oud is als het computergebruik zelf – en terecht. Onze nadruk ligt op welke aspecten van het systeem de bovengenoemde abstracties zich moeten aanpassen.

Energieverbruik en geheugengebruik worden vaak over het hoofd gezien in de race om de uitvoeringstijd te minimaliseren, wat de belangrijkste zorg is van alle gebruikers. Om een concreet voorbeeld te geven, neem de alomtegenwoordige interface voor dynamische geheugentoewijzing, die bestaat uit GNU's mallocfunctiefamilie. Volgens de basisprincipes is geheugenfragmentatie de grootste vijand van elke geheugentoewijzer. Maar er is weinig onderzoek gedaan naar de definitie van fragmentatie, en ontwerpers van geheugentoewijzers richten zich liever op problemen die van invloed zijn op latentie of beveiliging. Een ander voorbeeld komt uit het deep learning-domein, waar workloads te maken hebben met een zogenaamde "geheugenmuur" – afgezien van de overmatige energiebehoefte. Dit gaat vooral over geheugenbandbreedte, maar deels ook over de enorme opslagcapaciteit die nodig is, met name voor de exploderende vraag naar diensten die draaien op machine learning.

Zo komen we bij de onderzoeksdoelstellingen van dit proefschrift, die allemaal gezien kunnen worden als bewerkingen op een relatief hoog abstractieniveau, waarbij applicatieprogrammeurs de complexe synergie tussen hun code, het besturingssysteem en de fysieke hardware niet willen 'zien':

- Doelstelling A: Een principieel, geïnformeerd onderzoek uitvoeren naar de interactie tussen werklast en toewijzer en de geheugenvoetafdruk.

- Doelstelling B: Een schaalbare meer optimale implementatie leveren voor statische geheugenplanning.

- Doelstelling C: Applicationtwikkelaars ondersteunen bij het beter evalueren van de impact van bron-naar-bron-transformaties.

#### **Extended Abstract in Greek**

Το γεγονός ότι η σύγχρονη κοινωνία εξαρτάται από τους υπολογιστές για να λειτουργήσει μπορεί να συσκοτίζει το γεγονός ότι η επιστήμη των υπολογιστών, και κατ΄ επέκταση η μηχανική υπολογιστών, είναι ένας νέος κλάδος. Κάθε δεκαετία από τη δεκαετία του 1990 έχει αιχμαλωτίσει την προσοχή του κοινού με ένα ακόμη ψηφιακό θαύμα, ξεκινώντας από το Διαδίκτυο, στη συνέχεια τα μέσα κοινωνικής δικτύωσης, και τώρα την τεχνητή νοημοσύνη. Ο συνεχώς αυξανόμενος αντίκτυπος κάθε προαναφερθείσας προόδου στην οικονομία έχει με τη σειρά του κατευθύνει τα αντίστοιχα ερευνητικά φώτα: ο Παγκόσμιος Ιστός γέννησε την παράλληλη επεξεργασία, το Φαςεβοοκ γέννησε το υπολογιστικό νέφος, και παρόλο που η σκόνη δεν έχει καταλαγιάσει ακόμα, δεν μπορεί κανείς να αρνηθεί την ώθηση που τα LLM έχουν δώσει στους επιταχυντές υλικού και στη νέα τεχνολογία με επίκεντρο τη μνήμη, όπως το CXL και ο υπολογισμός-εντός-μνήμης.

Από τη μία πλευρά, το να καθοδηγείται ένας επιστημονικός κλάδος από τις εφαρμογές του είναι ένα απολύτως φυσικό φαινόμενο. Σε τελική ανάλυση, η αξία μιας ανακάλυψης πηγάζει από τον βαθμό στον οποίο ωφελεί το κοινό. Από την άλλη πλευρά, δεν μπορούμε παρά να αναρωτηθούμε: μήπως αυτή η πρόοδος συμβαίνει υπερβολικά γρήγορα. Πώς μπορούμε να είμαστε βέβαιοι ότι όλοι οι καρποί έχουν συλλεχθεί πριν προχωρήσουμε στο επόμενο παράδειγμα. Η διαίσθηση υποδηλώνει ότι δεν μπορούμε. Αλλά κάθε επόμενο παράδειγμα χτίζεται πάνω στο προηγούμενο. Αυτή η διατριβή βασίζεται στην πεποίθηση ότι απομένει σημαντικό έργο να γίνει στα θεμελιώδη των υπολογιστικών συστημάτων.

Ας ξεχινήσουμε με έναν ορισμό του τι εννοούμε με τον όρο 'υπολογιστικό σύστημα'. Στο κάτω μέρος της ιεραρχίας αφαίρεσης βρίσκεται το 'υλικό' (hardware), το οποίο θεωρούμε ως μια υπολογιστική μονάδα που αλληλεπιδρά με μια μονάδα μνήμης. Στην κορυφή βρίσκουμε μια εφαρμογή χρήστη που αποτελείται από (ι) πηγαίο κώδικα που έγραψε ένας προγραμματιστής και (ιι) βιβλιοθήκες τρίτων που εισάγονται ως εξαρτήσεις, γραμμένες από άλλους προγραμματιστές.

Συλλογικά, ο πηγαίος κώδικας της εφαρμογής μετατρέπεται σε εκτελέσιμες δυαδικές εντολές με τη βοήθεια ενός μεταγλωττιστή. Ανάμεσα στο εκτελέσιμο αρχείο και το υλικό του συστήματος βρίσκεται το λειτουργικό σύστημα, το οποίο παρέχει την ψευδαίσθηση ότι πρόκειται για μια αποκλειστική μηχανή, κρύβει την πραγματική πολυπλοκότητα του υλικού πίσω από διεπαφές και φροντίζει για την ασφαλή και αποδοτική εκτέλεση των πάντων.

Για μεγάλο χρονικό διάστημα, ο παραπάνω ορισμός ήταν μια βολική επινόηση: οι υπολογιστικές μονάδες είναι πολλές και ετερογενείς, η μνήμη θα μπορούσε να περιλαμβάνει χώρους διευθύνσεων σε άλλες μηγανές ή/χαι να είναι η ίδια ετερογενής, και ούτω καθεξής. Αλλά μια δεύτερη απαραίτητη παρατήρηση είναι ότι, παρ΄ όλα αυτά, το απλοποιημένο υπολογιστικό σύστημα παραμένει το μοντέλο που χρησιμοποιείται (αν χρησιμοποιείται κάποιο) από τους περισσότερους προγραμματιστές. Ένας λογικός τρόπος για να επιλυθεί αυτή η ένταση είναι να ενσωματώσουμε στην οπτική μας τις συγκεκριμένες επιδράσεις που έχει η εκτέλεση μιας εφαρμογής σε πτυχές του συστήματος που μας ενδιαφέρουν με άλλα λόγια, τη συμπεριφορά της. Οι σύγχρονοι αρχιτέχτονες συστημάτων θα πρέπει να αφήνουν τους απλούς προγραμματιστές να διατηρούν το απλοποιημένο μοντέλο τους, ενώ εργάζονται υπογείως για να παρέχουν υποδομή που προσαρμόζεται στα καθήκοντά της σε πραγματικό χρόνο. Αυτή η ιδέα μπορεί να ακούγεται συνώνυμη με εκείνη της αφαίρεσης, η οποία είναι τόσο παλιά όσο και η ίδια η πληροφορική—και δικαίως. Η έμφασή μας αφορά προς ποιες πτυχές του συστήματος θα πρέπει να προσαρμόζονται οι προαναφερθείσες αφαιρέσεις.

Η κατανάλωση ενέργειας και το αποτύπωμα μνήμης συχνά παραβλέπονται στον αγώνα για την ελαχιστοποίηση του χρόνου εκτέλεσης, που αποτελεί το κύριο μέλημα όλων των χρηστών. Για να δώσουμε ένα συγκεκριμένο παράδειγμα, ας εξετάσουμε την πανταχού παρούσα διεπαφή δυναμικής εκχώρησης μνήμης που περιλαμβάνει την οικογένεια συναρτήσεων malloc της GNU. Εξ ορισμού, ο κατακερματισμός της μνήμης είναι ο κύριος εχθρός οποιουδήποτε εκχωρητή. Αλλά λίγη δουλειά έχει γίνει στον ορισμό του κατακερματισμού, και οι σχεδιαστές εκχωρητών προτιμούν να εστιάζουν σε προβλήματα που επηρεάζουν τον λανθάνοντα χρόνο ή την ασφάλεια. Ένα άλλο παράδειγμα προέρχεται από τον τομέα της βαθιάς μάθησης, όπου οι φόρτοι εργασίας αντιμετωπίζουν το λεγόμενο 'τείχος της μνήμης'—πέρα από τις υπερβολικές ενεργειακές απαιτήσεις. Αυτό αφορά κυρίως το εύρος ζώνης της μνήμης αλλά εν μέρει και την τεράστια χωρητικότητα αποθήκευσης που απαιτείται, ειδικά για την εκρηκτική ζήτηση για υπηρεσίες που βασίζονται στη μηχανική μάθηση.

Έτσι, φτάνουμε στους ερευνητικούς στόχους αυτής της διατριβής, οι οποίοι όλοι μπορούν να θεωρηθούν ως λειτουργίες σε ένα σχετικά υψηλό επίπεδο αφαίρεσης όπου οι προγραμματιστές εφαρμογών δεν θέλουν να 'βλέπουν' την πολύπλοκη συνέργεια μεταξύ του κώδικά τους, του λειτουργική συστήματος και του φυσικού

#### υλιχού:

- Στόχος Α: Διεξαγωγή μιας αρχειοθετημένης, τεκμηριωμένης μελέτης της αλληλεπίδρασης φόρτου εργασίας-εκχωρητή και του αποτυπώματος μνήμης.

- Στόχος Β: Παράδοση μιας κλιμακούμενης υλοποίησης SOTA για στατικό σχεδιασμό μνήμης.

- Στόχος Γ: Παροχή βοήθειας στους προγραμματιστές εφαρμογών για την καλύτερη αξιολόγηση του αντικτύπου των μετασχηματισμών από πηγαίοσε-πηγαίο κώδικα.

**Λέξεις κλειδιά:** στατικός σχεδιασμός μνήμης, δυναμική κατανομή μνήμης, διαχείριση μνήμης, καταμέτρηση ενέργειας, μηχανική λογισμικού

#### List of Abbreviations

**2DBP** Two-Dimensional rectangular Bin Packing. xxiv, xxvii, 31–35, 37, 40, 42, 92

**AI** Artificial Intelligence. 45

AMD Advanced Micro Devices Inc., 97

ARM Advaned RISC Machine Inc., 97

**BA** The boxing algorithm by Buchsbaum et al., xxvii, 50–55, 57, 60–62

CIA Change Impact Analysis. 89, 90

CPU Central Processing Unit. 87, 96

CSV Comma-Separated Values. 37, 38

CXL Compute Express Link. xi, xv, 1

**DDTR** Dynamic Data Type Refinement. 93

**DM** Decision Maker. 83, 85–88

**DRAM** Dynamic Random Access Memory. 19, 24, 26, 27, 29, 41, 98

**DSA** Dynamic Storage Allocation. xxix, 5, 8, 15–17, 19, 20, 22, 23, 25, 29, 31, 33, 42, 45–49, 51, 53, 54, 62, 92–94

**ECDF** Empirical Cumulative Distribution Function. xxvii, 22–24

**EOF** End Of File. 105

FBWM Fuzzy Best-Worst Method. 87

xx \_\_\_\_\_\_List of Abbreviations

FU Functional Unit. 52, 54, 62

GNU GNU's Not Unix. xii, xvi, 4, 20, 36–38, 45

**GPT** Generative Pre-trained Transformer. vii, ix, 2

**GPU** Graphics Processing Unit. 87

HPT Hierarchical Performance Testing. 16, 17, 19, 27

HTML HyperText Markup Language. 21

I/O Input-Output. 6, 103

IEEE Institute of Electrical and Electronics Engineers. 97

IGC Interval Graph Coloring. 49, 54, 61

IR Intermediate Representation. 99, 100, 104

JSON JavaScript Object Notation. 21

LLM Large Language Model. xi, xv, 1, 9, 93

**LLVM** Low-Level Virtual Machine. xxv, 96, 99, 100, 104, 105, 109

LTO Link-Time Optimization. xxiv, 20, 23, 24, 26, 29

MCDM Multiple-Criteria Decision Making. xxviii, 9, 10, 82, 83, 85–87, 89, 94

MMU Memory Management Unit. 19, 26, 29

N/A Not Applicable. 28

NFR Non-Functional Requirement. 9, 83, 86–88, 94

**NP** Non-deterministic Polynomial time. 8, 42

**OS** Operating System. xi, xii, 3–5, 38, 45, 49, 92, 93

PARSEC Princeton Application Repository for Shared-Memory Computers.

PC Personal Computer. xxix, 21, 25, 28

**PGO** Profile-Guided Optimization. xxiv, 20, 23, 24, 26, 29

LIST OF ABBREVIATIONS \_\_\_\_\_\_ xxi

PT Processor Tracing. xxv, xxviii, 96–99, 104, 105

**RAPL** Running Average Power Limit. xxv, xxviii, 15, 19, 26, 27, 96–98, 100,  $102-105,\ 109,\ 110$

RISC Reduced Instruction Set Computer. 110

**RSS** Resident Set Size. 7, 8, 31, 32, 37, 40–42, 92, 93

SoC System-on-Chip. 21–23, 28

**SOTA** State Of The Art. vii, xii, xvii, 6, 8–11, 46, 48, 51, 96

SSA Static Single Assignment. 100

XML eXtensible Markup Language. 21

## **Contents**

| Po | opula | rized Abstract              | vii   |

|----|-------|-----------------------------|-------|

| G  | ерорі | ulariseerde Samenvatting    | ix    |

| Αl | bstra | ct                          | хi    |

| В  | eknop | ote samenvatting            | xiii  |

| E> | ctend | ed Abstract in Greek        | χv    |

| Li | st of | Abbreviations               | xxi   |

| Li | st of | Symbols                     | xxiii |

| Co | onten | ts                          | xxiii |

| Li | st of | Figures                     | xxvii |

| Li | st of | Tables                      | xxix  |

| 1  | Intr  | oduction                    | 1     |

|    | 1.1   | Scientific Approach         | 3     |

|    | 1.2   | Research Objectives         | 5     |

|    | 1.3   | State of the Art            | 7     |

|    |       | 1.3.1 Objective A           | 7     |

|    |       | 1.3.2 Objective B           | 8     |

|    |       | 1.3.3 Objective C           | 9     |

|    | 1.4   |                             | 10    |

|    | 1 5   | Pomaining Toyt Organization | 10    |

xxiv \_\_\_\_\_\_ CONTENTS

|     | e Impact of Dynamic Storage Allocation on CPython Execution ne, Memory Footprint and Energy Consumption: An Empirical |

|-----|-----------------------------------------------------------------------------------------------------------------------|

| Stı |                                                                                                                       |

| 2.1 | Introduction                                                                                                          |

|     | 2.1.1 Contributions                                                                                                   |

| 2.2 | Method                                                                                                                |

| 2.3 | Experimental Setup                                                                                                    |

|     | 2.3.1 PGO, LTO sensitivity                                                                                            |

|     | 2.3.2 Configuration points                                                                                            |

|     | 2.3.3 Benchmarking script                                                                                             |

|     | 2.3.4 Platform independence                                                                                           |

| 2.4 | Results                                                                                                               |

| 2.5 | Discussion                                                                                                            |

| 2.6 | Limitations                                                                                                           |

| 2.7 | Conclusions                                                                                                           |

| Be  | ond RSS: Towards Intelligent Dynamic Memory Management                                                                |

| 3.1 | Introduction                                                                                                          |

| 3.2 | Background                                                                                                            |

| 3.3 | Proposed Method                                                                                                       |

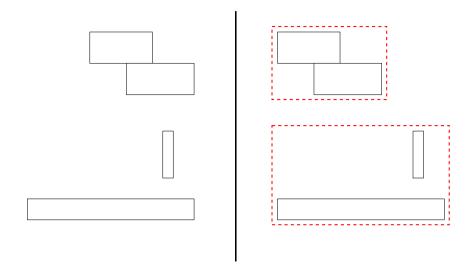

|     | 3.3.1 2DBP construction                                                                                               |

|     | 3.3.2 Fragmentation                                                                                                   |

| 3.4 | Evaluation                                                                                                            |

| 3.5 | Related Work and Comparison                                                                                           |

| 3.6 | Conclusion                                                                                                            |

| Fut | ureproof Static Memory Planning                                                                                       |

| 4.1 | Introduction                                                                                                          |

|     | 4.1.1 Against a Common Misunderstanding                                                                               |

|     | 4.1.2 Motivation and Related Work                                                                                     |

|     | 4.1.3 Contributions                                                                                                   |

| 4.2 | Dynamic Storage Allocation                                                                                            |

|     | 4.2.1 Elementary Cases                                                                                                |

|     | 4.2.2 Heuristics                                                                                                      |

| 4.3 | The Boxing Algorithm by Buchsbaum et al                                                                               |

|     | 4.3.1 Overview                                                                                                        |

|     | 4.3.2 Latent Invariants                                                                                               |

|     | 4.3.3 Critical Point Injection                                                                                        |

| 4.4 | Unboxing and Final Placement                                                                                          |

| 4.5 | Design and Implementation                                                                                             |

|     | 4.5.1 Interface                                                                                                       |

|     | 4.5.2 Input Representation                                                                                            |

|     | 4.5.3 Event Traversal                                                                                                 |

CONTENTS \_\_\_\_\_xxv

|   |      | 4.5.4           | Working with Different Lifetime Semantics 6                                                                              | 6        |

|---|------|-----------------|--------------------------------------------------------------------------------------------------------------------------|----------|

|   |      | 4.5.5           |                                                                                                                          | 7        |

|   |      | 4.5.6           | Prelude Analysis                                                                                                         | 8        |

|   |      | 4.5.7           | Fast and Correct Final Placement 6                                                                                       | 8        |

|   |      | 4.5.8           | Theorem 2 Simplification 6                                                                                               | 9        |

|   |      | 4.5.9           | Parallel Boxing                                                                                                          | 0        |

|   |      | 4.5.10          | Doors to Randomness                                                                                                      | 0        |

|   | 4.6  |                 |                                                                                                                          | 0        |

|   |      | 4.6.1           |                                                                                                                          | 3        |

|   |      | 4.6.2           | Question 3                                                                                                               | 3        |

|   |      | 4.6.3           | · ·                                                                                                                      | 5        |

|   |      | 4.6.4           | · ·                                                                                                                      | 5        |

|   | 4.7  | Discuss         |                                                                                                                          | 6        |

|   |      | 4.7.1           |                                                                                                                          | 6        |

|   |      | 4.7.2           | •                                                                                                                        | 9        |

|   |      | 4.7.3           |                                                                                                                          | 0        |

|   | 4.8  | Conclu          |                                                                                                                          | 1        |

|   |      | 0 0 0 - 0       |                                                                                                                          |          |

| 5 | Trar | slating         | Quality-Driven Code Change Selection to an Instance                                                                      |          |

|   | of N | <b>1ultiple</b> | Criteria Decision Making 8                                                                                               | 2        |

|   | 5.1  | Main A          | Approach                                                                                                                 | 3        |

|   |      | 5.1.1           | Decision-Making Core                                                                                                     | 5        |

|   | 5.2  | Prototy         | vpe                                                                                                                      | 6        |

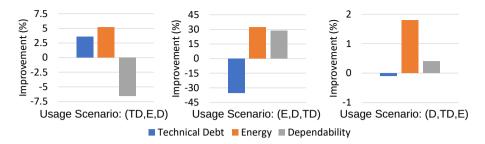

|   | 5.3  | Results         | 8                                                                                                                        | 7        |

|   |      | 5.3.1           | Threats to Validity                                                                                                      | 8        |

|   | 5.4  | Discuss         | sion and Future Work                                                                                                     | 9        |

|   | 5.5  | Conclu          | $sion \dots \dots$ | 0        |

|   |      |                 |                                                                                                                          |          |

| 6 |      | clusion         | _                                                                                                                        | 1        |

|   | 6.1  |                 | J                                                                                                                        | 1        |

|   | 6.2  | Future          | -                                                                                                                        | 2        |

|   |      | 6.2.1           | y y                                                                                                                      | 2        |

|   |      | 6.2.2           | v e                                                                                                                      | 3        |

|   |      | 6.2.3           | Source-level Model Construction 9                                                                                        | 4        |

| ^ | D-II | ala Da          | de Die de France Assessation                                                                                             | _        |

| Α |      |                 |                                                                                                                          | <b>5</b> |

|   | A.1  |                 |                                                                                                                          | 18       |

|   |      |                 |                                                                                                                          | 18<br>18 |

|   |      |                 |                                                                                                                          |          |

|   |      |                 |                                                                                                                          | 8        |

|   | 4.0  | A.1.4           | 9                                                                                                                        | 9        |

|   | A.2  | Method          |                                                                                                                          | -        |

|   |      | A.2.1           | Obstacles and workarounds                                                                                                | 1        |

|              | A.3   | Evaluation                      | 106 |  |  |  |

|--------------|-------|---------------------------------|-----|--|--|--|

|              |       | A.3.1 Experimental setup        | 107 |  |  |  |

|              |       | A.3.2 Results and discussion    | 109 |  |  |  |

|              | A.4   | Conclusions                     | 110 |  |  |  |

| В            | Cha   | pter 4 Addendum                 | 111 |  |  |  |

|              | B.1   | Lemma 1                         | 111 |  |  |  |

|              | B.2   | The Impossibility of Theorem 19 | 112 |  |  |  |

| Bibliography |       |                                 |     |  |  |  |

| Lis          | st of | Publications                    | 129 |  |  |  |

# **List of Figures**

| 1.1 |                                                                        |  |  |  |  |  |  |

|-----|------------------------------------------------------------------------|--|--|--|--|--|--|

|     | cial Intelligence"                                                     |  |  |  |  |  |  |

| 1.2 | Simplified computer system model                                       |  |  |  |  |  |  |

| 1.3 | Objectives-extended computer system model                              |  |  |  |  |  |  |

| 1.4 | Thesis organization, research path, objective synergies 13             |  |  |  |  |  |  |

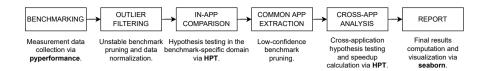

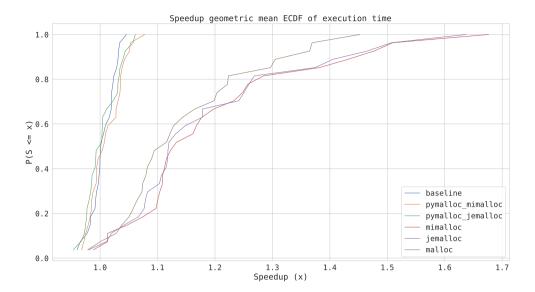

| 2.1 | CPython DSA methodology                                                |  |  |  |  |  |  |

| 2.2 | CPython DSA experiment setup                                           |  |  |  |  |  |  |

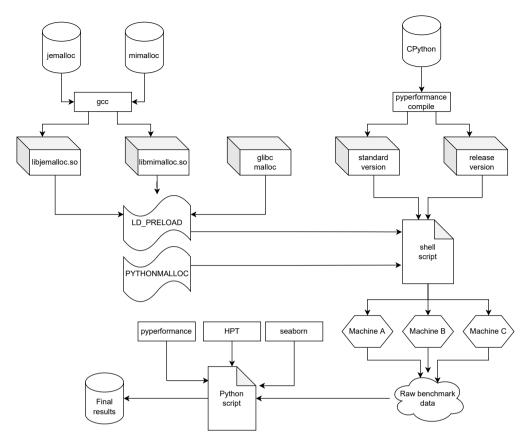

| 2.3 | Memory footprint ECDF, embedded, release                               |  |  |  |  |  |  |

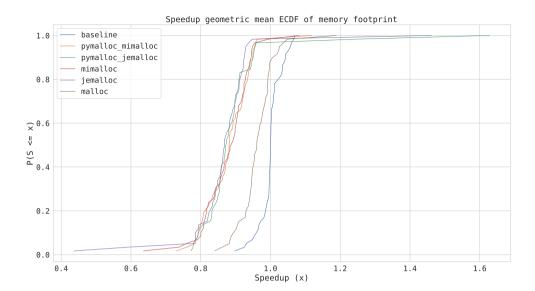

| 2.4 | Time ECDF, embedded, standard                                          |  |  |  |  |  |  |

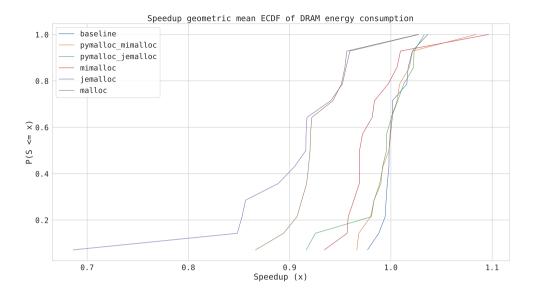

| 2.5 | Energy ECDF, server, release                                           |  |  |  |  |  |  |

| 2.6 | Core nergy ECDF, laptop, standard                                      |  |  |  |  |  |  |

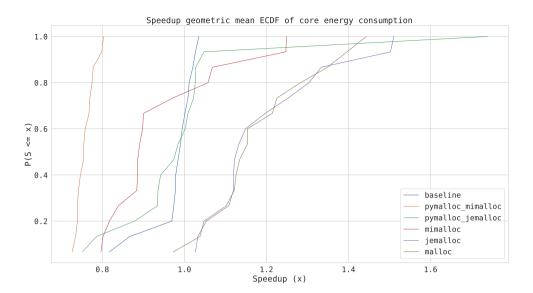

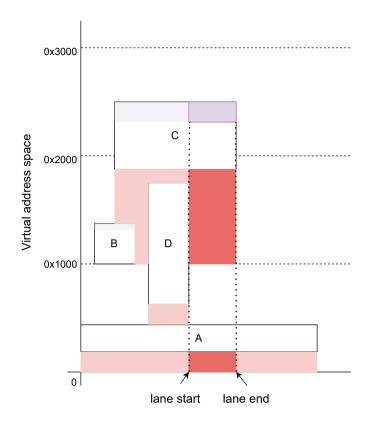

| 3.1 | 2DBP example                                                           |  |  |  |  |  |  |

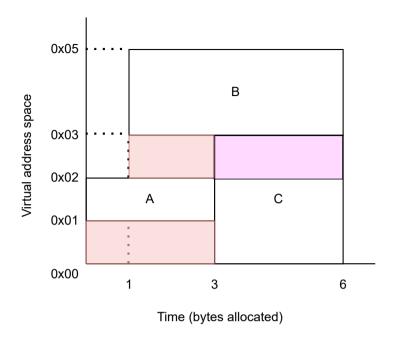

| 3.2 | Approach for studying Objective #3 35                                  |  |  |  |  |  |  |

| 3.3 | Gap identification algorithm                                           |  |  |  |  |  |  |

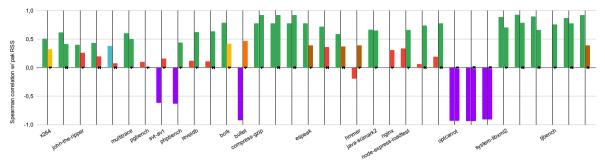

| 3.4 | Objective #3 main results                                              |  |  |  |  |  |  |

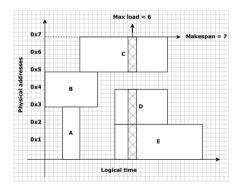

| 4.1 | A more detailed illustration of the dynamic storage allocation         |  |  |  |  |  |  |

|     | (DSA) problem. This instance comprises five buffers and a              |  |  |  |  |  |  |

|     | (suboptimal) solution, i.e., offset assignment to each of the buffers, |  |  |  |  |  |  |

|     | is depicted                                                            |  |  |  |  |  |  |

| 4.2 | Interval Graph Coloring                                                |  |  |  |  |  |  |

| 4.3 | First-fit placement                                                    |  |  |  |  |  |  |

| 4.4 | BA main idea                                                           |  |  |  |  |  |  |

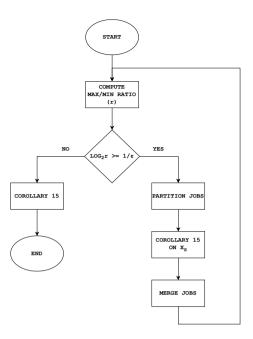

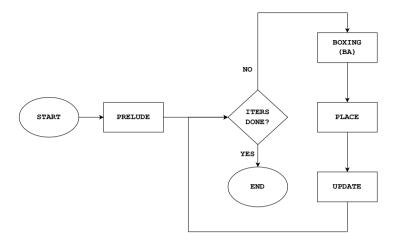

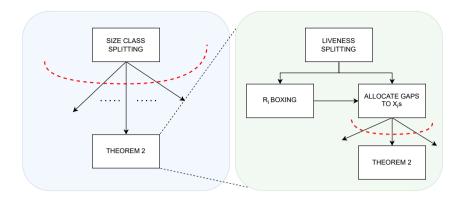

| 4.5 | T16 flow diagram                                                       |  |  |  |  |  |  |

| 4.6 | Unboxing pseudocode                                                    |  |  |  |  |  |  |

| 4.7 | idealloc flow diagram                                                  |  |  |  |  |  |  |

| 4.8 | Parallelism opportunities in idealloc                                  |  |  |  |  |  |  |

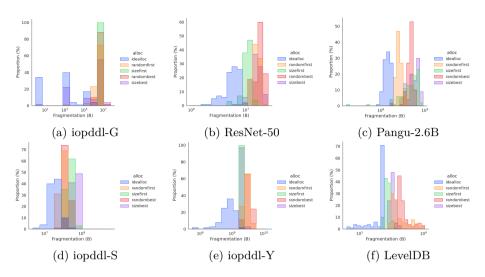

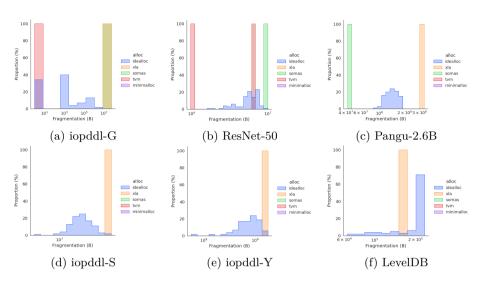

| 4.9 | Fragmentation histograms against heuristics                            |  |  |  |  |  |  |

xxviii \_\_\_\_\_\_LIST OF FIGURES

| 4.10                                                             | Fragmentation histograms against the SOTA                     |     |  |  |  |  |  |

|------------------------------------------------------------------|---------------------------------------------------------------|-----|--|--|--|--|--|

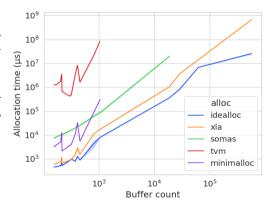

| 4.11 idealloc's single-iteration latency versus its competition, |                                                               |     |  |  |  |  |  |

|                                                                  | function of total buffer count. Note the interference graph's |     |  |  |  |  |  |

|                                                                  | impact at the far end of the curve                            | 75  |  |  |  |  |  |

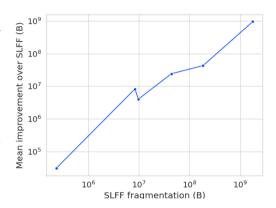

| 4.12                                                             | idealloc's mean improvement over its bootstrap heuristic as a |     |  |  |  |  |  |

|                                                                  | function of the bootstrap heuristic's own fragmentation       | 76  |  |  |  |  |  |

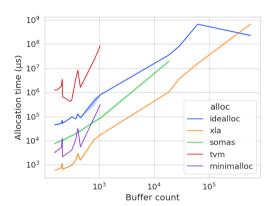

| 4.13                                                             | idealloc's total latency versus its competition               | 78  |  |  |  |  |  |

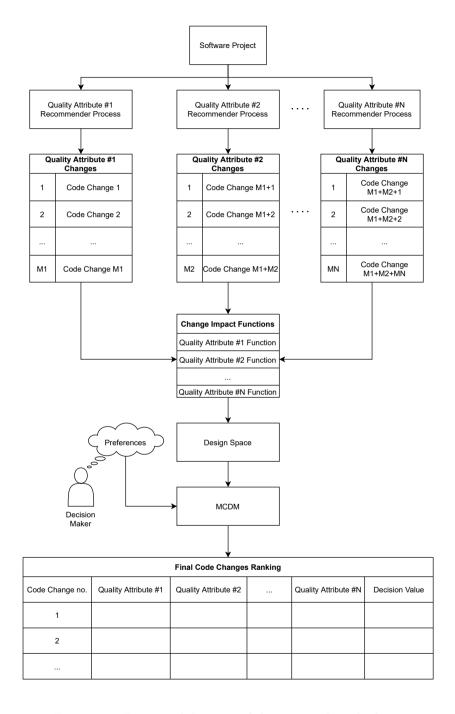

| 5.1                                                              | Functional diagram of the proposed method                     | 84  |  |  |  |  |  |

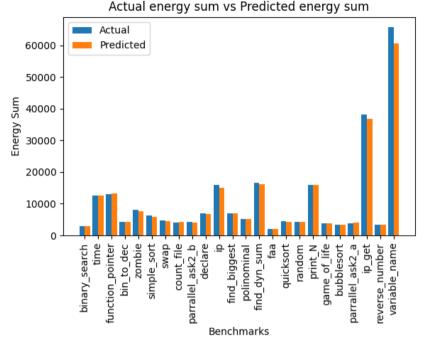

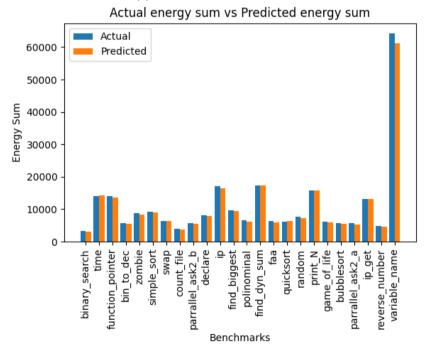

| 5.2                                                              | MCDM prototype results                                        | 88  |  |  |  |  |  |

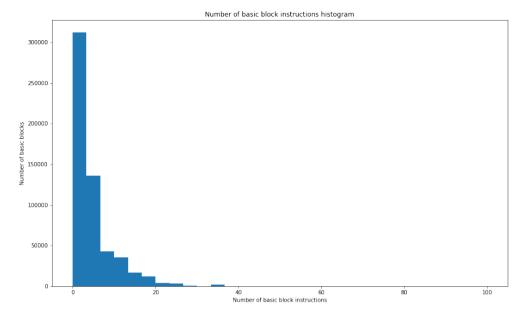

| A.1                                                              | Basic block instructions histogram                            | 99  |  |  |  |  |  |

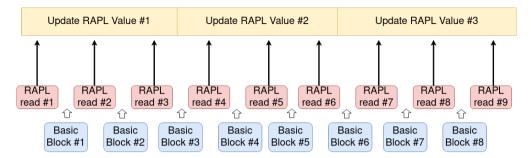

|                                                                  | Effect of RAPL's low refresh rate                             | 100 |  |  |  |  |  |

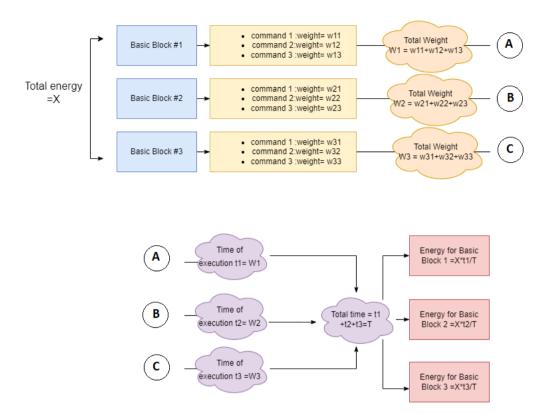

| A.3                                                              | Throughput-based energy splitting                             | 101 |  |  |  |  |  |

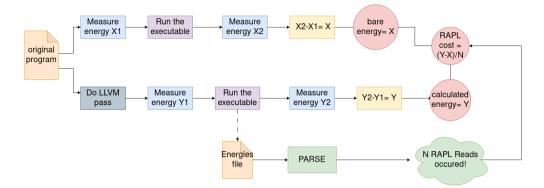

| A.4                                                              | RAPL-read overhead measurement                                | 103 |  |  |  |  |  |

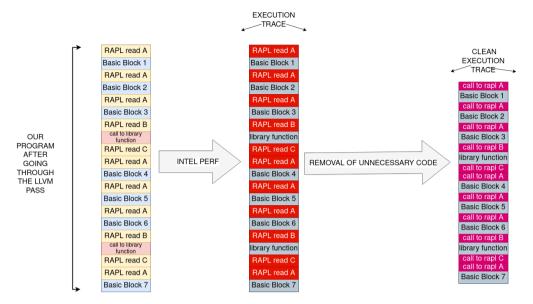

| A.5                                                              | PT-enabled external code energy accounting                    | 104 |  |  |  |  |  |

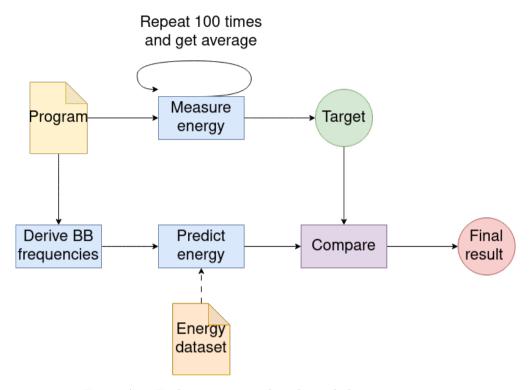

| A.6                                                              | Objective #2 evaluation method                                | 106 |  |  |  |  |  |

| A.7                                                              | Objective #2 evaluation results                               | 108 |  |  |  |  |  |

|                                                                  |                                                               |     |  |  |  |  |  |

# **List of Tables**

| 2.1 | CPython DSA materials                                             | 19  |

|-----|-------------------------------------------------------------------|-----|

| 2.2 | CPython DSA benchmarks                                            | 21  |

| 2.3 | Server CPython DSA speedups                                       | 27  |

| 2.4 | PC CPython DSA speedups                                           | 28  |

| 2.5 | Embedded CPython DSA speedups                                     | 28  |

| 3.1 | Elementary malloc/free transforms                                 | 36  |

| 3.2 | malloc trace file structure                                       | 37  |

| 4.1 | Findings and remedies applied to BA's FUs                         | 62  |

| 4.2 | Experimental setup used for evaluating idealloc                   | 71  |

| 4.3 | Fragmentation measurements and corresponding points               | 74  |

| 5.1 | Design space sample                                               | 85  |

| A.1 | Machines used for evaluation                                      | 107 |

|     | A qualitative comparison of our tool versus the state-of-the-art. | 109 |

#### Chapter 1

#### Introduction

The fact that modern society depends on computers in order to function may obscure the fact that computer science, and consequently computer engineering, is a young discipline. To the extent that one can trust Wikipedia<sup>1</sup>, we know for example that humans have been studying numbers for more than 5,000 years; geometry 4,000 (though it took more than the first thousand before flourishing); anatomy 3,000 and so on. However, the paper which introduced the notion of the computer in the sense of a flexible information-processing machine, i.e., Alan Turing's seminal work on Hilbert's Entscheidungsproblem [118], needs another eleven years to become a century old. And as a reminder of the non-trivial amount of effort separating the world of *notions* from the *physical* world, almost a decade had to pass before the genius of John von Neumann turned Turing's concepts into a real machine [120].

But reality did not give our discipline time to mature before the popularity of its applications exploded. Each decade since the 1990s has captivated the public's attention with yet another digital miracle, starting with the Internet, then social media, and now artificial intelligence. The ever growing impact of each aforementioned advancement on the economy has in return directed the respective research spotlights: the Web spawned parallel processing, Facebook spawned cloud computing, and though the dust has yet to settle, one cannot deny the push that LLMs have given to hardware accelerators and novel memory-centric technology such as CXL and compute-in-memory. Note that providing and accurate history of progress in computing is out of this dissertation's scope. The claims in this paragraph stem from our judgement, to the extent that it has been informed from spending the past few years thinking about computers.

$<sup>^{1}</sup> https://en.wikipedia.org/wiki/Timeline\_of\_scientific\_discoveries$

2 \_\_\_\_\_\_\_INTRODUCTION

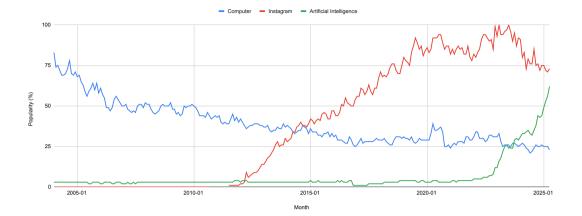

Figure 1.1: Popularity comparison of the terms "Computer", "Instagram" and "Artificial Intelligence", as searched on Google worldwide. Chart extracted via Google Trends.

One cannot deny, however, that there have been trends and attractors of the community's collective interest.

On the one hand, a scientific discipline being driven by its applications is a most natural phenomenon. It is after all the degree to which it benefits the public from where a breakthrough draws its value. On the other hand, we cannot help but wonder: could this progress be happening too fast? How can we be certain that all fruits have been reaped before moving on to the next paradigm? Intuition suggests we cannot. But each next paradigm is built on top of the previous one. So who is to blame for the fact that training ChatGPT-3 requires as much energy as 130 American homes consume in a year [16]? If it were something inherent in deep learning, DeepSeek would not have been able to make headlines all around the world with a model both better and 10x more efficient than its competition<sup>2</sup>.

According to Figure 1.1, ten years have passed since computers themselves were as interesting to the world as Instagram. At the time of writing, AI is as popular as the machines it runs on were fifteen years ago. In fact one can observe a slow yet steady decline in the amount of attention that we pay to what has become the world's infrastructure. This thesis is founded upon the belief that meaningful work remains to be done in the fundamentals of

$<sup>^2</sup>$ https://www.tomshardware.com/tech-industry/artificial-intelligence/deepseeks-ai-breakthrough-bypasses-industry-standard-cuda-uses-assembly-like-ptx-programming-instead

SCIENTIFIC APPROACH \_\_\_\_\_\_\_

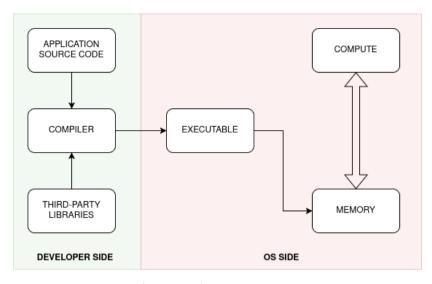

Figure 1.2: A (simplified) model of a computer system.

computer systems.

# 1.1 Scientific Approach

Let us begin with a definition of what we mean with the term "computer system". Figure 1.2 serves as an aid. At the bottom of the abstraction hierarchy (right side of the figure) lies the "hardware", which we view as a compute unit interacting with a memory module. At the top (left side) we find a user application consisting of (i) source code that a developer wrote and (ii) third-party libraries imported as dependencies, written by other developers. Collectively, the application's source code is turned into executable binary instructions via the help of a compiler. In between the executable and the system's hardware lies the OS, which provides the illusion that this is a dedicated machine, hides the hardware's actual complexity behind interfaces, and takes care of running everything safely and efficiently.

The first remark to be made at this point is that, for a long time now, the above definition has been a comfortable fabrication [30]: compute units are many and heterogeneous, memory could encompass address spaces in *other* machines and/or be heterogeneous itself, and so on. But a second necessary remark is that, nevertheless, the simplified computer system of Figure 1.2 remains the model used (if any) by most developers today [12]. A reasonable means to

4 \_\_\_\_\_\_ INTRODUCTION

resolve this tension is to incorporate in our view the specific effects that an application's execution brings upon aspects of the system that we care about; in other words, its behavior. Modern system architects should let laymen developers retain their simplified model, while working underground to deliver infrastructure that adapts to its tasks in real time. This idea may sound synonymous to that one of abstraction, which is as old as computing itself—and rightfully so. Our emphasis regards what aspects of the system should the aforementioned abstractions adapt toward.

Energy consumption and memory footprint are often overlooked in the race to minimize execution time, which is the chief concern of all users [104, 10]. To give a concrete example, consider the ubiquitous dynamic memory allocation interface comprising GNU's malloc family of functions. The largest part of the research presented in this thesis was sparked by a seminal survey on malloc published thirty years ago [121]. The main point of that survey was that, by first principles, memory fragmentation is the main enemy of any allocator. Moreover, it is a consequence of the particular interaction between the program and the allocator. Last but not least, a quantitative definition of it is elusive. But little work on defining fragmentation has been conducted ever since, and allocator designers prefer to focus on problems impacting latency such as thread contention [25, 89], producer-consumer relationships [79], and language runtimes [76]. And yet, as both this thesis and other works have shown, the interaction between a specific application and a memory allocator significantly impacts the resulting energy consumption and process memory footprint. Another example stems from the deep learning domain, where workloads are facing a so-called "memory wall" [39]—apart from the excessive energy requirements mentioned already. This is mostly about memory bandwidth but partly also about the massive storage capacity needed, especially for exploding demand for machine learningpowered services.

At this point we have laid the ground to elaborate on the terms comprising the title of this thesis. By doing so, we hope to achieve a clear description of our scientific approach. Let us start parsing in reverse: the title suggests that our work takes place in **native contexts**. We are interested in no further virtualization than that imposed by the OS on a single machine. Higher-level abstractions such as virtual machines and distributed computation will be viewed, if present, as traditional OS processes interacting with the host's hardware. It was this narrow scope that we were referring to earlier as "fundamentals"; in other words, operations and interfaces that are ubiquitous in computing. By positioning our research in this way, we hope to provide insights and tools with as wide an applicability as possible.

In this context, we want to **enable** optimizations. We have witnessed more than once during the course of our studies the presentation of research that

takes *imaginary* capabilities as a given. We have done so ourselves as the second Chapter will show. But there is a world of difference between building what one imagined and building on top of it. We are interested in the first half. Our claim of "enabling" optimizations is a subtle way of acknowledging our failure to complete building what we imagined, but we nevertheless deliver a couple of concrete first steps.

The optimizations at hand will be **behavior-based**. We allude here to the notion that there is no free lunch in today's systems, and probably there never was. Workloads have characteristics that make them distinct from one another. When expressed on different hardware platforms, their impact on performance is also different. It is our firm belief that such characteristics have to be exploited en route to optimization. The main characteristic we will be dealing with is dynamic memory allocation.

The rest of the title, i.e., specific ties to energy consumption and memory footprint, will be unpacked in the background sections of each Chapter.

# 1.2 Research Objectives

Thus, we are brought to the research objectives of this dissertation, all of whom can be viewed as operations at a relatively high abstraction level where application programmers do not want to "see" the complex synergy between their code, the OS and the physical hardware.

#### Objective A

Conduct a principled, informed study of workload-allocator interaction and memory footprint.

Dynamic memory allocation is a both ubiquitous and fundamental operation. It is telling of our epistemic status around it that in performance-critical situations such as real-time embedded systems, dynamic memory allocation is avoided as if it posed existential risks. The mystery at the heart of the problem is memory fragmentation, the amount of memory beyond a program's needs that was wasted. Very little work around taming or even defining fragmentation exists. We ascribe this situation to an up-to-now lack of tools for describing the source of fragmentation, which is the interaction between a workload's requests for memory and the corresponding allocator's placement policy. We show that the bin-packing variant of DSA is a perfect fit for the task, and propose a novel fragmentation measure on top of it.

6 \_\_\_\_\_\_INTRODUCTION

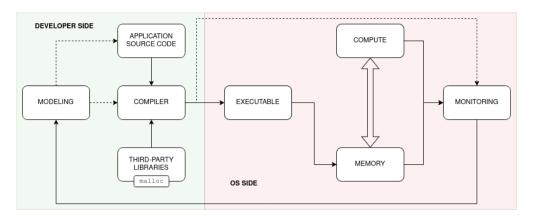

Figure 1.3: Computer system model extended with components and relationships that this thesis treats. Bold arrows stand for I/O relationships. Dotted arrows for assistance. Objective A focuses on malloc, a fundamental operation closely tied to program behavior and affecting both energy consumption and memory footprint. Objective B offers a tool for investigating the theoretical limits of malloc by providing a scalable, SOTA off-line oracle for it. Objective C adopts a bird's eye view of the application development lifecycle and proposes an agnostic decision-making framework for source-level code transformations leveraging lower-level information.

#### Objective B

Deliver a scalable SOTA implementation for static memory planning.

Future allocators must be informed by "perfect" solutions to the allocation patterns of the workloads they face. These solutions must by definition have access to the entire allocation history of a process. The task of producing such solutions is *static memory planning*. Existing implementations are either not scalable or excessively wasteful. We come up with an implementation that exhibits none of those hindrances. We achieve this goal by (i) building on top of the best known algorithm to date, (ii) discovering and reinforcing its weak spots, and (iii) leveraging modern systems programming techniques to deliver a safe, parallel implementation.

Our implementation's source code and the benchmarks used for evaluation are publicly available on  ${\it GitHub}.$

STATE OF THE ART \_\_\_\_\_\_ 7

#### Objective C

Provide application developers with assistance to better evaluate the impact of source-to-source transformations.

Developers writing software for a specific computer system do not have the ability to change the system itself. They thus embark on optimizing applications through source-to-source transformations. Due to the underlying complexity of both the system and the application, these transformations are bound to affect energy consumption and memory footprint in non-trivial ways. But additional goals may be put on the optimization task, such as technical debt elimination or security enhancements. To make their final decision, the user must operate on information linking each candidate transformation to changes in each aspect of interest. We provide a structured way of handling such information.

#### 1.3 State of the Art

We will describe the state of the art per objective, and identify the gaps addressed in each case. Be advised that parts of the following sections have been copied from the author's list of publications.

#### 1.3.1 Objective A

For this objective, we aim to open the black box standing between workload-allocator interaction and memory fragmentation. This link was first put to paper by Wilson et. al in their seminal 1995 survey on dynamic memory allocation [121]. A couple of years later, some of the authors returned with the most comprehensive study of fragmentation to date [57]. While acknowledging that many possible definitions exist, they focused on two and concluded that fragmentation is practically "solved". Their experiments, however, were trace-based simulations operating entirely on virtual memory and did not take *physical memory* into consideration.

In most recent times, practitioners have converged to a coarse view of fragmentation which is based on RSS, that is, the amount of physical memory consumed by a process (which is *different* from the amount of memory it allocated due to demand paging). Using two different allocators on the same workload, they conclude that the one yielding less fragmentation is the one resulting in smaller peak RSS [106, 81, 50]. We find this stance rather hazardous, since it (i) obscures the fact that allocators operate on *virtual* memory, (ii) and

8 \_\_\_\_\_\_ INTRODUCTION

mixes together the impact of an allocator's policy and its *implementation*, i.e., the data structures it internally uses for book-keeping.

Yet, as novel work occasionally shows, fragmentation remains elusive [87]: lacking a principled methodology to quantify it, we are adopting indirect approaches to merely inspect its effects. Chapter 2 motivates our focus on dynamic memory allocation by showing the impact of different allocators on the CPython runtime's energy consumption and memory footprint. Chapter 3 proposes a novel, structured view of workload-allocator interaction based on DSA, and a fragmentation measure which demonstrably correlates with RSS without sacrificing placement policy observability.

- Gap in the SOTA: An agreed-upon representation of memory fragmentation as incurred by dynamic memory allocators.

- Contribution: A demonstration of the suitability of DSA to capture fragmentation, and open source tools to study it further.

#### 1.3.2 Objective B

The mathematical formulation of dynamic memory allocation is DSA. It is an NP-complete combinatorial optimization task that is a variation of bin packing. Our goal in this objective is to implement a golden standard for DSA.

A summary of theoretical work on DSA up to two decades ago can be found in the Introduction section of Buchsbaum et al. [13] The same paper presents the SOTA algorithm for the general case. Kierstead and Saoub have introduced generalized DSA, which allows some spatial overlap between rectangles [62]. Related but different problems are the Storage Allocation Problem [91], 2D Geometric Knapsack [45] and Unsplittable Flow on a Path [42].

As far as implementations go, Maas et al have proposed hybridizing heuristics and meta-optimization with TelaMalloc [83]. Moffitt improved upon TelaMalloc with an isomorphism between DSA and lattice theory [90]. Lamprou et al. introduced a heuristics-based solution with additional constraints [73].

Such recent efforts have been motivated by the memory-saving benefits of applying DSA to deep learning compilers for both training and inference. As a result, evaluation sections are always limited in that context. A rigorous evaluation with a focus on general-purpose DSA has not been conducted. We undertake this task in Chapter 4, along with contributing a golden standard implementation.

STATE OF THE ART \_\_\_\_\_\_\_9

• Gap in the SOTA: A scalable, efficient and effective implementation for static memory planning. A rigorous evaluation of existing solutions. Necessary conceptual and technical insights for future work.

• Contribution: All of the above.

#### 1.3.3 Objective C

The task at hand is evaluating a set of candidate code changes under a set of oftentimes conflicting criteria of software quality.

The term "software quality" refers to a program's characteristics outside its functional specification. Several standards have been proposed, the most popular of which is ISO/IEC 25010<sup>3</sup>. Prior art does not exhibit any consensus on the meaning of the term. In their 1996 survey on software quality, Osterweil et al. limit its notion to the consistency between a program's intended and actual behavior [98]. Cavano and McCall recognized as early as 1978 the inherent difficulty in both defining and measuring software quality, which should in their opinion be application-specific [15]. Since we shall be taking software quality criteria as a given, the key insight from this paragraph is that the process we are after must be extremely flexible.

In particular, we are interested in the impact that source code changes, i.e., source-to-source transformations, have on aspects orthogonal to the program's function. Such aspects have been named NFRs in the literature [41, 86, 5, 54]. We treat the problem of deciding upon a pool of heterogeneous code changes, i.e., not all of them improving the same NFR. Similar works exist. For instance, Ouni et al. perform an automated search in refactoring space, adopting a genetic algorithm to evaluate possible code changes [99]. Such search-based formulations have evolved to incorporate LLMs in the decision making process [33]. We refrain from automated methods since it is a known fact that teams of developers prefer manual actions when refactoring [93].

Our work in Chapter 5 thus provides decision support for the manual application of NFR-targeting code changes. To the best of our knowledge, the closest intellectual relative is Zhao and Hayes' work on rank-based decision support [124]. The key difference of our contribution is that it does not subscribe to any particular type of NFR, and formulates the problem as an instance of MCDM [55]. For instance, there is a whole line of work focusing on the economic impact of refactoring, mostly technical debt [14, 28, 29, 26, 32].

<sup>&</sup>lt;sup>3</sup>https://iso25000.com/index.php/en/iso-25000-standards/iso-25010

10 \_\_\_\_\_\_ INTRODUCTION

• Gap in the SOTA: Generic formulation of source-to-source transformations targeting *arbitrary* criteria.

• Contribution: View refactoring as MCDM.

## 1.4 A Note on Memory Fragmentation

A main theme across a large portion of this text is memory fragmentation. As already noted, multiple quantitative definitions of it exist. A commonly agreed upon qualitative definition is "memory that is available in aggregate, but not contiguous". In order to avoid developing further confusion around the phenomenon, we give here a brief descriptions of the two perspectives from which we approach fragmentation in this dissertation. Chapter 3 introduces an aggregate, page-local definition aligned with the demand paging mechanism of Linux. In that context, we were interested in summarizing workload-allocator interaction across time into a single number, which would hopefully correlate with the real memory footprint. Our definition is good to the extent that the expected monotonic relationship does indeed appear, but better alternatives could always exist. Chapter 4 adopts a much more conservative approach, measuring the amount of memory wasted as the difference between maximum memory allocated and maximum memory usage. This definition is useful for contexts such as the real, contiguous, physical address space of hardware accelerators with no virtualization. For the reasons explained in that Chapter, we are confident that this definition is the most appropriate for setups where memory is not virtual, i.e., contiguous memory pages correspond to contiguous memory.

## 1.5 Remaining Text Organization

The main body of this dissertation is organized as follows. Chapter 2 describes the case study initializing Objective A, and Chapter 3 demonstrates the core of our work there. Chapter 4 is an extensive account of how we achieved Objective B. Chapter 5 showcases our work on Objective C. A global discussion on the above and proposed future work are the matter of Chapter 6.

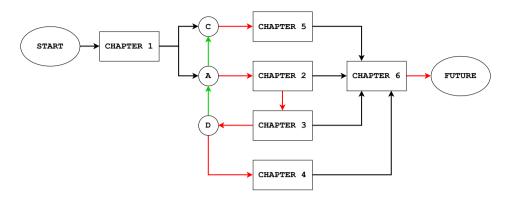

We depict the relationships between objectives, chapters and stages during our research trajectory on Figure 1.4. In the beginning, our intention was to (i) study the memory footprint and energy consumption of some fundamental operation and (ii) investigate ways of assisting the *integration* of systems-derived insights to the application development lifecycle. This spawned Objectives A and C, on

Figure 1.4: An illustration of the organization of this text, annotated with extra information. Ellipses are initial and "terminal" states. Circles are research objectives. Rectangles are thesis chapters. Black arrows represent logical implication. Red arrows indicate the research trajectory followed. Last but not least, green arrows indicate synergies between objectives. For instance Objective A can, by assisting the construction of high-level models around different malloc implementations, inform Objective C.

which we worked in parallel. The motivational study of malloc and CPython (Chapter 2) led us to the bin packing representation of workload-allocator interaction (Chapter 3). We were then led to investigate the malloc-related bin packing SOTA, and our work there is presented in Chapter 4.

# Chapter 2

# The Impact of Dynamic Storage Allocation on CPython Execution Time, Memory Footprint and Energy Consumption: An Empirical Study

This Chapter is a verbatim copy of the author's publication cited below:

LAMPRAKOS, C. P., PAPADOPOULOS, L., CATTHOOR, F., AND SOUDRIS, D. The impact of dynamic storage allocation on cpython execution time, memory footprint and energy consumption: An empirical study. In *Embedded Computer Systems: Architectures, Modeling, and Simulation* (Cham, 2022), A. Orailoglu, M. Reichenbach, and M. Jung, Eds., Springer International Publishing, pp. 219–234

CPython is the reference implementation of the Python programming language. Tools like machine learning frameworks, web development interfaces and scientific computing libraries have been built on top of it. Meanwhile, single-

board computers are now able to run GNU/Linux distributions. As a result CPython's influence today is not limited to commodity servers, but also includes edge and mobile devices. We should thus be concerned with the performance of CPython applications. In this spirit, we investigate the impact of dynamic storage allocation on the execution time, memory footprint and energy consumption of CPython programs. Our findings show that (i) CPython's default configuration is optimized for memory footprint, (ii) replacing this configuration can improve performance by more than 1.6x and (iii) application-specific characteristics define which allocator setup performs best at each case. Additionally, we contribute an open-source means for benchmarking the energy consumption of CPython applications. By employing a rigorous and reliable statistical analysis technique, we provide strong indicators that most of our conclusions are platform-independent.

#### 2.1 Introduction

Today Python is one of the most popular high-level programming languages<sup>1</sup>. Its reference implementation is CPython<sup>2</sup>. Python source code is usually compiled to bytecode and executed on the CPython virtual machine, which is implemented in C.

CPython is often criticized for its performance, which has previously been compared to that of other programming languages [103]. The results do indeed validate the criticism, but Python's extreme popularity cannot be ignored. Several Python libraries have dominated the programming landscape. SciPy [119] has democratized scientific computing, scikit-learn [102] has done the same for introductory machine learning projects, Pytorch [8] has almost monopolized deep learning pipelines in both academia and the industry.

CPython is not deployed just on servers or home computers, but is becoming all the more present on embedded systems<sup>34</sup>. This is largely owed to the availability of cheap single-board computers (SBCs) like the Raspberry  $\mathrm{Pi}^5$  and the BeagleBone<sup>6</sup>, which are capable of running GNU/Linux.

We thus consider improving the execution time, memory footprint and energy consumption of CPython applications a worthwhile endeavor. We believe lowhanging fruit should be reaped before having to examine CPython's internals.

<sup>&</sup>lt;sup>1</sup>https://insights.stackoverflow.com/survey/2020/

<sup>&</sup>lt;sup>2</sup>https://github.com/python/cpython

<sup>&</sup>lt;sup>3</sup>https://wiki.python.org/moin/EmbeddedPython

<sup>&</sup>lt;sup>4</sup>https://www.zerynth.com/blog/the-rise-of-python-for-embedded-systems/

<sup>&</sup>lt;sup>5</sup>https://www.raspberrypi.com/

<sup>&</sup>lt;sup>6</sup>https://beagleboard.org/bone

Consequently, we focus on configurations exposed by the language runtime that cause observable, non-random effects on performance<sup>7</sup>.

As regards the particular configuration under study, we picked DSA<sup>8</sup> for the following reasons: firstly, CPython does provide the option of configuring it. Secondly, DSA is a cornerstone operation used by most real-world programs and as a result demands attention. Finally, it is not well-understood [121], so treating it as a black box and benchmarking several versions of it may yield useful results.

#### 2.1.1 Contributions

We conducted a reliable, statistically rigorous empirical study of DSA's impact on the execution time, memory footprint and energy consumption of CPython programs. Our first contribution is providing quantitative answers to the research questions: (I) to what extent can a CPython application's performance with respect to execution time, memory footprint and energy consumption be improved by modifying the runtime's DSA configuration? (II) how much do optimizations in the runtime itself affect the expected improvement? (III) are performance improvements sensitive to application-specific characteristics? By addressing these questions, we pave the way towards predicting the optimal DSA configuration for a given application without resorting to brute-force methods. Note, however, that for the purposes of this Chapter, we are only interested in acquiring a coarse impression of whether DSA can have substantial impact. Transitioning from such an epistemic status to a methodology for picking the optimal allocator per case is non-trivial and, as our results show, extremely case-sensitive. Future practitioners' best hopes lie, in our opinion, in solutions that adapt in a fully dynamic way to the characteristics of the access patterns in the currently present application phase.

Our second contribution is an open-source modification of the pyperformance and pyperf packages, which enables the benchmarking of Python programs with respect to energy consumption. It can be used on all Linux-running machines featuring Intel's RAPL power capping interface [22, 47]. All of our results and accompanying code are publicly available on GitHub<sup>9</sup>.

<sup>&</sup>lt;sup>7</sup>From this point onward, we will use the term "performance" to refer collectively to the set of execution time, memory footprint and energy consumption. See Section ?? for details. <sup>8</sup>In this Chapter, DSA stands for "traditional" dynamic memory allocation in operating systems.