### Εθνικό Μετσοβίο Πολυτέχνειο

ΣΧΟΛΗ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ ΚΑΙ ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ ΤΟΜΕΑΣ ΤΕΧΝΟΛΟΓΙΑΣ ΠΛΗΡΟΦΟΡΙΚΗΣ ΚΑΙ ΥΠΟΛΟΓΙΣΤΩΝ ΕΡΓΑΣΤΗΡΙΟ ΜΙΚΡΟΫΠΟΛΟΓΙΣΤΩΝ ΚΑΙ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ

# LUMAX: A $\underline{LU}$ T-Based $\underline{M}$ ixed-Precision $\underline{Acc}$ elerator for LLM Inference on the Edge

A LUT-Based Mixed-Precision GeMM Accelerator with RISC-V RoCC for Efficient Low-Bit LLM Inference

### $\Delta$ ΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Κωνσταντίνου Ιωάννου

Επιβλέπων: Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π.

## LUMAX: A <u>LUT-Based Mixed-Precision Accelerator</u> for LLM Inference on the Edge

A LUT-Based Mixed-Precision GeMM Accelerator with RISC-V RoCC for Efficient Low-Bit LLM Inference

### $\Delta$ ΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Κωνσταντίνου Ιωάννου

Επιβλέπων: Δημήτριος Σούντρης Καθηγητής Ε.Μ.Π.

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την  $29^{\rm h}$  Σεπτεμβρίου, 2025.

Παναγιώτης Τσανάκας Δημήτριος Σούντρης

Καθηγητής Ε.Μ.Π.

Σωτήριος Ξύδης Καθηγητής Ε.Μ.Π. Επίκουρος Καθηγητής Ε.Μ.Π.

ΙΩΑΝΝΟΥ ΚΩΝΣΤΑΝΤΙΝΟΣ

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

Copyright © – All rights reserved Κωνσταντίνος Ιωάννου, 2025. Με επιφύλαξη παντός δικαιώματος.

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

## Περίληψη

Τα τελευταία χρόνια, η ραγδαία ανάπτυξη των μεγάλων γλωσσικών μοντέλων (LLMs) έχει αυξήσει τη ζήτηση για αποδοτιχή εχτέλεση τόσο σε υποδομές χέντρων δεδομένων όσο χαι σε πλατφόρμες περιορισμένων πόρων. Παρόλο που η χβαντοποιήση (quantization) μειώνει το υπολογιστιχό χόστος χαι την απαιτούμενη μνήμη, οι μικτής ακρίβειας πράξεις, όπου οι ενεργοποιήσεις διατηρούνται σε υψηλότερη ακρίβεια ενώ τα βάρη ποσοτικοποιούνται σε μικρότερο εύρος bit, παραμένουν αναποτελεσματικές στο γενικού σκοπού υλικό. Οι μέθοδοι που βασίζονται σε Πίνακες Αναζήτησης (LUT) προσφέρουν μια πολλά υποσχόμενη εναλλακτική λύση· ωστόσο, η επίτευξη της βέλτιστης ισορροπίας μεταξύ χρήσης μνήμης, ευελιξίας και προσαρμοστικότητας στο φόρτο εργασίας παραμένει πρόχληση. Προτείνουμε το LUMAX, έναν πλήρως ενσωματωμένο επιταχυντή μικτής ακρίβειας πολλαπλασιασμού πινάκων με βάση LUT, για ενεργειακά αποδοτική εκτέλεση μεγάλων γλωσσικών μοντέλων. Το LUMAX διαθέτει επαναδιαμορφώσιμο υλικό, επιτρέποντας την αποδοτική υποστήριξη διαφορετικών εύρων bit για ενεργοποιήσεις και βάρη. Για τη μείωση του κόστους των LUT, χρησιμοποιούμε LUT τεταρτημορίου μεγέθους (1-LUT) με αποδοτική δεικτοδότηση και συμπίεση δεδομένων, ελαχιστοποιώντας την αποθήκευση και τη μεταφορά δεδομένων. Το LUMAX έχει υλοποιηθεί ως συνεπεξεργαστής RocketChip (RoCC), επιτρέποντας έτσι απρόσχοπτη ενσωμάτωση με πυρήνες RISC-V. Επεχτείνοντας βασιχές ιδέες από πρόσφατα σχέδια βασισμένα σε LUT και συνδυάζοντάς τες με πλήρη ενσωμάτωση στον επεξεργαστή και επαναδιαμορφώσιμο υλιχό, το LUMAX προσφέρει έναν ευέλιχτο, ενεργειαχά αποδοτιχό επιταχυντή για ποσοτιχοποιημένη εκτέλεση LLM, συνδυάζοντας προσαρμοστικότητα υλικού, χρηστικότητα λογισμικού και αρχιτεκτονική αποδοτικότητα. Αποτελέσματα αξιολόγησης δείχνουν ότι το LUMAX, πρωτοτυποποιημένο σε FPGA ZCU106, μειώνει τη γρήση LUT και DSP έως και 33% και 96% αντίστοιγα, επιτυγγάνει με 79% λιγότερους κύκλους και προσφέρει έως και  $4.7\times$  επιτάχυνση στο LLaMA2, με έως και 70% βελτίωση στην ενεργειαχή αποδοτιχότητα σε σύγχριση με προηγούμενους επιταχυντές πολλαπλασιασμού πινάχων όπως το Gemmini.

Λέξεις Κλειδιά — Πίνακας Αναζήτησης (LUT), Μικτής Ακρίβειας Πράξεις, Επιταχυντής, Πολλαπλασιαμός Πινάκων, Χαμηλής Ακρίβειας Μεγάλα Γλωσσικά Μοντέλα.

## Abstract

In recent years, the rapid growth of large language models (LLMs) has increased demand for efficient inference on both datacenter and edge platforms. While quantization reduces computation and memory costs, mixed-precision operations, where activations remain in higher precision while weights are quantized to lower bitwidths, remain inefficient on general-purpose hardware. Lookup Table (LUT)-based methods offer a promising alternative, yet achieving an optimal balance of memory usage, flexibility, and workload adaptability remains challenging. We propose LUMAX, a fully integrated LUT-based mixed-precision GeMM accelerator for energy-efficient LLM inference. LUMAX features a reconfigurable hardware design, allowing for efficient support of different activation and weight bitwidths. To reduce LUT overhead, we employ a quarter-size LUT ( $\frac{1}{4}$ -LUT) with efficient indexing and data packaging, minimizing storage and data transfer. LUMAX has been implemented as a tightly coupled RocketChip Co-processor (RoCC), thus enabling seamless processor integration with RISC-V cores. By extending key ideas from recent LUT-based designs and combining them with full processor integration and reconfigurable hardware, LUMAX provides a flexible, power-efficient accelerator for quantized LLM inference, blending hardware adaptability, software usability, and architectural efficiency. Evaluation results show that LUMAX, prototyped on a ZCU106 FPGA, reduces LUT and DSP usage by up to 33% and 96%, achieves 79% fewer cycles, and delivers up to 4.7× speedup on LLaMA2, with up to 70% improved energy efficiency over prior GeMM accelerators such as Gemmini.

Key words — LUT, Mixed-Precision, Accelerator, GeMM, Low-bit LLM.

## Ευχαριστίες

Θα ήθελα να ευχαριστήσω θερμά τον κύριο Σωτήριο Ξύδη για την καθοδήγησή του κατά την εκπόνηση της διπλωματικής μου εργασίας, καθώς και τους υποψήφιους διδάκτορες Γιώργο Αλεξάνδρη και Γιώργο Αναγνωστόπουλο για τη συνεχή υποστήριξη και συνεργασία.

Ιδιαίτερες ευχαριστίες απευθύνω στον κύριο Δημήτρη Σούντρη για το δημιουργικό περιβάλλον του εργαστηρίου, που συνέβαλε καθοριστικά στην ολοκλήρωση της μελέτης.

Πάνω απ' όλα, θα ήθελα να ευχαριστήσω τους γονείς μου και την αδερφή μου για τη στήριξη και την υπομονή τους όλα αυτά τα χρόνια.

Κωνσταντίνος Ιωάννου Σεπτέμβριος 2025

## Contents

| П        | ερίλ                     | ηψη                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7                                                                                                        |

|----------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| <b>A</b> | bstra                    | ict                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                        |

| E۱       | υχαρ                     | ριστίες                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 11                                                                                                       |

| C        | ontei                    | nts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13                                                                                                       |

| Fi       | gure                     | List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 15                                                                                                       |

| Ta       | able                     | List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 18                                                                                                       |

| E:       | κτετ                     | αμένη Ελληνική Περίληψη                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 20                                                                                                       |

| 2        | 1.1<br>1.2<br>1.3<br>1.4 | Σχετιχή Βιβλιογραφία 1.2.1 Αφιερωμένοι Επιταχυντές για Κβαντισμένα Νευρωνικά Δίκτυα 1.2.2 Επιταχυντές Βασισμένοι σε LUT για Μικτής Ακρίβειας Κβαντισμένα Νευρωνικά Δίκτυα . Θεωρητικό Υπόβαθρο 1.3.1 Το Περιβάλλον Ανάπτυξης Chipyard 1.3.2 Chisel 1.3.3 RocketChip 1.3.4 Επιταχυντής RoCC 1.3.5 TileLink και Diplomacy 1.3.6 Συγχρονισμένες Μνήμες Ανάγνωσης (Sync Read Memories) 1.3.7 Θεωρητικό Υπόβαθρο: LLMs και Κβαντισμός Σχειδασμός Επιταχυντή 1.4.1 Σύνοψη του σχεδιασμού 1.4.2 Ροή Δεδομένων Επιταχυντή 1.4.3 Παραγωγή Προϊόντων 1.4.4 Τμήματα Μνήμης 1.4.5 Επιλογή Προϊόντος - Συσσώρευση 1.4.6 Βελτιστοποιήσεις Σχεδιασμού Αξιολόγηση και Αποτελέσματα | 22<br>28<br>33<br>34<br>34<br>35<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>46<br>46 |

| 3        | <b>Rel</b> 3.1           | ated Work  Dedicated Accelerators for Quantized Neural Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>53</b> 53                                                                                             |

Bibliography

|   |     | 3.1.1   | Gemmini: Systolic Architecture for GEMM                          |     |

|---|-----|---------|------------------------------------------------------------------|-----|

|   |     | 3.1.2   | Carat: Accelerator Architecture with Multiplier-Free GEMMs       |     |

|   |     | 3.1.3   | TATAA – A Transformable Accelerator for Transformers             |     |

|   |     | 3.1.4   | LeOPard – Gradient Based Learned Run time Pruning                |     |

|   |     | 3.1.5   | An Energy Efficient Soft SIMD Microarchitecture                  |     |

|   | 3.2 | LUT-E   | Based Accelerators for Mixed-Precision Quantized Neural Networks |     |

|   |     | 3.2.1   | FIGLUT: LUT-based Accelerator for FP-INT GEMM                    |     |

|   |     | 3.2.2   | 4-bit CNN Quantization with Compact LUT-Based Multipliers        | 63  |

|   |     | 3.2.3   | LUT Tensor Core                                                  | 65  |

| 4 | Bac | kgrour  |                                                                  | 69  |

|   |     | 4.0.1   | The Chipyard Development Environment                             | 69  |

|   |     | 4.0.2   | Chisel: Constructing Hardware                                    | 70  |

|   |     | 4.0.3   | RocketChip                                                       | 70  |

|   |     | 4.0.4   | RoCC Accelerator                                                 | 70  |

|   |     | 4.0.5   | TileLink & Diplomacy                                             | 71  |

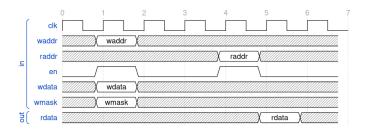

|   |     | 4.0.6   | Sync Read Memories                                               | 72  |

|   |     | 4.0.7   | Theoretical Background: LLMs and Quantization                    | 74  |

| 5 | Acc |         | or Design                                                        | 77  |

|   | 5.1 |         | rare Design Overview                                             |     |

|   | 5.2 |         | rare Dataflow                                                    |     |

|   | 5.3 | Major   | Components                                                       |     |

|   |     | 5.3.1   | Memory Blocks                                                    |     |

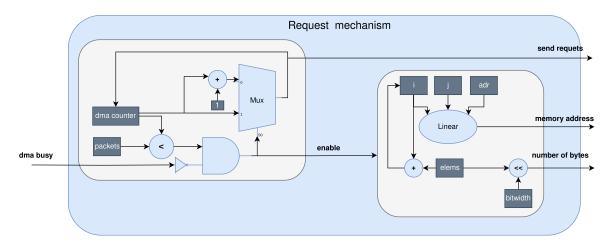

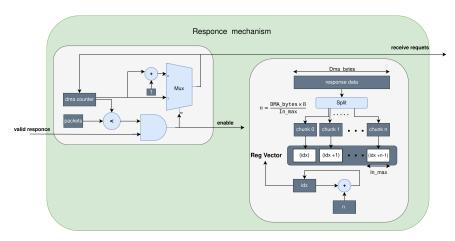

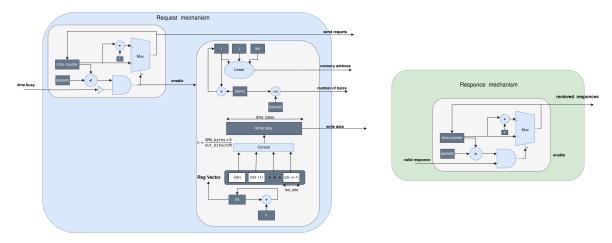

|   |     | 5.3.2   | Communication Architecture                                       |     |

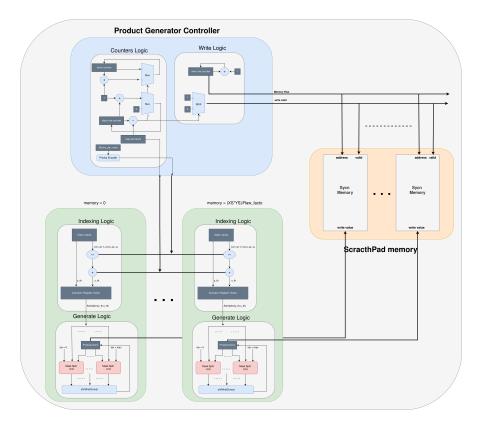

|   |     | 5.3.3   | Generate Products                                                |     |

|   |     | 5.3.4   | Select and Accumulate                                            | 104 |

|   | 5.4 | Design  | Optimizations                                                    |     |

|   |     | 5.4.1   | Select-and-Accumulate Pipeline                                   | 112 |

|   |     | 5.4.2   | Weight Ping Pong Buffers                                         | 113 |

|   |     | 5.4.3   | Balancing Main Memory Loads and Sync Memory Reads                | 114 |

|   | 5.5 | Cycle-  | Accurate Performance Model                                       | 115 |

| 6 | Exp | erimei  |                                                                  | 119 |

|   | 6.1 |         | mental Setup                                                     |     |

|   | 6.2 | Sensiti | vity Analysis on Generator Parameters                            |     |

|   |     | 6.2.1   | Gemmini as Baseline                                              | 121 |

|   |     | 6.2.2   | Results and Discussion                                           | 122 |

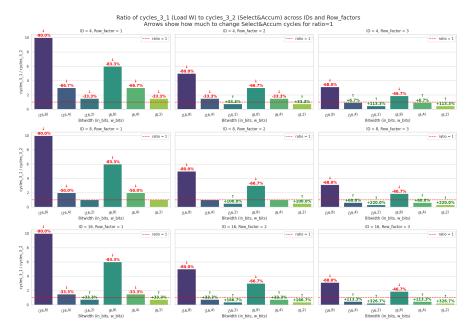

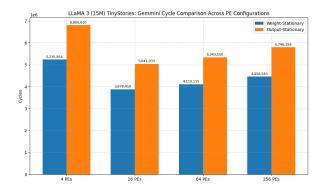

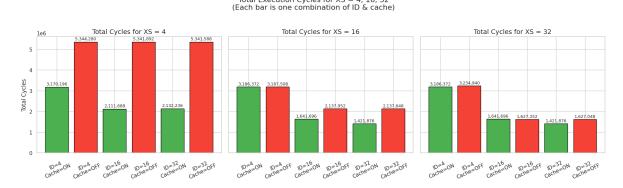

|   |     | 6.2.3   | Cycles Performace                                                | 122 |

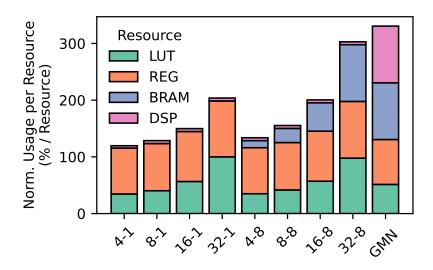

|   |     | 6.2.4   | Utilization Report                                               | 123 |

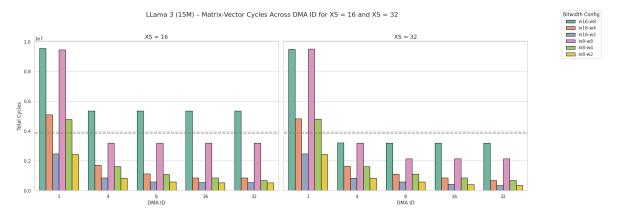

|   |     | 6.2.5   | Different Dma parameters                                         | 124 |

|   |     | 6.2.6   | Cache mode                                                       | 125 |

| 7 | Con | clusion | ns - Future Work                                                 | 127 |

|   |     |         |                                                                  |     |

129

# Figure List

| 1.2.1          | Σιστολιχός Πίναχας Gemmini                                                                                                                                                                                                                                                                                                                                                                                                                      | 2             |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| 1.2.2          | Επισκόπηση αρχιτεκτονικής επιταχυντή Carat                                                                                                                                                                                                                                                                                                                                                                                                      | $2^{4}$       |

| 1.2.3          | Αρχιτεκτονική υλικού του ΤΑΤΑΑ και μονάδα διπλής λειτουργίας επεξεργασίας                                                                                                                                                                                                                                                                                                                                                                       | 2             |

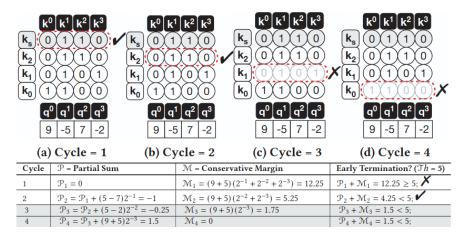

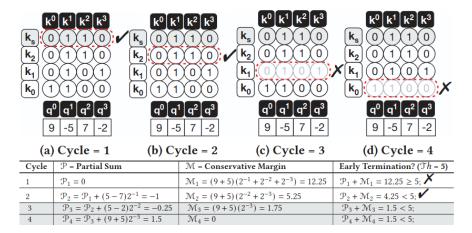

| 1.2.4          | Σύνοψη πρόωρου τερματισμού υπολογισμού για τη λειτουργία εσωτερικού γινομένου $Q \times K$ . Στο παράδειγμα, το $K$ παρουσιάζεται σε μορφή bit-serial, ενώ το $Q$ σε ακέραιη ολοκλήρωση με πλήρη ακρίβεια. Οι στήλες (a-d) απεικονίζουν μεμονωμένα στοιχεία του διανύσματος $K$ και οι γραμμές τα αντίστοιχα bits (MSB $\to$ LSB). Το σήμα $K$ υποδηλώνει το bit πρόσημο. Για απλοποίηση, τα στοιχεία του $K$ είναι κλιμακωμένα μεταξύ -1.0 και |               |

|                | +1.0. Ο πίνακας εμφανίζει τις μερικές τιμές αθροίσματος μετά από κάθε κύκλο                                                                                                                                                                                                                                                                                                                                                                     |               |

| 1.2.5          | Γενική μικροαρχιτεκτονική ενός πλακιδίου LeOPard                                                                                                                                                                                                                                                                                                                                                                                                | 2'            |

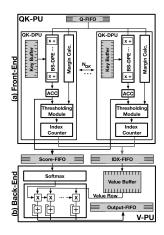

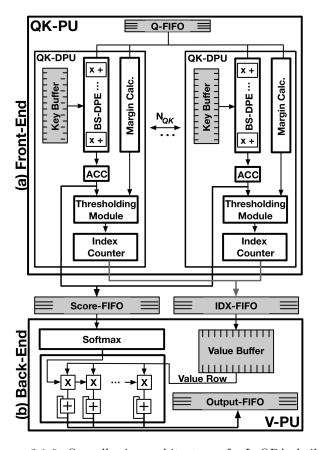

| 1.2.6          | Διάγραμμα μπλοχ της προτεινόμενης μιχροαρχιτεχτονιχής Soft SIMD. Το πρώτο στάδιο είναι η Μονάδα Αριθμητιχών (Arithmetic Unit - AU), και το δεύτερο η Μονάδα Επανασυσχευασίας Δεδομένων (Data Pack Unit - DPU). R1 έως R4 είναι καταχωρητές                                                                                                                                                                                                      | 28            |

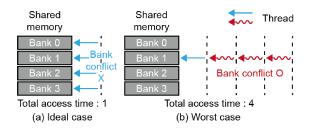

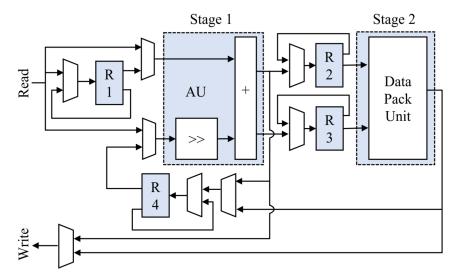

| 1.2.7          | Σύγκριση συγκρούσεων τραπεζών κατά την πρόσβαση σε κοινή μνήμη                                                                                                                                                                                                                                                                                                                                                                                  | 29            |

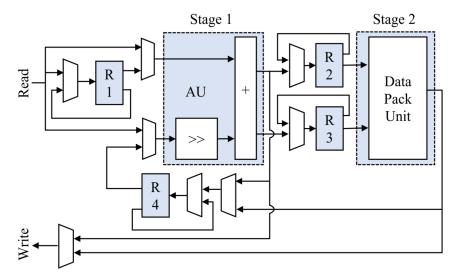

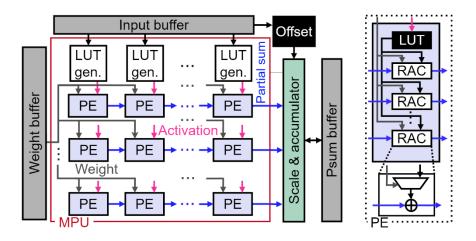

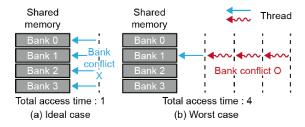

| 1.2.8          | Συνολική αρχιτεκτονική MPU του FIGLUT                                                                                                                                                                                                                                                                                                                                                                                                           | 29            |

| 1.2.9          | Βασιχή αρχιτεχτονική ΜΠ Ο του ΤΙσΕΟΤ                                                                                                                                                                                                                                                                                                                                                                                                            |               |

|                | Παράλληλοι πολλαπλασιασμοί για συνελικτικούς υπολογισμούς σε FPGA επιταχυντή                                                                                                                                                                                                                                                                                                                                                                    | 3             |

|                | Βελτιστοποιημένη μονάδα LUT με bit-serial προσέγγιση                                                                                                                                                                                                                                                                                                                                                                                            | 32            |

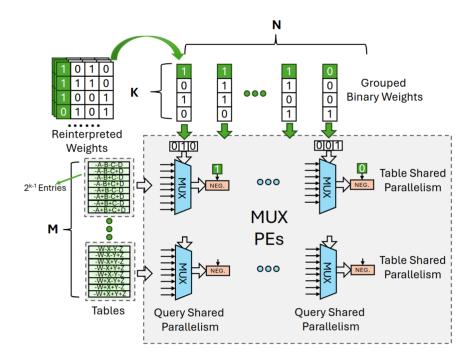

|                | Παράδειγμα στοιχείου LUT-based mpGEMM για ενεργοποιήσεις FP16 και βάρη INT1.                                                                                                                                                                                                                                                                                                                                                                    | 0.            |

| 1.2.11         | Η αναζήτηση στον πίνακα αντικαθιστά το εσωτερικό γινόμενο 4-στοιχείων                                                                                                                                                                                                                                                                                                                                                                           | 35            |

| 1.2.13         | Επιμηκυμένη τοποθέτηση MNK του LUT-based Tensor Core. Απαιτεί μεγάλο N (π.χ. $64/128$ ) για μέγιστη επαναχρησιμοποίηση και κατάλληλα $K$ (π.χ. $4$ ) για αποδοτικό μέγε-                                                                                                                                                                                                                                                                        |               |

| 1 9 1          | θος πίναχα                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\frac{3}{3}$ |

| 1.3.1<br>1.3.2 | Απλοποιημένη άποψη της διεπαφής RoCC                                                                                                                                                                                                                                                                                                                                                                                                            | Э;            |

| 1.3.2          | τα πεντε καναλία TheLink μεταξύ master και slave. Η τεραρχική πρότεραιοποιήση αποτρέπει αδιέξοδα και διασφαλίζει ροή δεδομένων.                                                                                                                                                                                                                                                                                                                 | 30            |

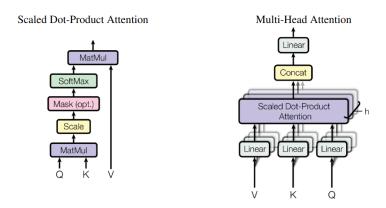

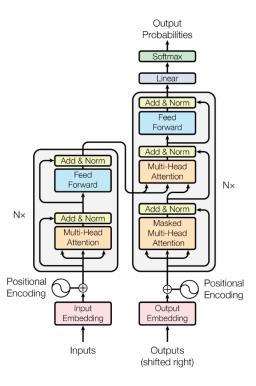

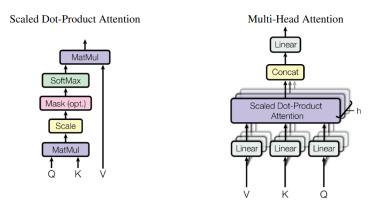

| 1.3.3          | Μπλοκ αυτοπροσοχής και πολυκεφαλικής προσοχής                                                                                                                                                                                                                                                                                                                                                                                                   | 3'            |

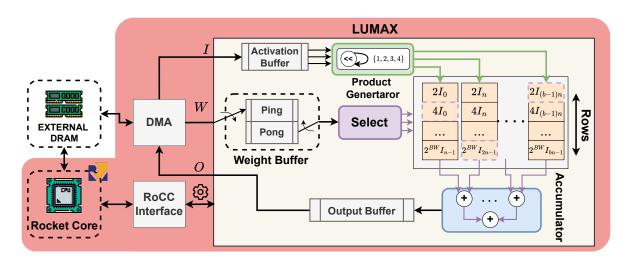

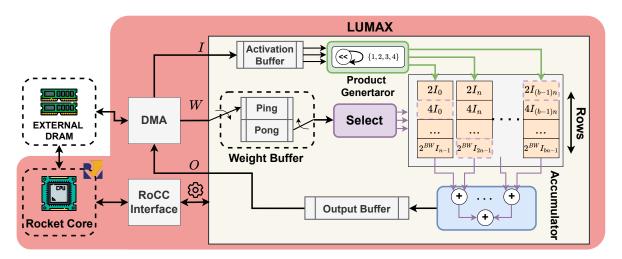

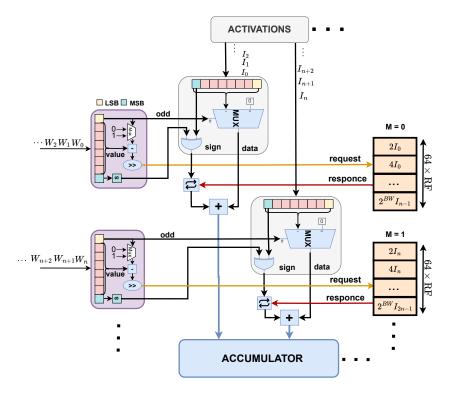

| 1.4.1          | The Proposed LUMAX Architecture                                                                                                                                                                                                                                                                                                                                                                                                                 | 39            |

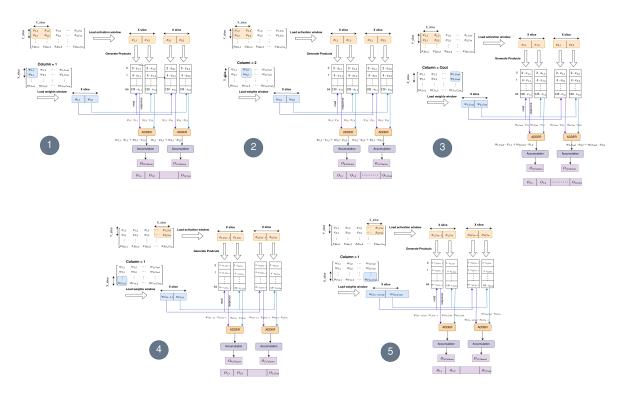

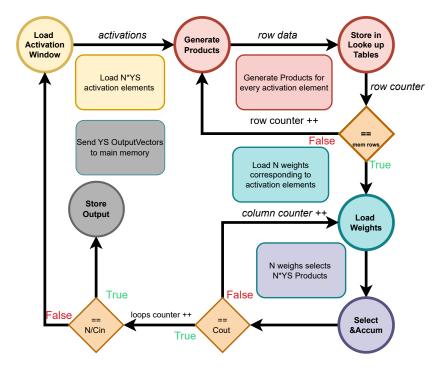

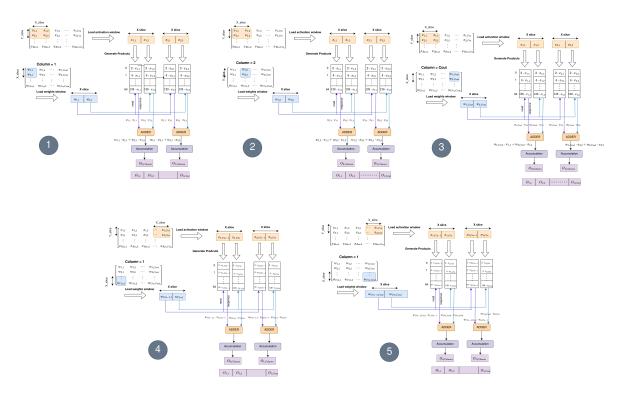

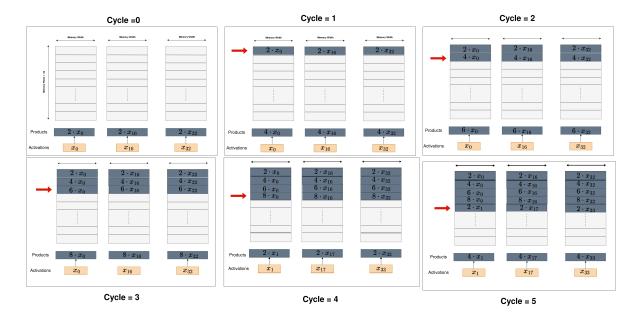

| 1.4.2          | Simplified Example of the Hardware Dataflow                                                                                                                                                                                                                                                                                                                                                                                                     | 4             |

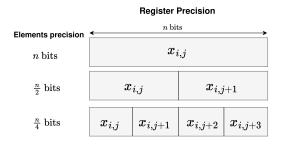

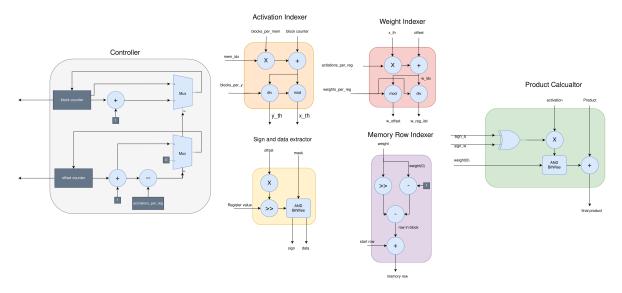

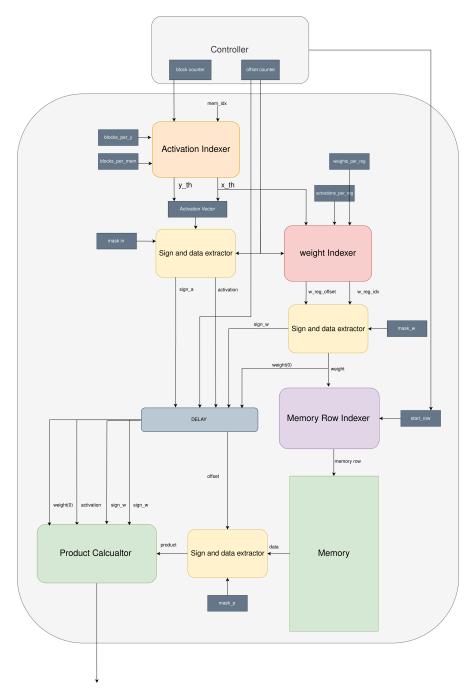

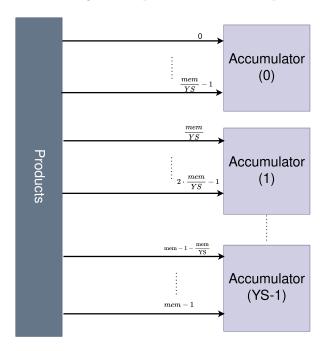

| 1.4.4          | Detailed Representation of the Select Module for Y = 1                                                                                                                                                                                                                                                                                                                                                                                          | 4:            |

| 1.4.3          | Mapping of activation blocks onto physical memory blocks, where each color corre-                                                                                                                                                                                                                                                                                                                                                               | 10            |

| 1.1.0          | sponds to a different activation block                                                                                                                                                                                                                                                                                                                                                                                                          | 4:            |

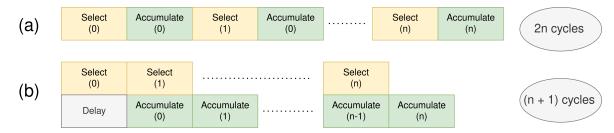

| 1.4.5          | Select-and-Accumulate Phases: (a) Without Pipelining, (b) With Pipelining                                                                                                                                                                                                                                                                                                                                                                       | 4             |

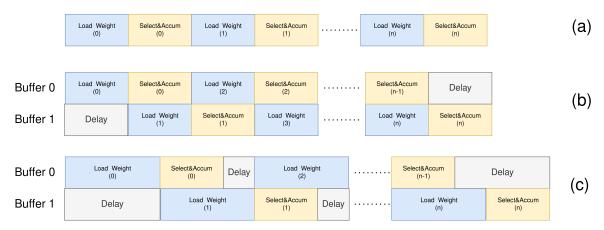

| 1.4.6          | Load Weights and Select & Accumulate phases: (a) without double buffering, (b) with                                                                                                                                                                                                                                                                                                                                                             | -             |

|                | double buffering where Load Weights and Select &Accumulate require the same number                                                                                                                                                                                                                                                                                                                                                              |               |

|                | of cycles, (c) with double buffering where the Load Weights stage needs more cycles                                                                                                                                                                                                                                                                                                                                                             |               |

|                | than the Select &Accumulate stage                                                                                                                                                                                                                                                                                                                                                                                                               | 46            |

| 1.5.1          | Normalized utilization of resources on the Xilinx ZCU106 FPGA for different M-RF                                                                                                                                                                                                                                                                                                                                                                |               |

|                | configurations of LUMAX and the Gemmini $4\times4$ (GMN) baseline. Each resource type                                                                                                                                                                                                                                                                                                                                                           |               |

|                | is normalized with respect to its maximum across all designs, enabling a fair comparison                                                                                                                                                                                                                                                                                                                                                        |               |

|                | of resource usage distribution rather than absolute counts                                                                                                                                                                                                                                                                                                                                                                                      | 48            |

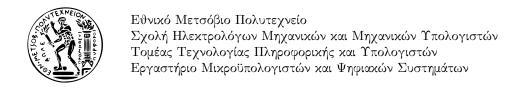

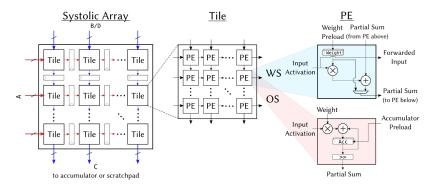

| 3.1.1                                                                                                                      | Gemmini Systolic Array.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 3.1.2                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 54                                                                               |

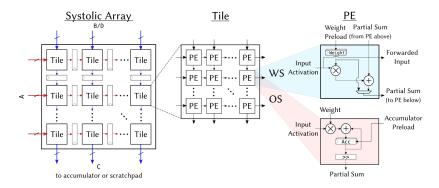

| 3.1.3                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55                                                                               |

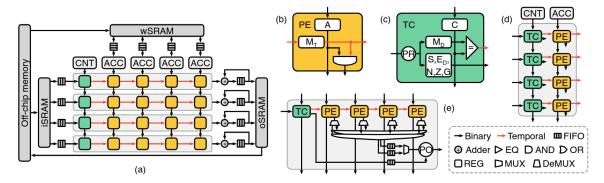

| 3.1.4                                                                                                                      | 1 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 56                                                                               |

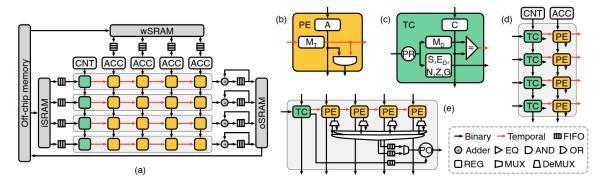

| 3.1.5                                                                                                                      | High-level overview of early-compute termination for dot-product operation $Q \times K$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                  |

|                                                                                                                            | In this example, K is represented in bit-serial format, whereas Q is in full-precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                                            | fixed-point format. In Figure (a-d) each column illustrate one element of K vector and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                  |

|                                                                                                                            | each row represents its corresponding bits (MSB $\rightarrow$ LSB). K indicates the sign bit. For                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                  |

|                                                                                                                            | simplicity, K elements are scaled to be between $-1.0$ and $+1.0$ . The table shows the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ر ر                                                                              |

| 0.4.0                                                                                                                      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 58                                                                               |

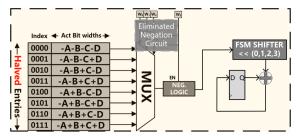

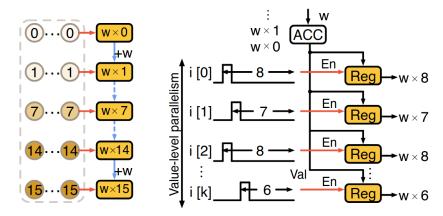

| 3.1.6                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59                                                                               |

| 3.1.7                                                                                                                      | Block scheme of the proposed Soft SIMD microarchitecture. The first stage is an Arithmetic Unit (AU), and the second stage is a Data Pack Unit (DPU). R1 to R4 are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                  |

| 0.0.1                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 60                                                                               |

| 3.2.1                                                                                                                      | Comparison of bank conflicts during shared memory access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

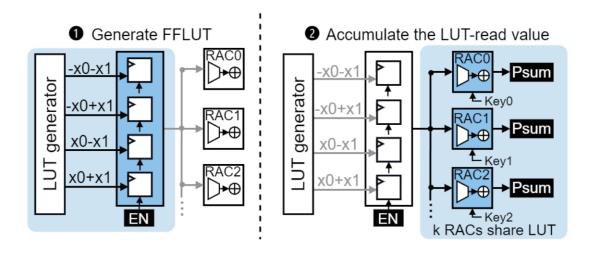

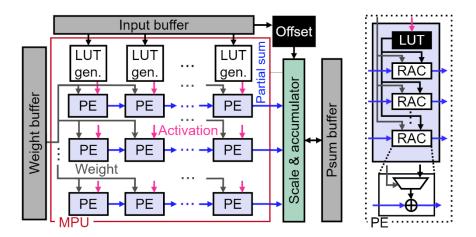

| 3.2.2                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                                               |

| 3.2.3                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 62                                                                               |

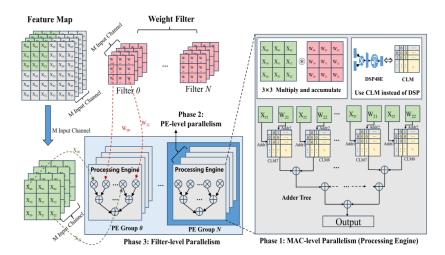

| 3.2.4                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 63                                                                               |

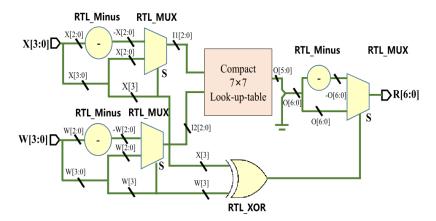

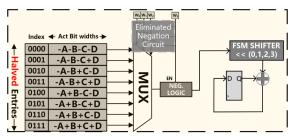

| 3.2.5                                                                                                                      | Basic CLM architecture for 4-bit multiplication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                  |

| 3.2.6                                                                                                                      | Peripheral RTL logic of the CLM implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

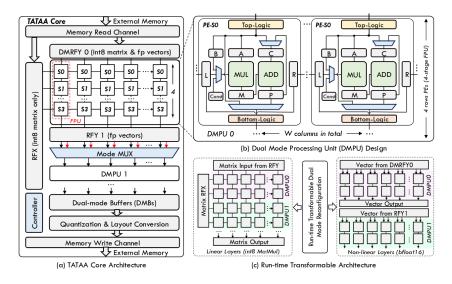

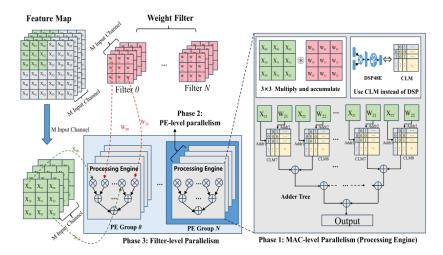

| 3.2.7                                                                                                                      | Multiple parallelism for convolution computation in FPGA accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 00                                                                               |

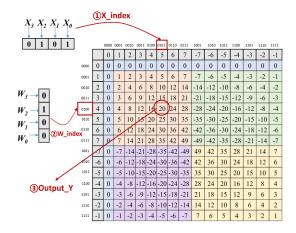

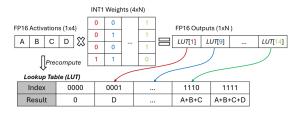

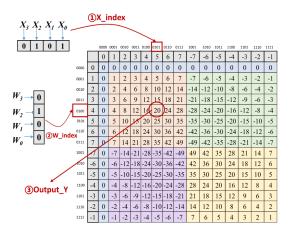

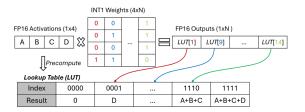

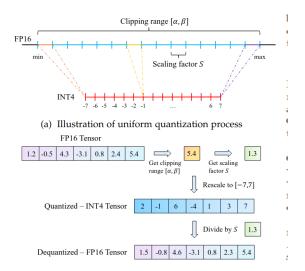

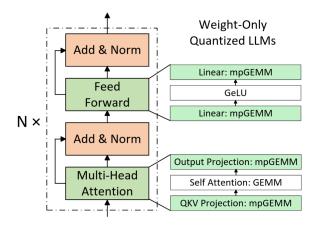

| 3.2.8                                                                                                                      | A naive LUT-based mpGEMM tile example of FP16 activations and INT1 weights. With the precomputed table, a table lookup can replace a dot product of 4-element                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                  |

|                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                               |

| 3.2.9                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 66                                                                               |

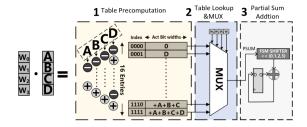

| 3.2.10                                                                                                                     | Conventional LUT hardware in three steps. Table precomputation and storage intro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U                                                                                |

| 0.2.10                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 67                                                                               |

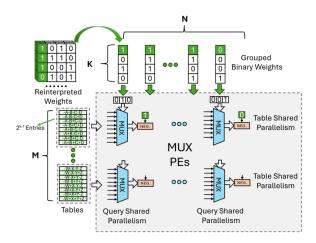

| 3.2.11                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ٠.                                                                               |

|                                                                                                                            | Flongated MINK tiling of LUI-based Tensor Core. LUI-based Tensor Core requires a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                  |

|                                                                                                                            | Elongated MNK tiling of LUT-based Tensor Core. LUT-based Tensor Core requires a larger N (e.g., 64/128) to maximize table reuse, along with a suitably sized K (e.g., 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                  |

| J                                                                                                                          | larger N (e.g., $64/128$ ) to maximize table reuse, along with a suitably sized K (e.g., 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67                                                                               |

|                                                                                                                            | larger N (e.g., $64/128$ ) to maximize table reuse, along with a suitably sized K (e.g., 4) for a cost-efficient table size.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                  |

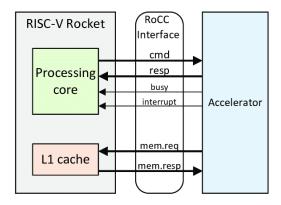

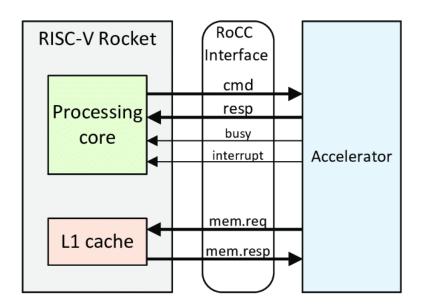

| 4.0.1                                                                                                                      | larger N (e.g., $64/128$ ) to maximize table reuse, along with a suitably sized K (e.g., 4) for a cost-efficient table size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 67<br>71                                                                         |

|                                                                                                                            | larger N (e.g., $64/128$ ) to maximize table reuse, along with a suitably sized K (e.g., 4) for a cost-efficient table size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71                                                                               |

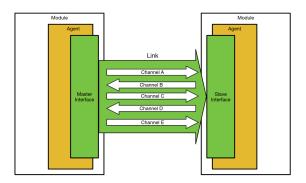

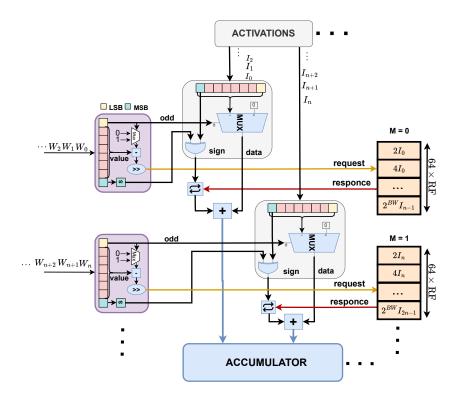

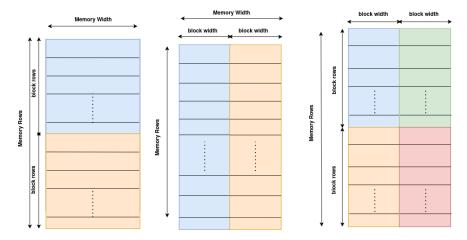

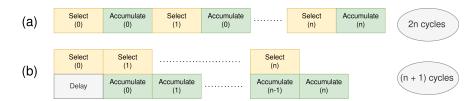

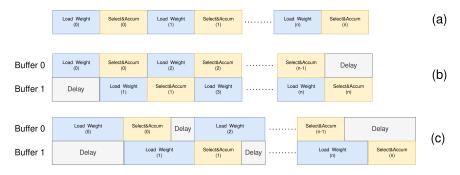

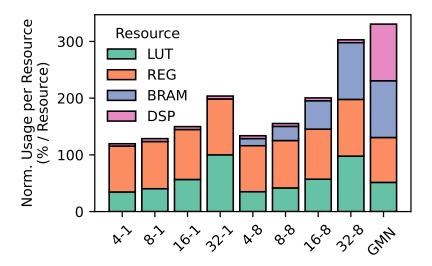

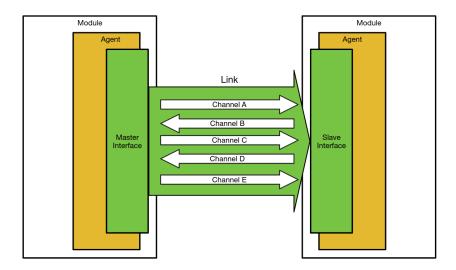

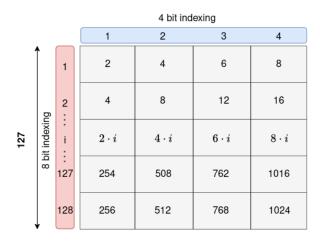

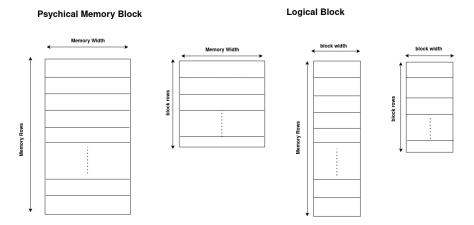

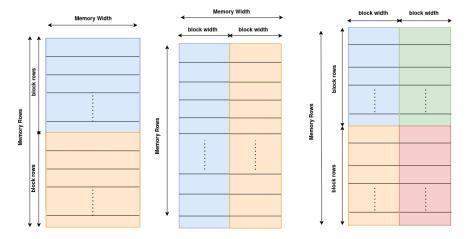

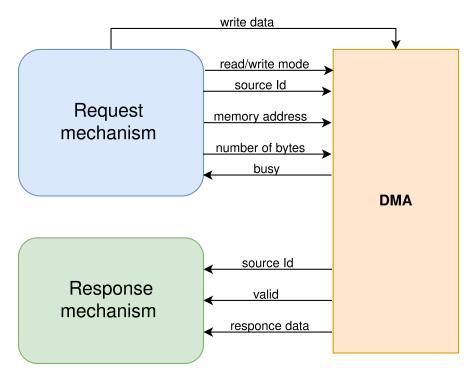

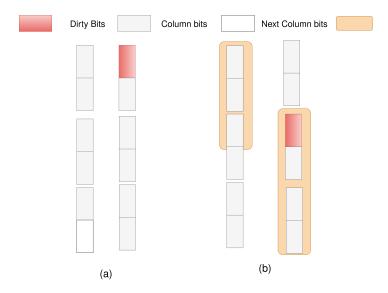

| 4.0.1<br>4.0.2                                                                                                             | larger N (e.g., $64/128$ ) to maximize table reuse, along with a suitably sized K (e.g., 4) for a cost-efficient table size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71<br>72                                                                         |