# NATIONAL TECHNICAL UNIVERSITY of ATHENS

### SCHOOL OF ELECTRICAL AND COMPUTER ENGINEERING

Division of Computer Science Computing Systems Lab

## Implementation of a Collective Remote Attestation Framework for IoT Devices

### DIPLOMA THESIS

of

Faidon Cornelis Kourounakis

Supervisor: Dionisios Pnevmatikatos Professor, NTUA

Athens, October 2025

## Implementation of a Collective Remote Attestation Framework for IoT Devices

### $\Delta$ ΙΠΛΩΜΑΤΙΚΗ ΕΡΓΑΣΙΑ

του

Φαίδων Κορνέλις Κουρουνάκη

Επιβλέπων: Διονύσιος Πνευματικάτος Καθηγητής ΕΜΠ

Εγκρίθηκε από την τριμελή εξεταστική επιτροπή την 10 Οκτωβρίου 2025.

Διονύσιος Πνευματικάτος Δημήτριος Σούντρης Καθηγητής ΕΜΠ Καθηγητής ΕΜΠ Γεώργιος Γκούμας Καθηγητής ΕΜΠ

Αθήνα, Οκτώβριος 2025.

.....

### Φαίδων Κορνέλις Κουρουνάκης

Διπλωματούχος Ηλεκτρολόγος Μηχανικός και Μηχανικός Υπολογιστών Ε.Μ.Π.

#### Copyright © Faidon Cornelis Kourounakis, 2025. All Rights Reserved

Απαγορεύεται η αντιγραφή, αποθήκευση και διανομή της παρούσας Εργασίας, εξ ολοκλήρου ή τμήματος αυτής, για εμπορικό σκοπό. Επιτρέπεται η ανατύπωση, αποθήκευση και διανομή για σκοπό μη κερδοσκοπικό, εκπαιδευτικής ή ερευνητικής φύσης, υπό την προϋπόθεση να αναφέρεται η πηγή προέλευσης και να διατηρείται το παρόν μήνυμα. Ερωτήματα που αφορούν τη χρήση της Εργασίας για κερδοσκοπικό σκοπό πρέπει να απευθύνονται προς τον συγγραφέα.

Copying, storage, and distribution of this Work, in whole or in part, for commercial purposes is prohibited. Reproduction, storage, and distribution are permitted for non-profit purposes of an educational or research nature, provided that the source is acknowledged and this message is retained. Questions regarding the use of the Work for commercial purposes must be addressed to the author.

Οι απόψεις και τα συμπεράσματα που περιέχονται σε αυτό το έγγραφο εκφράζουν τον συγγραφέα και δεν πρέπει να ερμηνευθεί ότι αντιπροσωπεύουν τις επίσημες θέσεις του Εθνικού Μετσόβιου Πολυτεχνείου.

The opinions and conclusions contained in this document are those of the author and should not be interpreted as representing the official positions of the National Technical University of Athens.

# Περίληψη

Η μαζική υιοθέτηση των συσκευών ΙοΤ απαιτεί ισχυρά μέτρα ασφαλείας για τη διασφάλιση της αχεραιότητάς τους και την αποτροπή διαταραχών. Αντιμετωπίζοντας αυτή την πρόκληση, η παρούσα εργασία παρουσιάζει ένα ελαφρύ, πλαίσιο Συλλογικής Απομαχρυσμένης Επαλήθευσης (Collective Remote Attestation) σχεδιασμένο για συσκευές με περιορισμένους πόρους. Στοχεύει στην εύχολη υιοθέτηση, αξιοποιώντας τον μηχανισμό Physical Memory Protection (PMP) της αρχιτεκτονικής RISC-V ως Ρίζα Εμπιστοσύνης υλιχού. Το προτεινόμενο αποχεντρωμένο πρωτόχολλο διεξάγει αμοιβαία ετερογενή επαλήθευση με τοπική επαλήθευση της ακεραιότητας της μνήμης flash. Η χρήση nonces και HMAC διασφαλίζει τη φρεσκάδα και την αυθεντικότητα των μηνυμάτων, μετριάζοντας τις επιθέσεις επανάληψης. Το πλαίσιο υλοποιείται χρησιμοποιώντας το FreeRTOS και αξιολογείται στο χαμηλού κόστους, ευρέως διαθέσιμο μικροελεγκτή ΕSP32-C3, το οποίο υποστηρίζει τα αναγκαία χαρακτηριστικά ασφαλείας. Η αξιολόγηση απόδοσης επιβεβαίωσε ότι η χρήση της CPU κλιμακώνεται γραμμικά ανάλογα με τον αριθμό των συσκευών και τη συχνότητα των επαληθεύσεων. Το πλαίσιο παρέχει μια βάση για μελλοντική έρευνα και επεκτάσεις σε ασφαλείς αποκεντρωμένους μηχανισμούς εμπιστοσύνης σε δίχτυα ΙοΤ με περιορισμένους πόρους.

# Λέξεις Κλειδιά

Συλλογική Απομακρυσμένη Επαλήθευση, Ασφάλεια ΙοΤ, ESP32, FreeRTOS, RISC-V

# Abstract

The mass adoption of Internet of Things devices necessitates robust security measures to ensure their integrity and prevent widespread disruption. Addressing this challenge in IoT networks, this work presents a lightweight Collective Remote Attestation framework designed for resource-constrained devices. It targets real-world adoption by leveraging the RISC-V Physical Memory Protection mechanism as the Hardware Root of Trust. The proposed decentralized protocol conducts mutual heterogeneous attestation with local verification of flash integrity. The use of nonces and HMAC ensures message freshness and authenticity, mitigating replay attacks. The framework is implemented using FreeRTOS and evaluated on the low-cost, readily available ESP32-C3 chip that supports the necessary security features. Performance testing confirmed CPU utilization scaling linearly with device count and attestation frequency. The framework provides a basis for future research and extensions on secure, decentralized trust mechanisms in resource-constrained IoT networks.

# Keywords

Collective Remote Attestation, IoT Security, ESP32-C3, FreeRTOS, RISC-V

# Acknowledgements

I would like to sincerely thank Professor Dionisios Pnevmatikatos for providing me with the opportunity to undertake this research and my advisor, Foivos Iliadis, for his guidance, constructive feedback, and encouragement, which were essential for the completion of this thesis.

I would also like to acknowledge my friends and university colleagues advice, and most importantly moral support enriched this experience. Lastly, I wish to extend my heartfelt appreciation to my parents and my brother for their constant encouragement and understanding, which sustained me through the most demanding stages of this work.

# Contents

| П            | ερίλ  | ηψη                     |                                                            | 4  |

|--------------|-------|-------------------------|------------------------------------------------------------|----|

| $\mathbf{A}$ | bstra | ıct                     |                                                            | 6  |

| $\mathbf{A}$ | ckno  | wledge                  | ements                                                     | 8  |

| 1            | Ext   | τεταμέ                  | ένη Περίληψη στα Ελληνικά                                  | 16 |

|              | 1.1   | Εισαγ                   | ωγή                                                        | 16 |

|              | 1.2   | Υπόβα                   | αθρό                                                       |    |

|              |       | 1.2.1                   | Ενσωματωμένα Συστήματα και $\Delta$ ιαδίκτυο των Πραγμάτων | 17 |

|              |       | 1.2.2                   | RISC-V xxx Physical Memory Protection                      | 17 |

|              |       | 1.2.3                   | Κρυπτογραφία                                               | 18 |

|              |       | 1.2.4                   | Εμπιστοσύνη και Secure Boot                                |    |

|              |       | 1.2.5                   | Απομακρυσμένη Επαλήθευση                                   |    |

|              | 1.3   | , ,                     | κή Βιβλιογραφία                                            | 19 |

|              |       | 1.3.1                   | PMP σε RTOS και Απομακρυσμένη Βεβαίωση                     | 19 |

|              |       | 1.3.2                   | Ρίζες Εμπιστοσύνης από την TCG                             | 19 |

|              |       | 1.3.3                   | Εναλλαχτικές Ρίζες Εμπιστοσύνης της Ακαδημαϊκής Κοινότητας |    |

|              |       | 1.3.4                   | Συλλογικά Πρωτόκολλα Απομακρυσμένης Επαλήθευσης            |    |

|              | 1.4   |                         | λαίσιο Απομακρυσμένης Επαλήθευσής μας                      |    |

|              |       | 1.4.1                   | Κίνητρο και Απαιτήσεις                                     |    |

|              |       | 1.4.2                   | Σχεδίαση Πρωτοκόλλου                                       |    |

|              |       | 1.4.3                   | Υλοποίηση                                                  |    |

|              | 1.5   |                         | όγηση                                                      |    |

|              |       | 1.5.1                   | Χρήση CPU με την πάροδο του χρόνου                         |    |

|              |       | 1.5.2                   | Ανάλυση Κλιμάκωσης Αριθμού Συσκευών                        |    |

|              |       | 1.5.3                   | Ανάλυση Συχνότητας Γύρων Επαλήθευσης                       |    |

|              | 1.6   | •                       | εράσματα και Μελλοντική Εργασία                            |    |

|              |       | 1.6.1                   | Συμπεράσματα                                               |    |

|              |       | 1.6.2                   | Μελλοντική Εργασία                                         | 35 |

| 2            | Intr  | $\operatorname{roduct}$ | ion                                                        | 37 |

|              | 2.1   | IoT .                   |                                                            | 37 |

|              |       | 2.1.1                   | 11                                                         |    |

|              |       | 2.1.2                   | The Challenge of Security                                  | 38 |

| 3            | Bac   | kgrou                   | nd                                                         | 40 |

|   | 3.1  | Embe           | dded Systems                                          | 40        |

|---|------|----------------|-------------------------------------------------------|-----------|

|   |      | 3.1.1          | Networking                                            |           |

|   |      | 3.1.2          | Real Time Operating Systems                           |           |

|   |      | 3.1.3          | Internet of Things                                    | 41        |

|   |      | 3.1.4          | RISC-V                                                | 42        |

|   | 3.2  | Crypt          | ography                                               |           |

|   |      | 3.2.1          | Hashing                                               | 43        |

|   |      | 3.2.2          | Asymmetric Cryptography                               | 44        |

|   |      | 3.2.3          | Message Authentication                                |           |

|   | 3.3  | Trust          |                                                       | 45        |

|   |      | 3.3.1          | Root of Trust                                         | 45        |

|   |      | 3.3.2          | Remote Attestation                                    | 45        |

| 4 | Rela | ated V         | Vork                                                  | 49        |

| _ | 4.1  |                | ous Uses of PMP in RTOS and Remote Attestation        |           |

|   |      | 4.1.1          | Secure Task Management in FreeRTOS: A RISC-V Core     | 10        |

|   |      | 1.1.1          | Approach with Physical Memory Protection              | 49        |

|   | 4.2  | Alterr         | native Roots of Trust by TCG                          |           |

|   | 1.2  | 4.2.1          | Trusted Platform Module as RoT                        |           |

|   |      | 4.2.2          | Device Identifier Composition Engine as RoT           |           |

|   | 4.3  |                | native Roots of Trust in Academia                     |           |

|   | 1.0  | 4.3.1          | GAROTA: Generalized Active Root-Of-Trust Architecture |           |

|   |      | 4.3.2          |                                                       |           |

|   |      | 4.3.3          | RATA: Remote Attestation with TOCTOU Avoidance        |           |

|   | 4.4  |                | lished Collective Remote Attestation Protocols        |           |

|   | 1.1  | 4.4.1          | SEDA                                                  |           |

|   |      | 4.4.2          | HEALED                                                |           |

|   |      | 1, 1, <u>-</u> |                                                       | 0 1       |

| 5 | Our  |                | ework                                                 | <b>55</b> |

|   | 5.1  |                | ation                                                 |           |

|   |      |                | Need for Special Purpose Hardware                     |           |

|   |      |                | Addressing RTOS Configuration                         |           |

|   | 5.2  | -              | rements                                               |           |

|   |      | 5.2.1          | System and Security Model                             |           |

|   |      | 5.2.2          | General Requirements                                  |           |

|   |      | 5.2.3          | Hardware Root of Trust                                |           |

|   |      | 5.2.4          | Targeting Harvard Architectures                       |           |

|   |      | 5.2.5          | Outside of our Scope                                  |           |

|   | 5.3  | Prelin         | ninary Cryptographic Design Considerations            |           |

|   |      | 5.3.1          | Basic Hash-Based Attestation                          |           |

|   |      | 5.3.2          | Incorporating Nonces for Replay Attack Mitigation     |           |

|   |      | 5.3.3          | Concluding Design Remarks                             |           |

|   | 5.4  |                | col Overview                                          |           |

|   |      | 5.4.1          | Offline Phase                                         |           |

|   |      | 5.4.2          | Online Phase                                          |           |

|   |      | 5.4.3          | Network Topology                                      |           |

|   | 5.5  | Imple:         | mentation                                             | 64        |

|    |        | 5.5.1   | Hardware Platform                 | 64                 |

|----|--------|---------|-----------------------------------|--------------------|

|    |        | 5.5.2   | Software Stack                    | 67                 |

|    |        | 5.5.3   | Project Structure                 | 68                 |

|    |        | 5.5.4   | Deployment Automation and Scripts | 70                 |

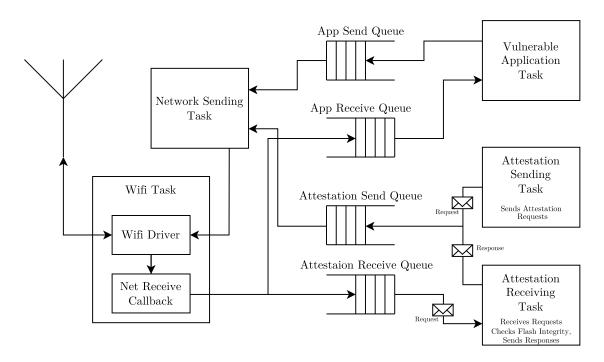

|    |        | 5.5.5   | Framework Architecture            | 72                 |

|    |        | 5.5.6   | Framework Configuration Options   | 73                 |

|    |        | 5.5.7   | Implementation Challenges         | 75                 |

|    |        | 5.5.8   | Implementation Omissions          | 77                 |

| _  | -      | 1       |                                   |                    |

| 6  | Eva    | luatior |                                   | <b>78</b>          |

|    | 6.1    | Metho   | odology                           | 78                 |

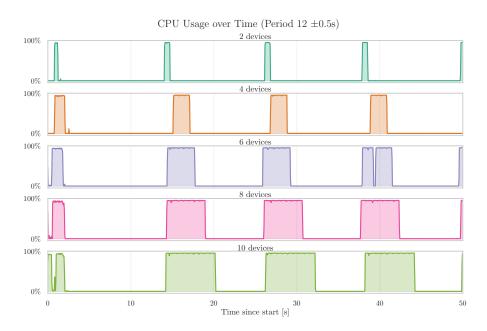

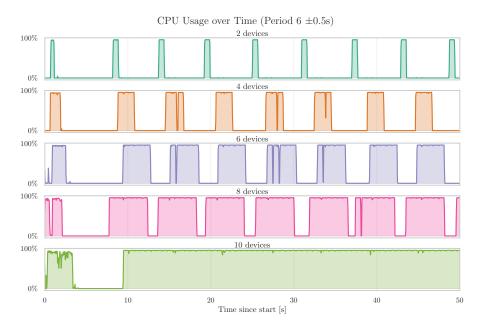

|    | 6.2    | CPU I   | Usage Over Time                   | 79                 |

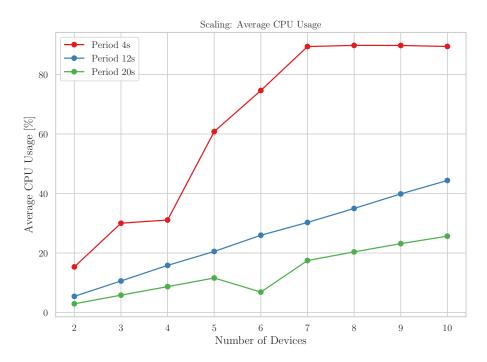

|    | 6.3    | Scaling | g Graphs                          | 81                 |

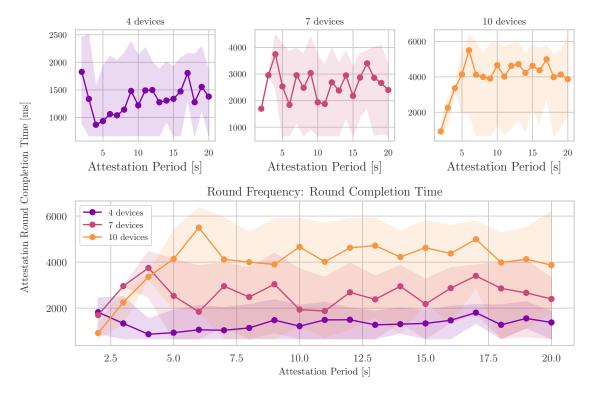

|    | 6.4    | Round   | l Frequency Graphs                | 84                 |

| 7  | Con    | clusio  | n and Future Work                 | 90                 |

|    | 7.1    | Conclu  | usion                             | 90                 |

|    | 7.2    |         | e Work                            |                    |

| Rı | Blio   | γραφί   | α                                 | 93                 |

| •  | $\sim$ |         | <b>∽</b>                          | $ \sigma$ $\sigma$ |

# List of Figures

| 1.1  | Παράδειγμα διαμόρφωσης ΡΜΡ [19]                                                                     | 18        |

|------|-----------------------------------------------------------------------------------------------------|-----------|

| 1.2  | Διάγραμμα ακολουθίας της Φάσης Εξερεύνησης με 2 συσκευές                                            | 22        |

| 1.3  | Διάγραμμα ακολουθίας ενός Γύρου Επαλήθευσης με 2 συσκευές                                           | 22        |

| 1.4  | Τοπολογία δικτύου: Κόμβοι $1,2,3,4,,N$ είναι όλοι συνδεδεμένοι                                      | 22        |

| 1.5  | Πλαχέτα ESP32-C3 Supermini                                                                          | 23        |

| 1.6  | Διάγραμμα Tasks RTOS για το Πλαίσιο Απομαχρυσμένης Επαλήθευσης                                      | 27        |

| 1.7  | Χρήση CPU σε βάθος χρόνου με περίοδο 12s                                                            | 29        |

| 1.8  | Χρήση CPU σε βάθος χρόνου με περίοδο 6s                                                             | 29        |

| 1.9  | Μέση χρήση CPU vs αριθμός συσκευών                                                                  | 30        |

| 1.10 | Μέγιστη χρήση RAM vs αριθμός συσκευών                                                               | 30        |

| 1.11 | Χρόνος απόχρισης μίας αίτησης RA vs αριθμός συσχευών                                                | 31        |

| 1.12 | Χρόνος ολοκλήρωσης κύκλου RA vs αριθμός συσκευών                                                    | 31        |

| 1.13 | Μέση χρήση CPU vs περίοδος RA. Η CPU μειώνεται με αύξηση της                                        |           |

|      | περιόδου                                                                                            | 32        |

| 1.14 | Μέγιστη χρήση RAM vs περίοδος RA. Το αποτύπωμα μνήμης παραμένει σχεδόν ανεπηρέαστο                  | 33        |

| 1.15 | Ποσοστό χρονικών υπερβάσεων vs περίοδος RA. Μικρές περίοδοι                                         |           |

|      | αυξάνουν τις υπερβάσεις                                                                             | 33        |

| 1.16 | Χρόνος απόχρισης μίας αίτησης RA vs περίοδος. Σταθεροποιείται                                       |           |

|      | πάνω από χρίσιμη περίοδο.                                                                           | 34        |

| 1.17 | Χρόνος ολοκλήρωσης κύκλου RA vs περίοδος. Σταθεροποιείται όταν                                      |           |

|      | η περίοδος ξεπερνά το κρίσιμο όριο.                                                                 | 34        |

| 3.1  | PMP Configuration Example [19]                                                                      | 42        |

| F 1  |                                                                                                     | <b>50</b> |

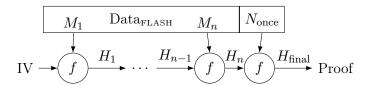

| 5.1  | Hash Diagram of $Hash(N_{once}  Flash)$                                                             | 59        |

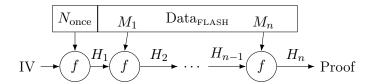

| 5.2  | Hash Diagram of $Hash(Flash  N_{once})$                                                             | 60        |

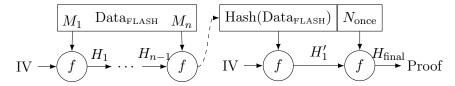

| 5.3  | Hash Diagram of $Hash(Hash(Flash), N_{once})$                                                       | 60        |

| 5.4  | Sequence diagram of Exploration Phase with 2 devices                                                | 63<br>63  |

| 5.5  | Sequence diagram of an Attestion Round with 2 devices                                               | 64        |

| 5.6  | Network Topology: Nodes $1, 2, 3, 4,, N$ are all connected                                          |           |

| 5.7  | ESP32-C3 Functional Block Diagram [10]                                                              | 66        |

| 5.8  | ESP32-C3 Supermini Board                                                                            | 66<br>73  |

| 5.9  | RTOS Task Diagram for the Attestation Framework [10]                                                | 13        |

| 6.1  | CPU usage over time for a round period of 12 seconds. Lines correspond to 2, 4, 6, 8 and 10 devices | 79        |

|      | correspond to $2, 4, 0, 0$ and to devices                                                           | 13        |

| 6.2  | CPU usage over time for a round period of 6 seconds. Lines             |    |

|------|------------------------------------------------------------------------|----|

|      | correspond to 2, 4, 6, 8 and 10 devices                                | 80 |

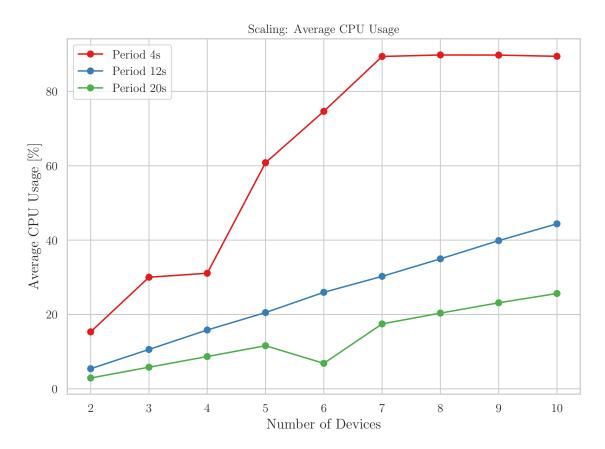

| 6.3  | Average CPU usage versus number of devices for three different         |    |

|      | attestation periods. As expected, CPU usage increases with the         |    |

|      | number of devices and higher frequency rounds                          | 81 |

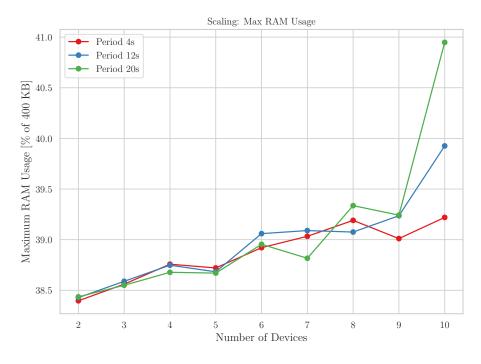

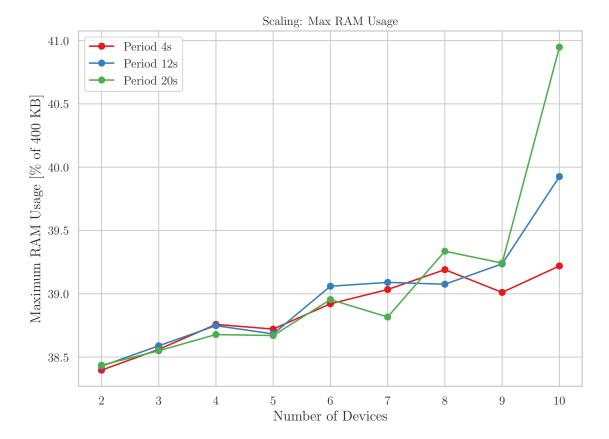

| 6.4  | Maximum RAM usage (stack + total heap) versus number of devices.       |    |

|      | Three different attestation periods are shown. Memory usage remains    |    |

|      | relatively stable with increasing devices                              | 82 |

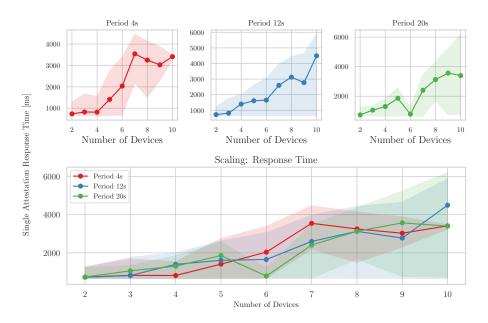

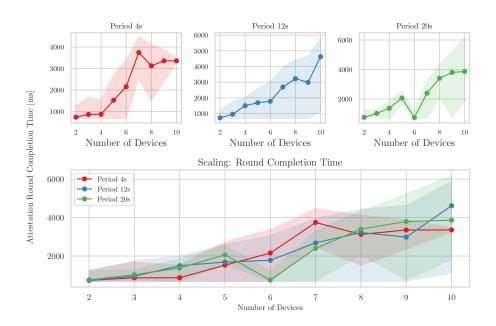

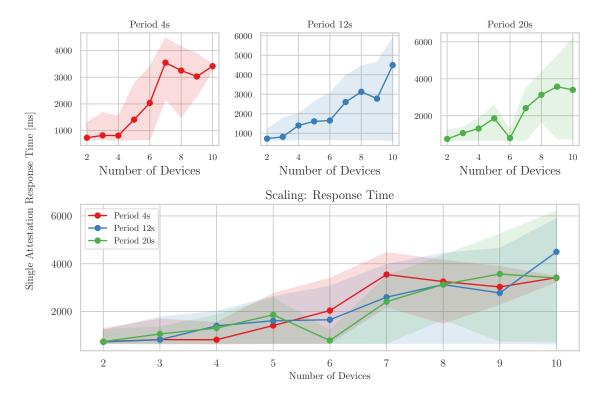

| 6.5  | Response time statistics (average, minimum, maximum) of single         |    |

|      | attestation requests versus number of devices. The plot highlights     |    |

|      | how response time grows with higher device counts                      | 83 |

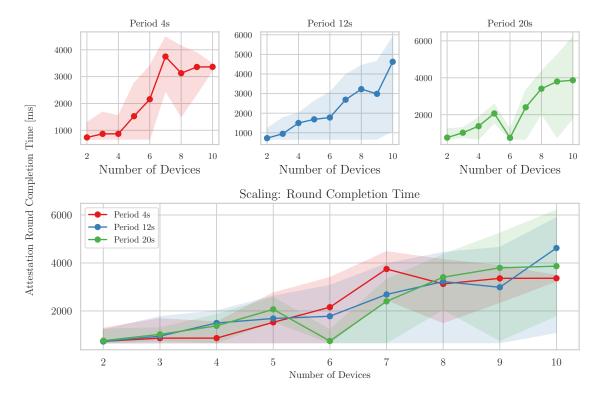

| 6.6  | Attestation round completion time (average, minimum, maximum)          |    |

|      | versus number of devices. Completion time scales with device count     |    |

|      | and attestation frequency                                              | 84 |

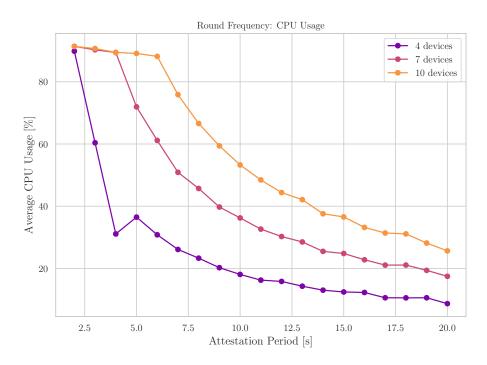

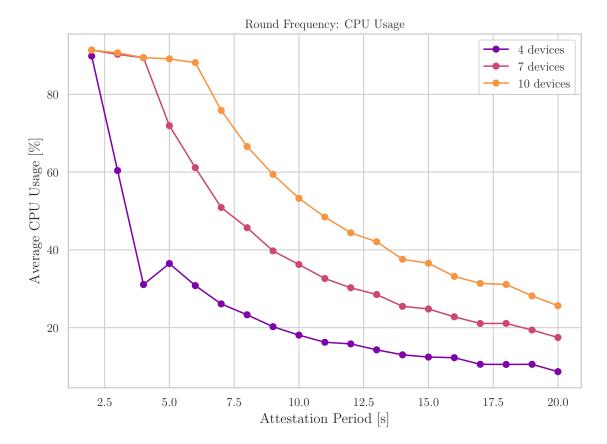

| 6.7  | Average CPU usage versus attestation period for 4, 7 and 10 devices.   |    |

|      | CPU usage decreases as the attestation period increases                | 85 |

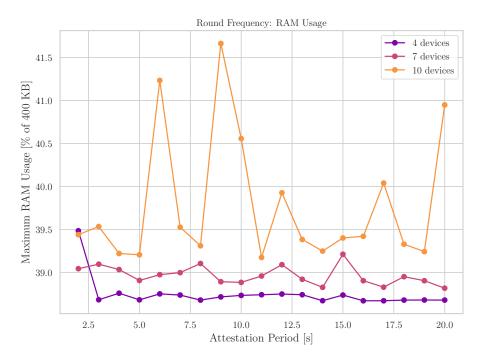

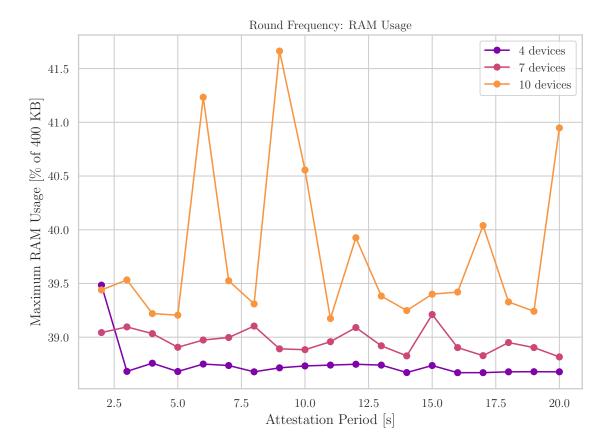

| 6.8  | Maximum RAM usage versus attestation period for 4, 7 and 10            |    |

|      | devices. Memory consumption remains mostly constant across periods.    | 86 |

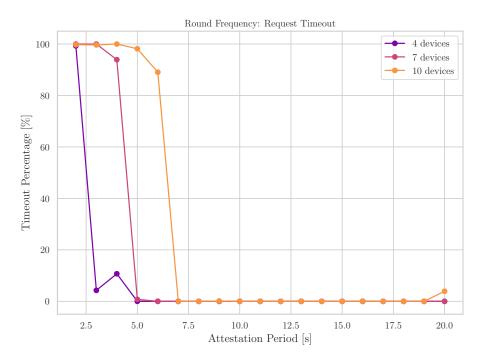

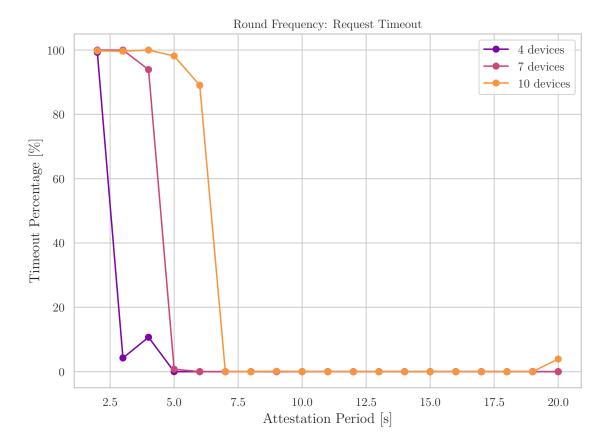

| 6.9  | Request timeout percentage versus attestation period for 4, 7 and 10   |    |

|      | devices. Higher frequency rounds increase the probability of timeouts. | 87 |

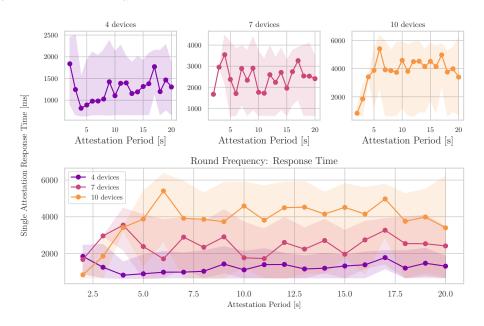

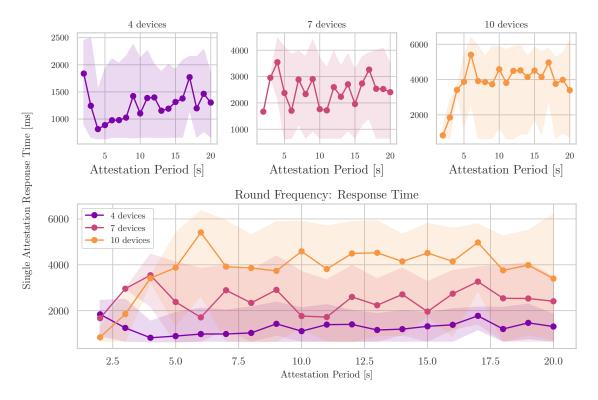

| 6.10 | Single attestation request response time (average, minimum, max-       |    |

|      | imum) versus attestation period for 4, 7 and 10 devices. Times         |    |

|      | exceeding the timeout are ignored                                      | 88 |

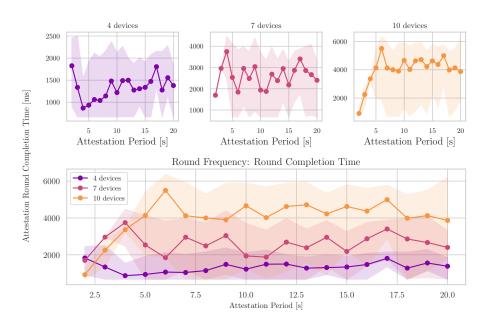

| 6.11 | Attestation round completion time (average, minimum, maximum)          |    |

|      | versus attestation period for 4, 7 and 10 devices. Completion times    |    |

|      | exceeding the timeout are ignored                                      | 89 |

# List of Tables

| 1.1 | Specifications of ESP32-C3 | 23 |

|-----|----------------------------|----|

| 5.1 | Specifications of ESP32-C3 | 65 |

# Chapter 1

# Εκτεταμένη Περίληψη στα Ελληνικά

# 1.1 Εισαγωγή

$To \Delta$ ιαδίχτυο των  $\Pi$ ραγμάτων (IoT) αναφέρεται σε ένα δίχτυο διασυνδεδεμένων συσχευών, αισθητήρων, ανθρώπων και υπηρεσιών, οι οποίες επικοινωνούν και ανταλλάσσουν δεδομένα με σκοπό την επίτευξη κοινών στόχων σε ποικίλα πεδία εφαρμογής. Η ευρεία διάδοση χαμηλού κόστους μικροελεγκτών και αισθητήρων έχει καταστήσει δυνατή την ενσωμάτωση του ΙοΤ σε πλήθος τομέων, όπως η υγειονομική περίθαλψη, όπου χρησιμοποιείται για απομακρυσμένη παρακολούθηση ασθενών και καταπιώμενες ιατρικές συσκευές· τα έξυπνα δίκτυα ενέργειας, όπου συμβάλλει στην ορθολογική διαχείριση ανανεώσιμων πηγών και την εξισορρόπηση της παραγωγής και κατανάλωσης· ο αυτοματισμός κατοικιών, για τον έλεγχο κλίματος, φωτισμού, ασφάλειας και ενεργειακής διαχείρισης $\cdot$  η βιομηχανία αυτοκινήτων, μέσω συστημάτων ασφαλείας, παρακολούθησης και άνεσης καθώς και οι έξυπνες πόλεις, με εφαρμογές στη διαχείριση απορριμμάτων, τη βελτιστοποίηση της κυκλοφορίας και της δημόσιας συγκοινωνίας.  $\Pi$ αρά τα σημαντικά οφέλη, η ραγδαία εξάπλωση των συσκευών  ${

m IoT}$  συνεπάγεται σοβαρές προκλήσεις ασφάλειας, καθώς οι ευπάθειες σε δικτυωμένα συστήματα μπορούν να εκμεταλλευτούν σε μεγάλη κλίμακα, με ενδεχόμενες συνέπειες την παραβίαση της ιδιωτικότητας των ασθενών, τον χίνδυνο για τη ζωή των ανθρώπων στις μεταφορές, την υπονόμευση της δημόσιας υποδομής ή τη χρήση τους σε εχτεταμένες χυβερνοεπιθέσεις, όπως οι επιθέσεις DDoS. Επομένως, καθίσταται αναγκαία η εφαρμογή αυστηρών προτύπων ασφάλειας και στρατηγικών μετριασμού των κινδύνων.  $\Sigma$ το πλαίσιο αυτό, η  $\Lambda$ πομακρυσμένη Επαλήθευση (Remote Attestation) αποτελεί κρίσιμη τεχνική για την επαλήθευση της αχεραιότητας των συσχευών, ενώ η  $\Sigma$ υλλογιχή Απομαχρυσμένη  ${

m E}$ παλή ${

m \vartheta}$ ευση  $({

m Col}$ lective Remote Attestation) αντιμετωπίζει επιπλέον προκλήσεις σχετικές με τη διάδοση εμπιστοσύνης και την αποτελεσματική επικοινωνία σε μεγάλα δίκτυα ΙοΤ.

Η παρούσα διπλωματική εργασία συνεισφέρει με τον σχεδιασμό και την υλοποίηση ενός πλαισίου Συλλογικής Απομακρυσμένης Επαλήθευσης, το οποίο εκτελεί αμοιβαία και ετερογενή αυτο-επαλήθευση σε δίκτυα του Διαδικτύου των Πραγμάτων (IoT), χωρίς να απαιτείται η ύπαρξη κεντρικού Επαληθευτή. Το πλαίσιο έχει σχεδιαστεί για να συνοδεύεται από εγγυήσεις σε υλικό: secure boot, secure storage και Προστασία

Φυσικής Μνήμης (PMP) της αρχιτεκτονικής RISC-V. Για την υλοποίηση επιλέχθηκε ο μικροελεγκτής ESP32-C3, με σκοπό το πλαίσιο να είναι άμεσα προσαρμόσιμο στη βιομηχανία και να αποτελέσει τη βάση για περαιτέρω έρευνα στο πεδίο της Απομακρυσμένης Επαλήθευσης.

# 1.2 Υπόβαθρο

Αυτή η ενότητα παρουσιάζει τα βασικά τεχνικά θεμέλια για την κατανόηση της ασφάλειας σε ενσωματωμένα συστήματα ΙοΤ, καλύπτοντας ενσωματωμένα συστήματα, ΙοΤ, κρυπτογραφία και απομακρυσμένη επαλήθευση.

# 1.2.1 Ενσωματωμένα Συστήματα και $\Delta$ ιαδίκτυο των Πραγμάτων

Τα ενσωματωμένα συστήματα είναι εξειδικευμένοι υπολογιστές σχεδιασμένοι για συγκεκριμένες λειτουργίες μέσα σε μεγαλύτερα συστήματα. Διαφέρουν από τους υπολογιστές γενικής χρήσης καθώς εκτελούν προκαθορισμένες εργασίες υπό συνθήκες πραγματικού χρόνου. Η δικτύωση είναι κρίσιμη για την επικοινωνία: Δικτυώνονται τόσο με ενσύρματα πρωτόκολλα (I2C, SPI και CAN) όσο και με ασύρματα (Wi-Fi, Bluetooth/BLE, Zigbee, Z-Wave, Thread) για την συνεργασία και επικοινωνία με άλλες συσκευές. Εξοπλίζονται τυπικά με Λειτουργικά Συστήματα Πραγματικού Χρόνου (RTOS) εξασφαλίζουν χρονικά προβλέψιμη εκτέλεση εργασιών μέσω αλγορίθμων χρονοπρογραμματισμού (pre-emptive, round-robin). Παραδείγματα είναι το FreeR-TOS, Zephyr και VxWorks.

Το ΙοΤ αναφέρεται σε δίκτυα συσκευών που επιτρέπουν απομακρυσμένη παρακολούθηση ή έλεγχο. Τα τυπικά επίπεδα μιας συσκευής ΙοΤ είναι το επίπεδο αισθητήρων, το επίπεδο δικτύου, το επίδπεδο επεξεργασίας δεδομένων και το επίπεδο εφαρμογής.

Στρώμα Αισθητήρων Συσκευές που συλλέγουν ή ενεργούν στα δεδομένα.

**Δικτυακό Στρώμα** Μεταφορά δεδομένων μέσω πρωτοκόλλων όπως Wi-Fi, Lo-RaWAN ή κινητά.

Στρώμα Επεξεργασίας Δεδομένων Αποθήκευση και ανάλυση στο cloud ή σε edge servers.

Στρώμα Εφαρμογής Ορατό στους χρήστες, για dashboards και έλεγχο συσκευών [20].

## 1.2.2 RISC-V אמו Physical Memory Protection

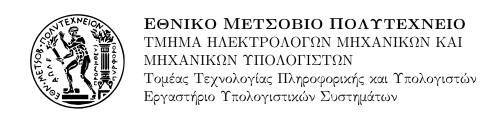

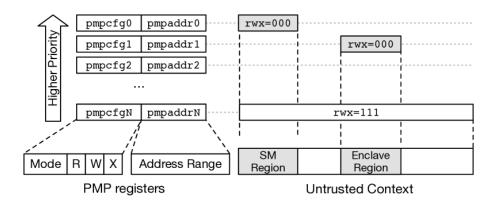

Το RISC-V είναι ανοιχτού κώδικα ISA, που έχει εισχωρήσει στις ΙοΤ συσκευές χαμηλού κόστους [17]. Η Προστασία Φυσικής Μνήμης (PMP), μια δημοφιλή επέκταση του RISC-V επιτρέπει απομόνωση μνήμης με έλεγχο πρόσβασης ανά περιοχή [19] μέσω ειδικών καταχωρητών όπως φαίνεται στο Σχήμα 1.1, απλούστερη από TDX/AMD SEV ή TrustZone για συστήματα χωρίς MMU.

Figure 1.1: Παράδειγμα διαμόρφωσης PMP [19]

### 1.2.3 Κρυπτογραφία

Η κρυπτογραφία εξασφαλίζει εμπιστευτικότητα, ακεραιότητα και αυθεντικότητα μέσω των μηχανισμών:

Κατακερματισμός Μετατρέπει δεδομένα οποιουδήποτε μεγέθους σε σταθερού μέγεθους περίληψη, π.χ., SHA-256, για έλεγχο ακεραιότητας.

Ασύμμετρη Κρυπτογραφία Ζεύγη δημόσιου/ιδιωτικού κλειδιού για ασφαλή κρυπτογράφηση και ψηφιακές υπογραφές (RSA, ECC).

Κώδικα Αυθεντικοποίησης Μηνύματος MACs και HMACs πιστοποιούν μηνύματα με συμμετρικά κλειδιά.

## 1.2.4 Εμπιστοσύνη και Secure Boot

Η Root of Trust (RoT) είναι έμπιστο υλικό που επιτρέπει την αλυσίδα εμπιστοσύνης (CoT) για επαλήθευση συστατικών συστήματος. Το Secure Boot επαληθεύει διαδοχικά το λογισμικό προς εκτέλεση χρησιμοποιώντας κρυπτογραφικούς ελέγχους ξεκινώντας από μια Ρίζα Εμπιστοσύνης (RoT).

# 1.2.5 Απομακρυσμένη Επαλήθευση

Η Απομαχρυσμένη Επαλήθευση (RA) επιτρέπει σε έναν επαληθευτή να ελέγξει την αχεραιότητα μιας απομαχρυσμένης συσκευής, βασιζόμενη σε μια Root of Trust (RoT) που προστατεύει χρίσιμες λειτουργίες. Ο prover μετρά (hash) τη διαμόρφωση ή τη συμπεριφορά του σε πραγματιχό χρόνο (PM, DM, EM, CF, SF) [23] και στέλνει αναφορά (attestation report) μαζί με έναν nonce και υπογραφή ή MAC για να να διασφαλιστεί η αυθεντιχότητα. Ο επαληθευτής ελέγχει την εγχυρότητα συγχρίνοντας τον hash ή επαληθεύοντας την υπογραφή/MAC. Σε μεγάλες αποχεντρωμένες υλοποιήσεις, η επαλήθευση χατανέμεται είτε με Self πρωτόχολλα (Self-V, Self-L, Self-LC) είτε με External πρωτόχολλα (Neighbor, Jury). Υλιχές RoT, όπως TPM, DICE, TrustZone, Intel SGX/TDX χαι RISC-V PMP, εξασφαλίζουν ότι το λογισμιχό επαλήθευσης χαι τα μυστιχά χλειδιά παραμένουν ασφαλή [2], [13], [14], [18], [25]. Τέλος, η Συλλογιχή RA (CRA) μειώνει το υπολογιστιχό χαι διχτυαχό φορτίο συγχεντρώνοντας επαληθεύσεις ομάδων συσχευών, ενώ τα μοντέλα απειλών περιλαμβάνουν λογισμιχούς αντιπάλους,

κινητούς αντιπάλους, μη-παρεμβατικούς και παρεμβατικούς φυσικούς επιτιθέμενους, καθώς και αντιπάλους τύπου Dolev-Yao με πλήρη έλεγχο του δικτύου [9], [23].

# 1.3 Σχετική Βιβλιογραφία

### 1.3.1 PMP σε RTOS και Απομακρυσμένη Βεβαίωση

Στα πλαίσια της διπλωματικής του, ο Larmann [24] τροποποίησε τον πυρήνα του FreeRTOS ώστε να ρυθμίζει δυναμικά τις εγγραφές PMP σε κάθε εναλλαγή διεργασίας, απομονώνοντας τις και τον πυρήνα. Οι περιοχές μνήμης ορίστηκαν μέσω linker scripts και χαρτογραφήθηκαν με τη λειτουργία Top-of-Range ενώ υποστηρίχθηκε και η ασφαλής δυναμική κατανομή μνήμης μέσω PMP. Τέλος ενσωματώθηκε το σχήμα κρυπτογραφήσης PRINCE για την μνήμη, ελεγχόμενο από δεσμευμένα bits στις εγγραφές PMP.

Το LIRA-V [16] παρουσιάζει το PMP ως RoT για απομακρυσμένη επαλήθευση σε μικροελεγκτές RISC-V. Ο κώδικας ROM φιλοξενεί κλειδιά και τις κρυπτογραφικές ρουτίνες, ενώ η PMP δημιουργεί περιοχές μόνο-εκτέλεσης για την προστασία των κλειδιών υπογραφής. Μετά την επανεκκίνηση, η PMP ρυθμίζεται και κλειδώνεται. Κατόπιν αιτήματος, μετράται η μνήμη και υπογράφεται για την παραγωγή απόδειξης βεβαίωσης. Το προτεινόμενο πρωτόκολλο αμοιβαίας επαλήθευσης δημιουργεί στη συνέχεια ασφαλές κανάλι με χρήση ECDH και κρυπτογραφημένων αποδείξεων.

### 1.3.2 Ρίζες Εμπιστοσύνης από την ΤCG

Πέρα από την PMP, η Trusted Computing Group (TCG) έχει ορίσει εναλλακτικές ρίζες εμπιστοσύνης υλικού. Το Trusted Platform Module (TPM) [3] παρέχει ασφαλή δημιουργία, αποθήκευση και χρήση κρυπτογραφικών κλειδιών, διατηρώντας μετρήσεις firmware και λειτουργικού συστήματος σε Platform Configuration Registers. Συστήματα όπως το TRAP [2] χρησιμοποιούν TPM για ανίχνευση αλλοίωσης κώδικα και επαλήθευση κόμβων.

Η Device Identifier Composition Engine (DICE) είναι μια ελαφρύτερη ρίζα εμπιστοσύνης που παράγει εφήμερες κρυπτογραφικές ταυτότητες κατά την εκκίνηση συνδυάζοντας ένα μοναδικό μυστικό συσκευής με μετρήσεις firmware. Το MATCH-IN αξιοποιεί DICE για αμοιβαία βεβαίωση σε ΙοΤ δίκτυα, εκδίδοντας πιστοποιημένες ταυτότητες συσκευών και επιτρέποντας αμοιβαία αυθεντικοποιημένα TLS κανάλια που αποδεικνύουν την αξιοπιστία των συσκευών.

# 1.3.3 Εναλλακτικές Ρίζες Εμπιστοσύνης της Ακαδημαϊκής Κοινότητας

Πολλές δημοσιεύσεις προτείνουν ελαφρυές, προσαρμοσμένες ρίζες εμπιστοσύνης για μικροελεγκτές. Το GAROTA εισάγει ένα ελάχιστο, τυπικά επαληθευμένο υλικό που τρέχει παράλληλα με την CPU, διασφαλίζοντας την εκτέλεση κρίσιμων ενεργειών ακόμη και υπό παραβιασμένου λογισμικού. Το PRoM στοχεύει κακόβουλο λογισμικό που μετακινείται δυναμικά, μετρώντας τυχαία επιλεγμένα τμήματα μνήμης παράλληλα σε

πολλαπλούς πυρήνες, μειώνοντας τον διαθέσιμο χρόνο απόκρυψης και διατηρώντας υψηλή διαθεσιμότητα. Τέλος, το RATA αντιμετωπίζει το πρόβλημα ΤΟCΤΟU καταγράφοντας με ασφάλεια τον χρόνο τελευταίας τροποποίησης της μνήμης προγράμματος, επιτρέποντας εκ των υστέρων ανίχνευση αλλαγών και μειώνοντας το υπολογιστικό κόστος όταν η μνήμη είναι γνωστό ότι είναι καθαρή.

# 1.3.4 Συλλογικά Πρωτόκολλα Απομακρυσμένης Επαλήθευσης

Η επεκτασιμότητα είναι κρίσιμη για μαζικά δίκτυα συσκευών. Το SEDA οργανώνει τις συσκευές σε επικαλυπτόμενο δένδρο ώστε να βεβαιώνουν αναδρομικά τους γείτονες και να συγκεντρώνουν αποτελέσματα, επιτρέποντας στον επαληθευτή να επιβεβαιώσει την ακεραιότητα ολόκληρου του σμήνους με μία υπογεγραμμένη αναφορά. Το HEALED επεκτείνει τη βεβαίωση προσθέτοντας αποκατάσταση: εντοπίζει αλλοιωμένα τμήματα μνήμης με χρήση Merkle Hash Tree, αντλεί σωστό κώδικα από αξιόπιστο κόμβο και επιδιορθώνει τη συσκευή, επαναφέροντάς την σε αξιόπιστη κατάσταση.

# 1.4 Το Πλαίσιο Απομακρυσμένης Επαλήθευσής μας

### 1.4.1 Κίνητρο και Απαιτήσεις

### Κίνητρο

Πολλές υπάρχουσες λύσεις απομαχρυσμένης επαλήθευσης απαιτούν εξειδικευμένο υλικό ή μη τυποποιημένα εξαρτήματα, περιορίζοντας την υιοθέτησή τους. Η εργασία μας στοχεύει στη δημιουργία ενός πρακτικού πλαισίου RA για πραγματικές, χαμηλού κόστους πλατφόρμες IoT, αξιοποιώντας το RISC-V PMP ως ρίζα εμπιστοσύνης (RoT), παρέχοντας μια βάση για μελλοντική έρευνα και υιοθέτηση.

### Σύστημα, Μοντέλο Απειλών και Απαιτήσεις

Το πλαίσιο μας υποθέτει ανάπτυξη με έναν μόνο ιδιοκτήτη, ο οποίος εκτελεί μια φάση εκτός σύνδεσης, κατά την οποία οι συσκευές προγραμματίζονται με κώδικα, κλειδιά και υπογραφές. Οι συσκευές λειτουργούν τόσο ως αποδείκτες όσο και ως επαληθευτές, πραγματοποιώντας αμοιβαία αυτο-επαλήθευση ώστε να επιτυγχάνεται αποκεντρωμένη παρακολούθηση ακεραιότητας. Υιοθετούμε το μοντέλο κινητού αντιπάλου λογισμικού, υποθέτοντας ότι ο επιτιθέμενος μπορεί να έχει πλήρη έλεγχο των ευάλωτων εφαρμογών και συμμετέχει στο δίκτυο, αλλά δεν μπορεί να παρακάμψει τη RoT, το secure boot ή να σπάσει τα κρυπτογραφικά σχήματα. Η RoT είναι η απομόνωση μνήμης μέσω PMP, ενώ το secure boot και η ασφαλής αποθήκευση κλειδιών διασφαλίζουν ότι οι συσκευές ξεκινούν σε επιτρεπόμενη κατάσταση και προστατεύουν το κρυπτογραφικό υλικό, παρέχοντας ένα ισχυρό και επεκτάσιμο θεμέλιο εμπιστοσύνης. Χρησιμοποιούνται nonces για την αποτροπή επιθέσεων επανάληψης και τυχαίες περίοδοι επαλήθευσης για τη μείωση κινδύνων ΤΟCTOU. Η επαλήθευση ακεραιότητας ακολουθεί την προσέγγιση Program Memory Attestation σε Harvard αρχιτεκτονικές, υπ

ολογίζοντας hash της μνήμης προγράμματος για την ανίχνευση αλλοιώσεων, αντί για επαλήθευση της ροής εκτέλεσης (control-flow attestation) ή εναλλακτική μεθόδου.

### Εκτός Πεδίου Εφαρμογής

Φυσικές επιθέσεις, κακόβουλος κώδικας που παραμένει μόνο στη μνήμη χωρίς μόνιμα ίχνη, επιθέσεις πλευρικού καναλιού και DDoS εξαιρούνται από το μοντέλο μας. Η επαλήθευση ροής εκτέλεσης δεν υλοποιείται λόγω πολυπλοκότητας και απαιτήσεων πόρων. Αν και το secure boot, η ασφαλής αποθήκευση και η απομόνωση μνήμης μέσω PMP δεν υλοποιούνται στο πλαίσιο αυτής της εργασίας, το πλαίσιο έχει σχεδιαστεί ώστε να μπορεί να τα ενσωματώσει σε μελλοντικές επεκτάσεις, διατηρώντας την έμφαση στη δημιουργία μιας επεκτάσιμης και κλιμακούμενης βάσης απομακρυσμένης επαλήθευσης.

### 1.4.2 Σχεδίαση Πρωτοκόλλου

### Προκαταρκτικές Σκέψεις Σχεδιασμού

Μία αφελής προσέγγιση, όπου ο Αποδεικτής απλώς επιστρέφει την τιμή Hash(Flash), είναι ευάλωτη σε επιθέσεις επανάληψης. Η εισαγωγή ενός τυχαίου  $N_{once}$  από τον  $\rm E$ παληθευτή μειώνει τον κίνδυνο καθώς επιβάλλει φρεσκάδα στην απόδειξη, αλλά η θέση του στο hash έχει σημασία. Οι τρεις υποψήφιες μορφές είναι  $Hash(N_{once}||Flash)$ ,  $Hash(Flash||N_{once})$ , και  $Hash(Hash(Flash), N_{once})$ . Η πρώτη απαιτεί από τον Επαληθευτή να γνωρίζει ολόκληρο το περιεχόμενο του flash για την επαληθευση, κάτι που δεν κλιμακώνεται εκτός αν όλες οι συσκευές είναι ίδιες. Οι δύο τελευταίες απαιτούν μόνο την αποθήχευση του Hash(Flash) ή της ενδιάμεσης χατάστασης του χαταχερματισμού, υποθέτοντας πως χρησιμοποιείται κατασκευή Merkle-Damgård, επομένως είναι ευάλωτες σε επιθέσεις τύπου ΤΟΟΤΟυ εάν ένας επιτιθέμενος μπορεί να επέμβει μετά από μερικό υπολογισμό. Σε όλες τις περιπτώσεις απαιτείται εγγύηση αυθεντικότητας επομένως, η οποία μπορεί να επιτευχθεί μέσω ΗΜΑC με κοινό μυστικό κλειδί που προκύπτει από ECDH ή RSA key exchange. Τα δημόσια κλειδιά πρέπει να είναι υπογεγραμμένα από τον κατασκευαστή, ενώ τόσο τα κλειδιά όσο και η ρουτίνα επαλήθευσης πρέπει να αποθηκεύονται σε ασφαλή μνήμη και να προστατεύονται από secure boot. Με αυτές τις εγγυήσεις, ο Αποδεικτής μπορεί τοπικά να συγκρίνει το hash του flash με το Golden Hash και να στείλει μόνο ένα λογικό αποτέλεσμα (επιτυχία/αποτυχία) χωρίς να εκθέτει η ασφάλεια της Απομακρυσμένης Επαλήθευσης.

#### Επισκόπηση Πρωτοκόλλου

Το προτεινόμενο πρωτόχολλο πραγματοποιεί Αποχεντρωμένη Αμοιβαία Απομαχρυσμένη Επαλήθευση με Τοπικό Έλεγχο Αχεραιότητας flash και περιλαμβάνει:

- Φάση Εκτός Σύνδεσης: Προμήθεια συσκευών με firmware, ιδιωτικά/δημόσια κλειδιά, υπογραφές κατασκευαστή και ασφαλή αποθήκευση κλειδιών.

- Στάδιο Εχχίνησης: Το secure boot επαληθεύει το firmware, αποχρυπτογραφεί τα κλειδιά, υπολογίζει και αποθηκεύει το έγκυρο Golden Hash της flash, και προστατεύει περιοχές μνήμης και κλειδιών.

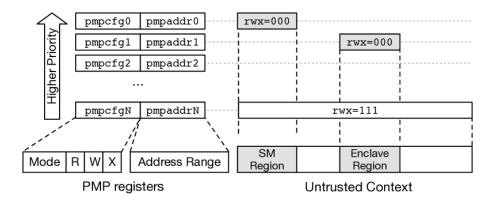

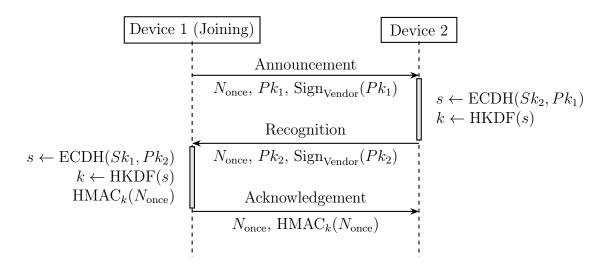

• Φάση Εξερεύνησης: Οι συσκευές ανακαλύπτουν γείτονες μέσω τριπλής χειραψίας (ανακοίνωση, αναγνώριση, επιβεβαίωση), επαληθεύουν υπογεγραμμένα κλειδιά και υπολογίζουν κοινό κλειδί ΗΜΑC μέσω ECDH+HKDF (Σχήμα 1.2).

Figure 1.2: Διάγραμμα αχολουθίας της Φάσης Εξερεύνησης με 2 συσκευές

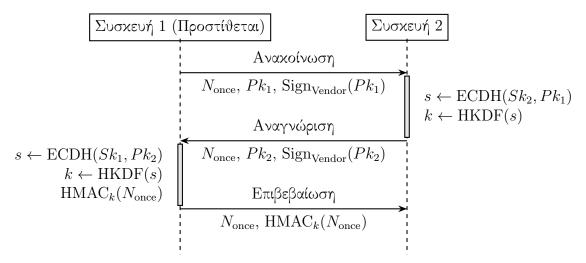

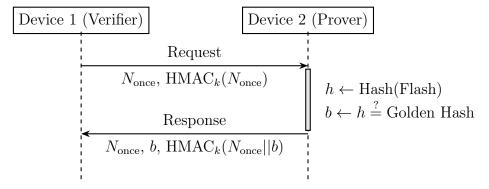

• Γύροι Επαλήθευσης: Κάθε συσκευή δρα ως Επαληθευτής στέλνοντας αιτήματα με φρέσκα nonces σε όλους τους γείτονες, ελέγχει τις απαντήσεις με ΗΜΑΟ εντός χρονικού ορίου και καταγράφει το αποτέλεσμα. Ως Αποδεικτής, η συσκευή εκτελεί αυτο-επαλήθευση συγκρίνοντας Hash(Flash) με το  $Golden\ Hash$  και στέλνει υπογεγραμμένη ανταπόκριση με το αποτέλεσμα (Σχήμα 1.3).

Figure 1.3: Διάγραμμα ακολουθίας ενός Γύρου Επαλήθευσης με 2 συσκευές

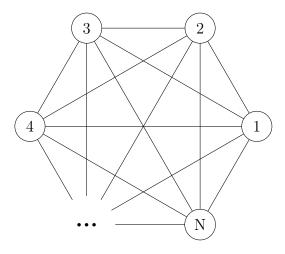

Όλες οι συσκευές αλληλο-επαληθεύονται με όσες βρίσκονται εντός εμβέλειας, σχηματίζοντας πλήρως συνδεδεμένο γράφο εμπιστοσύνης στην κοινή περίπτωση.

Figure 1.4: Τοπολογία δικτύου: Κόμβοι 1, 2, 3, 4, ..., N είναι όλοι συνδεδεμένοι

## 1.4.3 Υλοποίηση

### Υλικό Πλατφόρμας

Για την ανάπτυξη του Πλαισίου Απομακρυσμένης Επαλήθευσης επιλέχθηκε το τσιπ ESP32-C3 της Espressif λόγω χαμηλού κόστους, μικρών διαστάσεων και πλούσιων

δυνατοτήτων.

Table 1.1: Specifications of ESP32-C3

| Χαρακτηριστικό                         | Τιμή/Πληροφορίες            |

|----------------------------------------|-----------------------------|

| Αρχιτεκτονική                          | 32-bit RISC-V Μονοπύρηνος   |

| Pipeline                               | 4-stage, in-order, scalar   |

| Μέγιστη Συχνότητα                      | 160 MHz                     |

| Wi-Fi Συνδεσιμότητα                    | 2.4 GHz Wi-Fi (802.11b/g/n) |

| Bluetooth Συνδεσιμότητα                | Bluetooth 5 (LE)            |

| Εσωτερική ROM                          | 384 KB                      |

| Εσωτερική SRAM                         | 400 KB                      |

| Μνήμη RTC (Χαμηλής Ισχύος)             | 8 KB                        |

| Μέγιστη Υποστηριζόμενη Εξωτερική Μνήμη | Up to 16 MB                 |

| Πλήθος GPIO                            | 16 or 22                    |

| Τάση Εισόδου                           | 3.0 V to 3.6 V              |

| Κρυπτογραφικοί Επιταχυντές             | AES, SHA, RSA, HMAC, RNG    |

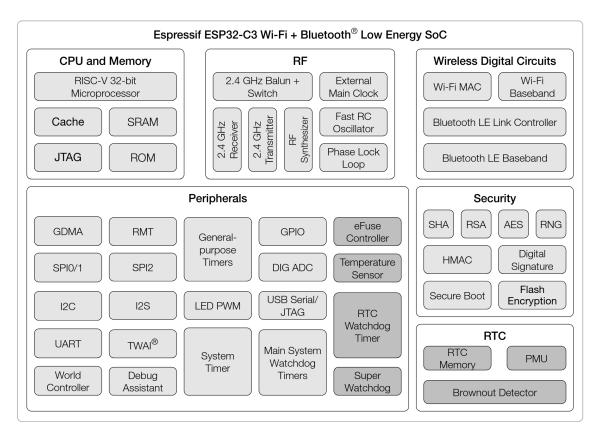

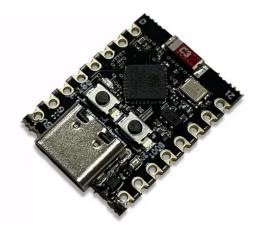

Στον πίνακα 1.1 παρατίθονται κάποια από τα χαρακτηριστικά του. Πρόκειται για έναν 32-bit single-core επεξεργαστή RISC-V με συχνότητα έως 160 MHz, 4 MB flash, 400 KB SRAM, Wi-Fi 2,4 GHz, Bluetooth 5 LE, καθώς και επιταχυντές υλικού για RSA, SHA, HMAC, AES και ασφαλές RNG. Υποστηρίζει secure boot, κρυπτογραφημένη αποθήκευση flash και PMP, ικανοποιώντας τις απαιτήσεις μας.

Figure 1.5: Πλακέτα ESP32-C3 Supermini

Στο Σχήμα 1.5 εμφανίζεται η πλακέτα ESP32-C3 Supermini που χρησιμοποιήθηκε στην ανάπτυξη. Αποτελεί μια πλέον οικονομική επιλογή, καθώς είναι διαθέσιμη σε τιμή μικρότερη των 2 ευρώ [30].

### Λογισμικό

Το πλαίσιο υλοποιήθηκε σε C για την ευκολότερη ενσωμάτωση με τις υπόλοιπες βιβλιοθήκες που αξιοποιήθηκαν:

FreeRTOS Το FreeRTOS είναι ένας πυρήνας λειτουργικού συστήματος πραγματικού χρόνου (RTOS) ανοιχτού κώδικα από την AWS, σχεδιασμένος για ενσωματωμένα

συστήματα με περιορισμένους πόρους. Διαθέτοντας πολυδιεργασία (multitasking), επικοινωνία μεταξύ εργασιών και μικρό αποτύπωμα μνήμης, το FreeRTOS είναι εξαιρετικά φορητό και έχει υιοθετηθεί ευρέως στο IoT, στα συστήματα αυτοκινήτων και στον βιομηχανικό αυτοματισμό, όπου η αποδοτική και προβλέψιμη απόδοση είναι κρίσιμης σημασίας.

ESP-IDF Το Espressif IoT Development Framework (ESP-IDF) είναι ένα ολοκληρωμένο, ανοικτού κώδικα SDK για τους μικροελεγκτές της Espressif, δομημένο πάνω στο FreeRTOS. Ενσωματώνει πληθώρα βιβλιοθηκών, συμπεριλαμβανομένων πρωτοκόλων δικτύωσης, επιπέδων αφαίρεσης υλικού. Η σχεδίαση του framework και το σύστημα μεταγλώττισης που βασίζεται στο CMake διευκολύνει την ανάπτυξη επεκτάσιμων και φορητών συστημάτων. Η απόφαση για την υιοθέτηση του ESP-IDF επηρεάστηκε σημαντικά από τον εγγενή ανοικτό του χαρακτήρα, ο οποίος επιτρέπει τη βαθιά παραμετροποίηση βασικών λειτουργιών—από τη διαχείριση μνήμης του FreeR-TOS και την πιθανή υλοποίηση απομόνωσης εργασιών μέσω της Προστασίας Φυσικής Μνήμης (Physical Memory Protection - PMP), έως την τροποποίηση της διαδικασίας Ασφαλούς Εκκίνησης (Secure Boot) για την ενίσχυση της Αλυσίδας Εμπιστοσύνης (Chain of Trust) του συστήματος.

MbedTLS Η MbedTLS, μια ελαφριά, ανοιχτού κώδικα κρυπτογραφική βιβλιοθήκη που αναπτύχθηκε από την ARM. Παρέχει μια ολοκληρωμένη σουίτα κρυπτογραφικών πρωτογενών συναρτήσεων και πρωτοκόλλων, οι οποίες αξιοποιήθηκαν στην παρούσα εργασία για την υλοποίηση αυθεντικότητα και γνησιότητα στην επικοινωνία. Επιπλέον, οι κρυπτογραφικές της συναρτήσεις χρησιμοποιήθηκαν για την επαλήθευση της ακεραιότητας της μνήμης flash έναντι μη εξουσιοδοτημένης τροποποίησης και αλλοίωσης δεδομένων. Η ενσωμάτωση της στο ESP-IDF παρέχει εύκολη χρήση των επιταχυντών υλικού.

### Δομή του Έργου

Το έργο ακολουθεί μια τυπική δομή ESP-IDF, επεκτεταμένη για να υποστηρίζει benchmarking, αρθρωτά στοιχεία και αυτοματισμό.

#### Πηγαίος Κώδικας

components Περιέχει αρθρωτό πηγαίο κώδικα: my\_attest για τη βασική λογική attestation, my\_benchmarking για τη μέτρηση απόδοσης, my\_crypto για κρυπτογραφικές λειτουργίες, my\_flash\_hash για τη μέτρηση ακεραιότητας της flash, και my\_net για τη δικτύωση.

scripts Μια συλλογή από scripts για δοχιμές, αποσφαλμάτωση (debugging) και αυτοματοποίηση.

### Παραγόμενα Αρχεία

benchmark Περιέχει όλα τα αυτόματα παραγόμενα αποτελέσματα του benchmarking, συμπεριλαμβανομένων των δεδομένων CSV (cpu\_usage\_time\_series, results.csv), των παραγόμενων plots και των debug logs.

build Περιέχει τα παραγόμενα από το ESP-IDF εκτελέσιμα (binaries) και αρχεία μεταγλώττισης (build files) για το flashing των συσκευών.

- keys Αποθηκεύει τα παραγόμενα κρυπτογραφικά κλειδιά τόσο για τον vendor όσο και για τις μεμονωμένες devices, συμπεριλαμβανομένων των υπογραφών.

- logs Περιέχει αρχεία καταγραφής (logs) από τη μεταγλώττιση και την παρακολούθηση της συσκευής.

### Αρχεία Ρυθμίσεων

- CMakeLists.txt Το χύριο script μεταγλώττισης για το σύστημα build του ESP-IDF.

- partitions.csv & .in Ο πίνακας κατάτμησης της μνήμης flash της συσκευής και το πρότυπό του.

- sdkconfig & .defaults Παραγόμενες και προκαθορισμένες από τον προγραμματιστή τιμές ρυθμίσεων για το framework και το ESP-IDF.

- .last\_build\_time Ένα αρχείο χρονοσφραγίδας (timestamp) που χρησιμοποιείται για τη βελτιστοποίηση της επανατοποθέτησης (redeployment).

### Αυτοματοποίηση Ανάπτυξης

Για την επιτάχυνση του κύκλου ανάπτυξης, δημιουργήθηκε μια σειρά από προγράμματα bash για την αυτοματοποίηση της μεταγλώττισης, του προγραμματισμού και της παρακολούθησης πολλαπλών συσκευών ταυτόχρονα. Χρησιμοποιώντας τα Tmux, Openssl και την εργαλειοθήκη ESP-IDF, αυτά τα scripts διαχειρίζονται τα πάντα, από τη δημιουργία κλειδιών έως τη μαζική ανάπτυξη και την ανάλυση αρχείων καταγραφής (logs).

- Ανάθεση Κλειδιών Σενάρια για τη δημιουργία και διαχείριση κρυπτογραφικών κλειδιών για τον προμηθευτή και τις συσκευές.

- generate\_vendor\_keys.sh: Αυτοματοποιεί τη δημιουργία ζευγών κρυπτογραφικών κλειδιών του προμηθευτή (vendor).

- generate\_sign\_device\_keys.sh: Δημιουργεί ένα ζεύγος κλειδιών για μια συσκευή και υπογράφει το δημόσιο κλειδί με το ιδιωτικό κλειδί του προμηθευτή.

- generate\_device\_partition\_binary.sh: Δημιουργεί ένα δυαδικό partition που περιέχει τη διεύθυνση MAC της συσκευής, όλα τα κλειδιά και τις υπογραφές.

- flash\_attestation\_partition.sh:  $\Delta$ ημιουργεί το τελιχό αρχείο partitions.csv, υπολογίζοντας το μέγεθος και τη θέση του attestation partition.

**Ανάπτυξη** Σενάρια για τον προγραμματισμό του firmware και την παρακολούθηση πολλαπλών συσκευών.

- find\_esp32\_dev.sh: Σαρώνει τις συσκευές του συστήματος για να βρει και να εμφανίσει όλες τις συνδεδεμένες πλακέτες ESP32.

- run\_device.sh: Προγραμματίζει μία μόνο συσκευή με τα απαιτούμενα κλειδιά και δυαδικά αρχεία, και στη συνέχεια ανοίγει έναν σειριακό monitor.

• run\_all.sh: Κάνει build το project και ενορχηστρώνει τον προγραμματισμό και την παρακολούθηση όλων των συνδεδεμένων συσκευών ταυτόχρονα, χρησιμοποιώντας το tmux.

Μέτρηση Επιδόσεων Σενάρια για την αυτοματοποίηση δοκιμών απόδοσης και την οπτικοποίηση των αποτελεσμάτων.

- benchmark.sh: Εκτελεί αυτοματοποιημένες δοκιμές και συλλέγει μετρήσεις (CPU, RAM, κ.λπ.) σε ένα αρχείο CSV.

- plot.py: Διαβάζει αρχεία CSV από τα benchmarks και δημιουργεί γραφήματα με τα δεδομένα απόδοσης.

**Διάφορα** Βοηθητικά scripts για παραμετροποίηση και αποσφαλμάτωση.

- update\_sdkconfig\_from\_defaults.sh: Ενημερώνει ένα υπάρχον αρχείο sdkconfig από ένα αρχείο προεπιλογών (defaults).

- generate\_partitions.sh:  $\Delta$ ημιουργεί το τελικό αρχείο partitions.csv για τη διάταξη της μνήμης flash της συσκευής.

- find\_errors.sh: Σαρώνει αρχεία καταγραφής (logs) για να βρει και να εξάγει μηνύματα 'Guru Meditation Error'.

- print\_keys.sh: Εμφανίζει τα κλειδιά από ένα δυαδικό αρχείο partition σε αναγνώσιμη από άνθρωπο δεκαεξαδική μορφή.

### Αρχιτεκτονική Πλαισίου

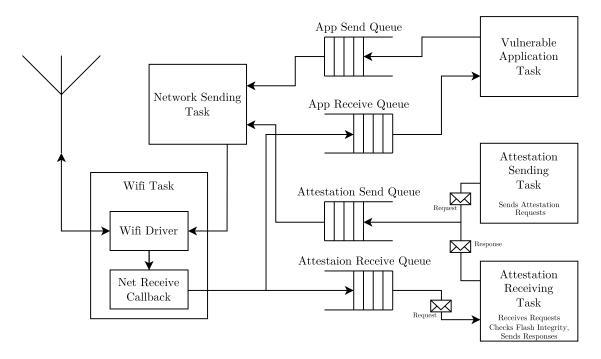

Το πλαίσιο σχεδιάστηκε γύρω από tasks και queues του FreeRTOS για modularity και real-time απόκριση. Κατά την εκκίνηση φορτώνονται τα credentials της συσκευής, ξεκινά η δικτύωση και οι tasks για Απομακρυσμένη Επαλήθευση και εφαρμογή.

Τα κύρια Tasks όπως φαίνονται και στο Σχήμα 1.6.

- Network Sending Task: Αποστέλλει πακέτα (ESP-NOW) από τις διεργασίες της Απομακρυσμένης Επαλήθευσης ή της εφαρμογής στο δίκτυο, προσθέτοντας ανάλογο αναγνωριστικό..

- Network Receiving Callback: Κατευθύνει εισερχόμενα πακέτα στις σωστές ουρές ανά τύπο μηνύματος.

- Attestation Sending Task: Ξεκινά ανακοινώσεις και αιτήματα επαλήθευσης.

- Attestation Receiving Task: Αντιδρά σε αιτήματα επαλήθευσης και καταγράφει αποτελέσματα από ανταποκρίσεις.

Figure 1.6: Διάγραμμα Tasks RTOS για το Πλαίσιο Απομακρυσμένης Επαλήθευσης

### Επιλογές Ρύθμισης του Πλαισίου

Το πλαίσιο έχει παραμετρικοποιηθεί με σταθερές χρόνου μεταγλώττισης που ρυθμίζονται στο αρχείο sdkconfig.defaults ή μέσω του menuconfig. Οι επιλογές κατηγοριοποιημένες:

- Pύθμιση Συσκευών Ορίζεται ο αριθμός των συσκευών (CONFIG\_MY\_NUM\_DEVICES), η παυση μετά την ανακάλυψη γειτόνων και timeout για επανασύνδεση γείτονα (CONFIG\_MY\_NEIGHBOURS\_FOUND\_WAIT\_MS, CONFIG\_MY\_TIME\_FROM\_LAST\_ATT\_RES\_TO\_RERECOG

- Pύθμιση Δικτύωσης Καθορίζει το μέγεθος πακέτου (CONFIG\_MY\_PACKET\_DATA\_MAX\_LENGTH), τη λογική επαναποστολής μηνυμάτων (CONFIG\_MY\_OFFLINE\_RESEND\_MAX\_COUNT, CONFIG\_MY\_RESEND\_DELAY\_MS) και την περίοδο ανακοινώσεων (CONFIG\_MY\_MSG\_ANNOUNCE\_SEND

- Περίοδο Επαλήθευσης Οι σταθερές CONFIG\_MY\_ATTESTATION\_INTERVAL\_MIN\_MS και CONFIG\_MY\_ATTESTATION\_INTERVAL\_MAX\_MS ορίζουν το τυχαίο χρονικό εύρος για την έναρξη νέων γύρων επαλήθευσης (attestation rounds).

- Επιλογές Καταγραφής Μια σειρά από σημαίες (flags) (CONFIG\_MY\_LOG\_...) για την ενεργοποίηση/απενεργοποίηση της αναλυτικής καταγραφής για συμβάντα δικτύου, μηνύματα, στατιστικά γειτόνων και γύρους πιστοποίησης, συν την περίοδο καταγραφής στατιστικών της CPU (CONFIG\_MY\_LOG\_CURRENT\_STATS\_PERIOD\_MS).

- Επιλογές Αξιολόγησης Απόδοσης Η επιλογή CONFIG\_MY\_BENCHMARKING ενεργοποιεί τη συλλογή μετρήσεων απόδοσης για διάρχεια που ορίζεται από την CONFIG\_MY\_BENCHMARK\_RUNTIME\_MS.

- Αναγνώριση Μηνυμάτων Οι CONFIG\_MY\_ATTESTATION\_MAGIC και CONFIG\_MY\_APP\_MAGIC είναι «μαγικοί αριθμοί» (magic numbers) που χρησιμοποιούνται για τη δρο-

μολόγηση εισερχόμενων πακέτων είτε στη μονάδα επαλήθευσης είτε στην εφαρμογή.

Επιλογές Κρυπτογραφίας Σημαίες όπως η CONFIG\_MY\_PK\_USE\_EC\_SECP192R1 επιλέγουν την ελλειπτική καμπύλη που χρησιμοποιείται για όλες τις λειτουργίες δημόσιου κλειδιού.

### Προκλήσεις Υλοποίησης και Παραλείψεις

Κατά την ανάπτυξη αντιμετωπίστηκαν προβλήματα όπως μη προγραμματιζόμενες συσκευές, ασταθείς USB hubs, σφάλματα χρονισμού δικτύου, συγκρούσεις MAC διευθύνσεων, ασυμφωνίες κατακερματισμού flash και buffer overflows, τα οποία αντιμετωπίστηκαν με επανασχεδιασμό κώδικα και έλεγχο μνήμης. Ορισμένες λειτουργίες ασφάλειας του υλικού (secure boot, κρυπτογραφημένη αποθήκευση, απομόνωση tasks μέσω PMP) έχουν εφαρμοστεί ανεξάρτητα της εργασίας αυτής στο παρελθόν και δεν υλοποιήθηκαν στο πλαίσιο αυτής της διπλωματικής αλλά η ενσωμάτωσή τους αποτελούν μελλοντική εργασία.

# 1.5 Αξιολόγηση

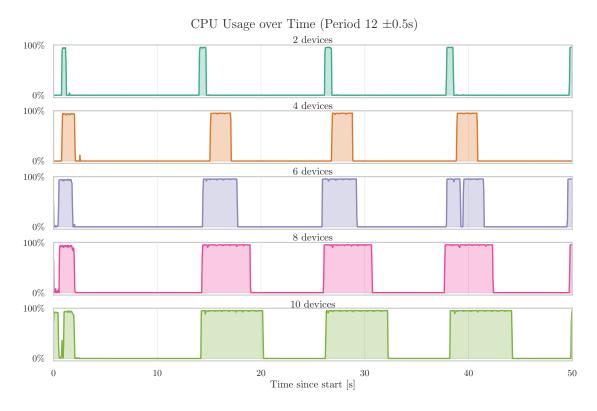

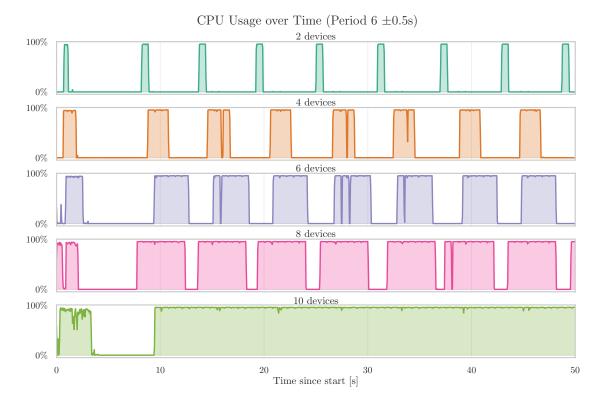

Αυτή η ενότητα παρουσιάζει την αξιολόγηση του συστήματός μας σε διαφορετικές διαμορφώσεις και φορτία, εστιάζοντας στη χρήση CPU, στην κατανάλωση μνήμης, στους χρόνους απόκρισης και στους χρόνους ολοκλήρωσης κύκλων απομακρυσμένης επαλήθευσης. Τα δεδομένα συλλέχθηκαν χρησιμοποιώντας το αυτοματοποιημένο script benchmark. sh σε  $10~{\rm ESP32-C3~Supermini~Boards}$ , με εκτελέσεις που διαφοροποιούν τόσο τον αριθμό των συσκευών (2–10) όσο και την περίοδο T των γύρων απομακρυσμένης επαλήθευσης (2–20s). T είναι η μέση τιμή της περίοδου καθώς για την αποφυγή επιθέσεων χρονισμού και συμφόρηση του δικτύου, η πραγματική περίοδος κάθε γύρου κάθε συσκευής επιλγόταν στο  $T\pm0.5s$ . Κάθε εκτέλεση διήρκησε 100s, με καταγραφή της CPU κάθε 100ms και συλλογή μέσων στατιστικών ανά συσκευή. Οι χρονικές υπερβάσεις (timeouts) συμβαίνουν αν η απόκριση υπερβεί T-1s, ενώ οι συγκεκριμένες ανταποκρίσεις δεν λήφθηκαν υπόψιν στους υπολογισμούς χρόνων απόκρισης.

## 1.5.1 Χρήση CPU με την πάροδο του χρόνου

Figure 1.7: Χρήση CPU σε βάθος χρόνου με περίοδο 12s.

Figure 1.8: Χρήση CPU σε βάθος χρόνου με περίοδο 6s.

Όπως φαίνεται στα Σχήματα 1.7,1.8, η CPU παρουσιάζει περιοδικές κορυφές που ευθυγραμμίζονται με τους κύκλους RA. Η διάρκεια των κορυφών αυξάνεται με τον αριθμό των συσκευών, καθώς αυξάνεται ο αριθμός των αιτημάτων προς απάντηση και οι κατακερματισμοί της μνήμης. Κατά την διάρκεια του κατακερματισμού η χρήση είναι 100%.

### 1.5.2 Ανάλυση Κλιμάκωσης Αριθμού Συσκευών

Μετρήσεις συναρτήσει του αριθμού συσκευών που συμμετέχουν στο δίκτυο.

Figure 1.9: Μέση χρήση CPU vs αριθμός συσκευών.

Στο Σχήμα 1.9 γίνεται ξεκάθαρο πως η μέση χρήση του επεξεργαστή, από τις ρουτίνες της Απομακρυσμένης Επαλήθευσης, αυξάνεται σχεδόν γραμμικά και παρατηρείται κορεσμός σε περιπτώσεις πολλών συσκευών με υψηλή συχνότητα.

Figure 1.10: Μέγιστη χρήση RAM vs αριθμός συσκευών.

Όπως αναμένουμε η χρήση μνήμης (ολόχληρου του συστήματος) μένει περίπου σταθερή κατά την αύξηση του πληθυσμού, καθώς το μεγαλύτερο αποτύπωμα οφείλεται στις υπόλοιπες λειτουργίες του μικροϋπολογιστή.

Figure 1.11: Χρόνος απόκρισης μίας αίτησης RA vs αριθμός συσκευών.

Figure 1.12: Χρόνος ολοκλήρωσης κύκλου RA vs αριθμός συσκευών.

Οι χρόνοι απόκρισης αιτημάτων και χρόνοι ολοκλήρωσης γύρου επαληθεύσεων από κάθε συσκευή αυξάνονται κατά την προσθήκη συσκευών στο δίκτυο όπως φαίνεται στα Σχήματα 1.11, 1.12. Αυτό οφείλεται στο ότι η διασπορά μεταξύ των περιόδων των αιτημάτων από όλες τις συσκευές είναι μικρή, με αποτέλεσμα τα αιτήματα κατά μέσο όρο να συγχρονίζονται και να προκαλούν συμφόρηση στις συσκευές.

## 1.5.3 Ανάλυση Συχνότητας Γύρων Επαλήθευσης

Μετρήσεις συναρτήσει της μέσης περιόδου μεταξύ διαχριτών Γύρων Επαλήθευσης.

Figure 1.13: Μέση χρήση CPU vs περίοδος RA. Η CPU μειώνεται με αύξηση της περιόδου.

Το σχήμα 1.13 επιβεβαιώνει πως η μέση χρήση του επεξεργαστή για την επαλήθευση είναι αντιστρόφος ανάλογη της περιόδου, δηλαδή ανάλογη της συχνότητας των γύρων απομαχρυσμένης επαλήθευσης που εχτελούνται.

Figure 1.14: Μέγιστη χρήση RAM vs περίοδος RA. Το αποτύπωμα μνήμης παραμένει σχεδόν ανεπηρέαστο.

Από το σχήμα 1.14 επίσης επιβεβαιώνεται πως το αποτύπωμα μνήμης του πρωτοκόλου δεν επηρεάζεται από την περίοδο. Η αυξομειώσεις που παρατηρούνται οφείλονται στον τυχαίο ταυτοχρονισμό των διαφορετικών χρήσεων της σωρού, και σε σχέση με την συνολική κατανάλωση μνήμης είναι αμελητέα.

Figure 1.15: Ποσοστό χρονικών υπερβάσεων vs περίοδος RA. Μικρές περίοδοι αυξάνουν τις υπερβάσεις.

Το Σχήμα 1.15 φανερώνει αυτό που παρατηρήθηκε και στα προηγούμενα γραφήματα σε περιπτώσεις πολλών συσκευών και μικρής περιόδου. Ο συνοστισμός αιτημάτων σε αυτές τις καταστάσεις προκαλεί υπερβάσεις χρόνου (timeouts) με απποτέλεσμα το επαληθευτής να μην αποκτά γνώση της κατάστασης του αποδείκτη. Παρατηρούμε επιπροσθέτως πως για κάθε αριθμό συσκευών, υπάρχει μια οριακή τιμή της περιόδου, άνω της οποίας το σύστημα είναι σταθερό και λειτουργικό.

Figure 1.16: Χρόνος απόκρισης μίας αίτησης RA vs περίοδος. Σταθεροποιείται πάνω από κρίσιμη περίοδο.

Figure 1.17: Χρόνος ολοκλήρωσης κύκλου RA vs περίοδος. Σταθεροποιείται όταν η περίοδος ξεπερνά το κρίσιμο όριο.

Στα Σχήματα 1.16, 1.17 παρατηρούμε πως η ανταπόχριση των συσχευών, τόσο

ατομικά όσο και συλλογικά, είναι ανεξάρτητη της μέσης περιόδου, δεδομένου πως αυτή ξεπερνά την οριακή τιμή για σταθερότητα του συστήματος.

# 1.6 Συμπεράσματα και Μελλοντική Εργασία

### 1.6.1 Συμπεράσματα

Η παρούσα εργασία παρουσίασε ένα απλό και επεκτάσιμο Πλαίσιο Απομακρυσμένης Επαλήθευσης για συσκευές ΙοΤ, αξιοποιώντας την Προστασία Φυσικής Μνήμης του RISC-V ως υλική Ρίζα Εμπιστοσύνης. Το πλαίσιο συνδυάζει μηχανισμούς για προστασία από επαναλήψεις, εγγυήσεις φρεσκάδας με nonces και αποκεντρωμένη RA peer-to-peer, επιτρέποντας συλλογικό έλεγχο ακεραιότητας χωρίς μοναδικό σημείο εμπιστοσύνης.

Η υλοποίηση στην πλατφόρμα ESP32-C3 απέδειξε αξιόπιστη λειτουργία σε δίκτυα διαφορετικών μεγεθών και συχνότητες επαλήθευσης. Η αξιολόγηση έδειξε ότι η χρήση CPU είναι ο κυριότερος παράγοντας απόδοσης, ενώ η κατανάλωση μνήμης παραμένει σταθερή. Ο σωστός καθορισμός των διαστημάτων επαλήθευσης εξασφαλίζει προβλέψιμους χρόνους ολοκλήρωσης και χαμηλά ποσοστά χρονικών εξαιρέσεων. Συνολικά, το πλαίσιο γεφυρώνει το χάσμα μεταξύ θεωρητικών συλλογικών σχεδίων RA και πρακτικής υλοποίησης σε συσκευές ΙοΤ περιορισμένων πόρων της βιομηχανίας.

### 1.6.2 Μελλοντική Εργασία

Δυνατές επεκτάσεις για βελτίωση του Πλαισίου Απομακρυσμένης Επαλήθευσής μας περιλαμβάνουν:

- **Ρίζα Εμπιστοσύνης στο Υλικό:** Ενσωμάτωση secure boot και ασφαλούς αποθήκευσης κλειδιών, σε συνδυασμό με PMP για διαχωρισμό εργασιών στο FreeRTOS στην υλοποίηση [24].

- Εξυπνότερη Επαλήθευση: Ενσωμάτωση περιοδικού ελέγχου ακεραιότητας αντί ελέγχου μετά από κάθε εισερχόμενο αίτημα επαλήθευσης.

- Βελτιστοποίηση Απόδοσης: Μείωση χρήσης μνήμης και CPU μέσω εναλλακτικών αλγορίθμων κατακερματισμού και πιθανοτικών μετρήσεων ακεραιότητας.

- **Κρυπτογραφία:** Ολοκλήρωση υποστήριξης RSA για δημόσια επαλήθευση, παράλληλα με την υπάρχουσα υλοποίηση με ECC.

- **Αυτοΐαση:** Δυνατότητα ασφαλούς και αυτοματοποιημένης αποκατάστασης μολυσμένων συσκευών εμπνευσμένη από το HEALED [8].

- Κλιμάκωση: Υποστήριξη σχηματισμού αποδοτικότερων τοπολογιών (π.χ. δενρικών) για Συλλογική Απομακρυσμένη Επαλήθευση όπως το SEDA [4].

- Προστασία από DDoS: Αξιοποίηση challenge-response και φίλτρων για αντίσταση σε επιθέσεις υπερφόρτωσης.

Αυτές οι βελτιώσεις θα ενισχύσουν περαιτέρω την ανθεκτικότητα, την αποδοτικότητα και τη δυνατότητα υιοθέτησης συλλογικών πλαισίων RA σε μεγάλης κλίμακας δίκτυα

ΙοΤ περιορισμένων πόρων.

## Chapter 2

## Introduction

## 2.1 IoT

Humans have always used technology as a tool, to improve and optimize our society. Internet of Things is no different case than that. Internet of things (IoT) is a collection of many interconnected objects, services, humans, and devices that can communicate, share data, and information to achieve a common goal in different areas and applications. These devices are in essence tiny computers, embedded in our society and lives.

## 2.1.1 Applications of IoT

The recent emergence of low cost interconnected chips, sensors has allowed many industries to adopt IoT and improve their operations. Common examples are [11]:

Healthcare IoT devices are used for remote health monitoring, such as with heart beat and respiration sensors, fall detection for the elderly, accelerometers, and pedometers. Devices have even been used inside the body, with pill-sized devices to examine the digestive system, and the acquired data is then transmitted to other devices for processing, filtering, and visualization.

Smart Grids and Metering IoT plays a crucial role in the transition to a green grid, where renewables make the majority of energy sources. All sources have to be able to monitor their potential output power, communicate it to the grid administrators which meter all consumer and industry needs concurrently. Admins dispatch quotas of power output distributed sources have to meet, and all that in a matter of milliseconds, in order to keep the grid stable, with minimal voltage and frequency deviations, or in the case of failure, to bring parts of the grid back up to speed quickly [20].

**Home Automation** Most modern homes are equipped with interconnected AC, fridges, heating, dehumidifiers, lighting, EV chargers and of course a variety of humidity, brightness, temperature, and air composition sensors. These can all be organized into smart systems, to provide a comfortable home e.g. with

ambient lighting, constant humidity and temperature, and smart charging during cheap electricity hours. Even more, intrusion or smoke detectors connected to the internet can notify absent home owners in critical moments.

Automotive Industry A plethora of IoT is used in the cars of the 21st century, from temperature, acceleration, wear, oil level sensors to critical safety systems like the ABS, tranction control, the airbags and to the more optional and comfort features like climate control, seat heating, infotainment, navigation [22].

Smart Cities Modern cities can be equipped with trash and recycling bins that have weight sensors and notify the waste management authorities which have the information available to optimize waste retrieval only where and when it's needed, reducing the necessary man-hours and fuel of their trucks. At the same time smart traffic lights that can sense the number of cars in each intersection and any incoming buses or trams can optimize their schedule to prioritize public vehicles and optimize car flow. This can improve or even solve congestion, and, together with bus/trolley/tram GPS tracking and monitoring through the internet [6], they can drastically increase the quality of the public transportation resulting in reduced travel times for all!

## 2.1.2 The Challenge of Security

n recent years, the proliferation of Internet of Things (IoT) devices has increased dramatically due to their widespread availability, low cost, and diverse applications. However, this rapid growth introduces significant challenges, particularly in the domain of security. The responsibility of ensuring the security and integrity of these devices becomes critical as their numbers continue to escalate.

Experience in the field of computer engineering has consistently demonstrated that any computational system inherently possesses vulnerabilities. When such systems are network-connected, these vulnerabilities become considerably more exposed and accessible to malicious actors. The security of IoT devices is of particular concern given their massive scale of deployment. A single exploited vulnerability or compromised entry point has the potential to affect millions of devices simultaneously, leading to widespread disruption.

Hijacked IoT devices can pose a big threat, dependent on the industry the are applied in. Compromised health monitors pose a huge privacy concern for all patients while the can result in life or death situations for much of the elderly clientele of this industry. Furthermore, in the automotive industry attacks can lead to deadly accidents and rogue cars, while the same goes for the rest of the transportation sector; Smart traffic lights are credible attack vectors for adversaries to sabotage one's roads [15] while cyberattacks on rail, public transportation systems and airports are far and wide in the age of IoT (e.g. [21], [26]). A compromised electric grid is also a major strategic liability for any country as it can be a very useful asset in the hands of a rival state [5]. Finally a network of compromised IoT devices can be used as a botnet for DDoS attacks or to infect an even wider range of devices.

It is for this reason crucial to not only have rigorous standards and security best practices in the development of such IoT Solutions, but also greater mitigation strategies. Such a mitigation technique could be the detection of intrusion in IoT during their operation.

Such a method, of ensuring security and trust in networks of interconnected IoT devices is Remote Attestation. It enables a single verifier device, or multiple verifiers, to be sure at a given time that their peers, are not compromised and working as meant. Scale this to tens or thousands of devices and Collective Remote Attestation brings challenges of it's own, for efficient communication, aggregation, and propagation of this trust.

This thesis contributes to the field by designing and implementing a Collective Remote Attestation framework, performing mutual heterogenous self-verifying attestation in IoT networks without a central Verifier. It is designed to be accompanied by hardware guarantees through secure boot, secure storage and RISC-V PMP. The implementation targeted the ESP32-C3 microcontroller, in order for the framework to be easily adaptable to industry and serve a basis for future research in the field of Remote Attestation.

## Chapter 3

## Background

To understand the security challenges at the heart of this work, we must first establish a technical foundation. This chapter introduces the core technological domains involved: the specialized nature of embedded systems, the interconnected world of the Internet of Things (IoT), the fundamental cybersecurity principles that protect them, and the critical process of remote attestation.

## 3.1 Embedded Systems

An embedded system is a specialized computer—a combination of a processor, memory, and I/O peripherals—designed for a dedicated function within a larger electronic or mechanical system. Unlike a general-purpose PC, an embedded system performs predefined tasks, often with strict real-time computing requirements. These systems are ubiquitous, powering everything from consumer electronics like digital watches to industrial machinery and automotive systems.

## 3.1.1 Networking

Networking is crucial for modern embedded systems, enabling them to communicate with other devices and central servers. The choice of technology hinges on the application's requirements for range, bandwidth, and power consumption.

Wired Protocols For on-board communication, protocols like I2C (Inter-Integrated Circuit) and SPI (Serial Peripheral Interface) connect microcontrollers to peripherals [1]. In robust industrial and automotive applications, CAN (Controller Area Network) bus is prevalent due to its noise resistance.

Wireless Protocols The rise of IoT has spurred wireless adoption. Wi-Fi (IEEE 802.11) is used for high-bandwidth applications where power is readily available. For low-power, short-range communication, several protocols compete: Bluetooth and its low-energy variant, BLE, are standard for point-to-point connections in wearables and personal gadgets. For creating robust mesh networks, particularly in smart home automation, protocols like Zigbee, Z-Wave, and the IP-based Thread are common choices. In long-range, low-

power (LPWAN) scenarios, cellular technologies like **NB-IoT** and **LTE-M**, alongside protocols like **LoRaWAN**, allow battery-powered devices to send small amounts of data over several kilometers [7].

## 3.1.2 Real Time Operating Systems

A Real Time Operating System (RTOS) is an operating system intended to serve real-time applications that process data and events as they come in, typically without buffering delays. The key characteristic of an RTOS is not high speed, but determinism: the ability to process and respond to events within a predictable and guaranteed time frame. This is critical in systems where a delayed response could lead to a system failure, such as in an automobile's braking system or a medical device.

An RTOS manages the system's resources (CPU time, memory) through a scheduler. Common scheduling algorithms include pre-emptive scheduling, where a higher-priority task can interrupt a lower-priority one, ensuring that critical tasks are always executed first. When multiple equal-priority tasks have to be scheduled, the scheduler can allow any task to run uninterrupted, until it yields, which can lead to starvation. Alternatively it can adopt a round-robin approach, where every task is given a time slot to process in

Popular examples of RTOS include FreeRTOS, Zephyr, and VxWorks.

## 3.1.3 Internet of Things

As mentioned before, the Internet of Things (IoT) refers to the vast network of physical devices, vehicles, home appliances, and other items embedded with electronics, software, sensors, actuators, and connectivity which enables these objects to connect and exchange data. The goal of IoT is to create a seamless fabric of interconnected objects that can be monitored, controlled, and optimized remotely, leading to improvements in efficiency, accuracy, and economic benefit.

An IoT architecture is typically composed of four main layers [20]:

- Sensing Layer This consists of the "things" themselves—the physical devices with sensors and actuators that collect data from their environment (e.g., temperature, motion) or act upon it (e.g., turning on a light).

- **Network Layer** This layer is responsible for transmitting the data collected by the sensing layer to a central processing platform. It includes gateways and the communication protocols (e.g., Wi-Fi, LoRaWAN, cellular).

- **Data Processing Layer** This layer, often located in the cloud or on an edge server, is where the data is stored, processed, and analyzed.

- **Application Layer** This is the user-facing layer, where the processed data is presented in a meaningful way, such as through a dashboard, and where users can control the IoT devices.

## 3.1.4 RISC-V

RISC-V [17] is an open standard instruction set architecture based on the principles of reduced instruction set computing (RISC). Unlike proprietary ISAs like x86 or ARM, RISC-V is free and open-source, allowing researchers, companies, and hobbyists to design and implement processors without licensing fees. Its modular design enables a small, simple base ISA that can be extended with optional features such as integer multiplication, floating-point operations, or vector processing. Its openness has spurred innovation, transparency, and a rapidly growing ecosystem of hardware, software, and development tools.

RISC-V has become especially popular in IoT because of its flexibility, scalability, and cost-effectiveness. Manufacturers can customize the ISA to include only the instructions they need, minimizing power consumption and silicon area—critical factors for low-cost, battery-powered devices. Its open-source nature removes licensing costs, making it attractive for startups and small companies developing IoT solutions. Additionally, the growing ecosystem of RISC-V development boards, compilers, and operating system support (like FreeRTOS and Zephyr) makes it easier for engineers to adopt. As a result, RISC-V is increasingly being used in microcontrollers, smart sensors, and edge devices where efficiency, affordability, and security are top priorities.

## **Physical Memory Protection**

Physical Memory Protection (PMP) is a standard feature in RISC-V architecture designed for memory isolation in security-critical systems. In essence it consists a simple Memory Protection Unit (MPU) as it enables firmware to define specific physical memory regions and control the associated access permissions. PMP plays a crucial role in protecting memory for high-privilege binaries, such as firmware, and in trusted execution environments, where it isolates enclaves and manages shared memory regions. [19]

Figure 3.1: PMP Configuration Example [19]

PMP is configured using per-hardware-thread machine-mode control registers, with each core potentially having up to 16 PMP registers. Each PMP entry comprises a configuration register (pmpcfg) and an address register (pmpaddr). The

pmpcfg register specifies the addressing mode and permission bits (read, write, execute), while the pmpaddr defines the address range using one of three addressing modes: 4-byte aligned word (NA4), naturally-aligned power-of-two (NAPOT), or top-of-range (TOR). PMP entries operate as a whitelist, meaning memory is inaccessible by default unless explicitly defined by an entry. Entries are statically prioritized, where the lowest-numbered entry that matches a memory access (including the privilege mode) dictates whether the access succeeds or fails. The PMPChecker, a core hardware module, implements these rules, taking the memory address, access size, PMP register states (including lock bits and permissions), and the current privilege mode as inputs to determine the access permissions. Exceptions include denying permissions for partial matches within a region and granting default full access for high privilege modes or no access for low privilege modes when an address is not covered by any PMP region [19].

Analogous technologies in rival architectures are TDX/AMD SEV for x86 and TrustZone for Arm, which are richer in capabilities, able to provide TEEs but more costly. PMP provides a simpler solution that them, for systems without a Memory Management Unit (MMU).

## 3.2 Cryptography

Cryptography provides the essential tools to achieve confidentiality, integrity, and authenticity in communications and data storage.

## 3.2.1 Hashing

A cryptographic hash function is an algorithm that takes an input of arbitrary size (e.g., a file, a message) and produces a fixed-size string of characters, which is called a hash value or digest. A key property of these functions is that they are one-way; it is computationally infeasible to reverse the process and derive the original input from its hash. They are also designed to be collision-resistant, meaning it is extremely difficult to find two different inputs that produce the same hash value. Common hashing algorithms include SHA-256 (Secure Hash Algorithm 256-bit) and SHA-3.

SHA-256 first pads the input to a multiple of 512 bits by appending a '1' bit, followed by enough '0' bits, and then the 64-bit message length; it then processes the message in 512-bit blocks using the Merkle–Damgård construction, chaining a compression function to produce the final 256-bit hash. Each block is combined with the hash of the previous block, ensuring that the output depends on the entire message.

Hashing is widely used to verify data integrity; if the hash of a received file matches the hash computed by the sender, the receiver can be confident the file was not altered in transit.

## 3.2.2 Asymmetric Cryptography

Also known as public key cryptography, this system uses pairs of keys: a public key  $K_{\text{pub}}$ , which may be disseminated widely, and a private key  $K_{\text{priv}}$ , which is known only to the owner. The two keys are mathematically linked.

If the public key is used to encrypt data, only the corresponding private key can decrypt it. Formally, if M is a message:

$$C = E_{K_{\text{pub}}}(M)$$

where E is the encryption function and C is the ciphertext. Decryption is then performed using the private key:

$$M = D_{K_{\text{priv}}}(C)$$

where D is the decryption function. This process provides **confidentiality**.

Conversely, a message can be "signed" using the private key to create a digital signature:

$$S = \operatorname{Sign}_{K_{\text{priv}}}(M)$$

Anyone with the public key can then verify this signature:

$$\operatorname{Verify}_{K_{\operatorname{pub}}}(M,S) \Rightarrow \operatorname{True}$$

This confirms both the authenticity of the sender and the integrity of the message.

Prominent algorithms include RSA (Rivest-Shamir-Adleman) and Elliptic Curve Cryptography (ECC).

## 3.2.3 Message Authentication

Message authentication is the process of verifying that a received message comes from the alleged source and has not been altered. While digital signatures (using asymmetric cryptography) provide this, a more lightweight method is a Message Authentication Code (MAC). A MAC is generated using a symmetric key (a single key shared between the sender and receiver) and the message content. The sender computes the MAC and sends it along with the message. The receiver performs the same computation on the received message using the shared key and compares their result to the received MAC. If they match, the message is authenticated.

A common implementation is HMAC (Hash-based Message Authentication Code), which enhances the security of basic MACs by combining a secret key with a cryptographic hash function in a carefully structured way that resists common attacks. It works by hashing the message together with the key twice; once with an "inner"

key and once with an "outer" key, providing strong integrity guarantees even if the underlying hash function has some weaknesses. Formally, HMAC is defined as

$$\mathrm{HMAC}_K(M) = H((K \oplus \mathrm{opad}) \parallel H((K \oplus \mathrm{ipad}) \parallel M))$$

where H is the cryptographic hash function, K is the secret key (padded to the block size), M is the message, and opad and ipad are fixed outer and inner padding constants. This double application of the hash function ensures that even if part of the message is modified, the computed HMAC will no longer match, providing message authentication.

## 3.3 Trust

In cybersecurity, trust is not an assumption but a property that must be established through verifiable mechanisms. It is the foundation upon which secure operations are built.

## 3.3.1 Root of Trust

The Root of Trust (RoT) is a component or set of components within a system that is inherently trusted and cannot be compromised. All other secure operations depend on it. An RoT is typically implemented in hardware to make it immutable. For example, a hardware module containing an unchangeable cryptographic key can serve as an RoT. All subsequent software and operations rely on this initial anchor of trust. Building upon the RoT, a Chain of Trust (CoT) is a sequential process that verifies the integrity of a system's components, one after another.

#### Secure Boot

A typical Chain of Trust for computers can be described by the Secure Boot process. It describes the method through which a single computer can boot securely and verifiably the correct software stack. The process starts with the RoT, which is some type of ROM with boot code, which is guaranteed the first piece of machine code that is run during boot, and an immutable public key of the computer's vendor. These two guarantees are set in hardware and thus trusted. The ROM code (e.g. 1st boot stage) verifies the integrity of the next component in the boot sequence, by taking its hash and verifying the vendor's signature of that hash. If the bootloader is valid, execution is handed over to it and it is itself trusted to verify the next component (e.g. the operating system kernel), and so on. This ensures that every piece of software loaded onto the system has been authenticated and is in a known, trusted state. If any link in the chain is broken (i.e., a component's integrity check fails), the boot process can be halted to prevent the execution of compromised code.

#### 3.3.2 Remote Attestation

Remote Attestation (RA) is an effective solution to detect software compromises on remote devices. RA schemes allow a verifier to assess the integrity of the code and configuration of a remote prover. In a typical RA protocol the prover, upon request delivers a proof of its configuration to the verifier who compares it against an a priori defined set of correct configurations [9]. It is essentially a method of building out the Chain of Trust across a network of devices, and ensure their integrity.

This section will elaborate on the mechanics of this process, including hash acquisition, delivery, authenticity, alternative verification models and the foundational Root of Trust in such systems.

## **Acquisition of Configuration Hash**