# **Current-limiting methods for grid-forming inverters and their effect on transient stability**

## **DIPLOMA THESIS**

## **ANTONIS MAKRIGIORGIS**

**Supervisor**: Antonios Antonopoulos Associate Professor, NTUA

# **Current-limiting methods for grid-forming inverters and their effect on transient stability**

### **DIPLOMA THESIS**

## **ANTONIS MAKRIGIORGIS**

**Supervisor**: Antonios Antonopoulos Associate Professor, NTUA

Approved by the three-member scientific committee on the 19th of September 2025.

Antonios Antonopoulos Vasileios Nikolaidis Constantinos Vo

Associate Professor, NTUA

Vasileios Nikolaidis Assistant Professor, NTUA Constantinos Vournas Professor Emeritus, NTUA

Graduate of School of Electrical and Computer Engineering, National Technical University of Athens

Copyright © Antonis Makrigiorgis, 2025 All rights reserved.

You may not copy, reproduce, distribute, publish, display, modify, create derivative works, transmit, or in any way exploit this thesis or part of it for commercial purposes. You may reproduce, store or distribute this thesis for non-profit educational or research purposes, provided that the source is cited, and the present copyright notice is retained. Inquiries for commercial use should be addressed to the original author.

The ideas and conclusions presented in this paper are the author's and do not necessarily reflect the official views of the National Technical University of Athens.

# Περίληψη

Η μετάβαση του συστήματος ηλεκτρικής ενέργειας από ένα σύστημα που κυριαρχείται από σύγχρονες μηχανές σε ένα σύστημα που κυριαρχείται από μετατροπείς ηλεκτρονικών ισχύος, έχει επιφέρει σημαντικές τεχνικές και λειτουργικές προκλήσεις. Οι αντιστροφείς διαμόρφωσης δικτύου θεωρούνται μια υποσχόμενη λύση για την ενίσχυση της ευστάθειας των μελλοντικών συστημάτων ηλεκτρικής ενέργειας και για την διευκόλυνση της ενσωμάτωσης των μετατροπέων ηλεκτρονικών ισχύος στο δίκτυο, σε μεγάλη κλίμακα. Σε αντίθεση με τις σύγχρονες γεννήτριες, οι αντιστροφείς διαμόρφωσης δικτύου έχουν περιορισμένη αντοχή σε υπερένταση. Επομένως, οι μέθοδοι περιορισμού του ρεύματος είναι απαραίτητες για την προστασία των στοιχείων του μετατροπέα. Ο σκοπός της παρούσας διπλωματικής εργασίας είναι η κατανόηση των μεθόδων που χρησιμοποιούνται για τον περιορισμό του ρεύματος των αντιστροφέων διαμόρφωσης δικτύου σε διαταραχές, καθώς και η μελέτη της επίδρασης των μεθόδων αυτών στην μεταβατική ευστάθεια.

Αρχικά, παρουσιάζεται μια εκτενής ανασκόπηση των συχνά χρησιμοποιούμενων μεθόδων ελέγχου διαμόρφωσης δικτύου και περιορισμού ρεύματος, η οποία ακολουθείται από την υλοποίηση αρκετών από αυτές τις μεθόδους στο λογισμικό προσομοίωσης PLECS. Στην συνέχεια, πραγματοποιούνται προσομοιώσεις για την επιβεβαίωση της αποτελεσματικής λειτουργίας των υλοποιημένων μεθόδων περιορισμού ρεύματος σε διάφορα σφάλματα, καθώς και για την ανάδειξη διαφορών στην απόκριση τους.

Έπειτα, μελετάται η μεταβατική ευστάθεια των αντιστροφέων διαμόρφωσης δικτύου μέσω καμπυλών ισχύος-γωνίας, οι οποίες προκύπτουν από τα μοντέλα μεγάλου σήματος των χρησιμοποιούμενων μεθόδων περιορισμού ρεύματος. Παρουσιάζεται η θεωρητική πορεία ισχύος-γωνίας για βραχυκυκλώματα και αναλύεται η επίδραση του περιορισμού ρεύματος στην μεταβατική ευστάθεια. Τα μοντέλα μεγάλου σήματος και η θεωρητική ανάλυση επιβεβαιώνονται μέσω προσομοιώσεων.

Τέλος, πραγματοποιούνται προσομοιώσεις πραγματικού χρόνου για την αξιολόγηση της απόδοσης των υλοποιημένων μεθόδων περιορισμού ρεύματος, υπό συνθήκες πραγματικού χρόνου. Τα συστήματα ελέγχου υλοποιούνται σε έναν μικροελεγκτή, ο οποίος αλληλεπιδρά με το υπόλοιπο προσομοιωμένο σύστημα. Τα αποτελέσματα των προσομοιώσεων πραγματικού χρόνου δείχνουν ότι οι υλοποιημένες τεχνικές περιορισμού ρεύματος μπορούν να περιορίσουν αποτελεσματικά το ρεύμα για διαφορετικούς τύπους διαταραχών, υπό συνθήκες πραγματικού χρόνου.

**Λέξεις κλειδιά**: Αντιστροφείς διαμόρφωσης δικτύου, Μέθοδοι περιορισμού ρεύματος, Ελεγκτής στατισμού, Αδρανειακή συμπεριφορά, Μεταβατική ευστάθεια, Προσομοίωση πραγματικού χρόνου

## **Abstract**

The ongoing transformation of the power system from synchronous machine dominated to power electronic converter dominated, poses major technical and operational challenges. Grid-forming inverters are considered as a promising solution to enhance the stability of future power grids and facilitate the large-scale integration of power electronic converters into the grid. Unlike synchronous generators, the overcurrent capability of grid-forming inverters is limited. Therefore, overcurrent limiting methods are essential to prevent hardware damage of the converter. To that end, the main objective of this thesis is to understand the methods that are used to limit the current of grid-forming inverters during off-nominal conditions and to assess the effect of these methods on the transient stability.

First, a comprehensive review of common grid-forming and current-limiting control methods is presented, followed by the implementation of several of these methods in the PLECS simulation software. Then, time-domain simulations are carried out to validate the effectiveness of the implemented current-limiting methods under various types of disturbances and to highlight differences in their responses.

Next, the transient stability of grid-forming inverters is studied, through power-angle characteristics derived from the large-signal models of the employed current-limiting methods. The theoretical power-angle trajectory for short circuits is presented and the effect of current limitation on the transient stability margin is illustrated. The large-signal models and the theoretical analysis are validated through time-domain simulations.

Finally, hardware-in-the-loop real-time simulations are performed to assess the performance of the implemented current-limiting methods, under real-time conditions. The control systems are implemented on a microcontroller, which interacts with the rest of the simulated system. The results of the real-time simulations indicate that the implemented current-limiting techniques can effectively restrict the current for different types of disturbances, under real-time conditions.

**Keywords**: Grid-forming inverters, Current-limiting methods, Droop control, Inertial effect, Transient stability, Real-time simulation

## **Acknowledgments**

First and foremost, I am sincerely grateful to my supervisor, Prof. Antonios Antonopoulos, for his trust, guidance and invaluable advice on both technical and non-technical questions. His continuous encouragement and effective cooperation played a crucial role in the completion of this thesis.

I would also like to thank Mustafa Ibrahim and Marcio Magalhães de Oliveira for the technical discussions and for giving me the opportunity to visit the Section of System Studies, HVDC & FACTS of AFRY, in Sweden.

Moreover, I would like to thank my lab-mates Alkis and Christos, for creating a pleasant atmosphere in the lab and for the countless coffees we had throughout this thesis.

Last but not least, I would like to sincerely thank Iro for her continuous support, encouragement and patience throughout this work.

# **Contents**

| Па | ερίλην         | ψη      |                                                                   | 5  |  |  |

|----|----------------|---------|-------------------------------------------------------------------|----|--|--|

| Al | Abstract       |         |                                                                   |    |  |  |

| A  | know           | ledgme  | ents                                                              | 9  |  |  |

| E  | <b>ιτετα</b> ן | μένη Ελ | ληνική Περίληψη                                                   | 13 |  |  |

| 1  | Intr           | oductio | n                                                                 | 22 |  |  |

|    | 1.1            | Transf  | Formation of the power system                                     | 22 |  |  |

|    | 1.2            | Inverte | er Based Resources                                                | 23 |  |  |

|    | 1.3            | Overci  | urrent limiting for grid-forming inverters                        | 26 |  |  |

|    |                | 1.3.1   | The need for current-limiting methods for grid-forming inverters  | 26 |  |  |

|    |                | 1.3.2   | Challenges of current-limiting methods for grid-forming inverters | 27 |  |  |

|    | 1.4            | Object  | ive and structure of this thesis                                  | 28 |  |  |

|    |                | 1.4.1   | Objective and scope of this thesis                                | 28 |  |  |

|    |                | 1.4.2   | Structure of this thesis                                          | 29 |  |  |

| 2  | Grid           | l-formi | ng inverters and current- limiting methods                        | 30 |  |  |

|    | 2.1            | Grid-f  | orming control methods                                            | 30 |  |  |

|    |                | 2.1.1   | General control structure of grid-forming inverters               | 30 |  |  |

|    |                | 2.1.2   | Outer control loops                                               | 32 |  |  |

|    |                | 2.1.3   | Inner control loops                                               | 35 |  |  |

|    | 2.2            | Currer  | nt-limiting control methods for grid-forming inverters            | 38 |  |  |

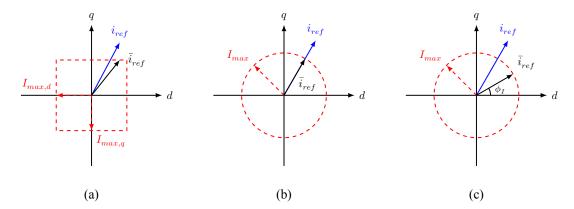

|    |                | 2.2.1   | Direct current-limiting methods                                   | 40 |  |  |

|    |                | 2.2.2   | Indirect current-limiting methods                                 | 43 |  |  |

|    |                | 2.2.3   | Hybrid current-limiting methods                                   | 48 |  |  |

|    | 2.3            | Impler  | mentation of grid-forming and current-limiting control methods    | 48 |  |  |

|    |                | 2.3.1   | Description of the studied system                                 | 48 |  |  |

|    |                | 2.3.2   | Implementation of outer loops                                     | 51 |  |  |

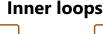

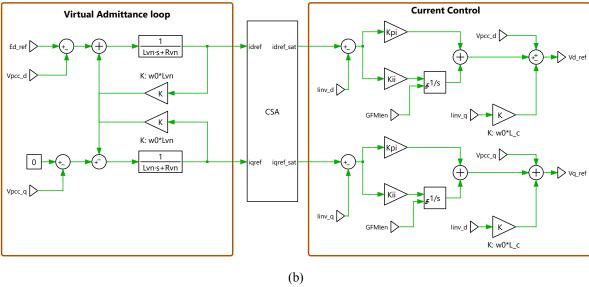

|    |                | 2.3.3   | Implementation of inner loops                                     | 51 |  |  |

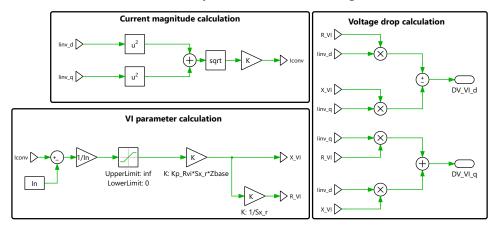

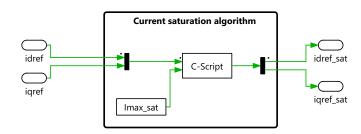

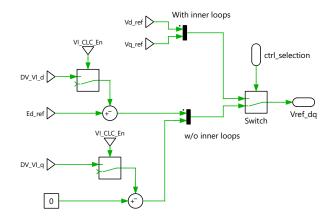

|    |                | 2.3.4   | Implementation of current-limiting control methods                | 52 |  |  |

|    | 2.4            | Simula  | ation results                                                     | 55 |  |  |

|    |                | 2.4.1   | Grid-forming control methods                                      | 56 |  |  |

|    |                | 2.4.2   | Current-limiting control methods                                  | 58 |  |  |

| 3  | Effe           |         | rrent-limiting methods on transient stability                     | 64 |  |  |

|    | 3.1            | Studie  | d system and assumptions                                          | 64 |  |  |

|    | 3.2            | Theore  | etical analysis                                                   | 65 |  |  |

|    |        | 3.2.1    | Non-inertial control                                | 65 |

|----|--------|----------|-----------------------------------------------------|----|

|    |        | 3.2.2    | Inertial control                                    | 67 |

|    |        | 3.2.3    | Fixed angle limiter                                 | 68 |

|    |        | 3.2.4    | Magnitude limiter                                   | 70 |

|    |        | 3.2.5    | Calculation of the critical clearing time           | 72 |

|    | 3.3    | Validat  | tion of the large-signal models through simulations | 75 |

|    |        | 3.3.1    | Non-inertial control                                | 75 |

|    |        | 3.3.2    | Inertial control                                    | 80 |

| 4  | Har    | dware-i  | n-the-loop real-time simulation                     | 83 |

|    | 4.1    | Brief in | ntroduction on Real-Time Simulations                | 83 |

|    | 4.2    | Config   | uration of the real-time simulation                 | 84 |

|    |        | 4.2.1    | RT Box                                              | 85 |

|    |        | 4.2.2    | TI C2000 LAUNCHXL-F28379D microcontroller           | 86 |

|    |        | 4.2.3    | RT Box launchpad interface                          | 86 |

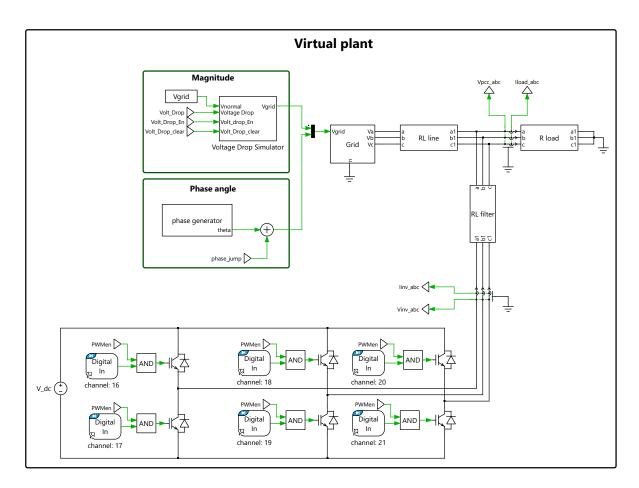

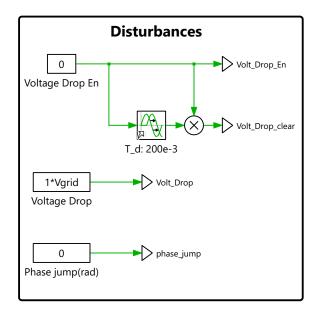

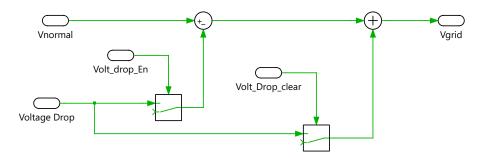

|    | 4.3    | Virtual  | plant model in RT Box                               | 87 |

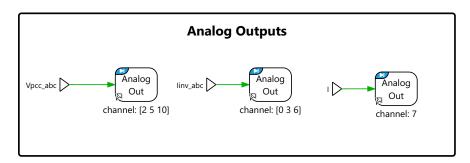

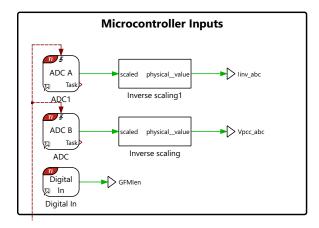

|    | 4.4    | Contro   | ller implementation                                 | 90 |

|    | 4.5    | Real-ti  | me simulation results                               | 92 |

| 5  | Con    | clusions | and Future Work                                     | 96 |

|    | 5.1    | Conclu   | isions                                              | 96 |

|    | 5.2    | Future   | work                                                | 97 |

| Bi | bliogi | raphy    |                                                     | 98 |

## Εκτεταμένη Ελληνική Περίληψη

## Κεφάλαιο 1. Εισαγωγή

Τα παραδοσιακά συστήματα ηλεκτρικής ενέργειας (ΣΗΕ) υφίστανται πολύ μεγάλες αλλαγές, λόγω της ανάγκης αντιμετώπισης της υπερθέρμανσης του πλανήτη. Παρατηρείται μια στροφή προς πιο καθαρές μορφές παραγωγής ηλεκτρικής ενέργειας, η οποία οδηγεί στην σταδιακή αντικατάσταση των μεγάλων κεντρικών θερμικών σταθμών παραγωγής με μικρότερης κλίμακας Ανανεώσιμες Πηγές Ενέργειας (ΑΠΕ), όπως ηλιακή και αιολική ενέργεια.

Στα παραδοσιακά ΣΗΕ κυριαρχούσαν οι σύγχρονες γεννήτριες, οι οποίες αναλάμβαναν την ρύθμιση τάσης και συχνότητας. Οι σύγχρονες γεννήτριες συμπεριφέρονται ως πηγές τάσης και έχουν μεγάλη αδράνεια δρομέα. Αυτά τα χαρακτηριστικά είναι αναγκαία για την ευσταθή λειτουργία του ΣΗΕ. Αντίθετα, οι πλειονότητα των ΑΠΕ συνδέονται στο δίκτυο μέσω αντιστροφέων ηλεκτρονικών ισχύος (inverters) και επομένως αναφέρονται με τον όρο "Inverter-Based Resources" (IBRs). Οι αντιστροφείς έχουν μεγάλες διαφορές σε σχέση με τις σύγχρονες γεννήτριες, όχι μόνο ως προς τα τεχνικά τους χαρακτηριστικά, αλλά και στον τρόπο που ανταποκρίνονται σε διαταραχές στο δίκτυο. Σε αντίθεση με τις σύγχρονες γεννήτριες, η λειτουργία των αντιστροφέων καθορίζεται κυρίως από το σύστημα ελέγχου τους. Επομένως, η μετάβαση από ένα ΣΗΕ που κυριαρχείται από σύγχρονες γεννήτριες σε ένα ΣΗΕ που κυριαρχείται από ΙΒRs, έχει φέρει πολλές προκλήσεις, οι οποίες πρέπει να αντιμετωπιστούν για να εξασφαλιστεί η ευστάθεια των μελλοντικών ΣΗΕ.

Οι αντιστροφείς που συνδέονται στο δίκτυο χωρίζονται σε δύο βασικές κατηγορίες, ανάλογα με το σύστημα ελέγχου τους. Οι δύο κατηγορίες είναι οι αντιστροφείς ακολούθησης δικτύου (grid-following inverters) και οι αντιστροφείς διαμόρφωσης δικτύου (grid-forming inverters). Παρόλο που οι grid forming (GFM) και grid following (GFL) αντιστροφείς έχουν παρόμοια τεχνικά χαρακτηριστικά (hardware) και κοινό στόχο την ανταλλαγή ενεργού και άεργου ισχύος με το δίκτυο, διαφέρουν σημαντικά στα συστήματα ελέγχου, στην μοντελοποίηση τους και στην απόκρισή τους σε διαταραχές στο δίκτυο.

Οι GFLIs, οι οποίοι αποτελούν την πλειονότητα των αντιστροφέων συνδεδεμένων στο δίκτυο, συγχρονίζονται με την τάση του δικτύου μέσω μιας μονάδας συγχρονισμού (π.χ PLL) και ανταλλάζουν ενεργό και άεργο ισχύ με το δίκτυο ελέγχοντας τις κατάλληλες συνιστώσες ρεύματος. Λόγω αυτής της τεχνικής ελέγχου, οι GFLIs συμπεριφέρονται ως πηγές ρεύματος. Ένα ΣΗΕ που κυριαρχείται από αντιστροφείς δεν μπορεί να λειτουργήσει χρησιμοποιώντας μόνο GFLIs, αφού χρειάζονται μια καλά ορισμένη τάση προκειμένου να συγχρονιστούν με το δίκτυο. Από την άλλη, οι GFMIs ελέγχονται με τέτοιο τρόπο ώστε να συμπεριφέρονται ως πηγές τάσης, με αποτέλεσμα να αποκρίνονται σε διαταραχές στο δίκτυο, παρόμοια με τις σύγχρονες γεννήτριες. Επομένως, οι GFMIs θεωρούνται μια πολύ υποσχόμενη λύση για την ενίσχυση της ευστάθειας των μελλοντικών ΣΗΕ.

Λόγω της συμπεριφοράς των GFMI ως πηγές τάσης, η στιγμιαία αντίδραση τους σε διαταραχές του δικτύου είναι να κρατήσουν την εσωτερική τους τάση σταθερή. Αυτό έχει ως

αποτέλεσμα την στιγμιαία αλλαγή του ρεύματος εξόδου τους. Παρότι η απόκριση αυτή είναι επιθυμητή, είναι προφανές ότι το ρεύμα του αντιστροφέα είναι πολύ ευαίσθητο στις συνθήκες του δικτύου, καθώς δεν ελέγχεται άμεσα. Επομένως, όταν η διαταραχή στο δίκτυο είναι επαρκώς μεγάλη (π.χ ένα τριφασικό βραχυκύκλωμα), αν δεν ληφθούν μέτρα, το ρεύμα θα υπερβεί το ονομαστικό επίπεδο. Αντίθετα με τις σύγχρονες μηχανές, οι οποίες μπορούν να αντέξουν ρεύματα αρκετές φορές μεγαλύτερα από το ονομαστικό για κάποιο χρονικό διάστημα, οι αντιστροφείς έχουν πολύ μικρές αντοχές σε υπερεντάσεις. Συνεπώς, προκειμένου οι GFMI να παραμένουν συνδεδεμένοι και να υποστηρίζουν το δίκτυο σε τέτοιες διαταραχές, πρέπει να υλοποιηθούν τεχνικές περιορισμού του ρεύματος τους.

Τα τελευταία χρόνια έχουν αναπτυχθεί πολλές μέθοδοι περιορισμού του ρεύματος των GFMI. Όταν ενεργοποιείται ο περιοριστής ρεύματος λόγω κάποιας διαταραχής, ο αντιστροφέας δεν μπορεί να κρατήσει σταθερή την εσωτερική του τάση. Συνεπώς, η δυναμική συμπεριφορά του αντιστροφέα κατά και μετά το σφάλμα καθορίζεται κυρίως από την τεχνική περιορισμού ρεύματος που χρησιμοποιεί. Ως αποτέλεσμα, παρόλο που ο βασικός στόχος των μεθόδων αυτών είναι η προστασία των στοιχείων του αντιστροφέα, επηρεάζουν παράλληλα και ζητήματα που αφορούν το ΣΗΕ, όπως η μεταβατική ευστάθεια, ο συντονισμός των προστασιών κλπ. Για τον λόγο αυτό, μια μέθοδος περιορισμού ρεύματος πρέπει να τηρεί κάποια κριτήρια που αφορούν τον ίδιο τον αντιστροφέα, αλλά και το ΣΗΕ.

# Κεφάλαιο 2. Αντιστροφείς διαμόρφωσης δικτύου και μέθοδοι περιορισμού ρεύματος

### Αντιστροφείς διαμόρφωσης δικτύου

Η πλειονότητα των grid forming μεθόδων ελέγχου μπορεί να περιγραφεί από ένα γενικό σύστημα ελέγχου. Οι είσοδοι του συστήματος είναι οι μετρήσεις για τα τριφασικά ρεύματα και τις τάσεις και οι τιμές αναφοράς για την ενεργό/άεργο ισχύ, την συχνότητα και το μέτρο της τάσης, ενώ η έξοδος είναι η αναφορά τάσης που τροφοδοτείται για την διαμόρφωση του αντιστροφέα. Το γενικό σύστημα ενός GFMI αποτελείται από διάφορα υποσυστήματα και επίπεδα, τα οποία είναι υπεύθυνα για διαφορετικές λειτουργίες. Για παράδειγμα το εξωτερικό επίπεδο ελέγχου παράγει τα χαρακτηριστικά της αναφοράς πηγής τάσης (μέτρο και γωνία), ενώ ο σκοπός του εσωτερικού επιπέδου είναι η ακολούθηση της αναφοράς αυτής.

Το εξωτερικό επίπεδο περιλαμβάνει τον ελεγκτή ενεργού ισχύος (ή βρόχος συγχρονισμού) και τον ελεγκτή άεργου ισχύος (ή βρόχος διαχείρισης του προφίλ τάσης), οι οποίοι είναι υπεύθυνοι για τον συγχρονισμό του αντιστροφέα με το δίκτυο και τη ρύθμιση τάσης αντίστοιχα. Συγκεκριμένα, ο ελεγκτής ενεργού ισχύος ρυθμίζει την ενεργό ισχύ και παρέχει στην έξοδό του την γωνία/συχνότητα της εσωτερικής τάσης του αντιστροφέα. Από την άλλη, ο βρόχος διαχείρισης του προφίλ τάσης συνδέεται με την άεργο ισχύ, και παρέχει το μέτρο της εσωτερικής τάσης του αντιστροφέα. Το εσωτερικό επίπεδο μπορεί να περιέχει επιπρόσθετους ελεγκτές τάσης και ρεύματος, ή μπορεί να παραληφθεί αφού η έξοδος του εξωτερικού επιπέδου είναι επαρκής για την υλοποίηση της συμπεριφοράς πηγής τάσης.

Υπάρχουν πολλές υλοποιήσεις για κάθε υποσύστημα του γενικού συστήματος ελέγχου και ο συνδυασμός τους οδηγεί σε αρκετές grid forming μεθόδους ελέγχου, οι οποίες διαφέρουν στην υλοποίηση του κάθε υποσυστήματος. Για παράδειγμα, κάποιες μέθοδοι ελέγχου που χρησιμοποιούνται συχνά για τον ελεγκτή ενεργού ισχύος είναι ο ελεγκτής στατισμού χωρίς και με βαθυπερατό φίλτρο και η μέθοδος Εικονικής Σύγχρονης Γεννήτριας. Μάλιστα, οι δύο τελευταίες είναι ισοδύναμες μεταξύ τους. Για τον βρόχο διαχείρισης του προφίλ τάσης μπορεί παρόμοια να χρησιμοποιθεί ελεγκτής στατισμού χωρίς και με βαθυπερατό φίλτρο, καθώς και ΡΙ ελεγκτές για το μέτρο της τάσης και για την άεργο ισχύ. Το εσωτερικό επίπεδο (αν

χρησιμοποιηθεί) μπορεί να αποτελείται από ένα ή δυο βρόχους ελέγχου. Για παράδειγμα μια υλοποίηση με έναν βρόχο, ελέγχει το μέτρο της τάσης. Μια πολύ συχνά χρησιμοποιούμενη υλοποίηση με δύο βρόχους περιλαμβάνει έναν ελεγκτή τάσης και έναν ελεγκτή ρεύματος, ενώ μια παρόμοια υλοποίηση αποτελείται από έναν βρόχο εικονικής αγωγιμότητας και έναν ελεγκτή ρεύματος.

## Μέθοδοι περιορισμού ρεύματος

Για την προστασία των GFMI σε περίπτωση σφαλμάτων, έχουν προταθεί στη βιβλιογραφία διάφορες μέθοδοι περιορισμού ρεύματος, οι οποίες μπορούν να ταξινομηθούν σε άμεσες, έμμεσες ή υβριδικές, ανάλογα με τον τρόπο με τον οποίο επιτυγχάνουν τον περιορισμό του ρεύματος. Συγκεκριμένα, οι άμεσες μέθοδοι περιορίζουν το ρεύμα προσαρμόζοντας κατάλληλα τις τιμές αναφοράς που παρέχονται στον ελεγκτή ρεύματος. Από την άλλη, οι έμμεσες μέθοδοι επιχειρούν να περιορίσουν το ρεύμα μειώνοντας το μέτρο της διαφοράς μεταξύ της εσωτερικής τάσης του αντιστροφέα και της τάσης στο σημείο σύνδεσης του, ή προσαρμόζοντας τις αναφορές ενεργού και άεργου ισχύος, ή αυξάνοντας την ισοδύναμη εμπέδηση εξόδου του αντιστροφέα. Οι υβριδικές μέθοδοι χρησιμοποιούν ένα συνδυασμό άμεσων ή/και έμμεσων τεχνικών περιορισμού ρεύματος.

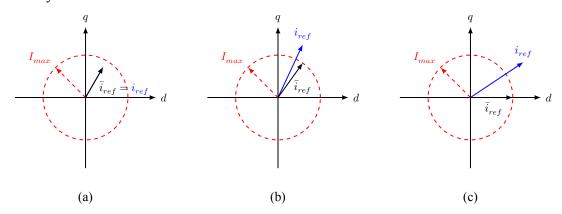

Οι άμεσες μέθοδοι διαφέρουν μεταξύ τους στον τρόπο με τον οποίο προσαρμόζουν τις αναφορές του ρεύματος. Για παράδειγμα ο περιοριστής μέτρου περιορίζει μόνο το μέτρο της αναφοράς του ρεύματος, χωρίς να αλλάζει τη γωνία του, ενώ ο περιοριστής σε δεδομένη γωνία περιορίζει το μέτρο και θέτει τη γωνία σε μια προκαθορισμένη τιμή. Επίσης υπάρχουν οι μέθοδοι που περιορίζουν το μέτρο του ρεύματος, δίνοντας προτεραιότητα σε κάποια συνιστώσα του (π.χ συνιστώσα d- ή q-άξονα).

Όσον αφορά τις έμμεσες μεθόδους, οι πιο συνηθισμένες είναι οι μέθοδοι εικονικής εμπέδησης (virtual impedance), οι οποίες μεταβάλλουν την αναφορά της τάσης περνώντας το μετρούμενο ρεύμα μέσω μιας εικονικής εμπέδησης και αφαιρώντας όρους που αντιστοιχούν στην πτώση τάσης πάνω στην εμπέδηση αυτή. Επομένως, αυτές οι τεχνικές επιτυγχάνουν τον περιορισμό του ρεύματος αυξάνοντας την ισοδύναμη εμπέδηση εξόδου του αντιστροφέα.

#### Υλοποίηση μεθόδων και προσομοιώσεις

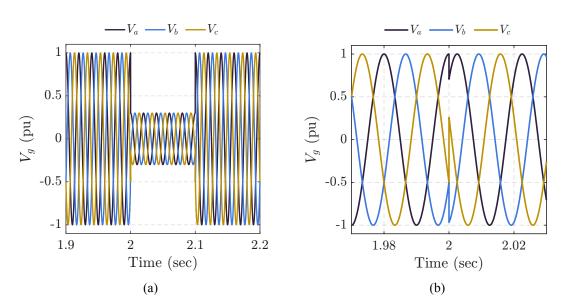

Για την επιβεβαίωση της λειτουργίας των τεχνικών περιορισμού ρεύματος, υλοποιήθηκαν διάφορες μέθοδοι στο πρόγραμμα προσομοίωσης PLECS και πραγματοποιήθηκαν προσομοιώσεις βύθισης τάσης και απότομης αλλαγής της φάσης της τάσης του δικτύου. Το σύστημα που προσομοιώθηκε αποτελείται από έναν GFM αντιστροφέα που συνδέεται στο δίκτυο μέσω ενός επαγωγικού φίλτρου και μιας γραμμής μεταφοράς. Το δίκτυο αναπαρίσταται από μια άπειρη τριφασική πηγή τάσης, ενώ ο αντιστροφέας μοντελοποιείται με το μοντέλο μέσης τιμής. Οι διαταραχές προσομοιώνονται μεταβάλλοντας την τάση του δικτύου.

Αναφορικά με το σύστημα ελέγχου του αντιστροφέα, για τον ελεγκτή ενεργού ισχύος υλοποιήθηκε ο ελεγκτής στατισμού με και χωρίς βαθυπερατό φίλτρο, ενώ για τον βρόχο διαχείρισης του προφίλ τάσης υλοποιήθηκε μόνο ο ελεγκτής στατισμού. Επίσης, υλοποιήθηκαν συστήματα με και χωρίς εσωτερικό επίπεδο ελέγχου. Για τις δομές με εσωτερικό επίπεδο υλοποιήθηκε το σύστημα ελέγχου με δύο βρόχους, το οποίο αποτελείται από βρόχο εικονικής αγωγιμότητας και ελεγκτή ρεύματος. Επιπρόσθετα, από τις άμεσες τεχνικές περιορισμού του ρεύματος υλοποιήθηκε ο περιοριστής μέτρου, ο περιοριστής σε δεδομένη γωνία και οι δύο μέθοδοι που δίνουν προτεραιότητα στην d- και q-συνιστώσα του ρεύματος, ενώ από τις έμμεσες υλοποιήθηκε η μέθοδος εικονικής εμπεδησης. Αναφέρεται επίσης ότι οι άμεσες μέθοδοι εφαρμόστηκαν σε συνδυασμό με την δομή που περιλαμβάνει

εσωτερικό επίπεδο ελέγχου, ενώ η μέθοδος εικονικής εμπέδησης χρησιμοποιήθηκε με την δομή χωρίς εσωτερικό επίπεδο.

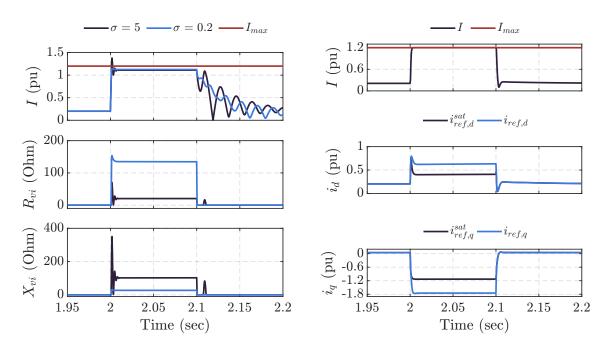

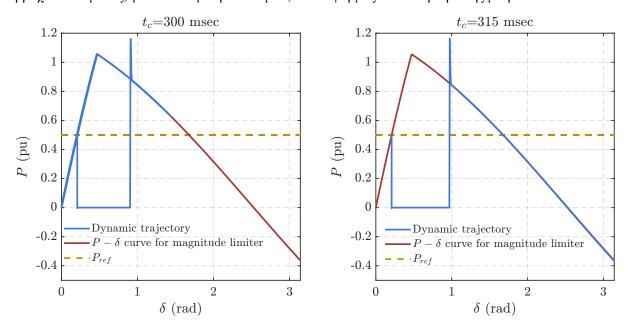

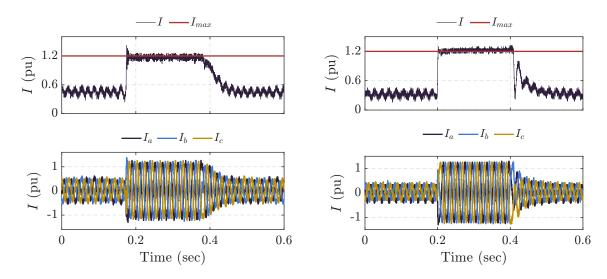

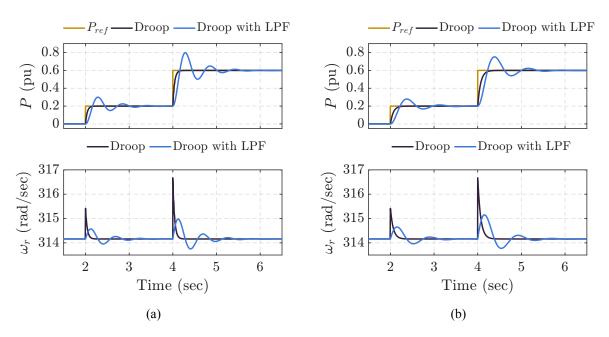

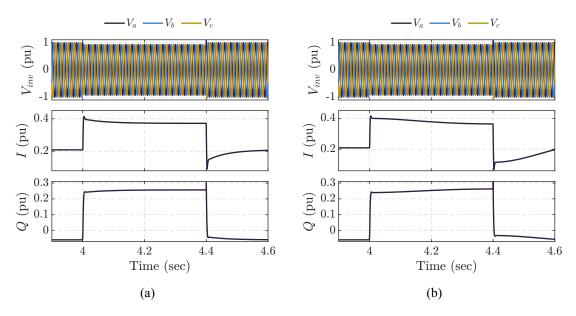

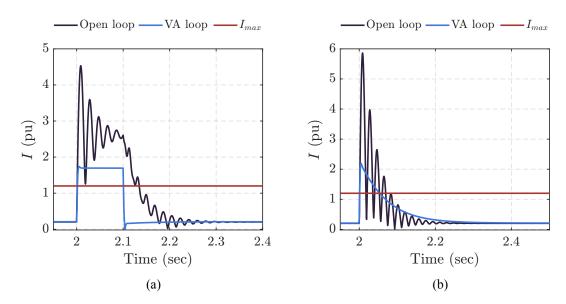

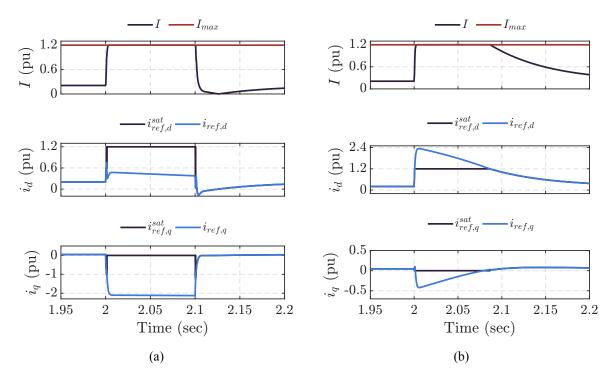

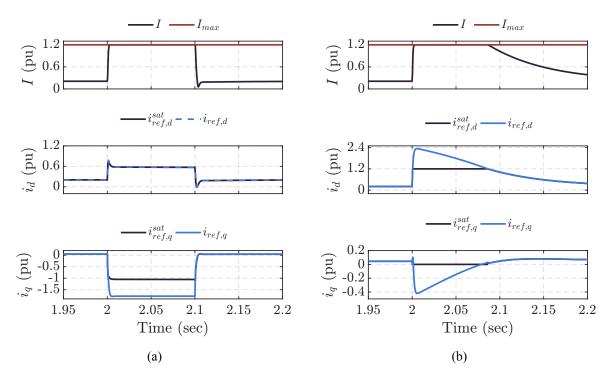

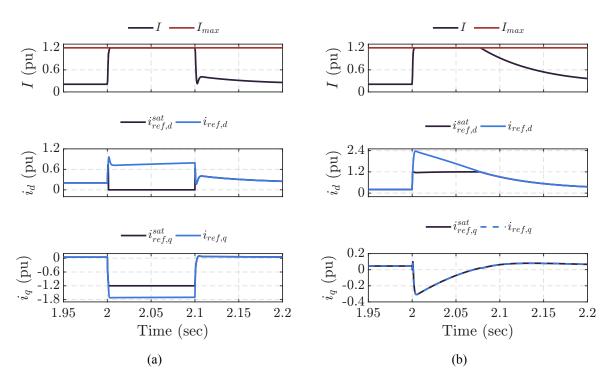

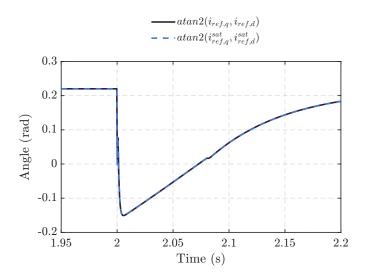

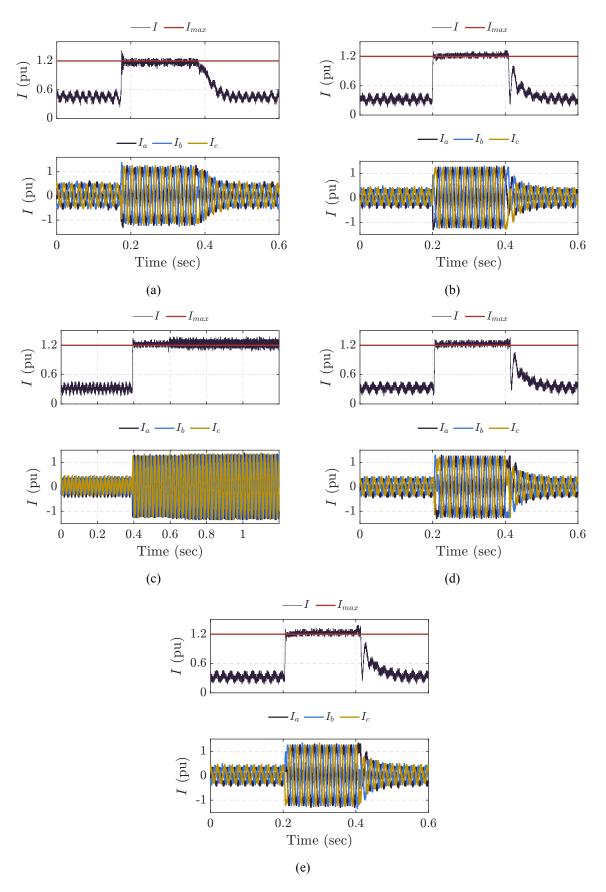

Αρχικά, μέσω προσομοιώσεων επιβεβαιώθηκε η ευαισθησία του ρεύματος στις συνθήκες του δικτύου, καθώς και ότι η προσθήκη του βαθυπερατού φίλτρου στον ελεγκτή στατισμού ενεργού ισχύος παρέχει εικονική αδράνεια. Έπειτα, για την επιβεβαίωση της λειτουργίας των τεχνικών περιορισμού ρεύματος προσομοιώθηκαν τα σφάλματα που αναφέρθηκαν πιο πάνω. Στο Σχήμα που ακολουθεί, παρουσιάζονται ενδεικτικά τα αποτελέσματα της προσομοίωσης της βύθισης τάσης του δικτύου για δύο μόνο από τις υλοποιημένες μεθόδους.

Σχήμα: Αποτελέσματα προσομοίωσης για βύθιση τάσης του δικτύου (Αριστερά) Εικονική εμπέδηση; (Δεξιά) Περιοριστής μέτρου

Φαίνεται ότι και οι δύο μέθοδοι περιορίζουν το μέτρο του ρεύματος. Όταν χρησιμοποιείται η μέθοδος της εικονικής εμπέδησης, μπορεί να εμφανιστεί προσωρινή υπερένταση στο αρχικό στάδιο του σφάλματός, ενώ στη συνέχεια δεν αξιοποιείται πλήρως το διαθέσιμο περιθώριο υπερέντασης του αντιστροφέα. Αντίθετα, ο περιοριστής μέτρου περιορίζει το ρεύμα ακριβώς στην μέγιστη επιτρεπτή τιμή, προσαρμόζοντας τις τιμές αναφοράς του ρεύματος.

Συμπερασματικά, τα αποτελέσματα των προσομοιώσεων επιβεβαιώνουν την ικανοποιητική λειτουργία των τεχνικών περιορισμού του ρεύματος που υλοποιήθηκαν.

# Κεφάλαιο 3. Επίδραση των μεθόδων περιορισμού ρεύματος στην μεταβατική ευστάθεια

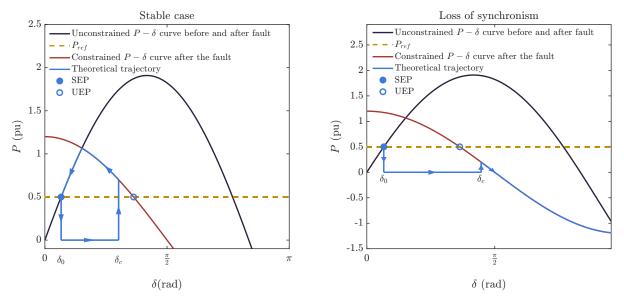

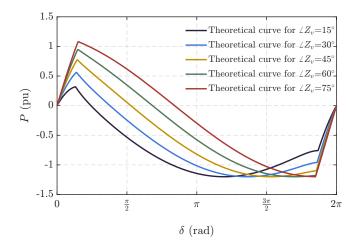

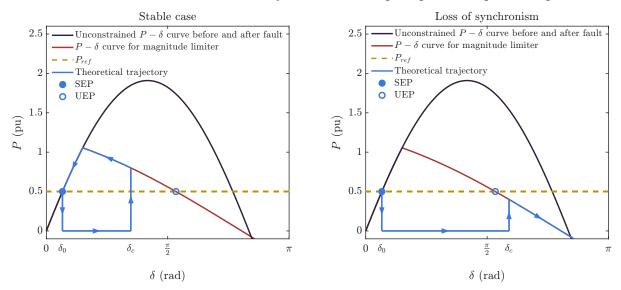

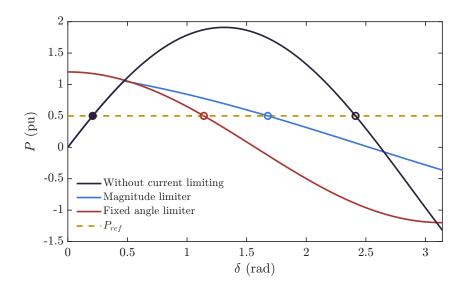

Παρόμοια με τις σύγχρονες γεννήτριες, η μελέτη της μεταβατικής ευστάθειας για τους GFMIs μπορεί να γίνει μέσω των  $P-\delta$  καμπύλων, όπου  $\delta$  είναι η διαφορά γωνίας μεταξύ της γωνίας αναφοράς για την εσωτερική τάση του αντιστροφέα και της γωνίας της τάσης του δικτύου. Αυτή η διαφορά γωνίας αναφέρεται ως Εικονική Γωνία Ισχύος. Σε αντίθεση με τις σύγχρονες γεννήτριες, σε μεγάλες διαταραχές είναι πιθανό να ενεργοποιηθεί ο περιοριστής ρεύματος του αντιστροφέα, και συνεπώς η  $P-\delta$  καμπύλη του αντιστροφέα καθορίζεται από την μέθοδο περιορισμού ρεύματος που εφαρμόζεται.

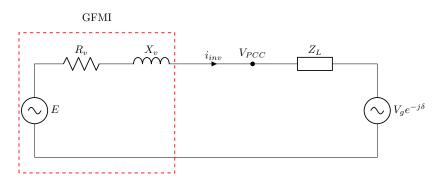

Για την μελέτη της μεταβατικής ευστάθειας του αντιστροφέα χρησιμοποιείται ένα

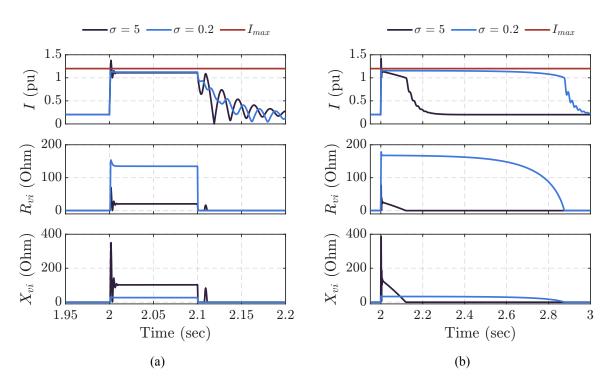

σύστημα στο οποίο ο αντιστροφέας συνδέεται σε έναν άπειρο ζυγό, παρόμοια με το σύστημα που χρησιμοποιήθηκε στο Κεφάλαιο 2. Επίσης, για την απλοποίηση της ανάλυσης, η γραμμή μεταφοράς θεωρείται πλήρως επαγωγική, ενώ αγνοείται η επίδραση του ελεγκτή στατισμού άεργου ισχύος. Επιπρόσθετα, για να μελετηθεί η επίδραση των μεθόδων περιορισμού ρεύματος στην μεταβατική ευστάθεια, στον παρόν Κεφάλαιο αναλύονται ενδεικτικά μόνο οι περιπτώσεις του περιοριστή μέτρου και περιοριστή σε δεδομένη γωνία.

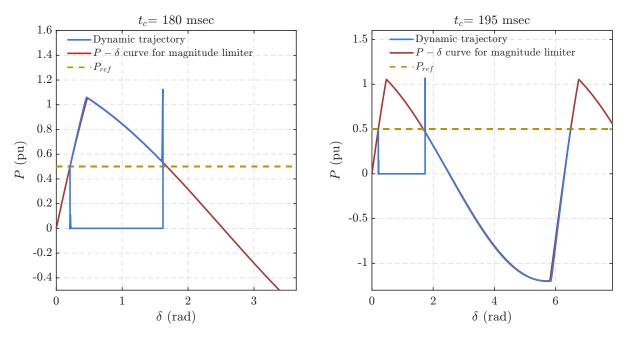

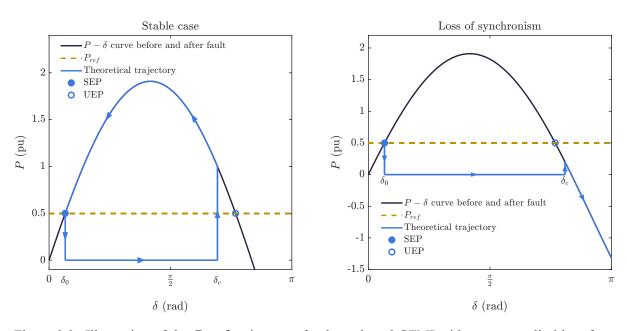

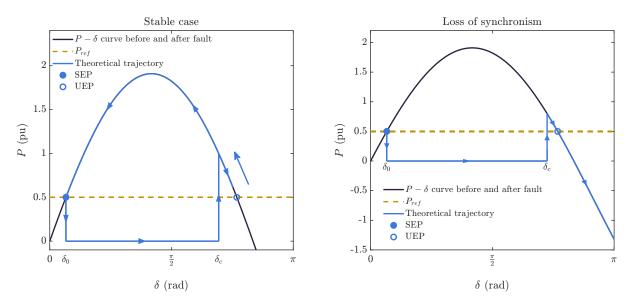

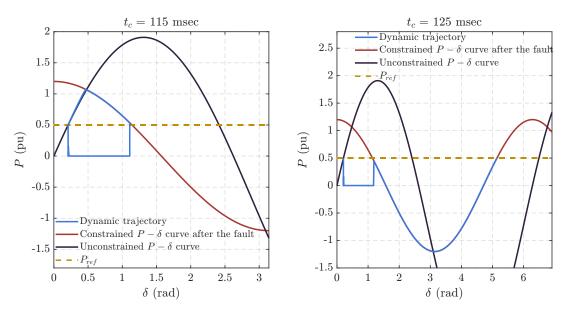

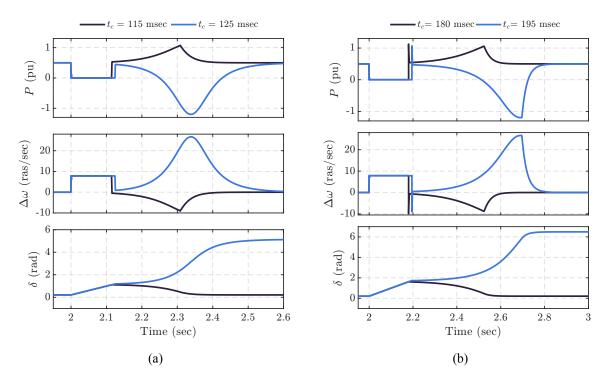

Οι  $P-\delta$  καμπύλες εξάγονται μέσω των μοντέλων μεγάλου σήματος για την κάθε μέθοδο που χρησιμοποιήθηκε. Έπειτα, με βάση τις  $P-\delta$  καμπύλες μπορεί να εξηγηθεί η πορεία της ενεργού ισχύος κατά και μετά από ένα σφάλμα, όπως ένα βραχυκύκλωμα, ανάλογα με το αν χρησιμοποιείται ελεγκτής στατισμού με ή χωρίς βαθυπερατό φίλτρο για τον ελεγκτή ενεργού ισχύος.

Στην περίπτωση του βραχυκυκλώματος, για να παραμείνει σε συγχρονισμό με το δίκτυο ο αντιστροφέας με τον απλό ελεγκτή στατισμού, αρκεί να εκκαθαριστεί το σφάλμα προτού η εικονική γωνία ισχύος ξεπεράσει την γωνία που αντιστοιχεί στο ασταθές σημείο ισορροπίας της  $P-\delta$  καμπύλης μετά το σφάλμα. Αλλιώς, ο συγχρονισμός χάνεται και μετά από περίπου ένα κύκλο ταλάντωσης η εικονική γωνία ισχύος καταλήγει στο νέο σημείο ισορροπίας (αν υπάρχει), επειδή το σύστημα για τον απλό ελεγκτή στατισμού είναι πρώτης τάξης.

Αντίθετα, η προσθήκη του βαθυπερατού φίλτρου έχει ως αποτέλεσμα την αύξηση της τάξης του συστήματος σε δεύτερης τάξης. Πλέον, ο αντιστροφέας μπορεί να χάσει τον συγχρονισμό με το δίκτυο ακόμα και αν το βραχυκύκλωμα εκκαθαριστεί προτού η εικονική γωνία ισχύος ξεπεράσει την γωνία που αντιστοιχεί στο ασταθές σημείο ισορροπίας. Συγκεκριμένα, κατά τη διάρκεια του βραχυκυκλώματος η συχνότητα του αντιστροφέα επιταχύνεται με αποτέλεσμα το  $\Delta \omega$  να γίνεται θετικό και να αυξάνεται η εικονική γωνία ισχύος. Όταν εκκαθαριστεί το σφάλμα, η συχνότητα αρχίζει να επιβραδύνεται αλλά το  $\Delta \omega$  παραμένει θετικό, και συνεπώς η εικονική γωνία ισχύος συνεχίζει να αυξάνεται. Αν το  $\Delta \omega$  γίνει αρνητικό προτού η εικονική γωνία ισχύος ξεπεράσει την γωνία που αντιστοιχεί στο ασταθές σημείο ισορροπίας, τότε η γωνία ξεκινάει να μειώνεται και καταλήγει στο ευσταθές σημείο ισορροπίας μετά από κάποιες ταλαντώσεις. Από την άλλη, αν η γωνία ξεπεράσει το ασταθές σημείο ισορροπίας προτού το  $\Delta \omega$  γίνει αρνητικό, τότε το  $\Delta \omega$  ξεκινάει να αυξάνεται ξανά και χάνεται ο συγχρονισμός με το δίκτυο.

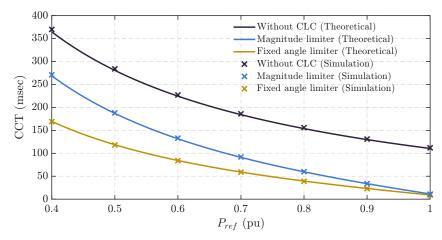

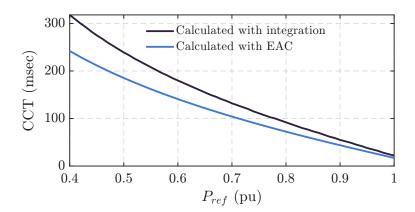

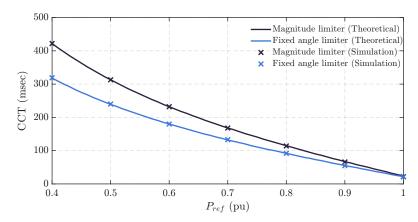

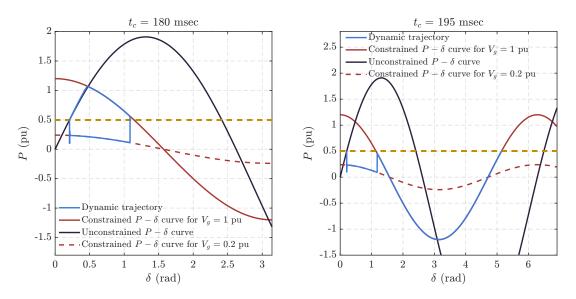

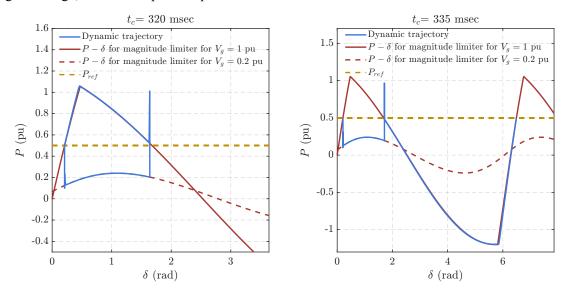

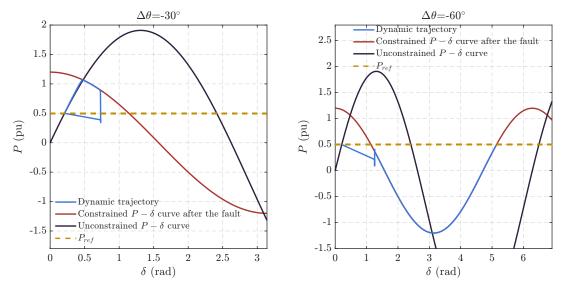

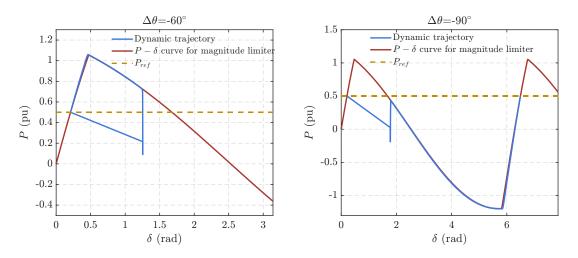

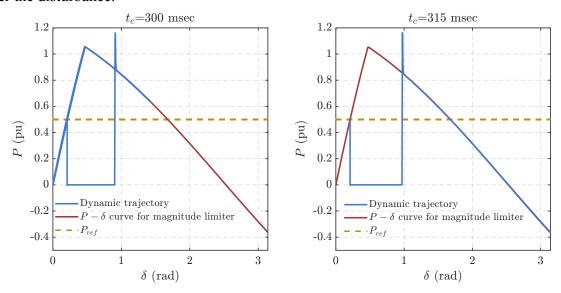

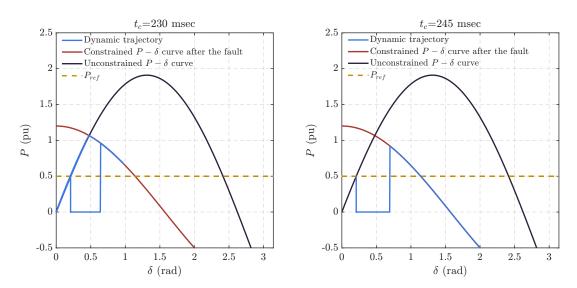

Αφού εξηγήθηκε η θεωρητική πορεία της ενεργού ισχύος κατά και μετά το βραχυκύκλωμα, μπορεί να μελετηθεί η επίδραση των μεθόδων περιορισμού ρεύματος στην μεταβατική ευστάθεια. Μέσω των  $P-\delta$  καμπύλων που προκύπτουν από τα μοντέλα μεγάλου σήματος των δύο μεθόδων, παρατηρείται ότι σε σχέση με την περίπτωση που δεν εφαρμόζεται περιορισμός ρεύματος, το ασταθές σημείο ισορροπίας μετατοπίζεται πιο κοντά στο ευσταθές και ότι η ικανότητα μεταφοράς ισχύος μειώνεται.  $\Omega$ ς αποτέλεσμα, ο περιορισμός του ρεύματος του αντιστροφέα επηρεάζει αρνητικά την μεταβατική ευστάθεια του. Επιπλέον, παρατηρείται ότι για τις συγκεκριμένες παραμέτρους εικονικής αγωγιμότητας που χρησιμοποιήθηκαν, ο περιοριστής μέτρου προσφέρει μεγαλύτερο περιθώριο μεταβατικής ευστάθειας σε σύγκριση με τον περιοριστή σε δεδομένη γωνία (για μηδενική προεπίλεγμένη γωνία). Τέλος, διαπιστώνεται ότι ο υπολογισμός του κρίσιμου χρόνου εκκαθάρισης με την μέθοδο των ίσων εμβαδών οδηγεί σε πιο συντηρητικά αποτελέσματα σε σύγκριση με την αριθμητική ολοκλήρωση των δυναμικών εξισώσεων.

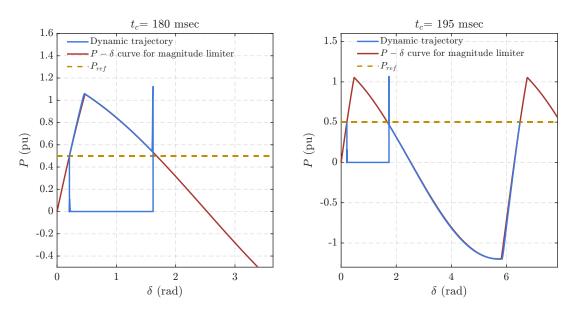

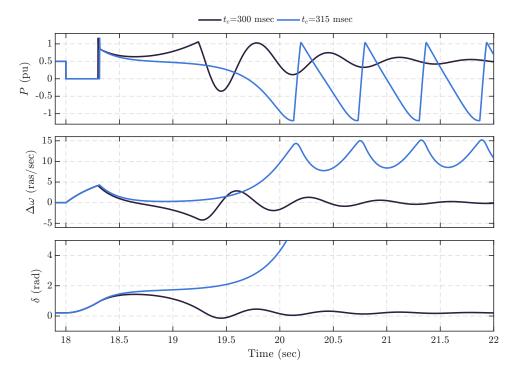

Προκειμένου να επιβεβαιωθούν τα μοντέλα μεγάλου σήματος και η θεωρητική ανάλυση, πραγματοποιούνται προσομοιώσεις διάφορων σφαλμάτων όπως βραχυκύκλωμα, βύθιση τάσης και απότομες αλλαγές φάσης της τάσης του δικτύου. Ενδεικτικά παρακάτω παρουσιάζεται η σύγκριση των θεωρητικών  $P-\delta$  καμπυλών με αυτές που προκύπτουν από την προσομοίωση ενός βραχυκυκλώματος, για τον ελεγκτή στατισμού με και χωρίς βαθυπερατό φίλτρο, χρησιμοποιώντας ως μέθοδο περιορισμού τον περιοριστή μέτρου.

Σχήμα: Σύγκριση θεωρητικών  $P-\delta$  καμπύλων με αυτές που προκύπτουν από την προσομοίωση ενός βραχυκυκλώματος, για τον ελεγκτή στατισμού, όταν εφαρμόζεται ο περιοριστής μέτρου

Σχήμα: Σύγκριση θεωρητικών  $P-\delta$  καμπύλων με αυτές που προκύπτουν από την προσομοίωση ενός βραχυκυκλώματος, για τον ελεγκτή στατισμού με βαθυπερατό φίλτρο, όταν εφαρμόζεται ο περιοριστής μέτρου

## Κεφάλαιο 4. Προσομοίωση πραγματικού χρόνου

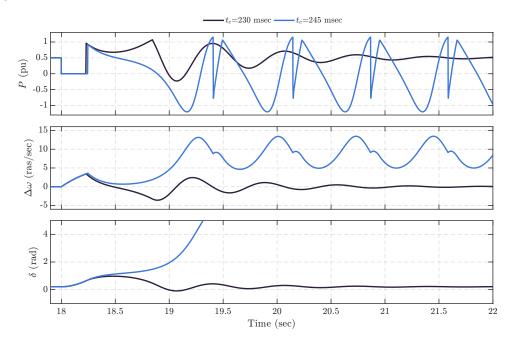

Οι προσομοιωτές πραγματικού χρόνου μπορούν να λύνουν τις διαφορικές εξισώσεις που περιγράφουν το σύστημα, σε πραγματικό χρόνο, με την χρήση ψηφιακού υλικού (digital hardware) και παράλληλων υπολογιστικών μεθόδων (parallel computing). Στις offline προσομοιώσεις, η στιγμή κατά την οποία είναι διαθέσιμα τα αποτελέσματα της προσομοίωσης δεν είναι σημαντική. Επομένως, η ταχύτητα με την οποία λύνονται οι εξισώσεις του συστήματος εξαρτάται από τους υπολογιστικούς πόρους και την πολυπλοκότητα του συστήματος. Αντίθετα, σε μια προσομοίωση πραγματικού χρόνου, οι

εξισώσεις του συστήματος για ένα βήμα προσομοίωσης πρέπει να επιλύονται μέσα στο ίδιο χρονικό διάστημα σε πραγματικό χρόνο.

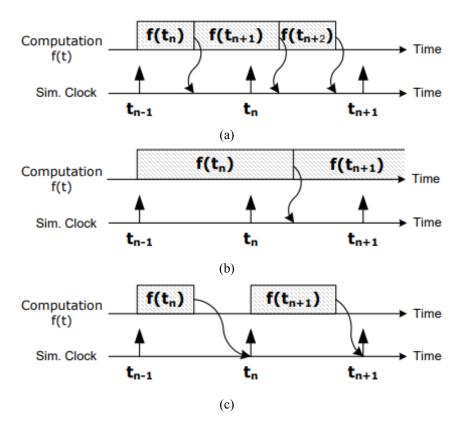

Όταν κάποια στοιχεία του συστήματος προσομοίωσης αντικαθίστανται με τον αντίστοιχο πραγματικό εξοπλισμό, ο οποίος αλληλεπιδρά με το υπόλοιπο σύστημα που προσομοιώνεται, η προσομοίωση αναφέρεται ως "harware-in-the-loop" (HIL). Επίσης, όταν το στοιχείο που αντικαθίσταται είναι ο ελεγκτής, η προσομοίωση αναφέρεται ως "controller hardware-in-the-loop" (CHIL). Με αυτό τον τρόπο, μια καινούρια υλοποίηση ελέγχου μπορεί να δοκιμαστεί σε συνθήκες πραγματικού χρόνου, όπου η συμπεριφορά των πραγματικών στοιχείων του συστήματος αναπαριστάται με μεγαλύτερη ακρίβεια.

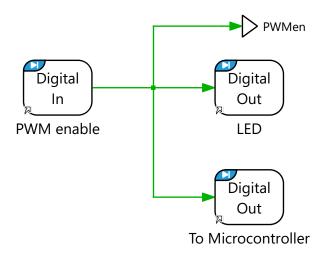

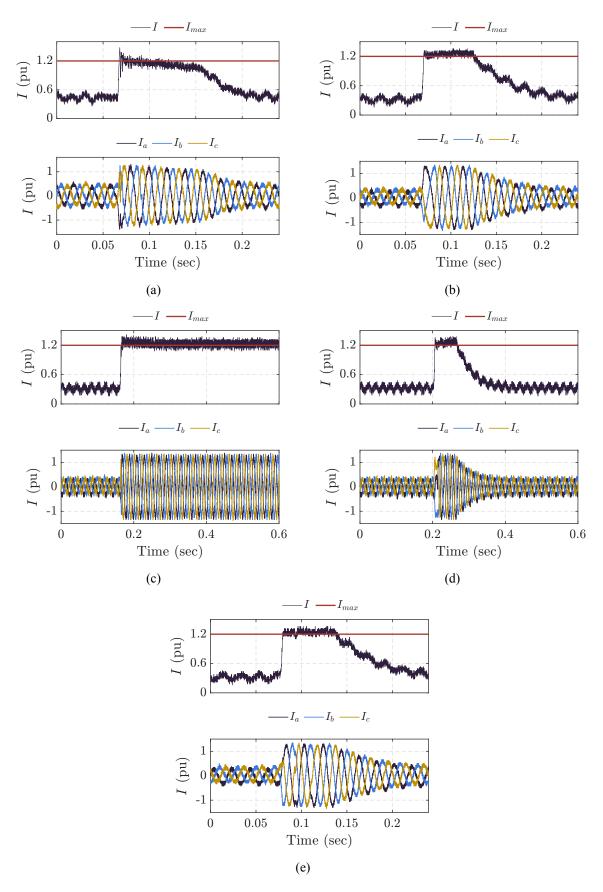

Με βάση τα πιο πάνω, πραγματοποιήθηκε μια CHIL προσομοίωση πραγματικού χρόνου, προκειμένου να επιβεβαιωθεί η αποτελεσματική λειτουργία των μεθόδων περιορισμού ρεύματος που υλοποιήθηκαν, σε συνθήκες πραγματικού χρόνου. Τα συστήματα ελέγχου υλοποιήθηκαν στον μικροεπεξεργαστή C2000 LAUNCHXL-F28379D της Texas Instruments, ενώ το υπόλοιπο σύστημα προσομοίωσης υλοποιήθηκε στον προσομοιωτή πραγματικού χρόνου RT Box 1 της Plexim. Πιο συγκεκριμένα, το RT Box προσομοιώνει το σύστημα ισχύος (π.χ δίκτυο, γραμμή μεταφοράς κλπ) και στέλνει τα αποτελέσματα για την τάση και το ρεύμα στον μικροεπεξεργαστή. Έπειτα, ο μικροεπεξεργαστής επεξεργάζεται τα σήματα που λαμβάνει με βάση τα υλοποιημένα συστήματα ελέγχου και παράγει τους παλμούς μεταγωγής των διακοπτικών στοιχείων του αντιστροφέα, τους οποίους στέλνει πίσω στο RT Box. Επιπλέον, χρησιμοποιήθηκε ένας παλμογράφος, προκειμένου να παρατηρηθούν οι κυματομορφές των σημάτων που παρέχει το RT Box ως έξοδο, όπως για παράδειγμα το τριφασικό ρεύμα εξόδου του αντιστροφέα.

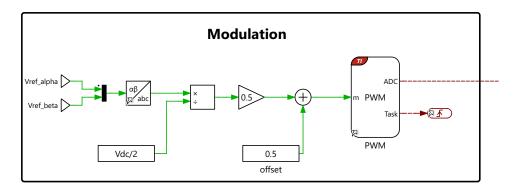

Το σύστημα που προσομοιώνεται στο RT Box είναι πολύ παρόμοιο με το αντίστοιχο των offline προσομοιώσεων. Οι κύριες διαφορές είναι η προσθήκη ενός ωμικού φορτίου στο σημείο που συνδέεται ο αντιστροφέας στο δίκτυο και η χρήση του πλήρους μοντέλου του αντιστροφέα με τους διακόπτες ισχύος αντί του μοντέλου μέσης τιμής. Ανάλογα, τα συστήματα ελέγχου που υλοποιούνται στον μικροελεγκτή είναι παρόμοια με αυτά των offline προσομοιώσεων, με την διαφορά ότι έχει προστεθεί το σύστημα διαμόρφωσης SPWM και κάποια βαθυπερατά φίλτρα για την καταστολή του θορύβου.

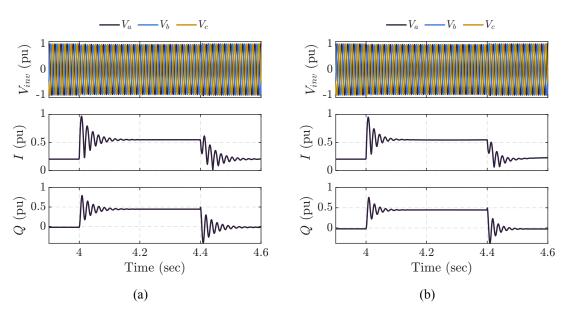

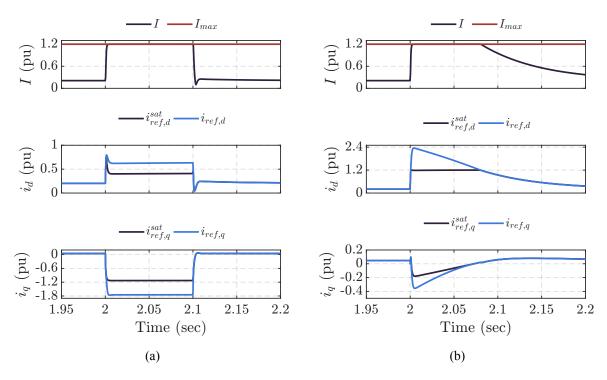

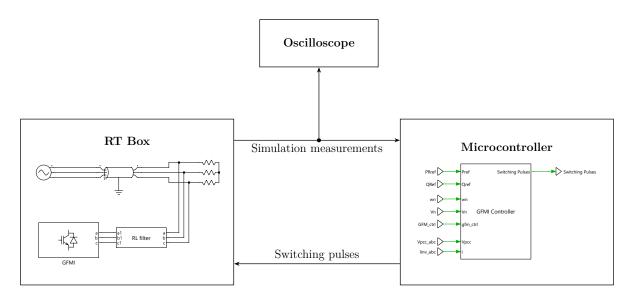

Για την επιβεβαίωση των τεχνικών περιορισμού ρεύματος που υλοποιήθηκαν, πραγματοποιήθηκαν προσομοιώσεις πραγματικού χρόνου για βραχυκύκλωμα και για απότομη αλλαγή φάσης της τάσης του δικτύου. Στο παρακάτω Σχήμα παρουσιάζονται ενδεικτικά τα αποτελέσματα της προσομοίωσης του βραχυκυκλώματος για δύο μόνο από τις υλοποιημένες μεθόδους. Συγκεκριμένα η μια μέθοδος είναι αυτή της εικονικής εμπέδησης, ενώ η άλλη είναι ο περιοριστής μέτρου προκειμένου να φανούν οι διαφορές στην απόκριση των έμμεσων και άμεσων μεθόδων.

Φαίνεται ότι και οι δύο μέθοδοι περιορίζουν το μέτρο του ρεύματος. Σε αντίθεση με τον περιοριστή μέτρου, φαίνεται ότι στην περίπτωση της εικονικής εμπέδησης παρατηρείται μια προσωρινή υπερένταση στο αρχικό στάδιο του σφάλματος, γεγονός που συνάδει με τα αποτελέσματα της offline προσομοίωσης.

Συμπερασματικά, τα αποτελέσματα των προσομοιώσεων πραγματικού χρόνου δείχνουν ότι οι υλοποιημένες τεχνικές περιορισμού του ρεύματος του αντιστροφέα λειτουργούν αποτελεσματικά υπό συνθήκες πραγματικού χρόνου.

## Κεφάλαιο 5. Συμπεράσματα και προοπτικές

#### Συμπεράσματα

Οι GFMI συμπεριφέρονται ως πηγές τάσης με αποτέλεσμα το ρεύμα τους να είναι

Σχήμα: Αποτελέσματα προσομοίωσης πραγματικού χρόνου για βραχυκύκλωμα (Αριστερά) Εικονική εμπέδηση; (Δεξιά) Περιοριστής μέτρου

ευαίσθητο σε συνθήκες του δικτύου. Επομένως, σε περιπτώσεις μεγάλων διαταραχών, το ρεύμα τους μπορεί να υπερβεί την μέγιστη επιτρεπόμενη τιμή, καθιστώντας απαραίτητη την εφαρμογή μεθόδων περιορισμού του ρεύματος. Ωστόσο, με την ενεργοποίηση αυτών των μεθόδων παρακάμπτεται η κανονική λειτουργία, με αποτέλεσμα η δυναμική συμπεριφορά του αντιστροφέα κατά και μετά το σφάλμα να καθορίζεται κυρίως από την μέθοδο που εφαρμόζεται.

Οι περισσότερες μέθοδοι διαμόρφωσης δικτύου μπορούν να αναπαρασταθούν από ένα γενικό σύστημα ελέγχου πολλαπλών επιπέδων και υποσυστημάτων. Συχνά χρησιμοποιούμενες υλοποιήσεις για τον ελεγκτή ενεργού ισχύος περιλαμβάνουν τον ελεγκτή στατισμού με και χωρίς βαθυπερατό φίλτρο και την Εικονική Σύγχρονη Γεννήτρια. Η προσθήκη του βαθυπερατού φίλτρου στον ελεγκτή στατισμού εισάγει εικονική αδράνεια, γεγονός που επιβεβαιώνεται μέσω προσομοίωσης.

Οι μέθοδοι περιορισμού του ρεύματος διακρίνονται σε άμεσες, έμμεσες και υβριδικές. Μερικές συχνά χρησιμοποιούμενες μέθοδοι υλοποιήθηκαν στο λογισμικό προσομοίωσης PLECS και η αποτελεσματική λειτουργία τους επιβεβαιώθηκε μέσω προσομοιώσεων για βυθίσεις τάσης και απότομες αλλαγές φάσης. Η μέθοδος εικονικής εμπέδησης δεν μπορεί να αξιοποιήσει πλήρως το περιθώριο υπερέντασης του αντιστροφέα σε όλη τη διάρκεια του σφάλματος και μπορεί να εμφανίσει προσωρινή υπερένταση στο αρχικό στάδιο του σφάλματος. Αντίθετα, οι άμεσες μέθοδοι μπορούν να πετύχουν γρήγορο και ακριβή περιορισμό του ρεύματος, αξιοποιώντας πλήρως το περιθώριο υπερέντασης.

Η Εικονική Γωνία Ισχύος χρησιμοποιείται για την ανάλυση της μεταβατικής ευστάθειας των GFMI, μέσω των  $P-\delta$  καμπύλων που προκύπτουν από μοντέλα μεγάλου σήματος, τα οποία διαφέρουν ανάλογα με τη μέθοδο περιορισμού ρεύματος που εφαρμόζεται. Εξηγείται ότι η πορεία της ενεργού ισχύος μετά από ένα βραχυκύκλωμα διαφέρει μεταξύ του ελέγχου με και χωρίς αδράνεια. Επιπλέον, οι  $P-\delta$  καμπύλες που προκύπτουν για τον περιοριστή μέτρου και τον περιοριστή σε δεδομένη γωνία δείχνουν ότι ο περιορισμός ρεύματος μειώνει σημαντικά το περιθώριο μεταβατικής ευστάθειας. Ακόμη, η εφαρμογή της μεθόδου ίσων εμβαδών για τον υπολογισμό του κρίσιμου χρόνου εκκαθάρισης για βραχυκυκλώματα, οδηγεί σε συντηρητικά αποτελέσματα συγκριτικά με την αριθμητική ολοκλήρωση των δυναμικών εξισώσεων του συστήματος. Οι προσομοιώσεις που πραγματοποιήθηκαν επιβεβαιώνουν τα μοντέλα μεγάλου σήματος, καθώς και την θεωρητική ανάλυση.

Τέλος, μέσω προσομοίωσης πραγματικού χρόνου, επιβεβαιώθηκε ότι οι υλοποιημένες τεχνικές περιορισμού ρεύματος, μπορούν να περιορίζουν το ρεύμα σε σφάλματα όπως βραχυκύκλωμα και απότομη αλλαγή φάσης, υπό συνθήκες πραγματικού χρόνου.

## Προοπτικές

Μια προοπτική μελλοντικής δουλειάς είναι η ανάπτυξη σχημάτων αντιμετώπισης της συσσώρευσης ολοκληρωτικού σφάλματος (anti-windup schemes) όταν χρησιμοποιείται ελεγκτής τάσης αντί βρόχος εικονικής αγωγιμότητας. Επίσης, η σχεδίαση μεθόδων περιορισμού ρεύματος για ασύμμετρα σφάλματα είναι απαραίτητη. Μπορούν επίσης να υλοποιηθούν και να συγκριθούν μεταξύ τους, διάφορες μέθοδοι ενίσχυσης της μεταβατικής ευστάθειας. Πολύ σημαντική είναι η εφαρμογή μεθόδων περιορισμού ρεύματος για πιο πολύπλοκες τοπολογίες μετατροπέων, όπως είναι οι αρθρωτοί πολυεπίπεδοι μετατροπείς (ΜΜC). Τέλος, θεωρείται σημαντική η πειραματική επιβεβαίωση της λειτουργίας των μεθόδων περιορισμού ρεύματος.

## Chapter 1

## Introduction

## 1.1 Transformation of the power system

Traditional power systems are currently undergoing a major transformation, driven by the need to address global warming and reduce greenhouse gas emissions. There is a global shift towards cleaner forms of electric energy generation, resulting in a gradual replacement of large centralized thermal power plants with smaller scale Renewable Energy Sources (RES), such as solar and wind. This transition is being accelerated by ambitious national and international targets aimed at increasing the share of RES in the energy production mix, such as the EU commitment of achieving climate neutrality by 2050 [1], which sets a clear direction for the decarbonization of the power grid.

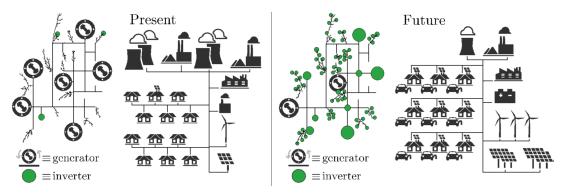

Conventional power grids were dominated by large Synchronous Generators (SGs), which were responsible for voltage and frequency regulation. Their low output impedance and the use of Automatic Voltage Regulators (AVR), allow them to operate as ideal voltage sources, which in combination with their high rotor inertia, are essential features for ensuring stable and reliable operation of the power system [2]. In contrast, most renewable energy sources are integrated into the grid via power electronic converters and are therefore referred to as Inverter-Based Resources (IBRs). Power electronic converters are significantly different than SGs, not only due to their hardware characteristics, but also in the way they respond to disturbances and grid events. Unlike SGs, their behavior is not governed by inherent physical properties such as rotor inertia, but it rather depends on their control algorithms [3]. Thus, the ongoing transformation from an SG-dominated grid to an IBR-dominated one, which is illustrated in Fig. 1.1, has introduced various engineering and operational challenges that need to be addressed, in order to ensure the stability and resilience of the future renewable-rich power grids.

Figure 1.1: Transition of the power grid from SG-dominated to IBR-dominated [4]

## 1.2 Inverter Based Resources

The majority of renewable energy sources are connected to the grid through a series of power electronic converters, because the power they generate is not inherently compatible with the power system's frequency and voltage level requirements (e.g 50 Hz, 20 kV) [5]. Despite the fact that some IBRs utilize more than one converter, their behavior is primarily determined by the last dc/ac inverter as it is directly connected to the grid [6], hence the term "Inverter Based Resources". Other IBRs include battery energy storage systems (BESS), fuel cells, high voltage direct current (HVDC) converters etc.

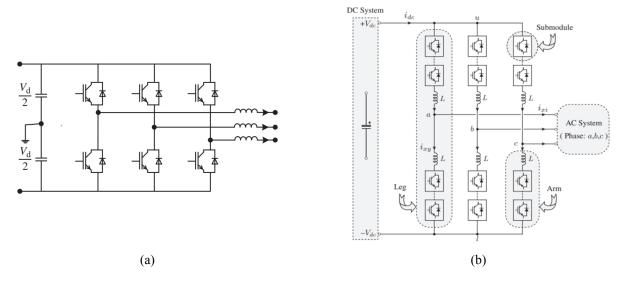

In recent years, the dc/ac conversion is achieved utilizing Voltage Source Converters (VSCs). These inverters use fully controllable semiconductors, such as IGBTs and power MOSFETs, allowing fast and precise control of their output voltage and four quadrant operation. As shown in Fig. 1.2, a three phase VSC converts the dc-link voltage to a three phase ac voltage at a specified fundamental frequency along with various harmonic components, using Pulse Width Modulation (PWM) techniques. In lower voltage levels, such as the distribution network, RES are connected to the grid with two-level VSCs [7], whose configuration is shown in Fig. 1.3a. These are the simplest VSCs and they consist of a common dc link and three half-bridge legs, one for each phase. In order to meet the requirements for harmonic injection to the grid, two-level VSCs should either use high switching frequencies or excessive harmonic filters, which lead to an increase of switching losses and system complexity respectively [8]. For this reason, in high-voltage high-power applications, such as HVDC links, multilevel converters are typically used as an alternative to conventional two-level VSCs. The most popular multilevel converter is the Modular Multilevel Converter (MMC), shown in Fig. 1.3b, which consists of a number of submodules that can either be a half-bridge or full-bridge topology and capacitors that are distributed in each submodule [8], [9]. This structure allows MMCs to produce an output voltage with multiple levels, leading to high quality waveforms combined with high efficiency.

Figure 1.2: High level representation of a three phase Voltage Source Converter [10]

As illustrated in Fig. 1.2 the reference voltage fed to the PWM is generated by the inverter's control system. Due to the high modulation bandwidth, the fundamental component of the output voltage can be considered equal to the reference. Thus, assuming that the dc-link voltage is constant, the voltage at the VSC terminal is determined by the control system

Figure 1.3: (a) Three phase two-level VSC [9]; (b) Three phase MMC with half-bridge or full-bridge submodules [11]

output. Depending on their control algorithm, grid-connected VSCs can be classified into two main categories, namely grid-following inverters (GFLIs) and grid-forming inverters (GFMIs) [5]. Despite having a very similar hardware configuration (dc link, output filters, switching valves etc) and sharing the common goal of injecting active and reactive power to the grid, GFMIs and GFLIs differ significantly in their control systems, modeling representation, response to grid events, and small signal stability under different grid strengths [12].

### **Grid-Following Inverters**

Currently, the vast majority of IBRs connected to the power system are controlled as grid following inverters. Traditionally, the main objective of GFLIs was to synchronize with the grid and supply active power, while maintaining their power factor close to unity [2]. GFLIs utilize a dedicated synchronization unit, such as a phase-locked loop (PLL), to track the angle of the voltage at the Point of Common Coupling (PCC). Then this angle is used to transform the measured voltage and current to the synchronous reference frame (i.e., the dq frame), where it is easier to design and implement the inverter controllers. The active and reactive power injection of a GFLI can be independently controlled, by adjusting the d-axis and q-axis component of the current respectively [2]. This control scheme is usually referred to as current control, because the output current of the inverter is directly controlled, and it is widely used in grid connected, as well as motor drive applications [4]. Because of the control principle that was explained above, it is evident that the behavior of GFLIs can be approximated as a current source with high parallel impedance [2], [4], [12].

Due to the growing number of IBRs that are connected to the grid and the replacement of synchronous generators, grid operators require that larger-scale IBRs have to actively support the power system, by exchanging active and reactive power depending on the type of disturbance. For instance, German grid operators require that IBRs should support the voltage by supplying (absorbing) reactive current, if the measured voltage decreases (increases) beyond a predefined dead-band [5], [13]. GFLIs can achieve this by accordingly adjusting active and reactive power set-points, while respecting the hardware limitations of the converter [12]. Due to the lack of inherent inertia in IBRs, another grid supporting function that can be added to the control system of GFLIs, is the so-called "synthetic inertia" or fast

frequency response (FFR), which regulates the active power output of the converter during frequency disturbances [14], [15]. The drawback of the FFR provided by GFLIs, is that frequency estimation and control delays can limit the efficiency of the inertial response. Furthermore, the use of the frequency derivative can introduce additional noise, compromising the stability of the system [15].

Despite being the dominant approach currently in use, grid-following inverters have two main shortcomings. Many research works have demonstrated that the use of a PLL and other synchronization units can deteriorate the small-signal stability of IBRs connected to low-strength parts of the grid [16], [17], [18]. Therefore, GFLIs are generally unsuitable for weak grid applications (i.e., low short circuit ratio) such as offshore wind parks connected to the grid through long transmission lines, as they cannot ensure stable operation [15]. Moreover, GFLIs operate under the assumption that they can synchronize and "follow" a stiff and already formed voltage, hence the term "grid following". Consequently, a future power electronics dominated grid can not operate using only grid-following converters, because they will have no voltage to synchronize to, due to the lack of voltage forming units such as synchronous generators [5], [16]. For the same reason, GFLIs can not help in the procedure of restarting the power system after a blackout, which is referred to as "black start" [16].

#### **Grid-Forming Inverters**

Although a formal and unified definition of GFMIs is still under discussion in academia and industry [12], there exist various different definitions, mainly proposed by grid codes, which describe the functionalities that a GFMI should have [19], [20]. Among all these definitions, the most common and accepted characteristic of GFMIs is their voltage-source behavior, which enables them to respond to grid events similar to SGs [21]. For instance, the North American Electric Reliability Corporation (NERC) states that grid-forming controls are "controls with the primary objective of maintaining an internal voltage phasor that is constant or nearly constant in the sub-transient to transient time frame" [22]. Thus, a GFMI can be defined as a converter controlled to behave as an AC voltage source, which is able to "form" the voltage without the need of other voltage forming units [21]. For this reason, grid-forming control of IBRs is widely recognized as a promising solution to enhance the stability of the future bulk power system.

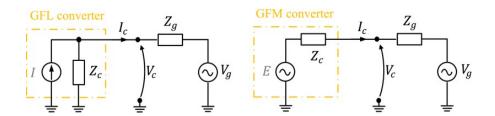

The main difference between GFMIs and GFLIs is that they are controlled as voltage and current sources respectively<sup>1</sup>, as illustrated in Fig. 1.4. However, there are various other differences between these two control strategies. First, unlike GFLIs, most GFM control strategies described in the literature, are able to achieve synchronization with the grid without using a dedicated synchronization unit, but rather by implementing the power synchronization principle of SGs in their controller [12], [23]. This feature of self-synchronization, in combination with their voltage source behavior, makes GFMIs more suitable than GFLIs for IBRs connected in weak grids. However, studies have shown that the small-signal behavior of GFLIs under strong grid scenarios is superior to that of GFMIs [24], [25].

Another difference lies in their grid supporting response during a disturbance. It has already been mentioned that GFLIs can support the grid by regulating their power output with the use of additional control loops. However, this response is not inherent and may therefore be inefficient [15], due to control and measurement delays [21]. On the other hand, because a GFMI is designed to mimic the behavior of a SG, it can provide an intrinsic response to

<sup>&</sup>lt;sup>1</sup>The operating behavior of the inverter should not be confused with the term "Voltage Source Converter". Both GFMIs and GFLIs belong in the category of Voltage Source Converters, but the former is controlled to behave as a voltage source, while the latter is controlled to behave as a current source.

Figure 1.4: Modeling representation of grid-following and grid-forming inverters [12]

Table 1.1: Comparison of grid-following and grid-forming inverters

| Grid-following inverters                                                   | Grid-forming inverters                                                                          |

|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| Assumes that the PCC voltage is already formed                             | Forms its terminal voltage                                                                      |

| Operates as a current source                                               | Operates as a voltage source                                                                    |

| Uses a dedicated synchronization unit (e.g PLL) to synchronize to the grid | Doesn't need a PLL to synchronize to the grid (although some GFM control methods may use a PLL) |

| Cannot black start a system                                                | Can potentially black start a system                                                            |

| Cannot operate at 100% IBR penetration                                     | Can operate at 100% IBR penetration                                                             |

| Better performance in stiff grids                                          | Stable operation at low system strengths                                                        |

| No inherent inertia support (needs additional controllers)                 | Some GFM control methods (e.g filtered droop and VSG) can provide inherent inertia              |

disturbances, i.e., independent of additional measurements and control algorithms, and help enhance the stability of the system. Finally, GFMIs can operate at 100% IBR penetration, as well as potentially black start a system [16], since they form the voltage at their terminal, instead of relying on other units to create a well-regulated voltage to synchronize to [5]. Table 1.1 summarizes the key differences between grid-forming and grid-following inverters.

## 1.3 Overcurrent limiting for grid-forming inverters

## 1.3.1 The need for current-limiting methods for grid-forming inverters

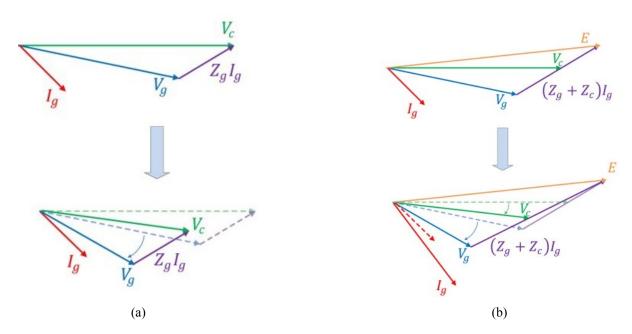

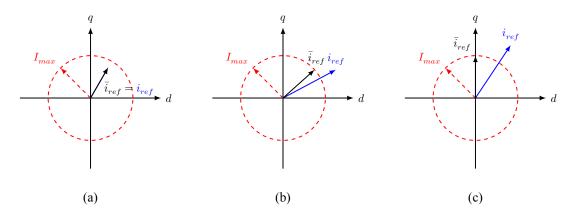

Since GFMIs and GFLIs operate as voltage and current sources respectively, their response to grid events can be significantly different, as illustrated in the phasor diagrams of Fig. 1.5. Referring to the simplified equivalent circuit of Fig. 1.4, where the upstream network is modeled as a Thevenin equivalent, when a disturbance causes the grid voltage phasor to change, the instantaneous response of a GFLI is to keep the current phasor unchanged. This occurs because the PLL must first re-synchronize with the grid voltage before feeding the new angle to the controller, which then determines the new current reference [12]. In contrast, due to its voltage source behavior, the instantaneous response of a GFMI is to maintain the internal voltage phasor constant, which leads to a change of the output current phasor [2], [12].

This inherent response to disturbances makes GFMIs very appealing for grid operators [26], as it is very similar to the behavior of SGs. However, it is evident that the output current

Figure 1.5: Phasor diagrams for a grid disturbance (a) Grid-following inverter; (b) Grid-forming inverter [12]

of GFMIs is very sensitive to grid conditions, because it is not directly controlled. Therefore, in the case of severe disturbances, such as a three-phase short circuit, if no action is taken, the output current of the GFMI will exceed the nominal. Unlike synchronous machines, which can withstand currents around 6-8 times their nominal for a certain amount of time, power electronic converters have a limited overcurrent capability, typically 1.2-2 pu, due to their semiconductor devices [21]. However, grid operators require that GFMIs remain connected and actively support the grid during faults, despite their inability to withstand overcurrent. A possible solution to this problem, is to over-dimension the converter components in order to be able to handle larger currents and better emulate the behavior of SGs, but it comes with a major financial cost [21]. Thus, to prevent unwanted tripping of GFMIs, proper overcurrent protection methods are essential, in order to avoid damage to the converter hardware and contribute to grid resilience during contingencies. For the aforementioned reasons, in recent years, the implementation of current-limiting control methods for GFMIs as well as their effect on the stability of the system, is gaining a lot of interest from academia and industry [27], [28].

## 1.3.2 Challenges of current-limiting methods for grid-forming inverters

Over the last years, a lot of current-limiting control methods for GFMIs have been proposed in the literature. A simple solution is to switch to GFL control when a fault is detected, which requires a back-up PLL and mode switching between synchronization methods [21], [23]. Due to the drawbacks associated with the use of a PLL and the fact that the fault response of GFLIs has been extensively studied [29], this method will not be discussed in this work. Otherwise, the basic GFM control structure is maintained and additional current-limiting control methods can be implemented, which operate only when necessary. When a disturbance leads to the triggering of the current limiter, the inverter is not able to maintain the internal voltage phasor constant, because the normal operation is superseded by the current limiter [27]. Therefore, the dynamic behavior of a GFMI during and after a severe disturbance is mainly determined by the utilized current-limiting control method. This implies that while the primary purpose of these methods

is to protect the inverter semiconductor devices, they also influence power system aspects, such as protection coordination, transient stability, voltage support etc [28].

To that end, an effective current limiting method should be designed to meet certain requirements concerning both the power system and the device itself. First, the current limiter should be able to protect the semiconductor devices from thermal breakdown, by quickly and accurately limiting the current magnitude, so it does not exceed the maximum allowable level. This should be achieved without introducing undesired harmonic components in the current and also without compromising the small-signal stability of the GFMI [28]. Additionally, the GFMI should be able to provide the appropriate fault-current contribution, depending on the type of the disturbance, as specified in grid codes [19]. For instance, the inverter should inject reactive current to the grid during voltage sags, or provide active phase-jump power. Also, the GFMI has to be capable of riding-through faults and restoring its normal operating condition after the faults are cleared [27]. This includes ensuring the transient stability of the converter, i.e., the ability to remain synchronized with the grid during and after a severe fault.

Due to the various system- and device-level requirements, the design of a single current-limiting method that meets all of them is a challenging task. Each of the current-limiting methods that have been proposed in the literature has its upsides and drawbacks. Recently, the effect of current-limiting methods on system aspects such as the reactive current profile of the GFMI during faults, and transient stability analysis and enhancement methods under current-limiting conditions, is gaining a lot of interest from researchers [30], [31], [32]. Nevertheless, many open issues and research questions remain. For instance, the transient stability analysis for systems with multiple GFMIs through the development of simplified models is a challenging issue [27]. Another vital issue which will require more research efforts, is the development of power system protection solutions that account for the behavior of GFMIs under various current-limiting methods, as well as the compatibility of current limiters with traditional protection schemes [28]. Overall, further research and development is essential to gain a deep understanding of the behavior of GFMIs during contingencies that drive them into current limitation, especially in the case of IBR-rich power systems.

## 1.4 Objective and structure of this thesis

## 1.4.1 Objective and scope of this thesis

The primary objective of this thesis is to analyze and understand the techniques by which current limitation is achieved in grid-forming inverters and to assess the effect of these methods on the transient stability of the inverter. To achieve this, a comprehensive review of grid-forming and current-limiting control methods is first presented. Additionally, the most commonly used methods are implemented and validated through both offline and real-time simulations. The simulation aims to provide a better understanding of the operating principles of these methods. The scope of this thesis is limited to the study of current-limiting methods for symmetrical faults and for two-level VSCs. Therefore, more complicated VSC topologies, as well as asymmetrical disturbances and unbalanced operating conditions are outside the scope of this work and will not be considered.

### 1.4.2 Structure of this thesis

The structure of this thesis is as follows:

Chapter 1 describes the transformation of the power grid from being dominated by synchronous machines to being dominated by inverter-based resources. It provides a brief overview of inverter based resources, highlighting the differences between the behavior of grid-forming and grid-following inverters. Then, the necessity of current-limiting methods for grid-forming inverters is underlined and the main challenges associated with these methods are presented.

Chapter 2 introduces the general system of a grid-forming inverter, followed by a comprehensive review of grid-forming and current-limiting control methods. The most frequently used methods are then implemented in the PLECS simulation software and time-domain simulations are performed, in order to validate their performance under various operating scenarios.

Chapter 3 studies the effect of current-limiting methods on the transient stability of the grid-forming inverter. First, the theoretical basis is established by presenting the large-signal models corresponding to the employed current-limiting method, along with the theoretical behavior of the grid-forming inverter during and after the fault. Then, time-domain simulations under various types of disturbances are carried out, to validate the large-signal models and the presented theoretical transient stability analysis.

Chapter 4 validates the effectiveness of the implemented current-limitation techniques under real-time conditions. It begins with a brief overview of real-time simulations, followed by the description of the real-time simulation setup. The implementation of the real-time simulation models and controllers is then presented and the differences from their offline simulation counterparts are highlighted. Finally, the real-time simulation results are shown.

Chapter 5 concludes the thesis, by summarizing the key points of each Chapter and discussing future work directions.

## Chapter 2

# Grid-forming inverters and currentlimiting methods

This Chapter provides an overview of various GFM control methods and current-limitation techniques that are commonly used in the literature. First, the general control structure of GFMIs is presented, followed by common GFM control methods. Then, the basic categories of current-limiting control methods are explained and the most frequently used methods from each category are described. The implementations of various GFM and current-limiting control methods in the PLECS simulation software are presented and time-domain simulations are performed to validate the controllers.

## 2.1 Grid-forming control methods

## 2.1.1 General control structure of grid-forming inverters

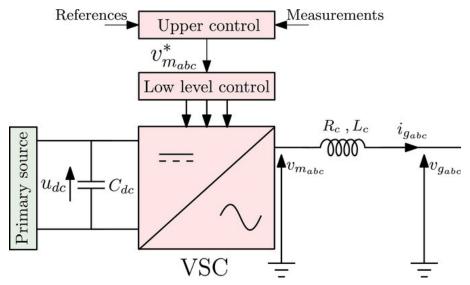

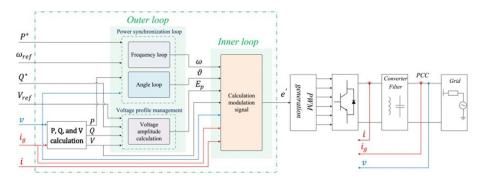

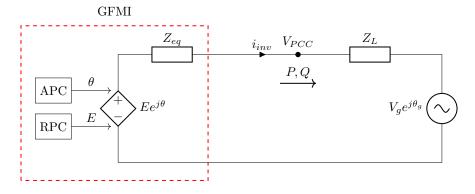

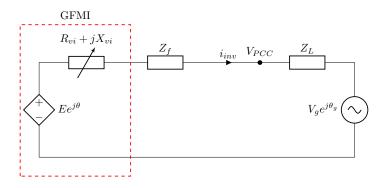

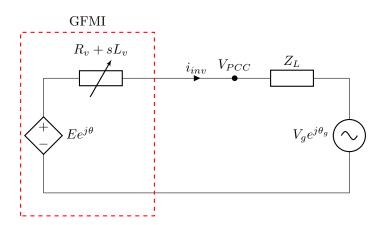

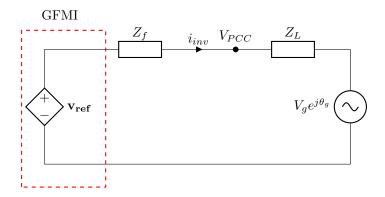

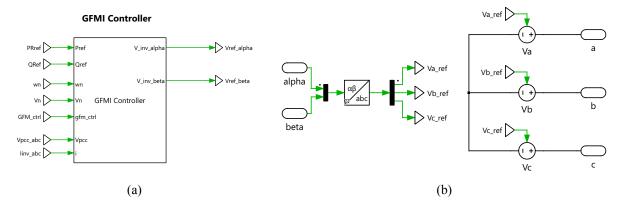

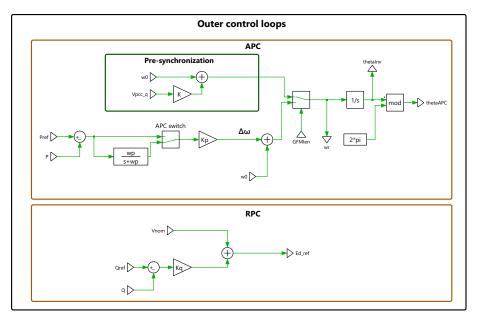

The most significant difference between the various GFM methods is their controller implementation. Despite the variety of GFM controls proposed in the literature, most of them can be represented by the general control structure of Fig. 2.1, where both the hardware and the software of a GFMI are shown. Regarding the hardware, the converter is connected to the grid (which is modeled as a Thevenin equivalent) though a filter, such as an LCL or a simple inductive filter. The purpose of this filter is to mitigate the harmonic distortion in currents and voltages caused by the switching behavior of the converter [21]. The inputs of the control system are the measured three-phase currents and voltages, as well as references for active/reactive power, frequency and voltage magnitude, and the output is the reference voltage that is fed to the PWM [12].

As shown in Fig. 2.1, a general control system of a typical GFMI consists of multiple subsystems and layers, which are responsible for different functionalities. For instance, the outmost layer, i.e., the outer loops, generate the characteristics of the voltage source reference, while the inner layer, i.e., the inner loops, are responsible for tracking this reference [21]. Due to the cascading structure of these layers, it is evident that in order to ensure the stability of the system, they have to operate at different time scales. More specifically, the outer loops are linked to the electromechanical transient dynamics, while the inner loops are associated with the electromagnetic transient behavior. [21].

The outer layer includes the power synchronization loop and the voltage profile management loop, which are responsible for synchronization with the grid and voltage regulation respectively. The power synchronization loop aims to regulate the active power

Figure 2.1: Generalized structure of a grid forming inverter [12]

output of the converter and it generates the angle/frequency of the internal voltage source (IVS) of the GFMI. This angle is also used for the transformation of measured three phase current and voltage to the dq reference frame. On the other hand, the voltage profile management loop is related to the reactive power output of the GFMI and it provides the magnitude of the IVS. This follows the traditional link of active power with angle/frequency and reactive power with voltage magnitude, which is valid in predominantly inductive grids, such as the high-voltage transmission system. In contrast, for a low X/R ratio there is coupling between reactive power and frequency. Thus, the voltage is regulated through the active power and the frequency is controlled through the reactive power [2]. Additionally, in the case of comparable inductive and resistive parts of the grid (i.e the X/R ratio is close to 1), the voltage and frequency are linked with both active and reactive power, which requires a different controller structure [2]. However, by applying virtual impedance methods, the line impedance seen from the inverter can be adjusted to have a high X/R ratio [2]. For this reason, and because the focus will mainly be on high-voltage applications, only the outer loop structure that is shown in Fig. 2.1 will be considered in this work.

The inner loops can include additional voltage and current controllers that regulate the capacitor voltage and the inverter current respectively. Note that the output of the outer layer is sufficient for implementing the voltage source behavior of GFMIs and can be fed directly to the PWM. Thus, the inner loops are optional and can be bypassed. However, the use of a current controller can include certain benefits, such as active damping of the voltage controller, as well as the capability of simpler implementations of current-limitation techniques [21]. Also, the absence of an AC voltage controller, can cause distortion in the voltage waveform, in case of unbalanced or non linear loads [21]. The control structure without inner loops, also referred to as open loop control, is seldom used in practice [21].

Finally, the control system of the GFMI includes additional control blocks responsible for coordinate transformations, calculation of output power and voltage/current magnitude based on the measurements provided etc. For example, the active and reactive power are calculated using the following equations:

$$P = 1.5(i_d V_{PCC,d} + i_q V_{PCC,q}) , (2.1)$$

$$Q = 1.5(i_d V_{PCC,q} - i_q V_{PCC,d}) . (2.2)$$

There exist various control methods for the implementation of each subsystem that is shown in Fig. 2.1. The combination of these methods leads to multiple GFM control methods, which differ in the implementation of power synchronization loop, voltage profile management loop and the inner loops. In the following sections, an overview of the most common methods used for each subsystem will be provided.

## 2.1.2 Outer control loops

## Power synchronization loop

The power synchronization loop (or Active Power Controller) generates the frequency and angle of the internal voltage source of the GFMI. Therefore, it is responsible for the synchronization of the converter with the grid [5]. Some of the most frequently used implementations of this control loop are described below.

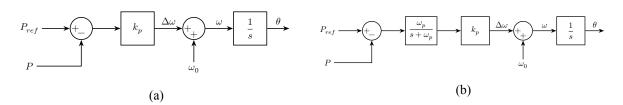

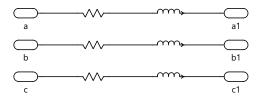

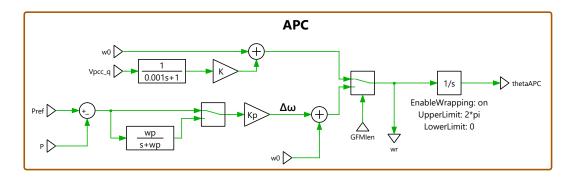

### Droop control

The first grid-forming control method used was the droop control, which was initially proposed to be used in isolated ac systems and uninterruptible power supplies [33]. This technique is inspired by the governor behavior, which allows the parallel operation of multiple SGs [2]. The droop controller calculates the frequency of the IVS as a linear function of the output active power, which is described by

$$\omega = \omega_0 + k_p (P_{ref} - P), \tag{2.3}$$

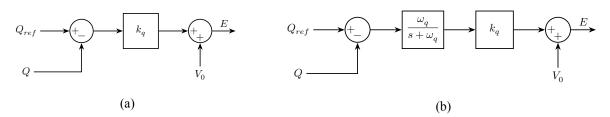

where  $k_p$  is the droop coefficient,  $\omega_0$  is the nominal angular frequency,  $P_{ref}$  is the active power set-point, and P is the measured instantaneous active power. The angle of the IVS is then calculated by integrating the frequency, as shown in the block diagram of Fig. 2.2a.

Despite being the simplest implementation of the Active Power Controller (APC), the droop control is highly effective and is able to synchronize without the need of other synchronization units under normal operating conditions [12].

As indicated in (2.3), a deviation of the instantaneous active power from its set-point will cause a step change in the frequency of the IVS of the GFMI [34]. Therefore, the droop controller does not provide inertia support, which is one of the main shortcomings of this method [2].

To mitigate fluctuations from the active power measurement, the droop controller can be equipped with a low pass filter (LPF) as shown in Fig. 2.2b. In this case, the equation describing the active power controller becomes

$$\omega = \omega_0 + k_p \frac{\omega_p}{s + \omega_p} \left( P_{ref} - P \right), \tag{2.4}$$

with  $\omega_p$  being the cut-off frequency of the LPF.

Figure 2.2: Block diagram of (a) Active power droop controller; (b) Active power droop controller with LPF

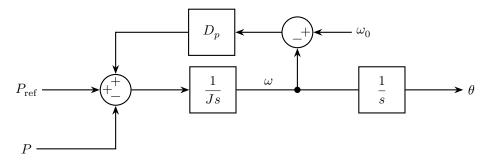

### Virtual synchronous generator

To address the decrease of inertia in future power systems and to better emulate the behavior of synchronous generators, the virtual synchronous generator (VSG) method was proposed [35], [36]. A simple approach to provide virtual inertia, is to implement the swing

equation of synchronous machines in the control of GFMIs [21]. To that end, the control function that generates the frequency of the IVS for the VSG method is the following [37]

$$\omega = \frac{1}{Js} \left( P_{ref} - P + D_p(\omega_0 - \omega) \right), \tag{2.5}$$

where  $D_p$  is the droop coefficient (or damping factor) and J is the virtual moment of inertia. Fig. 2.3 shows the block diagram of the Active Power Controller of a VSG.

Figure 2.3: Block diagram of the Virtual Synchronous Generator

It has been shown in [38], that the droop controller with the low-pass filter is equivalent to the VSG, thus making it a specific case of a VSG. Therefore, although the initial purpose of the low-pass filter was to mitigate fluctuations in the measured active power, it also provides virtual inertia to the GFMI.

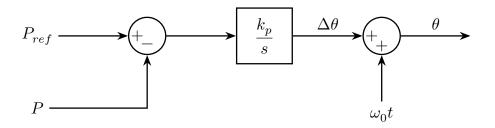

## Power synchronization control

The concept of power synchronization control (PSC) was proposed in [23] for a VSC-HVDC system, to provide voltage support when connected to a weak grid. The synchronization principle used in this method is similar to the operation of synchronous machines. The equation that describes the synchronization loop of the PSC is

$$\theta = \omega_0 t + k_p \int (P_{ref} - P), \tag{2.6}$$

where  $k_p$  is the controller gain. The block diagram of this control loop is given in Fig. 2.4. Taking the derivative of both sides in the above equation gives

$$\frac{d\theta}{dt} = \omega = \omega_0 + k_p (P_{ref} - P). \tag{2.7}$$

Figure 2.4: Block diagram of the power synchronization control

Comparing (2.7) and (2.3) as well as Fig. 2.2a and Fig. 2.4, it becomes evident that droop control and PSC are mathematically equivalent, despite being initially developed for different

applications. Therefore, PSC can be considered to be a specific version of the droop controller. Note that despite the fact that the PSC is able to synchronize with the grid without the use of a PLL, in case of faults the converter switches to GFL control using a backup PLL [23].

#### Other control methods

Another control method that was proposed to allow parallel operation of converters is the virtual oscillator control [39]. Unlike the other methods presented, the virtual oscillator control is not based on the operating principle of synchronous machines, but is rather inspired by the phenomenon of synchronization in networks of coupled oscillators. This method offers the benefits of faster synchronization and improved overall stability [21].

Additionally, a dc-link voltage controller that enables synchronization and dc-link voltage regulation is proposed in [40]. This method is referred to as ViSynC and it allows GFMIs to exhibit power-frequency characteristics similar to those of synchronous machines. Also with the use of certain control parameters, the damping and inertia can be tuned in a way that the dc link voltage remains in the acceptable range.

#### Voltage profile management loop

The voltage profile management loop (or Reactive Power Controller) is responsible for the calculation of the magnitude of the GFMI internal voltage source. Some of the methods proposed in the literature are presented below.

## Droop control

Similar to the APC, the droop controller can be used in the Reactive Power Controller (RPC) as well. In this case, the magnitude of the IVS is calculated as a linear function of the reactive power output, which is described by [2]

$$E = V_0 + k_q (Q_{ref} - Q), (2.8)$$

where  $k_q$  is the droop coefficient,  $V_0$  is the nominal voltage,  $Q_{ref}$  is the reactive power set point and Q is the measured reactive power output.

In analogy with the active power droop control, a low-pass filter can be used to mitigate fluctuations of the measured reactive power [37]. Then the control function becomes

$$E = V_0 + k_q \frac{\omega_q}{s + \omega_q} \left( Q_{ref} - Q \right), \tag{2.9}$$

with  $\omega_q$  being the cut-off frequency of the LPF. The block diagrams of the reactive power droop controller with and without low-pass filter are shown in Fig. 2.5.

Figure 2.5: Block diagram for (a) Reactive power droop controller; (b) Reactive power droop controller with LPF

### PI-based voltage control

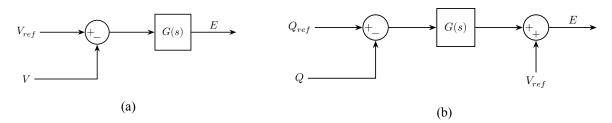

Another control method proposed for the voltage profile management loop is using a PI controller, which controls the magnitude of the measured PCC voltage to track its reference value [41]. This method was proposed for a STATCOM operating as a Virtual Synchronous Machine. The control function is the following:

$$E = (V_{ref} - V)G(s) \tag{2.10}$$

where  $V_{ref}$  is the reference voltage magnitude, V is the measured PCC voltage magnitude and G(s) is the transfer function of the PI controller. The transfer function of a basic PI controller is

$$G(s) = k_p + \frac{k_i}{s},\tag{2.11}$$

with  $k_p$  and  $k_i$  being the proportional and integral gain of the PI controller, respectively.

### PI-based reactive power control

Another PI-based control method, is the control of the reactive power output to follow its set-point, by utilizing a PI controller and an additional term for the feedforward of the voltage reference [12], [42]. The control function is

$$E = V_{ref} + (Q_{ref} - Q)G(s), (2.12)$$

with G(s) being the transfer function of the PI controller. The block diagram of the PI-based voltage and reactive power control is shown in Figures 2.6a and 2.6b respectively.

Figure 2.6: Block diagram of the (a) PI-based voltage controller; (b) PI-based reactive power controller [12]

### Other control methods

In addition to the control methods presented above, cascaded control structures including both PI-based and droop controllers have been proposed. For instance, in [23] the first (outer) layer is a PI controller regulating the reactive power, similar to the above, and the second (inner) layer is an Alternating Voltage Controller with a droop characteristic. Another popular implementation consists of a droop controller for the voltage difference in the first layer and then a PI controller regulating the reactive power in the second layer [12], [43].

## 2.1.3 Inner control loops

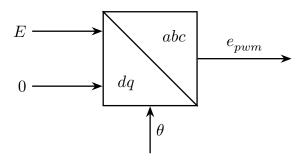

As it was previously explained, the GFMI synchronizes with the grid via the power synchronization loop, which generates the angle reference and the voltage profile management loop provides the magnitude of the IVS. Additional inner loops can be used for current limitation, voltage control, power-quality enhancement etc [21]. As shown in Fig. 2.1 the output of the inner loops is the reference voltage, which is then normalized (multiplied by

$2/V_{dc}$ ) and fed to the modulation. Various inner-loop implementations have been proposed in the literature, some of which are presented below.

## Direct voltage synthesis

The most straight-forward approach is to directly feed the output of the outer loops to the PWM [44]. Because the angle generated by the APC is used for coordinate transformations, the synchronous reference frame is aligned with the internal voltage source of the GFMI. Thus, the q-axis component of the IVS is zero, while the d-axis component is equal to the magnitude of the IVS, as provided by the voltage profile management loop. The direct voltage synthesis or open loop control is shown in Fig. 2.7. Despite having the benefit of simple implementation, this method lacks controllability over both the current and output voltage (i.e., after the filter impedance) of the GFMI. As a result, the output voltage cannot be maintained at its nominal value under different power generation scenarios and the GFMI may also suffer from overcurrent during faults [21].

Figure 2.7: Illustration of the open loop control

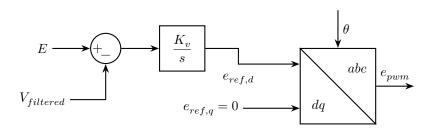

### Single-loop voltage magnitude control

The single-loop voltage magnitude (SLVM) control uses an integrator to regulate the output voltage amplitude to track the reference provided by the voltage profile management loop [21]. Fig. 2.8 shows the implementation of the SLVM control, where an LPF is used to suppress high-frequency noise in the measured output-voltage magnitude. Unlike the open-loop control, the output-voltage magnitude can be maintained at the nominal value during different power generation scenarios, due to the use of the integrator [21]. However, because of its typically low bandwidth, the SLVM exhibits similar dynamics with the open-loop control across a wide frequency range [21], [45]. Despite the output voltage amplitude control of the SLVM, it still lacks current controllability and thus it may also suffer from overcurrent during faults, if no additional current limiting techniques are used.

Figure 2.8: Illustration of the single loop voltage magnitude control

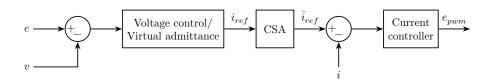

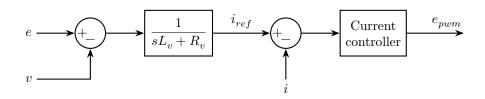

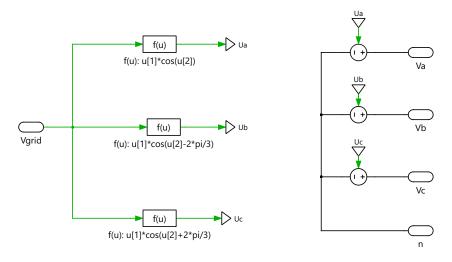

### Dual-loop vector voltage current control

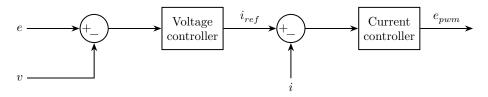

To address the lack of current controllability in the previous methods, a dual-loop voltage and current control is often used, which consists of a voltage controller in the first (outer) layer, followed by a current controller in the second (inner) layer [12]. The output of the current controller is the reference voltage fed to the PWM, as shown in the general block diagram of Fig. 2.9. The voltage and current controllers can either be implemented in the  $\alpha\beta$  or dq frame, using PR (Proportional+Resonant) or PI controllers respectively. The use of the current controller allows for easier implementation of current limiting methods.

Figure 2.9: General block diagram of the dual-loop vector voltage current control

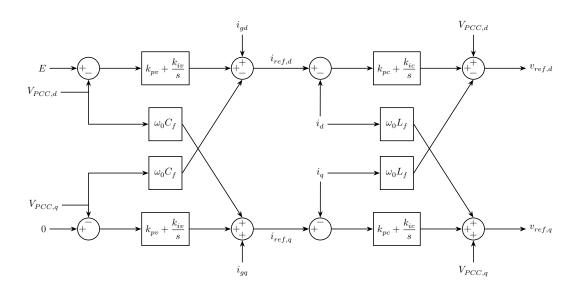

Fig. 2.10 shows the implementation of the dual-loop vector voltage current control in the dq reference frame, which consists of four PI controllers, two for each component of the voltage and current. Additionally, coupling terms and disturbances (such as  $\omega_0 L_f i_{dq}$ ,  $\omega_0 C_f V_{PCC,dq}$  and  $i_{g,dq}$ ,  $V_{PCC,dq}$ ) are compensated with the appropriate decoupling and feedforward terms [15].

Figure 2.10: Implementation of the dual-loop vector voltage current control in the dq-frame

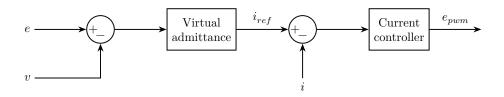

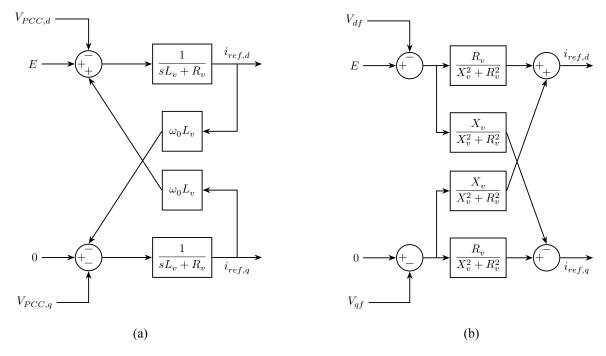

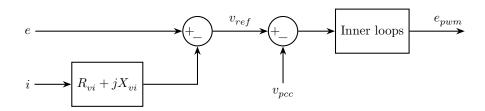

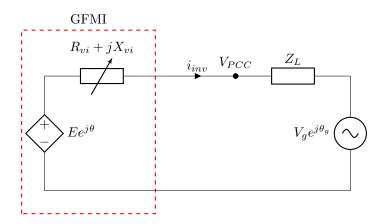

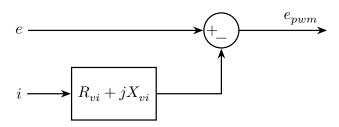

### Virtual admittance control