National Technical University of Athens School of Electrical and Computer Engineering Division of Information Transmission Systems and Material Technology

# Design and Manufacturing of an RF Power Amplifier for linear accelerators

# **Diploma Thesis**

Panagiotis Vlachos

Supervisor: Athanasios Panagopoulos,

Professor, National Technical University of Athens

Athens, October, 2025

National Technical University of Athens School of Electrical and Computer Engineering Division of Information Transmission Systems and Material Technology

# Design and Manufacturing of an RF Power Amplifier for linear accelerators

# **Diploma Thesis**

#### Panagiotis Vlachos

Supervisor: Athanasios Panagopoulos,

Professor, National Technical University of Athens

Approved by the three-member scientific committee on the 20 October 2025

Athanasios Panagopoulos Hercules Avramopoulos Dimitrios Apostolopoul

Athanasios Panagopoulos Professor, NTUA Hercules Avramopoulos Professor, NTUA Dimitrios Apostolopoulos Assistant Professor, NTUA

Athens, October, 2025

## **Panagiotis Vlachos**

Graduate of School of Electrical and Computer Engineering, National Technical University of Athens

# Copyright © Panagiotis Vlachos, 2025

All rights reserved.

You may not copy, reproduce, distribute, publish, display, modify, create derivative works, transmit, or in any way exploit this thesis or part of it for commercial purposes. You may reproduce, store or distribute this thesis for non-profit educational or research purposes, provided that the source is cited, and the present copyright notice is retained. Inquiries for commercial use should be addressed to the original author.

The ideas and conclusions presented in this paper are the author's and do not necessarily reflect the official views of the National Technical University of Athens, the European Spallation Source and of Uppsala University.

## Περίληψη

Η Ευρωπαϊκή Πηγή Σκέδασης Νετρονίων (ESS) είναι μια διεπιστημονική ερευνητική εγκατάσταση που κατασκευάζεται στο Λουντ της Σουηδίας και θα είναι ο πιο ισχυρός γραμμικός επιταχυντής πρωτονίων που έχει κατασκευαστεί ποτέ όταν ολοκληρωθεί η κατασκευή. Παρόλο που το ESS θα συμβάλει σημαντικά στη μελλοντική έρευνα, η εγκατάσταση θα είναι ένας μεγάλος καταναλωτής ενέργειας με σημαντικό περιβαλλοντικό αντίκτυπο. Επομένως, πραγματοποιούνται περιβαλλοντικά βιώσιμες εξελίξεις με στόχο την υιοθέτηση βελτιωμένων ενεργειακά αποδοτικών προσεγγίσεων. Ένα παράδειγμα αυτής της προσέγγισης θα είναι το νέο σύστημα που θα εφαρμοστεί για την τροφοδοσία 26 κοιλοτήτων spoke. Οι κοιλότητες Spoke είναι το πρώτο στάδιο της υπεραγώγιμης επιτάχυνσης στον γραμμικό επιταχυντή (LINAC) του ESS, αποτελούμενοι από 26 διπλές κοιλότητες spoke, με απαίτηση ισχύος 400kW ανά θάλαμο για να λειτουργήσουν. Το νέο σύστημα είναι ένας Ενισχυτής Ισχύος Στερεάς Κατάστασης (SSPA) που θα αντικαταστήσει τους ενισχυτές τετρόδου λόγω της υψηλής κατανάλωσης ισχύος τους.

Αυτή η διπλωματική εργασία επικεντρώνεται στον σχεδιασμό, προσομοίωση και κατασκευή ενός Ενισχυτή Στερεάς Κατάστασης (SSPA) ειδικά προσαρμοσμένου ώστε να λειτουργεί ως το πρώτο στάδιο του οδηγού μέσα στο σύστημα των 400kW SSPA που θα εγκατασταθεί για να τροφοδοτεί τις υπεραγώγιμες διπλές κοιλότητες spoke στην Ευρωπαϊκή Πηγή Σκέδασης Νετρονίων. Αυτή η μελέτη ξεκινά με μια εις βάθος ανάλυση των απαιτήσεων του συστήματος και των λειτουργικών παραμέτρων ολόκληρου του συστήματος, εντοπίζοντας βασικές μετρικές απόδοσης όπως η ισχύς εξόδου, η γραμμικότητα και η αποδοτικότητα. Μέσα από εντατική προσομοίωση και βελτιστοποίηση με τη χρήση λογισμικών εργαλείων (Advanced Design System (ADS) και Altium Designer), αναπτύσσεται μια αρχιτεκτονική SSPA, ικανή να ικανοποιήσει τις αυστηρές προδιαγραφές που απαιτεί η εφαρμογή ενώ μετριάζει ζητήματα όπως η αρμονική παραμόρφωση και η απαγωγή ισγύος. Ιδιαίτερη προσοχή δίνεται στην επιλογή και ολοκλήρωση τρανζίστορ, δικτύων προσαρμογής εμπέδησης και συστημάτων ψύξης ώστε να διασφαλιστεί η βέλτιστη λειτουργικότητα και μακροζωία υπό μεταβαλλόμενες συνθήκες λειτουργίας. Επιπλέον, πραγματοποιείται πειραματική επικύρωση του σχεδιασμένου πρωτοτύπου SSPA, η οποία περιλαμβάνει ολοκληρωμένες δοκιμές και χαρακτηρισμό σε όλο το εύρος λειτουργίας. Οι μετρικές απόδοσης, συμπεριλαμβανομένων της ισχύος εξόδου, της αποδοτικότητας, της απόκρισης συχνότητας και της γραμμικότητας, αξιολογούνται διεξοδικά, αποδεικνύοντας την αποτελεσματικότητα και αξιοπιστία του προτεινόμενου σχεδιασμού.

**Λέξεις Κλειδιά:** Γραμμικός Επιταχυντής, ESS, Στερεά Κατάσταση, Ενισχυτής Ισχύος, ραδιοσυχνότητα, spoke κοιλότητα, διάταξη τυπωμένου κυκλώματος, κατασκευή, μετρήσεις, LDMOS, μικροταινία, πυρηνική φυσική

### **Abstract**

The European Spallation Source (ESS) is a multidisciplinary research facility that is being built in Lund, Sweden and is the most powerful linear proton accelerator ever built. Even though ESS will contribute greatly to the future research, the facility will be a large power consumer with significant environmental impact. Therefore, environmentally- sustainable developments are undertaken towards the adoption of energy savings and improved energy-efficient approaches. One example of that approach will be the new system that will be implemented to power 26 spoke cavities. The Spoke cavities are the first stage of superconducting acceleration at the ESS linear accelerator (LINAC), consisted of 26 double spoke cavities, with 400kW power per cavity requirement to operate. The new system is a Solid-State Power Amplifier (SSPA) that will replace the tetrode amplifiers due to their high-power consumption.

This thesis focuses on designing, simulating and manufacturing a Solid-State Power Amplifier (SSPA) tailored specifically to serve as the first stage of the driver within the 400kW SSPA system that will be installed to power the superconducting double spoke cavities at European Spallation Source. This study begins with an in-depth analysis of the system requirements and operational parameters of the entire system, identifying key performance metrics such as output power, linearity and efficiency. Through rigorous simulation and optimization using software tools (Advanced Design System (ADS) and Altium Designer), a robust SSPA architecture is developed, capable of meeting the stringent specifications demanded by the application while mitigating issues such as harmonic distortion and power dissipation. Special attention is given to the selection and integration of high-power transistors, impedance matching networks, and cooling systems to ensure optimal functionality and longevity under varying operating conditions. Furthermore, experimental validation of the designed SSPA prototype is conducted, involving comprehensive testing and characterization across the entire operational range. Performance metrics including output power, efficiency, frequency response, and linearity are thoroughly evaluated, demonstrating the efficacy and reliability of the proposed design.

**Key Words:** Linear Accelerator, ESS, Solid-State, Power Amplifier, Radio Frequency, spoke cavities, layout, manufacturing, measurements, LDMOS, microstrip, nuclear physics

## Acknowledgements

With this thesis, I complete my five-year studies at the School of Electrical and Computer Engineering of the National Technical University of Athens. These years form the foundation of my life from this point onward. The person I have become during this time, not only academically, but also personally, is shaped by scientific thinking and perseverance. These studies will remain the solid ground upon which I will continue to build, nurture, and cultivate future opportunities and a life of fulfillment and happiness.

I would first like to express my sincere gratitude to Professor Athanasios Panagopoulos, my thesis advisor, for his continuous guidance, trust, and the numerous discussions we had throughout his courses. His teaching reflects his genuine dedication to cultivating engineers with critical thinking skills and a strong foundation of knowledge. Through his instruction, together with that of Emeritus Professor Panagiotis Cottis, I became truly fascinated by the field of telecommunications engineering and was able to find my academic identity. Attending their lectures was always something I looked forward to and deeply enjoyed. I will always be grateful for having been their student.

I would also like to thank the other members of my thesis committee, Professor Hercules Avramopoulos and Assistant Professor Dimitrios Apostolopoulos, for their support during the preparation of this thesis and for the valuable knowledge I gained through their courses.

Special thanks are due to the RF Sources Group at the European Spallation Source (ESS) for offering me the opportunity to work in such an inspiring and challenging environment. I would particularly like to thank Morten Jensen, RF Group Leader, for his supportive and guiding role, Bruno Lagoguez, RF Engineer, for our collaboration and valuable discussions; and Slavisa Micic, Electronics Engineer, for the technical insights and the many laughs we shared while soldering. My sincere appreciation also goes to all the other members of the RF group who made my stay at ESS both educational and memorable.

My time in Lund, Sweden, played a decisive role in my development as both an engineer and a person. I am deeply thankful to Emmanouil Trachanas, Accelerator Electrical Engineer, for his support during my stay in Sweden and for stepping up as a true role model, a source of professionalism, integrity, and kindness that continues to inspire me.

To my family, thank you for your support, patience, and belief in me throughout these years. To my grandmother, whose dream of studying nuclear physics continues to live through me, this work is as much yours as it is mine.

Finally, I wish to warmly thank my friends and all those I met during my academic years for their friendship, laughter, and shared experiences, as well as everyone I encountered in Lund and at ESS, the place where my life, both personal and scientific, truly began.

Panagiotis Vlachos Athens, October 2025

# **Table of Contents**

| Εκτενή Περίληψη στα Ελληνικά/ Extensive Summary in Greek        | 18 |

|-----------------------------------------------------------------|----|

| Chapter 1: Introduction                                         | 34 |

| 1 Introduction                                                  | 34 |

| 1.1 Scope                                                       | 34 |

| 1.2 The European Spallation Source                              | 34 |

| 1.3 Motivation                                                  | 36 |

| 1.4 Objectives                                                  | 37 |

| Chapter 2: Theoretical background                               | 38 |

| 2 Introduction                                                  | 38 |

| 2.1 The ESS linear accelerator                                  | 38 |

| 2.2 Microwave theory                                            | 43 |

| 2.2.1 S parameters                                              | 43 |

| 2.2.2 Transmission lines                                        | 44 |

| 2.2.3 Planar waveguides                                         | 47 |

| 2.2.4 Microstrip discontinuities modelling                      | 56 |

| 2.2.5 Stability                                                 | 58 |

| 2.3 Power Amplifiers                                            | 60 |

| 2.3.1 MOS and LDMOS Transistors                                 | 60 |

| 2.3.2 RF Power Definitions                                      | 62 |

| 2.3.3 Classes of Operation (A, B, AB)                           | 64 |

| 2.3.4 Power Amplifiers Applications in Accelerators             | 65 |

| Chapter 3: System description of 400kW SSPA                     | 67 |

| 3 Introduction                                                  | 67 |

| 3.1 Overview                                                    | 67 |

| 3.2 Input block                                                 | 68 |

| 3.3 Driver stage                                                | 69 |

| 3.4 Main amplifier                                              | 70 |

| 3.5 Output block                                                | 70 |

| 3.6 Monitoring systems, cooling systems and Supporting hardware | 71 |

| 3.7 Summary                                                     | 71 |

| Chapter 4: Designing Driver's 1st stage schematic               | 72 |

| 4 Introduction                                                  | 72 |

| 4.1 Transistor choice                                 | 72  |

|-------------------------------------------------------|-----|

| 4.1.1 Material Choice                                 | 72  |

| 4.1.2 Device choice                                   | 73  |

| 4.2 DC Simulations and Bias optimization              | 75  |

| 4.2.1 Gate Bias                                       | 75  |

| 4.2.2 Drain Bias                                      | 77  |

| 4.3 Bias networks and Behavior of real components     | 81  |

| 4.3.1 Bias networks topology                          | 81  |

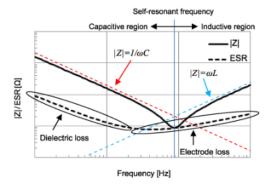

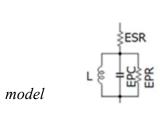

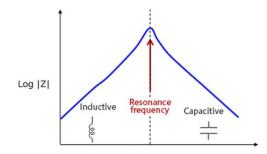

| 4.3.2 Behavior of real components                     | 82  |

| 4.3.3 Decoupling                                      | 84  |

| 4.3.4 RF Choke                                        | 87  |

| 4.3.5 Coupling                                        | 90  |

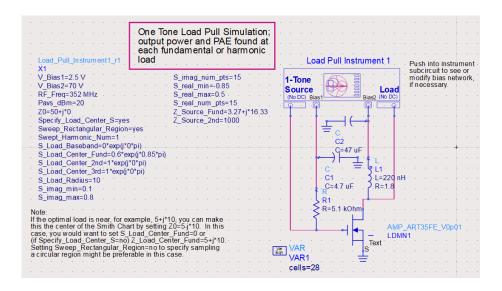

| 4.4 Load pull simulations                             | 90  |

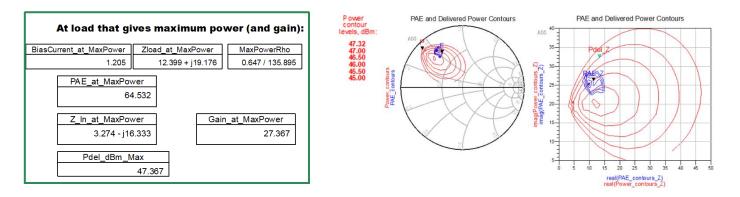

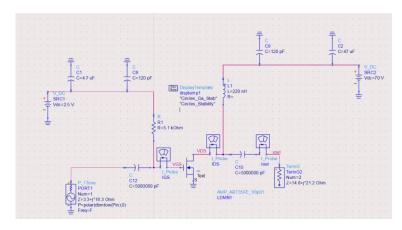

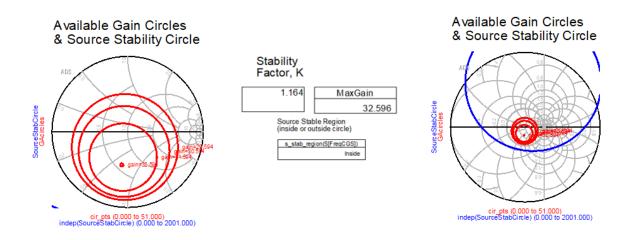

| 4.5 Stability                                         | 91  |

| 4.6 Summary                                           | 94  |

| Chapter 5: SSPA Driver's 1st stage Layout Development | 95  |

| 5 Introduction                                        | 95  |

| 5.1 Material choice                                   | 95  |

| 5.2 Transmission lines                                | 96  |

| 5.2.1 Trasmissioin line technology                    | 96  |

| 5.2.2 Dimensions of Microstrip and Current Handling   | 97  |

| 5.2.3 Transistor placement                            | 98  |

| 5.2.4 Connectors                                      | 100 |

| 5.3 Matching networks                                 | 100 |

| 5.3.1 1 <sup>st</sup> iteration                       | 101 |

| 5.3.2 2 <sup>nd</sup> iteration                       | 103 |

| 5.3.3 3 <sup>rd</sup> iteration                       | 109 |

| 5.3.4 4 <sup>th</sup> iteration                       | 110 |

| 5.3.5 5 <sup>th</sup> iteration                       | 111 |

| 5.4 Heatsink design                                   | 112 |

| 5.5 Simulation of layout                              | 114 |

| 5.6 Summary                                           | 119 |

| Chapter 6: SSPA Manufacturing and Testing             | 121 |

| 6 Introduction                     | 121 |

|------------------------------------|-----|

| 6.1 Gerber file and PCB Production | 121 |

| 6.2 Soldering and Assembly         | 124 |

| 6.3 Manufacturing non-idealities   | 128 |

| 6.4 Specifications                 | 130 |

| 6.5 Lab preparation                | 132 |

| 6.5.1 Equipment                    | 132 |

| 6.5.2 Bench Setup                  | 135 |

| 6.6 Measurements                   | 141 |

| 6.7 Summary                        | 163 |

| Chapter 7: Conclusion              | 167 |

| 7.1 Summary                        | 167 |

| 7.2 Next steps                     | 168 |

| 7.3 The Road Ahead                 | 169 |

| References                         | 170 |

| Appendices                         | 173 |

# **List of Figures**

| Figure 1.1: The ESS campus                                                                   | 34   |

|----------------------------------------------------------------------------------------------|------|

| Figure 1.2: Amplification topologies                                                         | 36   |

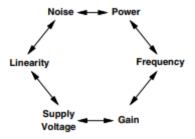

| Figure 1.3: RF design trade-offs                                                             | 37   |

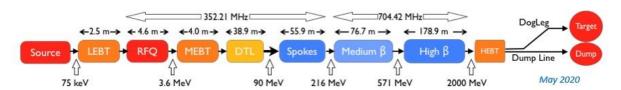

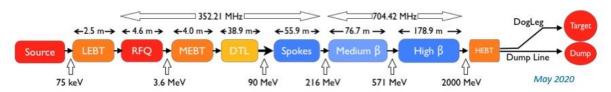

| Figure 2.1: The ESS linac schematic as of May 2020[6]                                        | 38   |

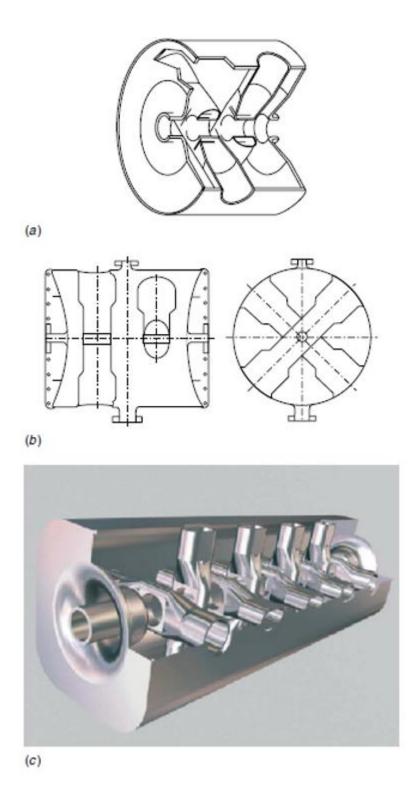

| Figure 2. 2: Spoke cavities examples[7]                                                      | 40   |

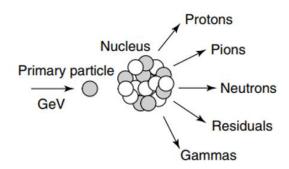

| Figure 2. 3: Generalized possible particle of a particle-nucleus interaction in the GeV ener | gy   |

| range [8]                                                                                    | 41   |

| Figure 2. 4: 2-port network                                                                  | 43   |

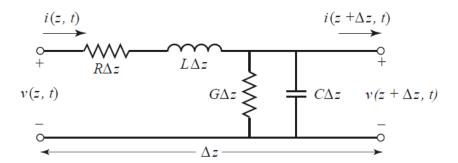

| Figure 2. 5:Voltage and current definitions and equivalent circuit for an incremental lengtl | h of |

| transmission line, ([10] page 49)                                                            | 44   |

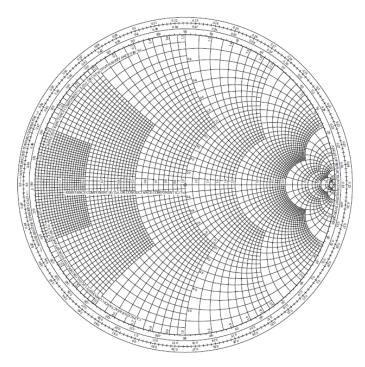

| Figure 2.6: The Smith chart                                                                  | 47   |

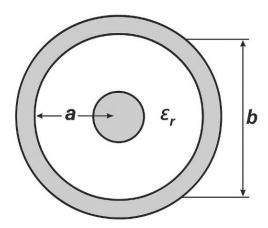

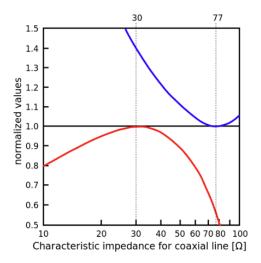

| Figure 2.7: Cross section of a coaxial transmission line                                     | 48   |

| Figure 2.8: Normalized attenuation and power-handling characteristics of an air-filled coa   |      |

| line as a function of characteristic impedance                                               | 52   |

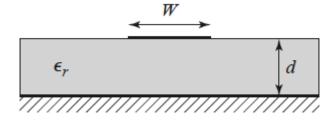

| Figure 2. 9: Geometry of a microstrip transmission line                                      | 52   |

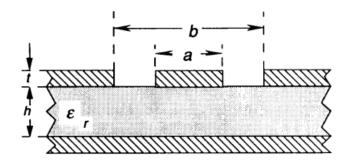

| Figure 2. 10: Geometry of a coplanar waveguide[11]                                           | 55   |

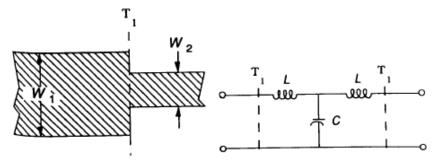

| Figure 2.11: Microstrip line step (abrupt change in width) and equivalent circuit            | 56   |

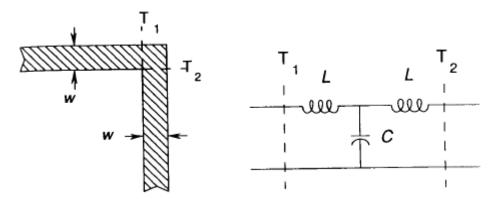

| Figure 2.12: Microstrip line right-angle bend and equivalent circuit                         |      |

| Figure 2. 13:LDMOS diagram[12]                                                               | 60   |

| Figure 2.14: Amplifier operating regions                                                     |      |

| Figure 2. 15: Amplifier classes of operation[13]                                             |      |

| Figure 3.1: Block diagram of the 400kW SSPA system                                           | 67   |

| Figure 3.2: Power per stage estimation of the 400kW SSPA system                              | 68   |

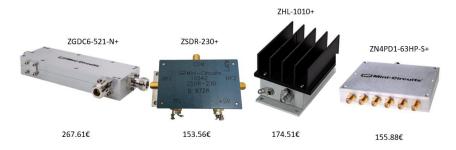

| Figure 3.3: List of components with manufacturer reference and price for Input block         | 68   |

| Figure 3. 4: List of components with manufacturer reference and price for Driver's block     | 69   |

| Figure 3.5: Driver's 1st stage                                                               | 70   |

| Figure 3.6: Driver's 2nd stage                                                               | 70   |

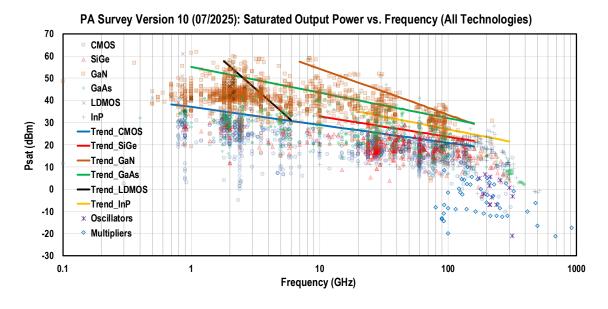

| Figure 4.2: Comparison of Semiconductor Technologies for Different Materials                 | 72   |

| Figure 4.3: Gain and Drain Efficiency as a function of output power[7]                       | 74   |

| Figure 4.4: ART35FE picture                                                                  | 74   |

| Figure 4.5: Recommended amplification line-up by Ampleon                                     | 74   |

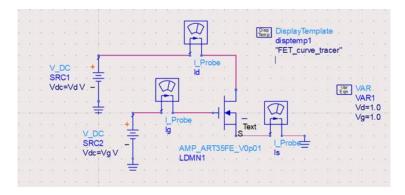

| Figure 4.6: Circuit topology simulated on ADS for DC curves                                  |      |

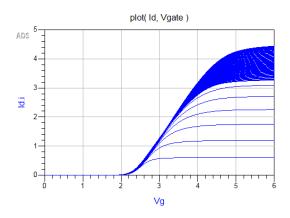

| Figure 4.7: Drain current as a function of Gate voltage                                      |      |

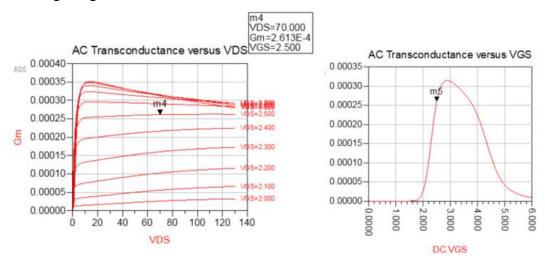

| Figure 4.8: AC Transconductance a function of Drain-Source and Gate-Source Voltage           |      |

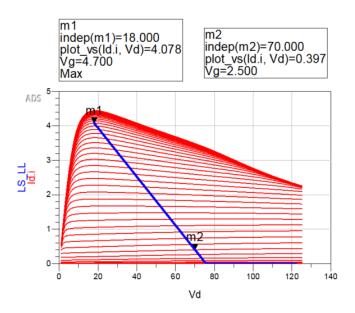

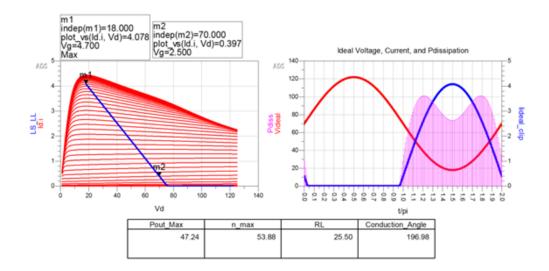

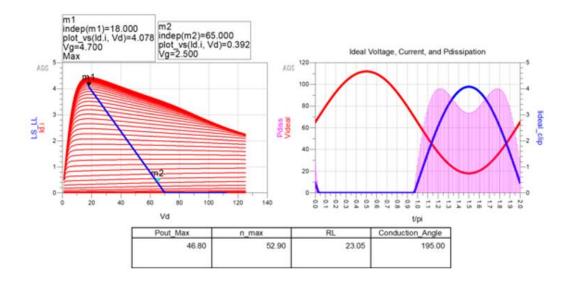

| Figure 4.9: Drain current as a function of Drain-Source voltage and the load-line selected.  |      |

| Figure 4.10: Circuit simulated for steady load and current-voltage plot                      |      |

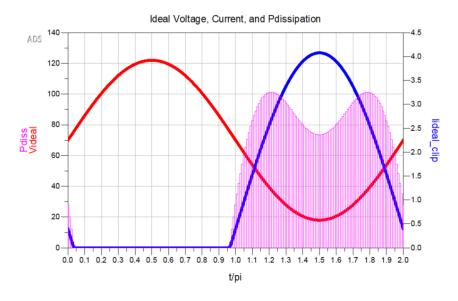

| Figure 4.11: I-V curves, load-lines and voltage, current and power waveforms for different | ıt   |

|--------------------------------------------------------------------------------------------|------|

| load values with tables of output power, efficiency, load and conduction angle             | 79   |

| Figure 4.12: Voltage, current and power waveforms for optimal load                         | 79   |

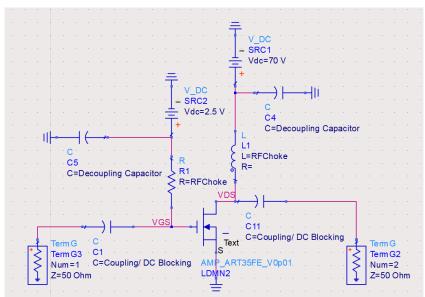

| Figure 4.13: Circuit topology of Bias networks on ADS                                      | 81   |

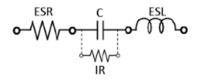

| Figure 4. 14: Ideal capacitor                                                              | 82   |

| Figure 4.15:Real capacitor Frequency-Impedance dependency                                  | 82   |

| Figure 4.16: Real capacitor circuit equivalent model                                       | 82   |

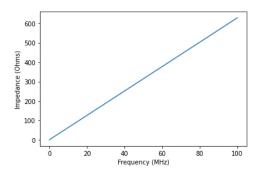

| Figure 4.17: Ideal Inductor Frequency-Impedance dependency                                 | 83   |

| Figure 4. 18:Real capacitor Frequency-Impedance dependency                                 | 83   |

| Figure 4. 19: Ideal Inductor circuit equivalent                                            |      |

| Figure 4.20: Picture of Bias capacitor CAA573X7S2A476M640LH                                |      |

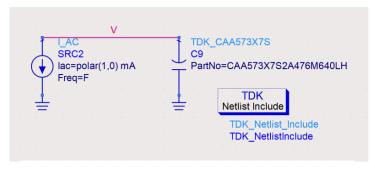

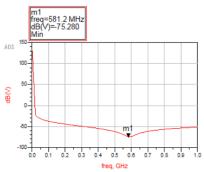

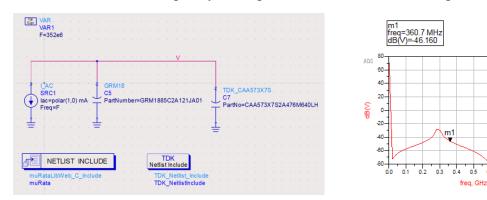

| Figure 4.21: Circuit simulated and frequency response of CAA573X7S2A476M640LH              | 84   |

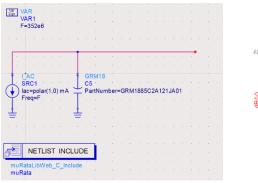

| Figure 4.22: Picture of bias capacitor GRM1885C2A121JA01                                   | 85   |

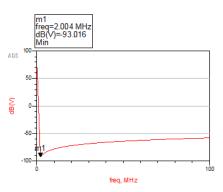

| Figure 4.23: Circuit simulated and frequency response of GRM1885C2A121JA01                 | 85   |

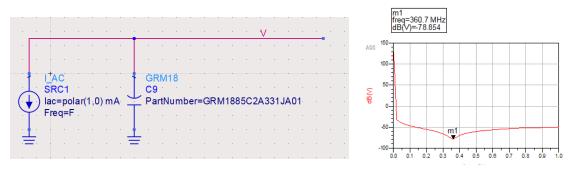

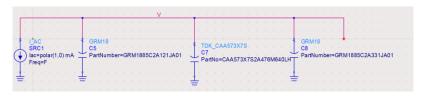

| Figure 4.24: Circuit simulated and frequency response of 2 Bias capacitors                 | 86   |

| Figure 4.25: Picture of Bias capacitor GRM1885C2A331JA01                                   | 86   |

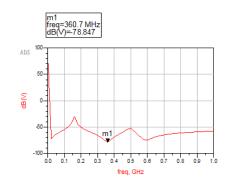

| Figure 4.26: Circuit simulated and frequency response of GRM1885C2A331JA01                 | 86   |

| Figure 4.27: Circuit simulated of Bias capacitors                                          | 87   |

| Figure 4.28: Frequency response of Bias network                                            |      |

| Figure 4.29: Picture of resistor RMCF1206JT5K10                                            |      |

| Figure 4.30: Picture of RF choke coil 2222SQ-221_E                                         | 88   |

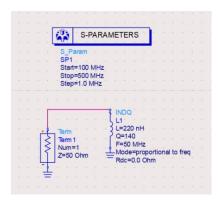

| Figure 4.31: Circuit model simulated and Z11-frequency graph                               | 89   |

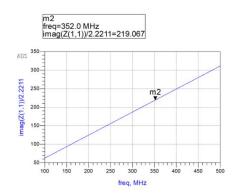

| Figure 4. 32: Quality factor and Inductance as a function of frequency for the RF choke co | oil  |

| 2222SQ-221_E[18]                                                                           |      |

| Figure 4.33: Circuit topology simulated for load-pull simulations                          | 90   |

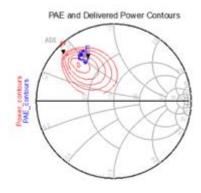

| Figure 4.34: Smith and cartesian chart of the power and power added efficiency contours    | 91   |

| Figure 4.35: Circuit topology simulated for small signal stability testing                 | 91   |

| Figure 4.36: Smith chart with available gain and source stability circles                  | 92   |

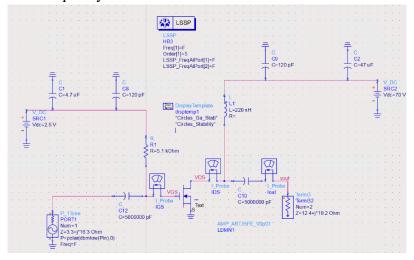

| Figure 4.37:Circuit topology simulated for large signal stability testing                  | 92   |

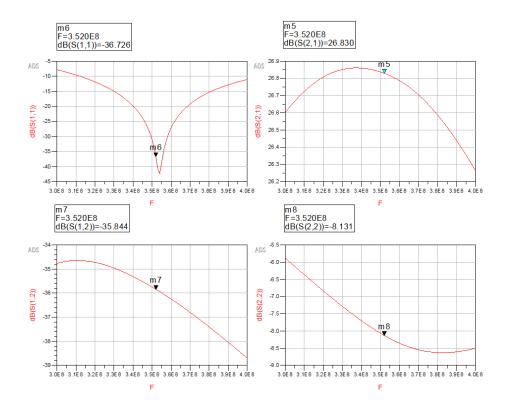

| Figure 4.38: S parameters magnitude in dBs of large signal simulation                      | 93   |

| Figure 5.1: Transmission line technologies of PCBs                                         | 96   |

| Figure 5.2: Dimensioning of microstrip and coplanar waveguide                              | 97   |

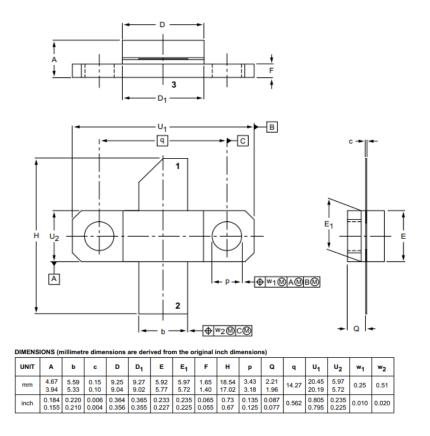

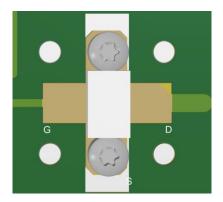

| Figure 5.3: Mechanical design of the transistor                                            | 99   |

| Figure 5. 4: PLA blocks picture                                                            | 99   |

| Figure 5. 5: Transistor                                                                    | 99   |

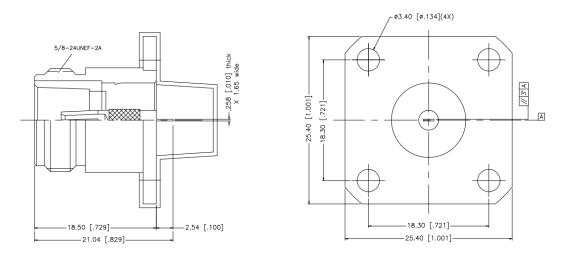

| Figure 5.6: N-type connectors mechanical design                                            | .100 |

| Figure 5. 7: Included distance in the                                                      | .101 |

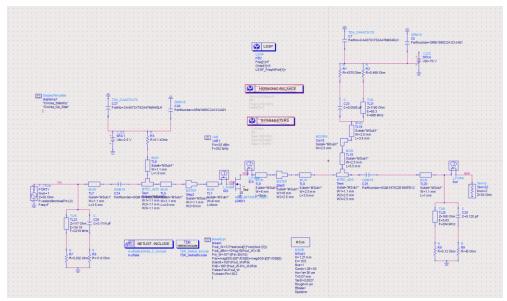

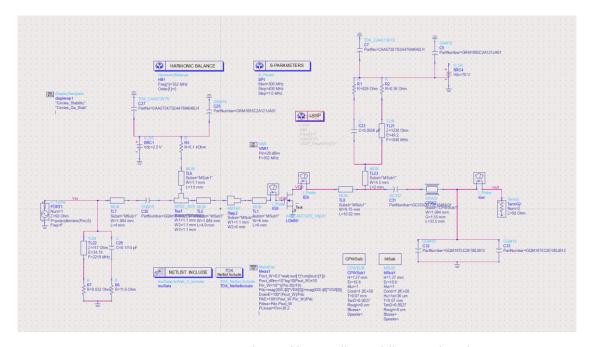

| Figure 5.8: Total amplifier circuit simulated                                              | .101 |

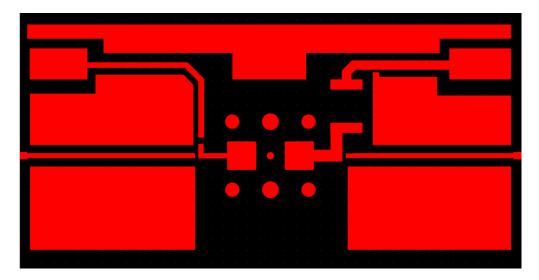

| Figure 5.9: Coppel layer design on Altium Designer                                         | .102 |

| Figure 5.10: List of components of matching networks of iteration #1                       |      |

| Figure 5.11: Dimensions of microstrip traces connecting                                    |      |

| Figure 5. 12: Circuit simulated on ADS to calculate input impedance                        | .103 |

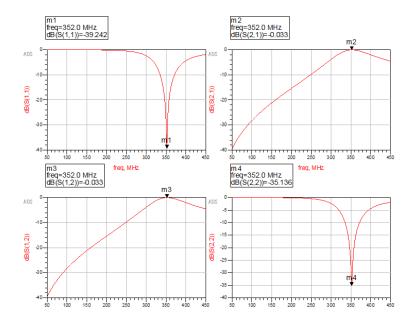

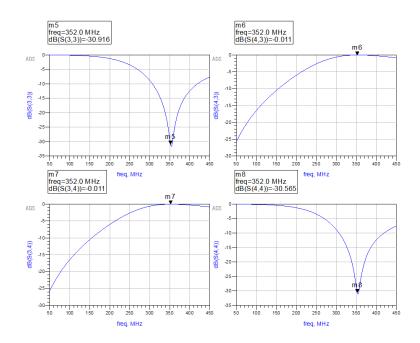

| Figure 5.13: S-parameters of input transistor pad magnitude                                   | 104 |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 5.14: Circuit simulated on ADS to calculate output impedance                           | 104 |

| Figure 5.15: S-parameters of output transistor pad magnitude                                  | 105 |

| Figure 5.16: Impedance transformations due to matching components on Smith chart              | 106 |

| Figure 5.17: Circuit simulation of input matching network                                     | 106 |

| Figure 5.18: Magnitude in dB of S-parameters of input matching network as a function          | of  |

| frequency                                                                                     | 107 |

| Figure 5.19: Circuit simulation of output matching network                                    | 107 |

| Figure 5.20: Magnitude in dB of S-parameters of output matching network as a function         | of  |

| frequency                                                                                     | 108 |

| Figure 5.21: List of components of matching networks of iteration #2 with manufactures        | r   |

| reference and impedance                                                                       | 108 |

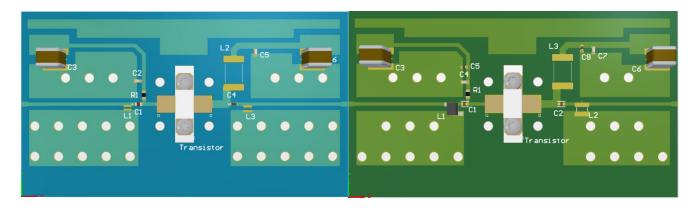

| Figure 5. 22: Layout designed for iteration #2                                                | 109 |

| Figure 5.23: Layout designed for iteration #3                                                 | 109 |

| Figure 5. 24: Impedance transformation on Smith chart for iteration #4                        |     |

| Figure 5.25: List of components for output matching network of iteration #4 with capacitation |     |

| and manufacturer reference                                                                    |     |

| Figure 5.26: Impedance transformation on Smith chart for iteration #5                         | 111 |

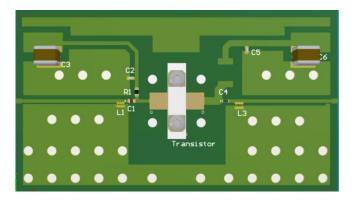

| Figure 5.27: Layout designed for iteration #5                                                 |     |

| Figure 5.28: Mechanical design of heatsink                                                    |     |

| Figure 5.29: Layout designed on Altium with holes for heatsink connection                     |     |

| Figure 5.30: Picture of heatsink                                                              |     |

| Figure 5.31: Circuit equivalent of layout #2 simulated on ADS                                 | 114 |

| Figure 5.32: Circuit equivalent of layout #2 and #5 simulated on ADS                          |     |

| Figure 5.33: Layout 1 in Altium Figure 5.34: Layout 2 in Altium                               |     |

| Figure 5.35:Layout 3 and 4 in Altium                                                          |     |

| Figure 5.36:Layout 5 and 5.2 in Altium                                                        |     |

| Figure 5.37: Simulation results of output power in dBm and W as a function of input po        |     |

|                                                                                               | 116 |

| Figure 5.38: Simulation results of drain efficiency and power added efficiency as a func      |     |

| of input power                                                                                |     |

| Figure 5.39: Simulation results of power dissipated and DC power offered as a function        | of  |

| input power                                                                                   |     |

| Figure 5.40: Simulation results of output power for and without standard gain                 | 117 |

| Figure 5.41: Simulation results of gain and output power as a function of input power         |     |

| Figure 5.42: Simulation results of Harmonics                                                  |     |

| Figure 5.43: Simulation results of S-parameters as a function of frequency                    |     |

| Figure 5.44: Simulation results of S-parameters as a function of input power                  |     |

| Figure 5.45: Simulation results of iterations #4 and #5 for output power as a function of     |     |

| power                                                                                         | _   |

| •                                                                                             | -   |

| Figure 6.1: Altium workspace                                                                  | 121 |

| Figure 6.2: Generated Gerber file                                                             |     |

| Figure 6.3: Drilling machine and copper plate                                          | 122   |

|----------------------------------------------------------------------------------------|-------|

| Figure 6.4: Top and Bottom layer after the drilling                                    | 122   |

| Figure 6.5: Pictures of PCB impairments                                                | 123   |

| Figure 6.6: Pictures of examples of good soldering                                     | 124   |

| Figure 6.7: Picture example of bad soldering                                           |       |

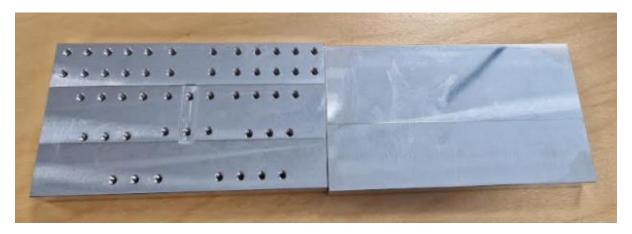

| Figure 6.8: Heatsink top and bottom view                                               |       |

| Figure 6.9: Picture of broken transistor                                               | 126   |

| Figure 6.10: Picture of the 3D printer                                                 | 126   |

| Figure 6.11: Picture of amplifier with PLA blocks                                      | 127   |

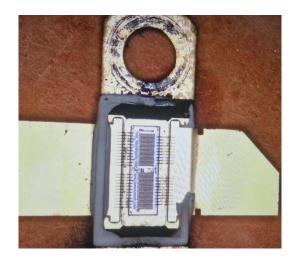

| Figure 6.12: Picture of amplifier with soldered transistor                             | 127   |

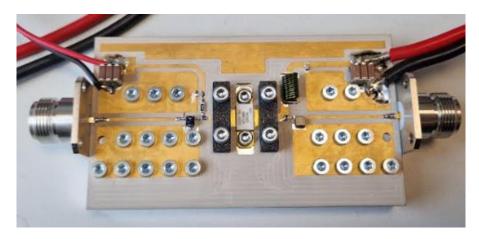

| Figure 6.13: Picture of assembled amplifier with PCB, heatsink and heat dissipator     | 128   |

| Figure 6.14: Manufacturing non idealities                                              | 129   |

| Figure 6. 15: Picturers of Rohde & Swartz SMC100A and Keysight Technologies N5182F     | 3-    |

| 503 signal generators                                                                  | 132   |

| Figure 6.16: Pictures of Aim-TTi EL 302 R and Rohde & Schwarz HMC8043 power supp       | olies |

|                                                                                        | 133   |

| Figure 6.17: Pictures of Rohde & Schwarz NRP2 Rohde & Schwarz NRX Power meters         | 133   |

| Figure 6.18: Picture of Keysight Technologies N9020B MXA signal analyzer               | 134   |

| Figure 6.19: Picture of Rohde & Schwarz ZNB4 Vector Network Analyzer                   | 134   |

| Figure 6.20: Picture of a High-Power Directional Coupler and an Attenuator             | 134   |

| Figure 6.21: Pictures of Weinschel Associates WA1453 and Valvo Circulator VAD1447A     | L.    |

|                                                                                        | 135   |

| Figure 6.22: Picture of RFS FLIR E63900 thermal camera                                 | 135   |

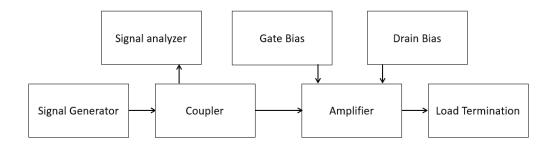

| Figure 6.23: Topology for power measurements                                           | 136   |

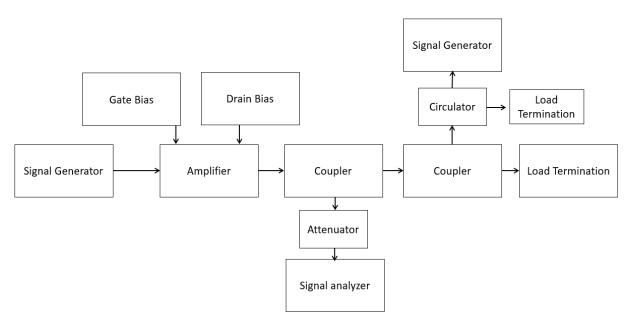

| Figure 6.24: Topology for signal analysis                                              | 137   |

| Figure 6.25: Topology for Vector Network Analyzer measurements                         | 137   |

| Figure 6.26: Topology for S11 measurements                                             | 138   |

| Figure 6.27: Topology for S22 measurements                                             |       |

| Figure 6.28: Bench overview of S22 measurements                                        | 139   |

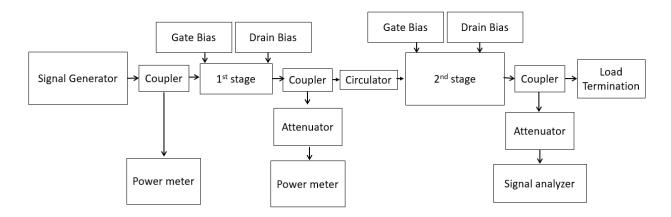

| Figure 6.29: Topology for cascaded amplifiers measurements                             |       |

| Figure 6.30: Measurements of output power and gain as a function of input power        | 142   |

| Figure 6.31: Measurements of output power as a function of input power for soldered    |       |

| transistor and PLA blocks connection                                                   | 142   |

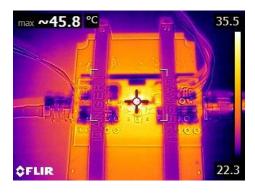

| Figure 6.32: Pictures from the thermal camera for soldered transistor and PLA blocks   |       |

| connection monitoring transistor's temperature                                         |       |

| Figure 6.33: Picture from the thermal camera monitoring output capacitor               | 144   |

| Figure 6.34: Picture from thermal camera monitoring transistor temperature of soldered |       |

| transistor in pulsed mode                                                              |       |

| Figure 6.35: Measurements of Efficiency, Power Added Efficiency, Dissipated power and  |       |

| Drain current as a function of input power                                             | 146   |

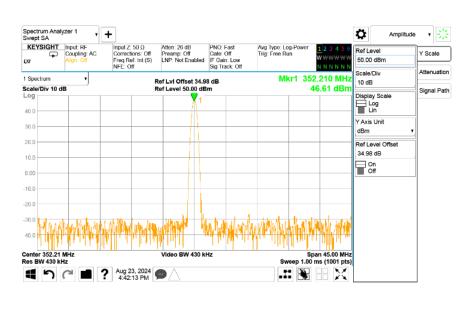

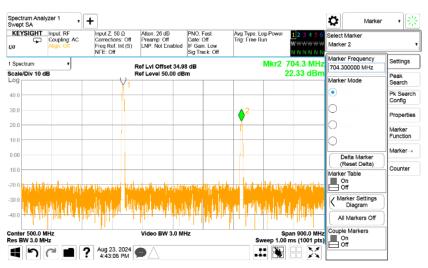

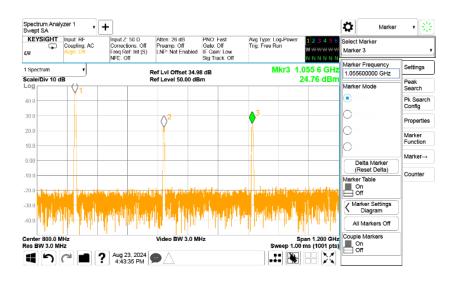

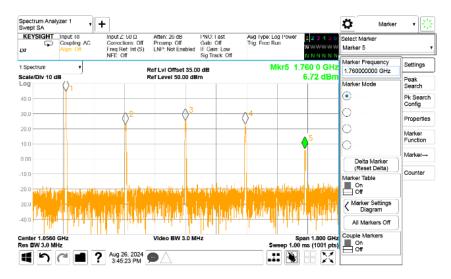

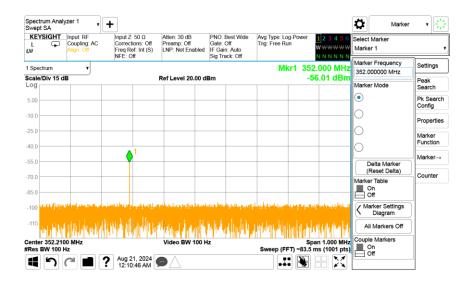

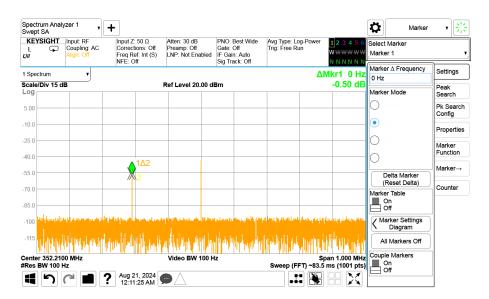

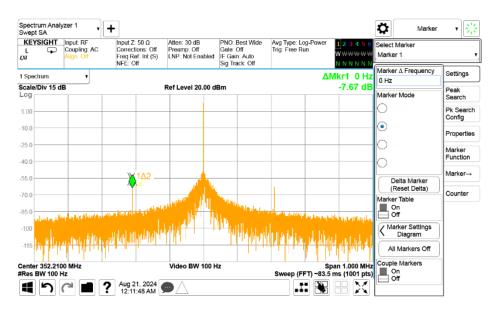

| Figure 6.36: Signal Analyzer screenshot measurements for amplitude of 1st and 2nd      |       |

| Harmonic                                                                               | 148   |

| Figure 6.37: Signal Analyzer screenshot measurements for amplitude of 3rd, 4th and 5th  | 1   |

|-----------------------------------------------------------------------------------------|-----|

| Harmonic                                                                                | 149 |

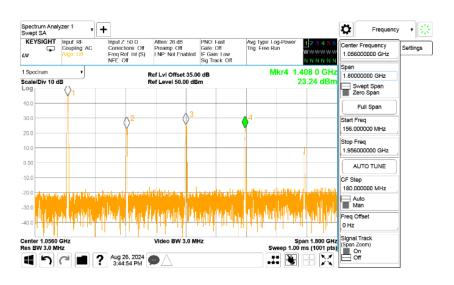

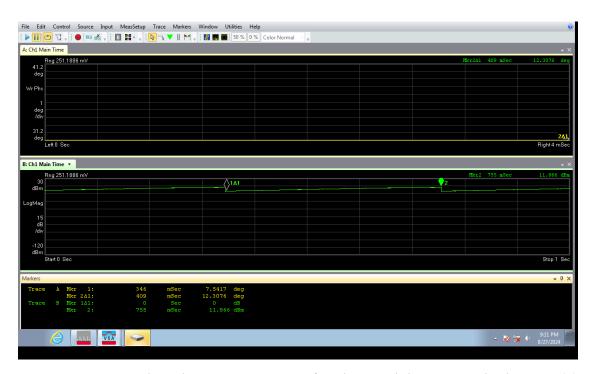

| Figure 6. 38: Signal Analyzer measurements for phase stability over 10dB dynamic (a).   | 150 |

| Figure 6.39: Signal Analyzer measurements for phase stability over 10dB dynamic (b).    | 151 |

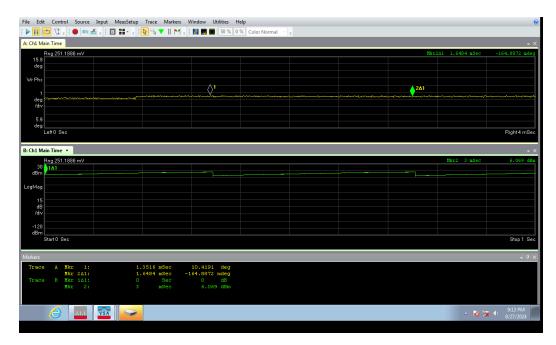

| Figure 6.40: Signal Analyzer screenshot for pulse measurements                          | 151 |

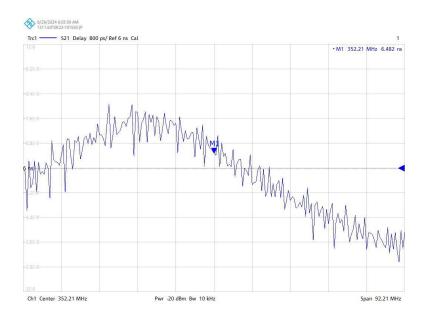

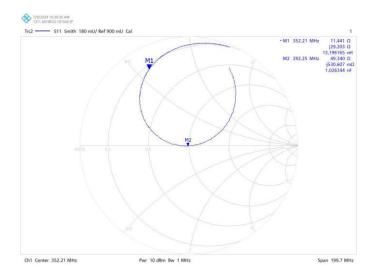

| Figure 6.41: Screenshot from the VNA for group delay measurements                       | 153 |

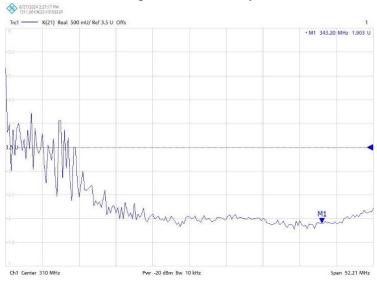

| Figure 6.42: Screenshot from the VNA for K-factor measurements                          | 153 |

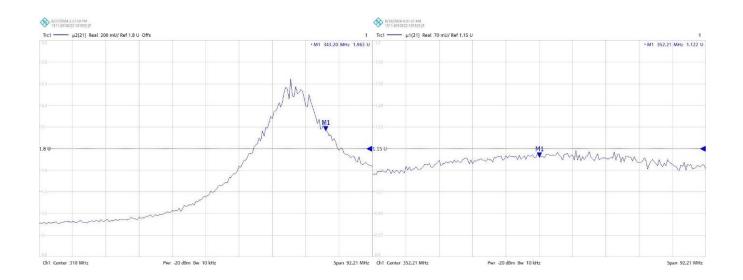

| Figure 6.43: Screenshot from the VNA for μ 2 and 1 factor measurements                  | 154 |

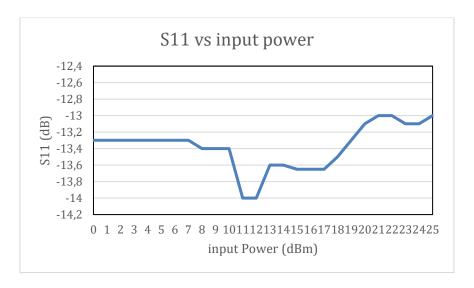

| Figure 6.44: Measurements of S11 parameter as a function input power                    | 155 |

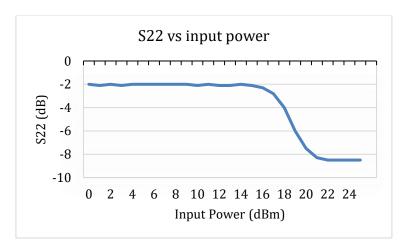

| Figure 6.45: Measurements of S22 parameter as a function input power                    | 156 |

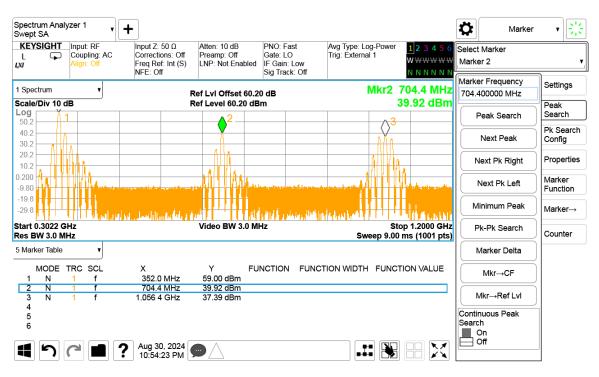

| Figure 6.46: Signal Analyzer screenshots of preparing S22 measurements                  | 157 |

| Figure 6.47: Signal Analyzer screenshot measuring the S22 parameter                     | 157 |

| Figure 6.48: Signal Analyzer screenshot for harmonics distortions                       | 159 |

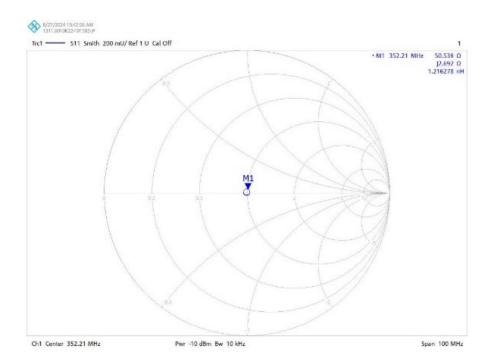

| Figure 6.49: Screenshot from VNA Smith chart measurements of                            | 159 |

| Figure 6.50: Picture of the circuit created to measure the characteristic               | 160 |

| Figure 6.51: Screenshot from VNA Smith chart measurements of impedance                  | 160 |

| Figure 6.52: Pictures from the thermal camera monitoring the temperature of the transis | tor |

| and the output coupling capacitor of iteration #5                                       | 162 |

| Figure 6.53: Comparison of measurements and simulated results of output power as a      |     |

| function of input power                                                                 | 165 |

| Figure 6.54: Comparison of measurements and simulated results of S-parameters as a      |     |

| function of input power                                                                 | 166 |

# **List of Tables**

| Table 1: ESS high level parameters ([1] page 2)                                         | 35  |

|-----------------------------------------------------------------------------------------|-----|

| Table 2: Operating parameters for existing and upcoming spallation neutron sources with |     |

| fundamental physics programs ([9])                                                      | 42  |

| Table 3: Solid-State Power Amplifiers in Accelerator RF Systems                         | 66  |

| Table 4: Design Specifications                                                          |     |

| Table 5: Specifications of chosen transistor                                            | 73  |

| Table 6: Voltage values calculation                                                     | 78  |

| Table 7: Summary of DC simulations                                                      |     |

| Table 8: Operational conditions for transistor failure                                  | 80  |

| Table 9: Specifications of CAA573X7S2A476M640LH                                         | 84  |

| Table 10: Specifications of GRM1885C2A121JA01                                           |     |

| Table 11: Specifications of GRM1885C2A331JA01                                           | 86  |

| Table 12: Specifications of RMCF1206JT5K10                                              |     |

| Table 13: Specifications of 2222SQ-221_E                                                | 88  |

| Table 14: Summary of Bias networks                                                      |     |

| Table 15: Specifications of RO3210 material                                             | 95  |

| Table 16: Dimensions of the microstrip traces and coplanar waveguides                   | 97  |

| Table 17: Summary of PCB material                                                       | 119 |

| Table 18: Dimensions of transmission line for 50 Ohms characteristic impedance          | 120 |

| Table 19: Transmission line dimensions for RF choke – transistor connection             | 120 |

| Table 20: Summary of matching network 2 and 3                                           | 120 |

| Table 21: Summary of matching network 4 and 5                                           | 120 |

| Table 22: Summary of power estimations per iteration                                    | 120 |

| Table 23: Specifications of the Driver's 1st stage                                      | 132 |

| Table 24: Power measurements of iteration #2                                            | 141 |

| Table 25: Power measurements comparison of soldered transistor and PLA blocks           | 143 |

| Table 26: Calculations of current consumption, DC power, efficiency,                    | 145 |

| Table 27: 1dB Bandwidth power measurements                                              | 147 |

| Table 28: Pulse repeatability under voltage drops                                       | 152 |

| Table 29: S11 measurements                                                              |     |

| Table 30: S22 measurements                                                              | 156 |

| Table 31: Cascaded amplifiers measurements                                              |     |

| Table 32: Power and current consumption measurements for iteration #5                   | 161 |

| Table 33: Summary of specifications and measurements                                    | 164 |

### Εκτενή Περίληψη στα Ελληνικά/ Extensive Summary in Greek

Οι επιταχυντές σωματιδίων αποτελούν θεμελιώδη εργαλεία της σύγχρονης επιστήμης και τεχνολογίας. Πρόκειται για συστήματα ικανά να επιταχύνουν φορτισμένα σωματίδια σε υψηλές ταχύτητες, χρησιμοποιώντας ηλεκτρικά και μαγνητικά πεδία. Σήμερα υπάρχουν χιλιάδες επιταχυντές σε λειτουργία παγκοσμίως, οι οποίοι βρίσκουν εφαρμογή σε ένα ευρύ φάσμα πεδίων: από τη βασική έρευνα στη φυσική υψηλών ενεργειών και την πυρηνική φυσική, έως την ιατρική απεικόνιση και θεραπεία, τη βιομηχανία και τις τεχνολογίες υλικών. Η παρούσα διπλωματική εργασία που υποβλήθηκε στην Σχολή Ηλεκτρολόγων Μηχανικών και Μηχανικών Υπολογιστών του Εθνικού Μετσόβιου Πολυτεχνείου εκπονήθηκε με βάση την εργασία του συγγραφέα στο European Spallation Source (ESS) το διάστημα Μάρτιος 2024-Αύγουστος 2024. Το European Spallation Source ή Ευρωπαϊκή Πηγή Θρυμματισμού θα αποτελέσει τον ισχυρότερο του είδους επιταχυντή όταν ολοκληρωθεί η κατασκευή του. Πρόκειται για να έναν γραμμικό επιταχυντή όπου πρωτόνια μέσω ηλεκτρομαγνητικών πεδίων επιταχύνονται και συγκρούονται με έναν στόχο μόλυβδου, με τα σκεδαζόμενα νετρόνια έπειτα να συλλέγονται και να χρησιμοποιούνται για τα ποικίλα πειράματα που στεγάζει το ερευνητικό κέντρο.

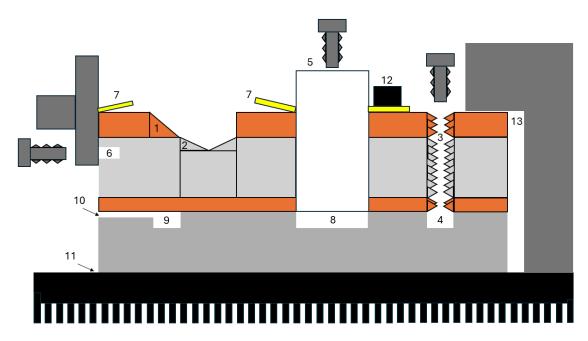

Το σχηματικό διάγραμμα του γραμμικού επιταχυντή του ESS, Μάιος 2020

Σε αυτό το διάστημα η ομάδα των πηγών ραδιοσυχνοτήτων διενεργούσε συνεργασία με το πανεπιστήμιο Uppsala University (UU) για την διερεύνηση εναλλακτικών πηγών τροφοδότησης των spoke κοιλοτήτων του γραμμικού επιταχυντή. Το ESS θα αποτελέσει κόμβο ανάπτυξης και έρευνας για την Ευρώπη, έχοντας όμως μεγάλες ενεργειακές ανάγκες. Αποφασίστηκε να διερευνηθούν εναλλακτικοί τρόποι τροφοδότησής που μπορούν να αντικαταστήσουν τις υπάργουσες λύσεις με άλλες αποδοτικότερες. Επιλέγθηκε να χρησιμοποιηθεί η τεχνολογία ενισχυτών ισχύος στερεάς κατάστασης καθώς συνδυάζουν υψηλή αποδοτικότητα που κυμαίνεται στο διάστημα 50 με 80 % σε χαμηλές ανάγκες τροφοδοσίας. Συγκεκριμένα, για να καλυφθούν οι ενεργειακές ανάγκες των spoke κοιλοτήτων, για κάθε μια από αυτές θα κατασκευαστεί είναι σύστημα ενισχυτών ισχύος στερεάς κατάστασης (SSPA) με ισχύ εξόδου 400kW. Η υπάρχουσα λύση ήταν οι ενισχυτές τετρόδων, με αποδοτικότητα περίπου στο 50%. Ένας ακόμα λόγος για την στροφή στην τεχνολογία στερεάς κατάστασης είναι πως γενικότερα η τεχνολογία στις μικροκυματικές συχνότητες στρέφεται προς εκείνη την κατεύθυνση. Καθώς το πλάνο του ESS είναι λειτουργία για τουλάχιστον 40 χρόνια είναι αναγκαίο να έχουν βρεθεί λύσεις που θα επιτρέπουν την ομαλή λειτουργία του επιταχυντή με τεχνολογίες που εξελίσσονται παράλληλα στην αγορά.

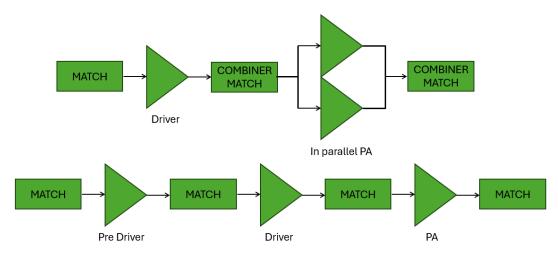

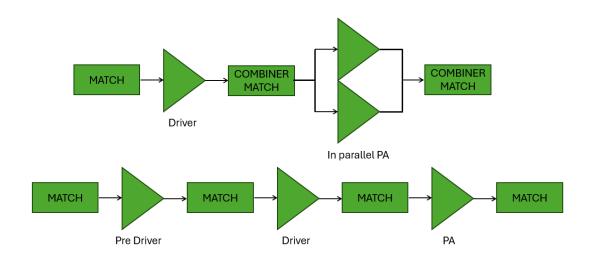

Το πρώτο κεφάλαιο της διπλωματικής έχοντας εισάγει τον αναγνώστη στο εγχείρημα για βελτίωση της ενεργειακής απόδοσης του ESS, παραθέτει και αναλύει την λύση που επιλέχθηκε. Συγκεκριμένα, η τοπολογία θα αποτελείται από πολλά παράλληλα και σε σειρά στάδια ενίσχυσης με συνεχή επίβλεψη της διαδικασίας από εξωτερικά συστήματα για να διασφαλιστεί η ομαλή λειτουργία.

Τοπολογίες ενισχυτών ισχύος

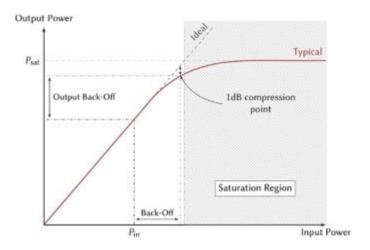

Σκοπός της διπλωματικής αυτής είναι ο σχεδιασμός και η κατασκευή ενός ενισχυτή ισχύος όπου θα λειτουργεί ως πρώτο στάδιο του οδηγού σε αυτή την αλυσίδα με τις εξής προδιαγραφές: 352,21 MHz συχνότητα λειτουργίας, αποδοτικότητα μεγαλύτερη από 50% και ισχύς εξόδου 50W. Μέσω αυτής της εργασίας δίνεται η δυνατότητα να παρεισφρήσει ο συγγραφέας στον κόσμο της σχεδίασης ραδιοσυχνοτήτων όπου αναζητείται ο ιδανικός συμβιβασμός ανάμεσα στα βασικά χαρακτηριστικά ενός ενισχυτή: θόρυβος, ισχύς, συχνότητα, κέρδος, τάση τροφοδοσίας και γραμμικότητα.

Στο δεύτερο κεφάλαιο παρατίθεται το απαραίτητο θεωρητικό υπόβαθρο ώστε να γίνουν αντιληπτά τα βήματα που ακολουθήθηκαν για την σχεδίαση.

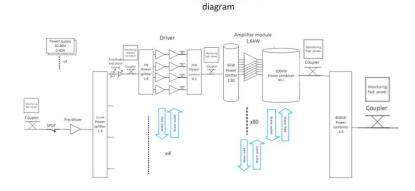

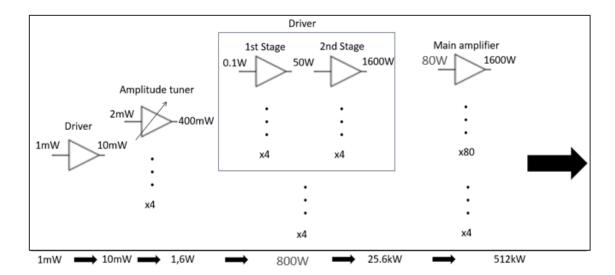

Στο τρίτο κεφάλαιο αναλύεται το σύστημα SSPA των 400 kW, το οποίο προορίζεται για την τροφοδότηση των 26 spoke κοιλοτήτων του γραμμικού επιταχυντή (LINAC) του ESS, καθεμία εκ των οποίων απαιτεί ισχύ 400 kW στα 352.21 MHz. Παρουσιάζεται η αρχιτεκτονική του συστήματος, οι λόγοι επιλογής της συγκεκριμένης τοπολογίας, καθώς και η λειτουργία και επιλογή των επιμέρους υποσυστημάτων και εξαρτημάτων. Επιπλέον, παρουσιάζεται η συμβολή του συγγραφέα στη διαμόρφωση του καταλόγου υλικών Bill of Materials και στην ανάλυση κόστους του συστήματος, με τις τιμές να αντιστοιχούν στον Απρίλιο του 2024.

400kW Amplifier block

Το μπλοκ διάγραμμα της τοπολογίας 400kW SSPA

Η τοπολογία του συστήματος αποτελείται από πέντε διαδοχικά στάδια ενίσχυσης: προενισχυτή, ρυθμιστή πλάτους και φάσης, 1ο στάδιο οδηγού, 2ο στάδιο οδηγού και κύριο ενισχυτή ισχύος, τα οποία λειτουργούν σε παράλληλη διάταξη με πολλούς ενισχυτές για λόγους αξιοπιστίας και βελτιστοποίησης της εξόδου. Καθ' όλη τη διαδρομή του σήματος, κατευθυντικοί συζεύκτες παρέχουν πληροφορίες για την κατάσταση λειτουργίας, επιτρέποντας την παρακολούθηση και προστασία του συστήματος. Το στάδιο εισόδου περιλαμβάνει έναν συζεύκτη για την παρακολούθηση της ισχύος εισόδου, έναν διακόπτη τύπου SPDT για προστασία από υπερφόρτωση, έναν προενισχυτή και έναν διαχωριστή ισχύος 1:4. Σκοπός του είναι η αρχική ενίσχυση του σήματος από 1 mW σε 10 mW και η διανομή του σε τέσσερα παράλληλα κανάλια.

Το στάδιο οδηγού αποτελεί το κύριο αντικείμενο της διπλωματικής εργασίας. Αποτελείται από ρυθμιστή πλάτους, ρυθμιστή φάσης, διαιρέτη 1:4, το πρώτο και δεύτερο στάδιο ενίσχυσης του οδηγού, καθώς και έναν συνδυαστή ισχύος 4:1. Τρεις κατευθυντικοί συζεύκτες τοποθετούνται σε καίρια σημεία για έλεγχο της ενίσχυσης και ανίχνευση πιθανών απωλειών. Η χρήση ρυθμιστών πλάτους και φάσης εξασφαλίζει την ορθή προσαρμογή του ηλεκτρομαγνητικού κύματος και την αποφυγή σπινθηρισμών ή αστοχιών κατά τη λειτουργία. Το κύριο στάδιο ενίσχυσης είναι το τελευταίο και ισχυρότερο τμήμα της αλυσίδας, υπεύθυνο για τη μεγιστοποίηση της συνολικής παραγόμενης ισχύος. Οι διαιρέτες και συνδυαστές ισχύος του σταδίου αυτού έχουν σχεδιαστεί από το Πανεπιστήμιο της Ουψάλας, καθώς δεν διατίθενται αντίστοιχα εμπορικά εξαρτήματα που να καλύπτουν αυτά τα επίπεδα ισχύος. Το στάδιο εξόδου περιλαμβάνει τέσσερις συζεύκτες για την παρακολούθηση της ισχύος κάθε κύριου ενισχυτή και έναν τελικό συνδυαστή 4×100 kW. Ένας ισχυρός τελικός συζεύκτης τοποθετείται πριν από την κοιλότητα για την παρακολούθηση και προστασία έναντι τόξων.

Παράλληλα, εξετάζονται τα συστήματα παρακολούθησης, τα συστήματα ψύξης, καθώς και το υποστηρικτικό υλικό του συστήματος. Οι πληροφορίες από τους συζεύκτες επεξεργάζονται από τα συστήματα παρακολούθησης που αναπτύσσει η ομάδα RF Sources, ενώ η απαγωγή θερμότητας επιτυγχάνεται μέσω του υδρόψυκτου συστήματος του εργαστηρίου RF. Το υποστηρικτικό υλικό περιλαμβάνει συνδετήρες τύπου N, πυκνωτές προστασίας, ικριώματα και καλωδιώσεις. Τέλος, παρουσιάζεται αναλυτικά ο Πίνακας Υλικών (BoM), ο οποίος καταρτίστηκε ώστε να εκτιμηθεί το συνολικό κόστος του έργου (534.024,79 €), να οργανωθούν τα δεδομένα της αρχιτεκτονικής και να αποκτηθεί βαθύτερη κατανόηση των RF εξαρτημάτων και των τεχνικών προδιαγραφών τους.

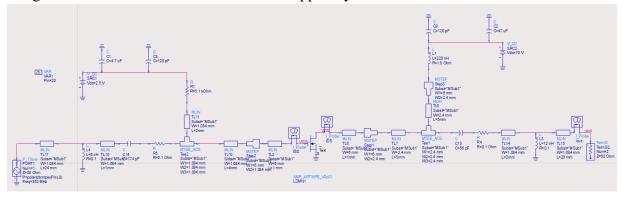

Στο τέταρτο κεφάλαιο αναλύεται διεξοδικά η διαδικασία σχεδίασης του πρώτου σταδίου του οδηγού του ενισχυτή στερεάς κατάστασης (SSPA) των 400 kW. Στόχος του σταδίου είναι η ενίσχυση του σήματος εισόδου στα απαραίτητα επίπεδα ισχύος ώστε να οδηγήσει με ασφάλεια τα επόμενα στάδια της αλυσίδας ενίσχυσης. Η διαδικασία περιλαμβάνει την επιλογή κατάλληλου τρανζίστορ, τη βελτιστοποίηση των τάσεων πόλωσης, τη διαμόρφωση των κυκλωμάτων πόλωσης, καθώς και τη διερεύνηση της ιδανικής εμπέδησης εισόδου και εξόδου που θα παρουσιαστεί στον ενισχυτή, αλλά και της σταθερότητας του ενισχυτή μέσω προσομοιώσεων μικρού και μεγάλου σήματος στο λογισμικό Advanced Design System (ADS) της Keysight.

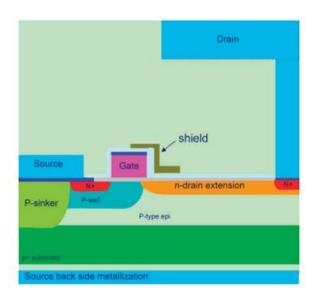

Η πρώτη φάση του σχεδιασμού αφορά την επιλογή της κατάλληλης τεχνολογίας τρανζίστορ. Μελετήθηκαν οι διαθέσιμες ημιαγώγιμες τεχνολογίες, βάσει της σχέσης συχνό-

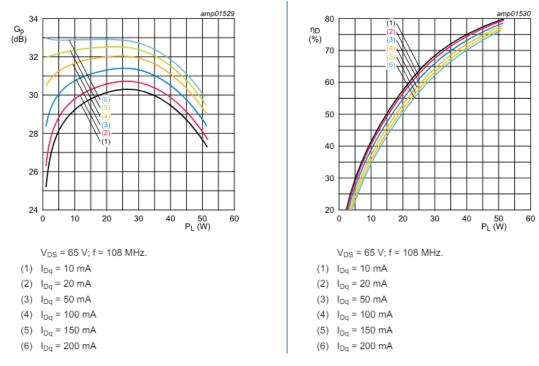

τητας λειτουργίας και παραγόμενης ισχύος. Μετά από σύγκριση, επιλέχθηκε η τεχνολογία LDMOS (Laterally Diffused Metal Oxide Semiconductor/ Πλευρικά Διάχυτος Ημιαγωγός Οξειδίου Μετάλλου), η οποία προσφέρει εξαιρετική γραμμικότητα, υψηλή απόδοση και ανθεκτικότητα σε θερμικές και ηλεκτρικές καταπονήσεις. Επιπλέον, είναι η πλέον ώριμη τεχνολογία για εφαρμογές υψηλής ισχύος στην περιοχή των VHF και UHF, καλύπτοντας πλήρως τη συχνότητα λειτουργίας των 352.21 MHz του επιταχυντή ESS. Ως ενεργό στοιχείο επιλέχθηκε το τρανζίστορ ART35FE της εταιρείας Ampleon. Η επιλογή αυτή έγινε λόγω της υψηλής απόδοσης, του μεγάλου περιθωρίου λειτουργίας σε υψηλές θερμοκρασίες και τάσεις, και της εγγυημένης μακροχρόνιας διαθεσιμότητας, στοιχείο κρίσιμο για βιομηχανικά και ερευνητικά έργα μεγάλης διάρκειας όπως το ESS. Το τρανζίστορ διαθέτει ονομαστική ισχύ εξόδου 35 W, τυπικό κέρδος 30 dB και αποδοτικότητα 70% στα 108 MHz, γεγονός που το καθιστά ιδανικό για χρήση ως πρώτο στάδιο οδηγού, πριν το κύριο στάδιο ισχύος που χρησιμοποιεί το μεγαλύτερο τρανζίστορ ΑRT2Κ0FEG της ίδιας εταιρείας. Η συνδυασμένη χρήση αυτών των δύο τρανζίστορ εξασφαλίζει βέλτιστη μεταφορά ισχύος μεταξύ των σταδίων και υψηλή συνολική αποδοτικότητα.

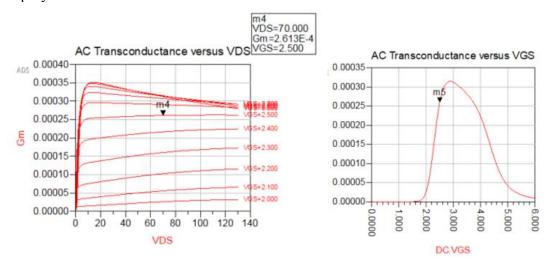

Αφού επιλέχθηκε το ενεργό στοιχείο, η επόμενη φάση του σχεδιασμού ήταν η βελτιστοποίηση των τάσεων πόλωσης. Για τον σκοπό αυτό πραγματοποιήθηκαν DC προσομοιώσεις στο περιβάλλον του ADS, προκειμένου να καθοριστεί το σημείο λειτουργίας που προσφέρει τον καλύτερο συμβιβασμό μεταξύ ισχύος εξόδου, αποδοτικότητας και θερμικής σταθερότητας.

Αποτελέσματα προσομοιώσεων για εξάρτηση της διαγωγιμότητας με την τάση του drain και του gate

Από τις προσομοιώσεις του ρεύματος ως συνάρτηση της τάσης πύλης (ID-VGS) προέκυψε ότι η αγωγιμότητα του τρανζίστορ ξεκινά γύρω στα 2 Volt, ενώ η μέγιστη διαγωγιμότητας επιτυγχάνεται κοντά στα 2.9 Volt. Με βάση αυτά τα αποτελέσματα επιλέχθηκε τάση πόλωσης πύλης VGS = 2.5 V, τιμή που εξασφαλίζει λειτουργία στη γραμμική περιοχή με επαρκή περιθώριο για διακυμάνσεις. Στη συνέχεια πραγματοποιήθηκε ανάλυση της χαρακτηριστικής καμπύλης ID-VDS, προκειμένου να καθοριστεί η τάση drain. Μελετώντας τις καμπύλες φόρτου και τα αντίστοιχα σημεία λειτουργίας για διαφορετικές τιμές τάσης, επιλέχθηκε VDS = 70 V. Η τιμή αυτή υπερβαίνει ελαφρώς την ονομαστική τάση του τρανζίστορ

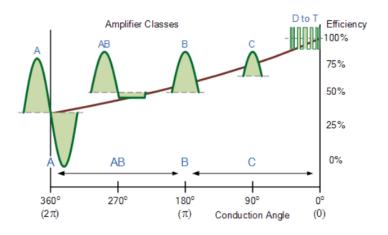

(65 V), αλλά γίνεται εκμετάλλευση της αυξημένη ανθεκτικότητα της σειράς ART και επιτρέποντας τη μέγιστη δυνατή ισχύ εξόδου. Οι προσομοιώσεις έδειξαν ότι με αυτές τις συνθήκες το τρανζίστορ λειτουργεί στην τάξη AB, επιτυγχάνοντας αποδοτικότητα περίπου 54% και ισχύ εξόδου γύρω στα 53 W. Η συγκεκριμένη τάξη λειτουργίας προσφέρει έναν βέλτιστο συνδυασμό αποδοτικότητας και γραμμικότητας, καθώς το τρανζίστορ άγει για περισσότερο από τη μισή περίοδο του σήματος.

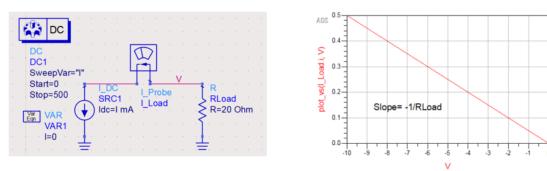

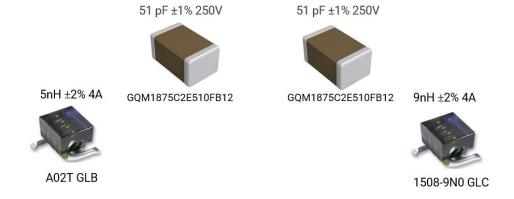

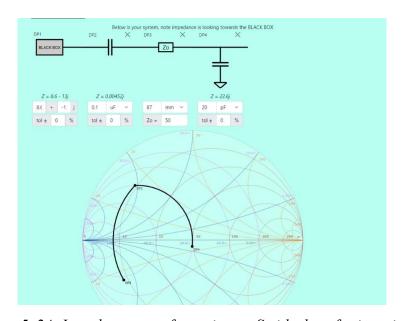

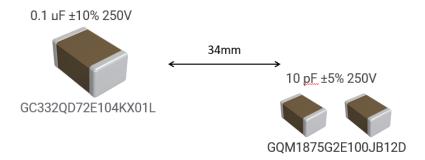

Αφού καθορίστηκαν τα σημεία πόλωσης, το επόμενο βήμα ήταν η σχεδίαση των κυκλωμάτων πόλωσης. Σκοπός τους είναι η σταθερή τροφοδοσία του τρανζίστορ με συνεχές ρεύμα χωρίς να επηρεάζεται η ραδιοσυχνότητα του σήματος. Τα κυκλώματα αυτά αποτελούνται από πυκνωτές αποσύζευξης, πυκνωτές σύζευξης και πηνία RF choke. Οι πυκνωτές αποσύζευξης συνδέονται παράλληλα με τις γραμμές τροφοδοσίας ώστε να "γείωνουν" κάθε ανεπιθύμητο ΑC σήμα, εξασφαλίζοντας σταθερή πόλωση και αποφυγή ταλαντώσεων. Η συμπεριφορά τους εξαρτάται έντονα από τη συχνότητα συντονισμού και την εσωτερική τους αντίσταση, γι' αυτό χρησιμοποιείται συνδυασμός πυκνωτών διαφορετικών τιμών για τη βελτίωση της απόκρισης γύρω από τα 352 MHz. Οι πυκνωτές σύζευξης, αντίστοιχα, επιτρέπουν τη διέλευση της RF ισχύος ενώ απομονώνουν τα DC κυκλώματα των σταδίων μεταξύ τους. Ιδιαίτερη σημασία δόθηκε και στην επιλογή των RF chokes, που εμποδίζουν τη διέλευση της RF ισχύος προς την πηγή τροφοδοσίας επιτρέποντας παράλληλα την απρόσκοπτη διέλευση του DC ρεύματος. Στην είσοδο του κυκλώματος χρησιμοποιήθηκε αντίσταση υψηλής τιμής αντί για πηνίο, δεδομένου ότι το ρεύμα πύλης είναι πρακτικά μηδενικό. Αντίθετα, στην έξοδο απαιτείται επαγωγικό στοιχείο υψηλής ποιότητας και αντοχής, καθώς το ρεύμα που διαρρέει το τρανζίστορ φθάνει σε επίπεδα αρκετών αμπέρ. Η επιλογή του κατάλληλου πηνίου βασίστηκε στην ανάλυση του συντελεστή ποιότητας, της μέγιστης τιμής RMS ρεύματος και της συχνότητας συντονισμού, ώστε να εξασφαλιστεί σταθερή συμπεριφορά στην περιοχή λειτουργίας.

Για να επιβεβαιωθεί η θερμική και ηλεκτρική ανθεκτικότητα του σχεδιασμού, πραγματοποιήθηκαν επιπλέον υπολογισμοί βασισμένοι στο εργαλείο αξιολόγησης της Ampleon. Οι υπολογισμοί απέδειξαν ότι για τις επιλεγμένες συνθήκες λειτουργίας (VDS = 70 V, ID  $\approx 1$  A) ο μέσος χρόνος αστοχίας του τρανζίστορ υπερβαίνει τα 18 έτη, ενώ η μέγιστη θερμοκρασία σύνδεσης φθάνει στους  $99^{\circ}$ C, τιμές που επιβεβαιώνουν τη βιωσιμότητα του σχεδιασμού με την προϋπόθεση ύπαρξης επαρκούς συστήματος ψύξης.

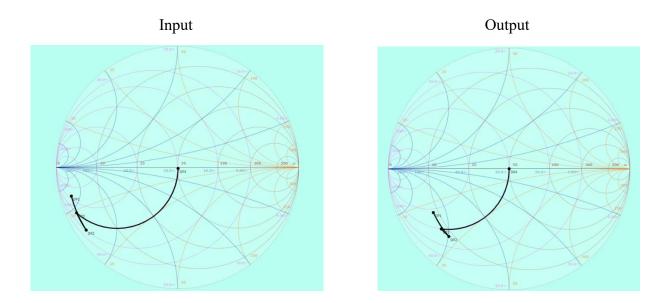

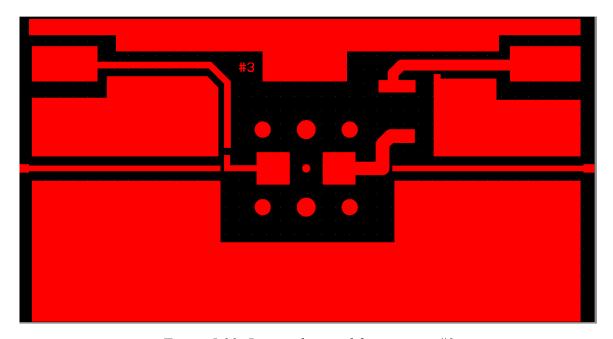

Στη συνέχεια πραγματοποιήθηκαν load-pull προσομοιώσεις, μία από τις σημαντικότερες διαδικασίες στο σχεδιασμό ενισχυτών ισχύος.

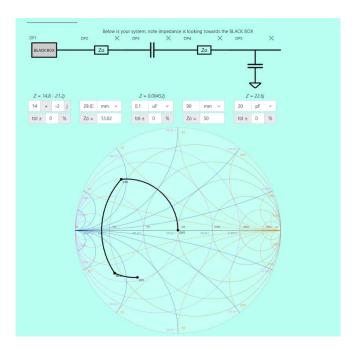

Το διάγραμμα Smith με τις γραφικές της PAE και της ισχύος εξόδου του ενισχυτή

Οι προσομοιώσεις αυτές επιτρέπουν την εύρεση των βέλτιστων τιμών εισόδου και εξόδου σύνθετης αντίστασης που μεγιστοποιούν την αποδοτικότητα και την ισχύ εξόδου. Με τη χρήση του εργαλείου load-pull του ADS, σαρώθηκαν οι αντιστάσεις εισόδου και εξόδου και παρατηρήθηκαν τα αντίστοιχα περιγράμματα ισχύος και απόδοσης πάνω στο διάγραμμα Smith. Με αυτόν τον τρόπο προσδιορίστηκαν οι τιμές αντιστάσεων που παρουσιάζουν στο τρανζίστορ τη βέλτιστη φόρτιση για τις επιθυμητές επιδόσεις.

Η τελική φάση του σχεδιασμού περιλαμβάνει τη μελέτη σταθερότητας του ενισχυτή. Εξετάστηκε τόσο η σταθερότητα μικρού σήματος όσο και η σταθερότητα μεγάλου σήματος. Στην πρώτη περίπτωση, πραγματοποιήθηκε προσομοίωση S-παραμέτρων για χαμηλή ισχύ εισόδου, προκειμένου να διασφαλιστεί ότι ο ενισχυτής δεν θα ταλαντώνει. Η ανάλυση έδειξε ότι οι καμπύλες σταθερότητας καλύπτουν ολόκληρη την περιοχή του διαγράμματος Smith, ενώ ο παράγοντας Rollet (K-factor) υπερβαίνει τη μονάδα, υποδεικνύοντας άνευ όρων σταθερότητα. Για τη δεύτερη περίπτωση, πραγματοποιήθηκε προσομοίωση μεγάλης ισχύος με ανάλυση αρμονικής ισορροπίας, ώστε να επιβεβαιωθεί η σταθερότητα ακόμη και σε συνθήκες κορεσμού. Οι υπολογισμοί των παραμέτρων Κ και Δ, καθώς και των παραγόντων σταθερότητας πηγής και φορτίου μ, επιβεβαίωσαν ότι ο ενισχυτής παραμένει σταθερός σε όλο το εύρος λειτουργίας.

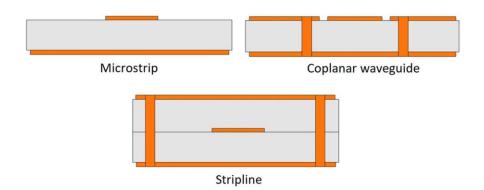

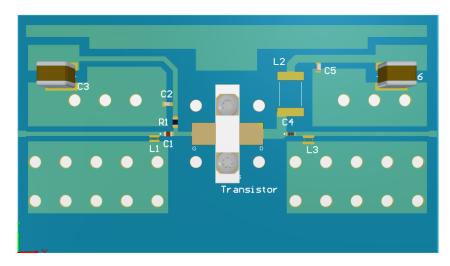

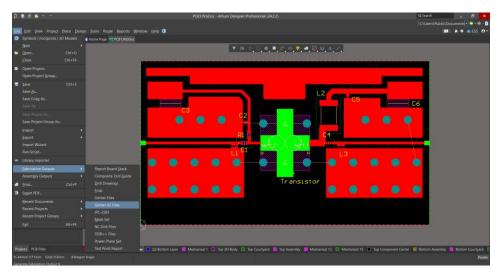

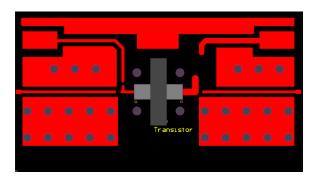

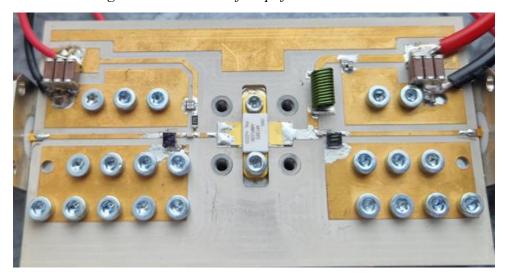

Στο πέμπτο κεφάλαιο αναλύεται διεξοδικά η διαδικασία σχεδίασης της διάταξης του ενισχυτή. Η ανάπτυξη της διάταξης, που ολοκληρώθηκε στο Altium Designer, αποτελεί κρίσιμο στάδιο της συνολικής σχεδίασης, καθώς καθορίζει την ηλεκτρική συμπεριφορά, τη θερμική σταθερότητα και την αξιοπιστία του κυκλώματος. Τα βασικά βήματα που ακολουθήθηκαν είναι η επιλογή του υλικού του υποστρώματος, η επιλογή της τεχνολογίας γραμμών μεταφοράς, ο σχεδιασμός των δικτύων προσαρμογής, η ανάπτυξη του συστήματος ψύξης και, τέλος, η προσομοίωση της τελικής διάταξης στο λογισμικό ADS.

Η διαδικασία ξεκινά με την επιλογή του κατάλληλου υλικού για το υπόστρωμα του κυκλώματος. Η επιλογή αυτή επηρεάζει καθοριστικά την απόδοση, τη θερμική συμπεριφορά και τη σταθερότητα της συχνότητας. Το υλικό που επιλέχθηκε είναι το RO3210 της Rogers Corporation, ένα κεραμικά ενισχυμένο υλικό ειδικά σχεδιασμένο για εφαρμογές υψηλών συχνοτήτων. Η υψηλή διηλεκτρική του σταθερά (10.8) επιτρέπει τη σχεδίαση πολύ συμπαγών κυκλωμάτων, κάτι που είναι κρίσιμο, καθώς στο σύστημα του ESS θα κατασκευαστούν δεκαέξι ενισχυτές του πρώτου σταδίου οδηγού και ο διαθέσιμος χώρος στον θάλαμο είναι περιορισμένος. Παράλληλα, ο χαμηλός συντελεστής απωλειών του (0.0027) εξασφαλίζει ελάχιστες απώλειες ισχύος, συμβάλλοντας στη συνολική ενεργειακή αποδοτικότητα του SSPA. Εξίσου σημαντικό ρόλο παίζει η θερμική συμπεριφορά του υλικού. Ο θερμικός συντελεστής της διηλεκτρικής σταθεράς (-459 ppm/°C) σημαίνει ότι το υλικό παρουσιάζει μικρή μεταβολή των ηλεκτρικών χαρακτηριστικών με τη θερμοκρασία, γεγονός ιδιαίτερα σημαντικό σε εφαρμογές υψηλής ισχύος όπου το θερμικό φορτίο είναι σημαντικό. Η θερμική αγωγιμότητα 0.81 W/m/Κ επιτρέπει την αποτελεσματική διάχυση της παραγόμενης θερμότητας, ενώ σε συνδυασμό με το σύστημα ψύξης που θα αναλυθεί παρακάτω, εξασφαλίζει τη σταθερή λειτουργία του ενισχυτή.

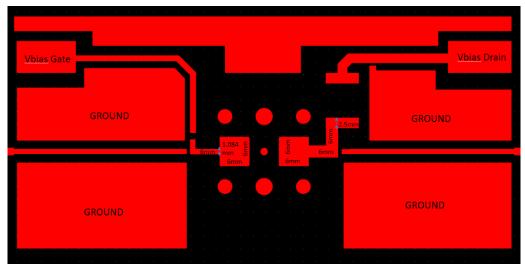

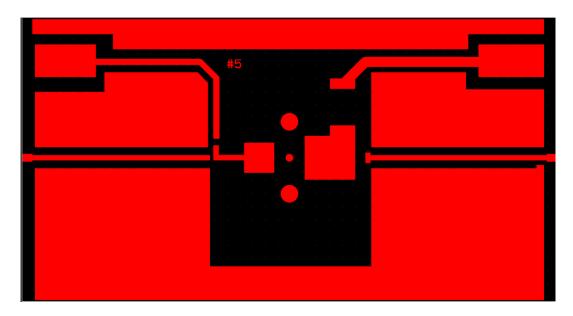

Αφού καθορίστηκε το υλικό του PCB, ακολούθησε η επιλογή της τεχνολογίας γραμμών μεταφοράς. Εξετάστηκαν οι τρεις κύριες τεχνολογίες, μικροταινιακή γραμμή, η ενδο-

στρωματική ταινιογραμμή και ο συνεπίπεδος κυματοδηγός. Η τεχνολογία μικροταινίας προσφέρει απλότητα κατασκευής και ευκολία πρόσβασης στα επιφανειακά εξαρτήματα, ενώ ο συνεπίπεδος κυματοδηγός προσφέρει καλύτερο έλεγχο της εμπέδησης και βελτιωμένη θερμική διαχείριση, καθώς οι γειτονικές γειώσεις συμβάλλουν στη διάχυση θερμότητας. Η ενδοστρωματική ταινιογραμμή, αν και εξαιρετικά αποδοτική ως προς την απομόνωση, απαιτεί πολυστρωματικά PCB και είναι πιο δύσκολη στην κατασκευή. Έτσι, επιλέχθηκε συνδυασμός μικροταινιακής γραμμής και ενδοστρωματικής ταινιογραμμής, επιτυγχάνοντας τον βέλτιστο συμβιβασμό μεταξύ ευκολίας κατασκευής, ακρίβειας εμπέδησης και απόδοσης.

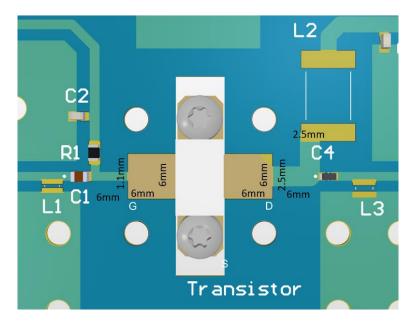

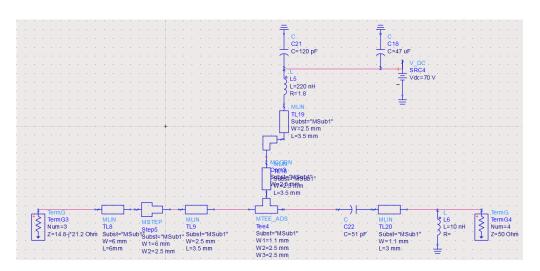

Για τη γραμμή μεταφοράς σχεδιάστηκαν οι διαστάσεις ώστε να διατηρείται χαρακτηριστική εμπέδηση 50 Ω, κάτι απαραίτητο για την ελαχιστοποίηση ανακλάσεων και απωλειών. Το πλάτος των ιχνών καθορίστηκε με βάση τη διηλεκτρική σταθερά και το πάχος του υποστρώματος, ενώ πραγματοποιήθηκαν προσομοιώσεις στο ADS για να επιβεβαιωθεί η σωστή εμπέδηση. Ιδιαίτερη μέριμνα δόθηκε στην ικανότητα των αγωγών να χειρίζονται τα αναμενόμενα ρεύματα λειτουργίας. Για το σημείο σύνδεσης του τρανζίστορ με το πηνίο RF choke, όπου το ρεύμα αγγίζει τα 4 A, η γραμμή μεταφοράς σχεδιάστηκε με πλάτος 2.2 mm ώστε να αποτρέπονται απώλειες λόγω φαινομένου επιδερμικού βάθους και υπερθέρμανσης. Η τοποθέτηση του τρανζίστορ στην πλακέτα αποτέλεσε κρίσιμο στάδιο, καθώς επηρεάζει τόσο τη μηχανική σταθερότητα όσο και τη θερμική αγωγιμότητα. Το τρανζίστορ τοποθετείται επιφανειακά και απαιτείται εξαιρετικά ακριβής προσαρμογή των επιφανειών σύνδεσης (pad) της πύλης και της αποχέτευσης. Οι διαστάσεις των pad καθορίστηκαν ώστε να εξασφαλίζουν βέλτιστη μεταφορά ισχύος και θερμική επαφή. Επιπλέον, λόγω των μηχανικών τάσεων που δημιουργούνται κατά τη λειτουργία, προτάθηκαν δύο λύσεις στήριξης: άμεση κόλληση του τρανζίστορ πάνω στο PCB ή χρήση 3D εκτυπωμένων υποστηρικτικών μπλοκ από PLA που ασκούν ομοιόμορφη πίεση στα pad, εξασφαλίζοντας σταθερή επαφή. Η δεύτερη λύση επιτρέπει την ευκολότερη επαναχρησιμοποίηση του τρανζίστορ σε επόμενες δοκιμές, μειώνοντας το κόστος. Στη συνέχεια, ενσωματώθηκαν οι RF συνδέσεις τύπου Ν, απαραίτητες για τη σύνδεση του ενισχυτή με το υπόλοιπο σύστημα μέσω ομοαξονικών καλωδίων. Η μηγανική τους τοποθέτηση υπολογίστηκε με ακρίβεια, ώστε να διασφαλιστεί ηλεκτρική συνέχεια, σωστή εμπέδηση 50  $\Omega$  και μηχανική σταθερότητα.

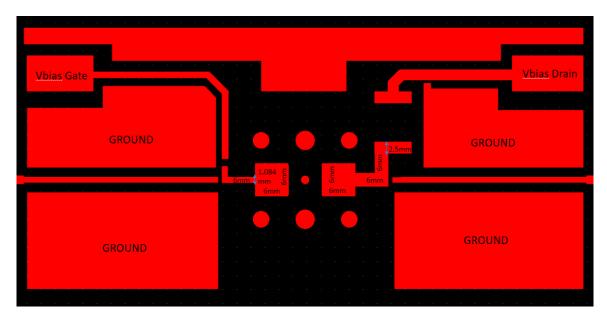

Η διάταζη των στρωμάτων χαλκού όπως σχεδιάστηκε στο Altium

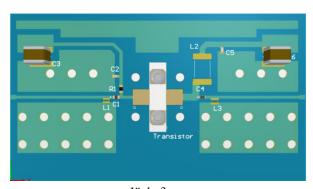

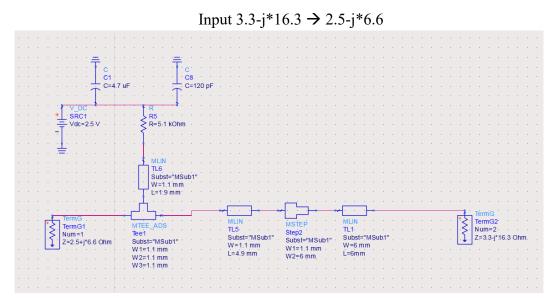

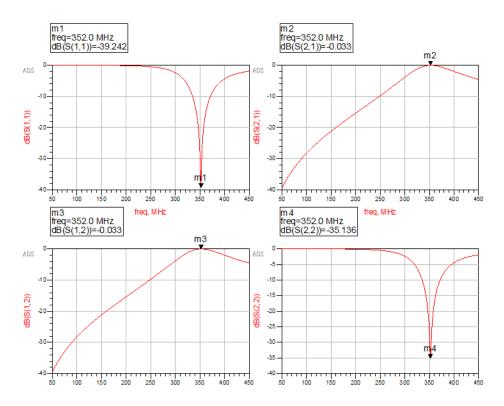

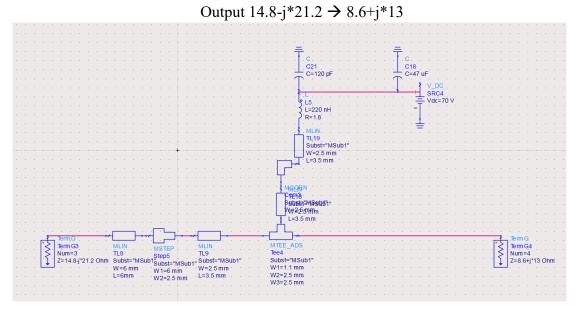

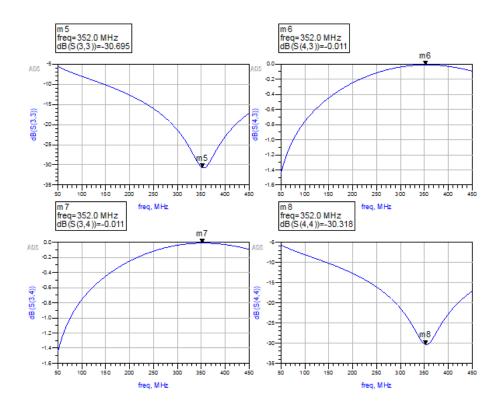

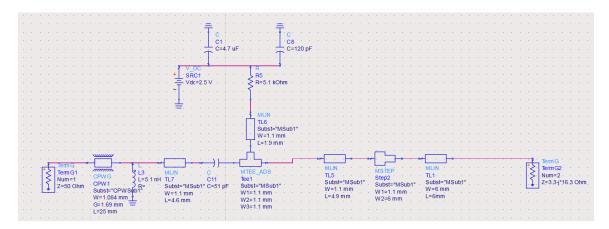

Το επόμενο στάδιο ήταν ο σχεδιασμός των δικτύων προσαρμογής (matching networks). Στόχος τους είναι η βελτιστοποίηση της μεταφοράς ισχύος μεταξύ του τρανζίστορ και των υπολοίπων σταδίων του κυκλώματος, παρουσιάζοντας στα άκρα του τρανζίστορ τη συζυγή εμπέδηση των θυρών του. Οι τιμές των βέλτιστων εμπεδήσεων προήλθαν από τις load-pull προσομοιώσεις του προηγούμενου κεφαλαίου. Ο σχεδιασμός ξεκίνησε με απλές διατάξεις συνδυασμού μικροταινιακών γραμμών και διακριτών εξαρτημάτων (πηνίων και πυκνωτών) και εξελίχθηκε μέσω επαναλαμβανόμενων βελτιώσεων.

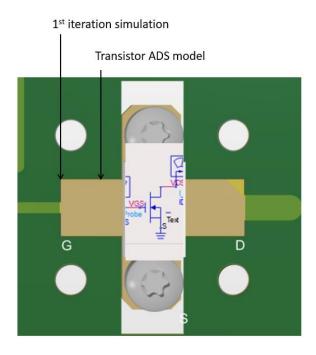

Στην πρώτη έκδοση, ο ενισχυτής παρήγαγε την επιθυμητή ισχύ μόνο στο θεωρητικό μοντέλο, καθώς ο προσομοιωτής του τρανζίστορ ξεκινούσε 0.7 mm εντός του σώματος του εξαρτήματος, με αποτέλεσμα να μην επιτυγχάνεται σωστή προσαρμογή. Μετά από επικοινωνία με τον κατασκευαστή και διόρθωση του μοντέλου, η δεύτερη έκδοση παρουσίασε ικανοποιητική προσαρμογή και σταθερή συμπεριφορά. Ακολούθησαν τρεις ακόμη βελτιώσεις. Στην τρίτη έκδοση, οι αιχμηρές γωνίες των ιχνών στρογγυλοποιήθηκαν για να μειωθεί η πυκνότητα ρεύματος και οι απώλειες, ενώ οι επίπεδες γειώσεις συνδέθηκαν για την αποφυγή βρόχων γείωσης. Στην τέταρτη έκδοση, η υπερθέρμανση του πυκνωτή σύζευξης αντιμετωπίστηκε με χρήση μεγαλύτερου εξαρτήματος και τροποποίηση των αποστάσεων των στοιχείων. Τέλος, στην πέμπτη έκδοση, το δίκτυο εξόδου απλοποιήθηκε με μια ευρύτερη επιφάνεια σύνδεσης και μικρότερη απόσταση εξαρτημάτων, μειώνοντας τις απώλειες και τη θερμική φόρτιση.

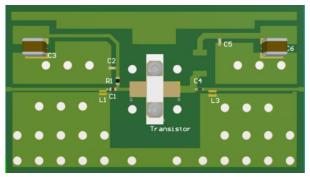

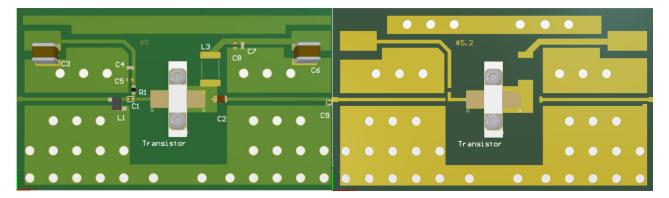

Ι<sup>η</sup> έκδοση

2η έκδοση

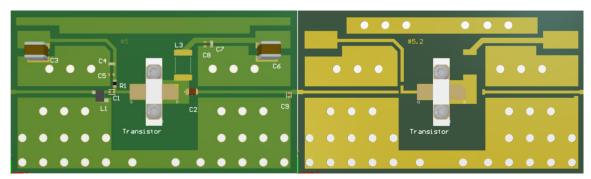

3η και 4η έκδοση

5η και 5.2 έκδοση

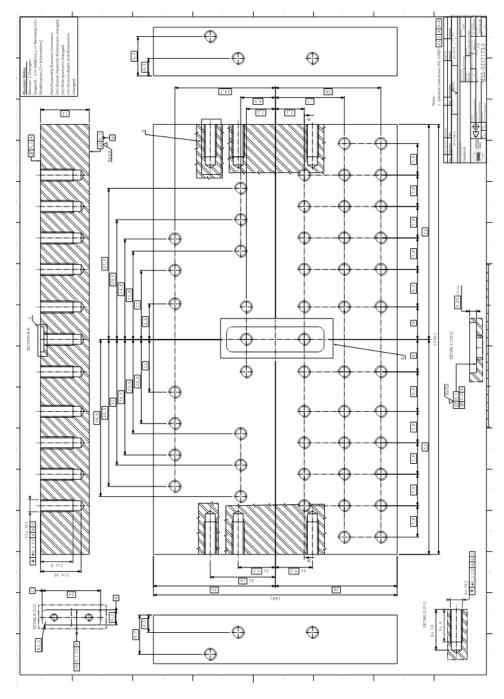

Αφού ολοκληρώθηκε η ηλεκτρική σχεδίαση, ακολούθησε ο μηχανικός σχεδιασμός του συστήματος ψύξης. Ο ενισχυτής λειτουργεί σε συνθήκες υψηλής ισχύος, συνεπώς η θερμική διαχείριση είναι καθοριστική. Το heatsink σχεδιάστηκε από αλουμίνιο διαστάσεων 60×106 mm, με πλήθος οπών για βίδες M3, ώστε να επιτρέπει την ασφαλή στήριξη του PCB, του τρανζίστορ και των υποστηρικτικών μπλοκ. Στο σημείο τοποθέτησης του τρανζίστορ έχει διαμορφωθεί εσοχή, ώστε το εξάρτημα να έρχεται σε πλήρη επαφή με το αλουμίνιο, το οποίο λειτουργεί τόσο ως μηχανική βάση όσο και ως επίπεδο γείωσης. Η συγκεκριμένη διάταξη βελτιώνει σημαντικά τη μεταφορά θερμότητας, επιτρέποντας τη σταθερή λειτουργία ακόμη και σε παρατεταμένη χρήση.

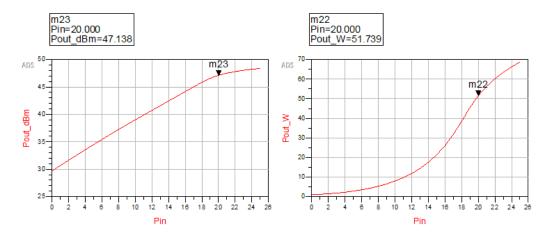

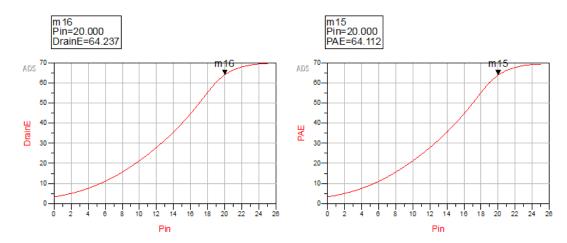

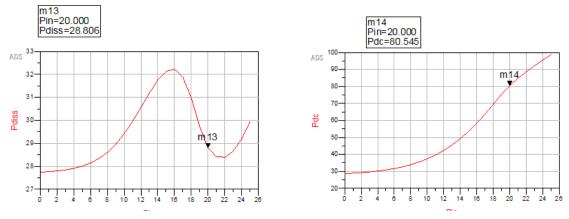

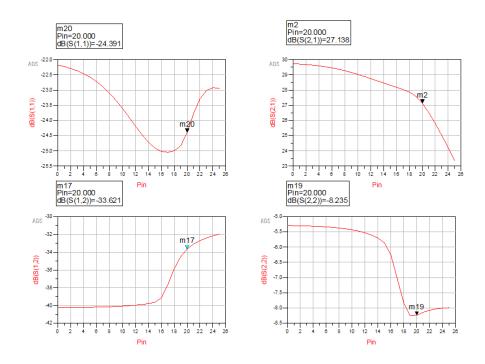

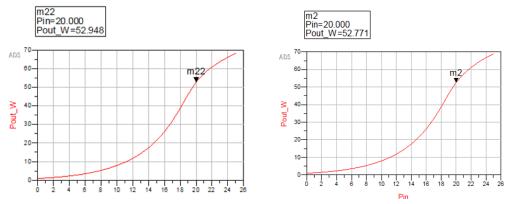

To heatsink

Το τελικό στάδιο της διαδικασίας περιλαμβάνει την προσομοίωση της διάταξης στο ADS, με χρήση ρεαλιστικών μοντέλων για όλα τα εξαρτήματα. Οι προσομοιώσεις πραγματοποιήθηκαν τόσο σε επίπεδο συχνότητας όσο και σε επίπεδο ισχύος. Τα αποτελέσματα έδειξαν ότι για ισχύ εισόδου 20 dBm ο ενισχυτής αποδίδει ισχύ εξόδου 50 W, επιτυγχάνοντας απόδοση 64%. Οι αρμονικές παραμορφώσεις παραμένουν σε αποδεκτά επίπεδα, ενώ οι παράμετροι S έδειξαν σταθερότητα και καλή προσαρμογή στο εύρος λειτουργίας. Ο υπολογισμός του παράγοντα σταθερότητας Κ έδωσε τιμή 1.136, αποδεικνύοντας ότι ο ενισχυτής είναι άνευ όρων σταθερός σε όλες τις συνθήκες λειτουργίας.

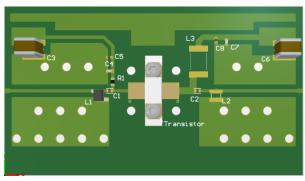

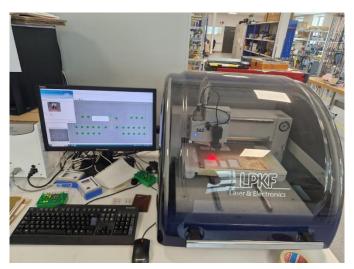

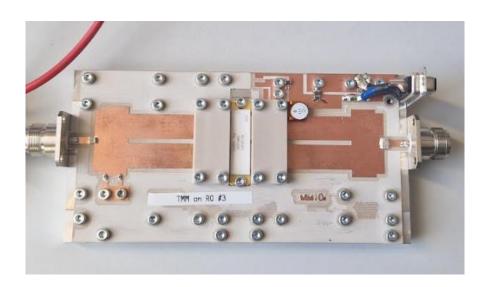

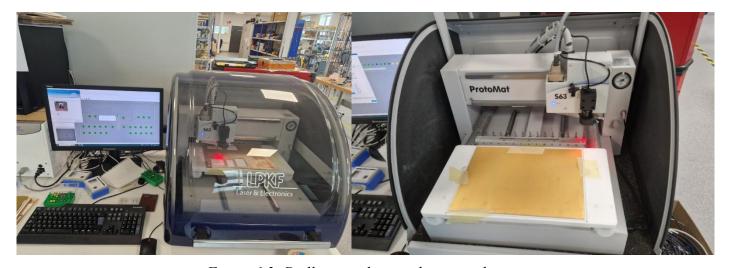

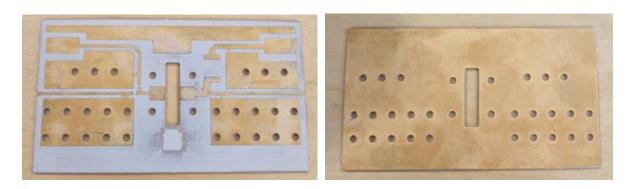

Στη συνέχεια περιγράφονται οι διαδικασίες κατασκευής και οι μετρήσεις που πραγματοποιήθηκαν, ως φυσική συνέχεια του προηγούμενου κεφαλαίου. Η παραγωγή ξεκίνησε με την εξαγωγή των Gerber από το Altium, επιλέγοντας μόνο ό,τι απαιτείται για υψηλή συχνότητα: περίγραμμα πλακέτας για τον ακριβή καθορισμό διαστάσεων, επάνω στρώση χαλκού με ίχνη και επίπεδα γείωσης (η κάτω παραμένει πλήρης γείωση), καθώς και τα αρχεία διάτρησης για όλες τις οπές στερέωσης, τους συνδέσμους τύπου Ν και την εγκοπή τοποθέτησης του τρανζίστορ ώστε να έρχεται σε άμεση επαφή με το heatsink. Τα αρχεία φορτώθηκαν στο LPKFS63 και κατεργαστήκαμε φύλλα RO3210, με μηχανική συγκράτηση για σταθερότητα. Σε αρκετές επαναλήψεις εμφανίστηκαν ζητήματα φθοράς κοπτικών και περιορισμών του μηχανήματος· σε στροφές 270° και σε ασυνέχειες πλάτους μικροταινίας παρατηρήθηκε υπερκοπή, ενώ σε άλλες περιπτώσεις η διάτρηση υπολείπονταν του ονομαστικού βάθους. Αυτά οδήγησαν σε μικροαποκλίσεις γεωμετρίας που μετατοπίζουν ελαφρά τη χαρακτηριστική εμπέδηση και, τελικά, τους συντονισμούς.

Το μηχάνημα LPKFS63

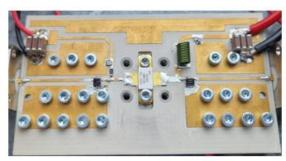

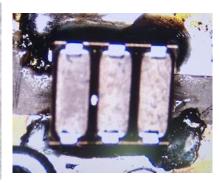

Η συναρμολόγηση εστίασε στην ποιότητα των κολλήσεων και την μηχανική σταθερότητα. Εφαρμόστηκε flux, προθέρμανση επιφανειών και στη συνέχεια συγκόλληση ώστε να αποφεύγονται κενά, γέφυρες κασσίτερου ή υπερβολική ποσότητα που αυξάνει απώλειες. Οι συνδετήρες N βιδώθηκαν πρώτα στο heatsink για μηχανική ακαμψία και κατόπιν κολλήθηκαν στην ταινιογραμμή, ώστε να διασφαλιστεί ομοιόμορφη γείωση και ελαχιστοποίηση παρασιτικών από την πλευρά του μεταλλικού σώματος. Το heatsink ελέγχθηκε ως προς την τραχύτητα, καθώς η ποιότητα επαφής επηρεάζει εξίσου την θερμική αγωγιμότητα και το επίσες.

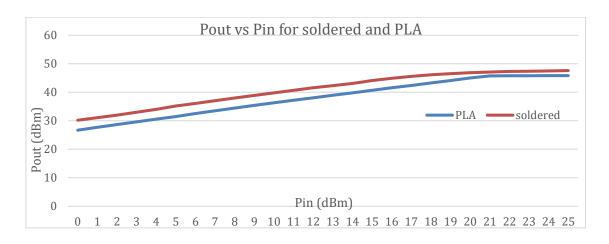

πεδο γείωσης. Για τη σύνδεση των pads του τρανσίστορ με τη μικροταινία δοκιμάστηκαν δύο μέθοδοι: άμεση κόλληση και μηχανική πίεση με εκτυπωμένα μπλοκ PLA. Η δεύτερη διευκόλυνε συγκρίσεις πλακετών και επαναχρησιμοποίηση του τρανζίστορ, αλλά εισήγαγε μια επιπλέον διηλεκτρική οδό (εr  $\approx 3.2$ ) και μικρή παρασιτική σύζευξη προς γη. Η τελική εικόνα ήταν σαφής: η απευθείας κόλληση δίνει μεγαλύτερη ισχύ εξόδου και σταθερότερη θερμική συμπεριφορά. Μετά τη συναρμολόγηση, κόπηκαν και κολλήθηκαν τα bias καλώδια με σύντομες RF διαδρομές.

Η κατασκευασμένη πλακέτα με το τρανζίστορ αριστερά συγκρατημένο με PLA και δεξιά με συγκόλληση

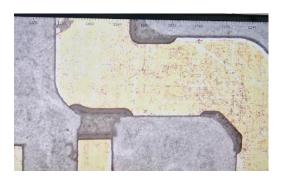

Στην πράξη, οι μη ιδανικότητες της κατασκευής αποτυπώθηκαν στις μετρήσεις. Ανομοιόμορφη κοπή χαλκού/διηλεκτρικού γύρω από οπές ή στις ακμές ιχνών μεταβάλλει την τοπική εμπέδηση και την κατανομή ρεύματος. Αχρησιμοποίητες οπές στο heatsink λειτούργησαν σαν μικρές κοιλότητες που εγκλωβίζουν πεδία. Μικρές γωνιακές αποκλίσεις ή υπερβολική κόλληση στους Ν-συνδετήρες πρόσθεσαν χωρητικά παρασιτικά. Επίσης, οποιαδήποτε μικροκενά επαφής ανάμεσα σε PCB— heatsink ή heatsink—dissipator επιδείνωσαν ταυτόχρονα θερμική αγωγιμότητα και συνέχεια γείωσης. Η εφαρμογή θερμικής πάστας και ελεγχόμενης πίεσης με μπλοκ από PLA συνέβαλε στον περιορισμό των ανακριβειών.

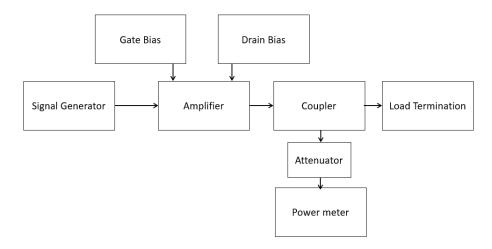

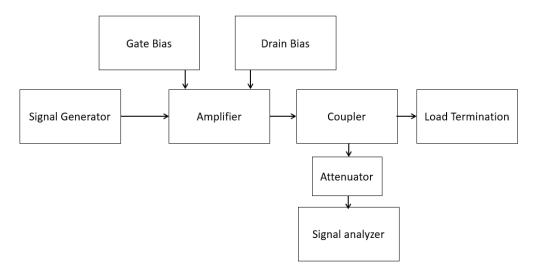

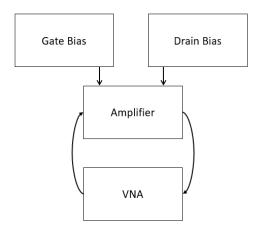

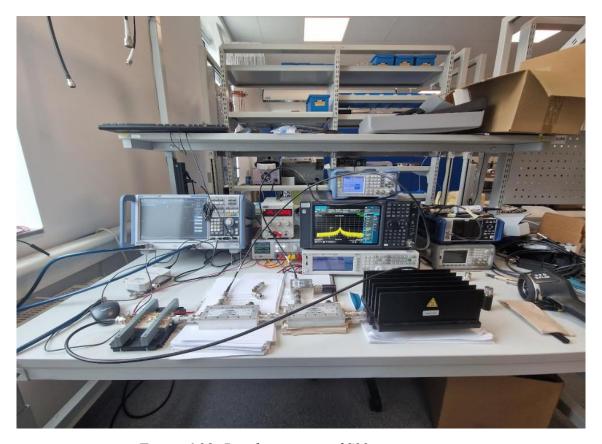

Οι δοκιμές συνοδεύτηκαν από αναλυτική παρουσίαση και τεχνική αξιολόγηση των οργάνων και εξαρτημάτων που χρησιμοποιήθηκαν στο σύστημα μετρήσεων. Περιγράφονται οι γεννήτριες σήματος που παρείχαν την απαιτούμενη ισχύ και δυνατότητα παραγωγής παλμών, τα τροφοδοτικά για τη ρύθμιση και τον έλεγχο των τάσεων πόλωσης, καθώς και τα όργανα μέτρησης που χρησιμοποιήθηκαν για την παρακολούθηση της ισχύος, του φάσματος και των S-παραμέτρων. Παρουσιάζονται επίσης τα παθητικά στοιχεία που συνέθεσαν το κύκλωμα μετρήσεων μαζί με την αιτιολόγηση επιλογής τους, τη συνδεσμολογία τους και τη συμβολή τους στη διασφάλιση της ακρίβειας και της προστασίας του εξοπλισμού κατά τη διαδικασία των μετρήσεων.

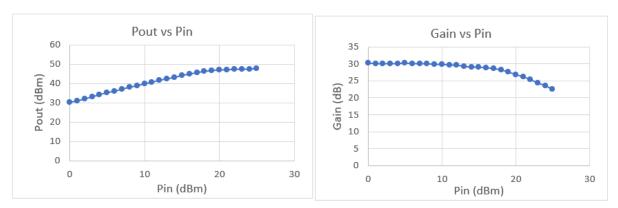

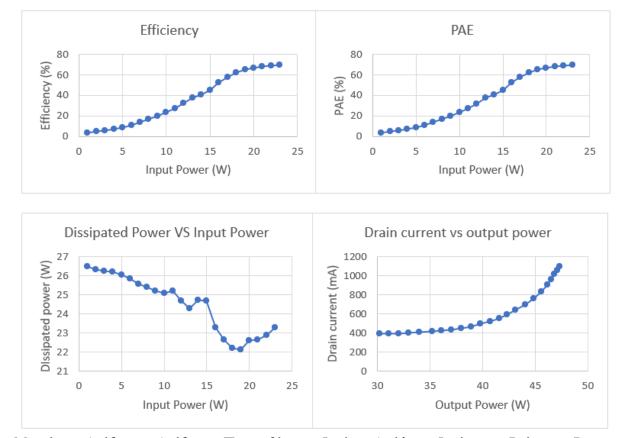

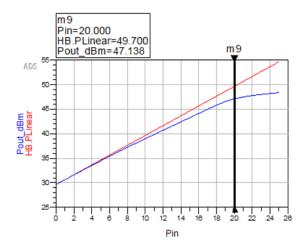

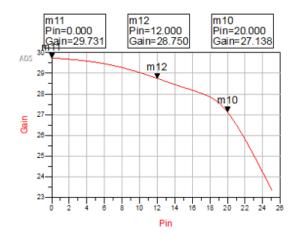

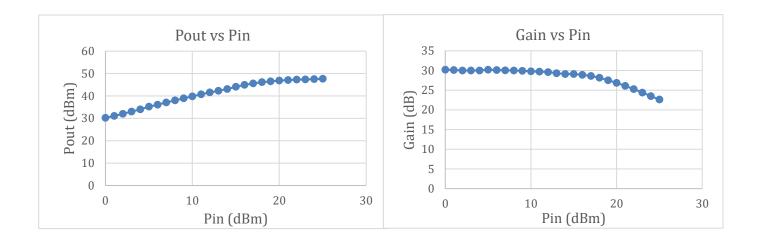

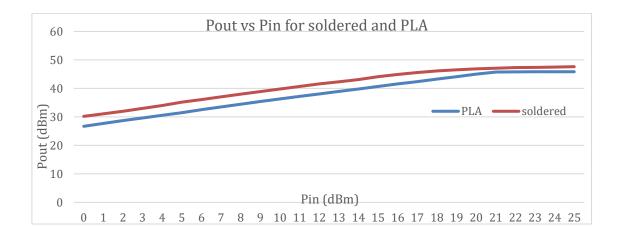

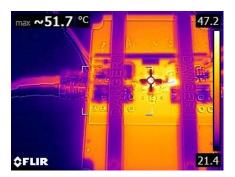

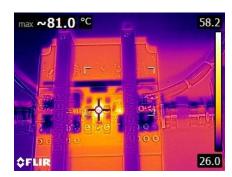

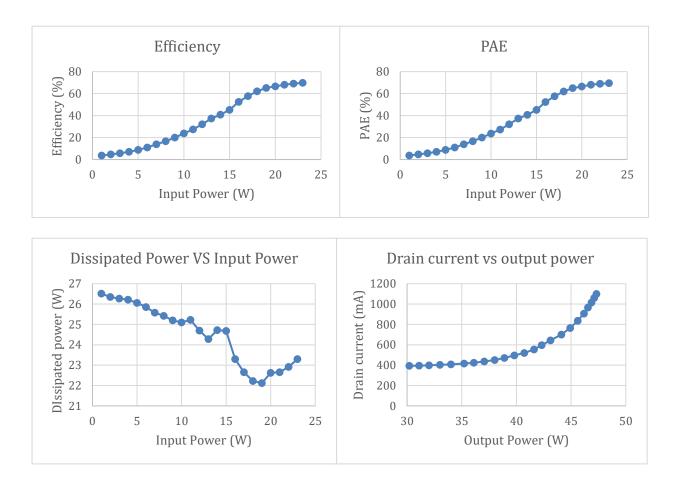

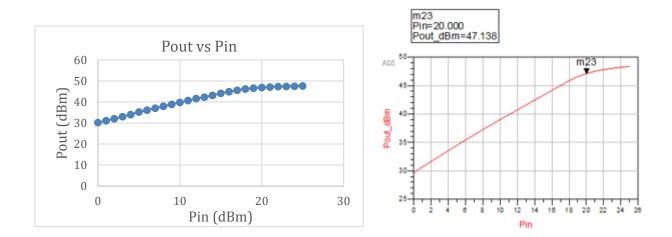

Στα αποτελέσματα της δεύτερης επανάληψης PCB, με ισχύ εισόδου 20 dBm μετρήθηκαν: ισχύς εξόδου 48.4 W και κέρδος 26.85 dB, στα 21 dBm η έξοδος ανέβηκε σε 51.3 W, επιβεβαιώνοντας ότι το στάδιο λειτουργεί βαθιά σε κορεσμό. Σε χαμηλές εισόδους το κέρδος υπερέβη τα 30 dB, και στη ζώνη λειτουργίας (10 dB δυναμικό) καταγράφηκε συμπίεση ~3 dB, όπως αναμενόταν. Η απόδοση και η απόδοση με πρόσθεση ισχύως αυξήθηκαν σημαντικά με την έξοδο, αγγίζοντας ~68% κοντά στα 48–54 W, ενώ η απωλούμενη ισχύς μειώθηκε αντίστοιχα. Η κατανάλωση ρεύματος ακολούθησε εκθετική σχέση με την ισχύ εξόδου, ένδειξη ότι πέρα από τα ονομαστικά όρια απαιτείται προσοχή. Η σύγκριση «κολλημένο τρανζί-

στορ» έναντι «PLA blocks» έδειξε συστηματικά χαμηλότερη ισχύ εξόδου για τη δεύτερη περίπτωση και υψηλότερες θερμοκρασίες. Με απευθείας κόλληση, η θερμοκρασία σταθεροποιήθηκε περί τους 50–55 °C σε CW και ~45 °C σε παλμική λειτουργία.

Μετρήσεις ισχύος εξόδου και κέρδους ως προς ισχύ εισόδου για την 2η εκδοχή

Μετρήσεις Απόδοσης, Απόδοσης Προστιθέμενης Ισχύος, Απώλειας Ισχύος και Ρεύματος Drain ως συνάρτηση της Ισχύος Εισόδου

Μετρήσεις ισχύος εξόδου ως συνάρτηση της ισχύος εισόδου για σύνδεση συγκολλημένου τρανζίστορ και με μπλοκ PLA

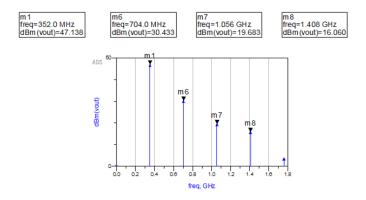

Ως προς το εύρος ζώνης, με sweep συχνότητας προέκυψε -1 dB εύρος ζώνης περίπου 50 MHz, με μια ελαφρά μετατόπιση συντονισμού που αποδίδεται σε μικροατέλειες κόλλησης και τοποθέτησης. Η φασματική ανάλυση σε CW κοντά στη λειτουργία έδωσε επίπεδα 2ης και 3ης αρμονικής περί -24 dBc και -22 dBc αντίστοιχα, τιμές συμβατές με την έντονα μη γραμμική περιοχή. Δεν παρατηρήθηκαν πλάγιοι λοβοί. Σε παλμική λειτουργία, η πτώση ισχύος εντός παλμού ήταν ~0.05 dB και η μεταβολή φάσης ~0.2°, χωρίς αξιοσημείωτο ripple και με εξαιρετική επαναληψιμότητα από παλμό σε παλμό. Επιπλέον ελέγχθηκαν μικρές μεταβολές της Vd (68-70 V) και καταγράφηκαν μεταβολές ισχύος/φάσης τάξης λίγων dB/μοιρών, επαληθεύοντας ανθεκτικότητα σε ρεαλιστικές τροφοδοτικές διακυμάνσεις.

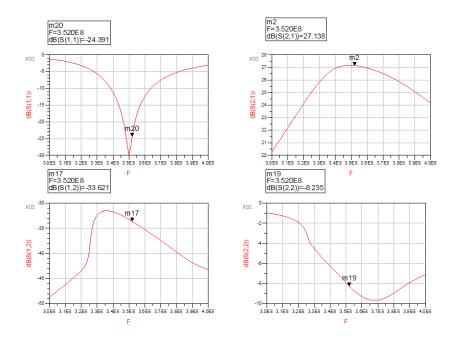

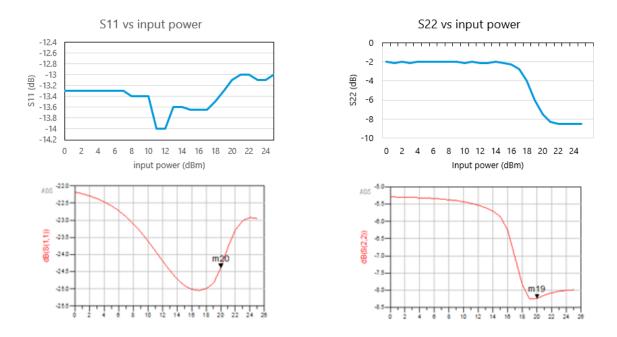

Οι μετρήσεις για την σταθερότητα έδειξαν K>1 και μS, μL >1 σε χαμηλές ισχύς, άρα άνευ όρων σταθερότητα στη γραμμική περιοχή, ενώ η ομαδική καθυστέρηση μετρήθηκε  $\sim$ 6.5 ns, εντός στόχων. Το S11 κυμάνθηκε κοντά στα -13 dB (εξαρτώμενο από ισχύ), ενώ το S22 βελτιώθηκε με την ισχύ, από περίπου -2 dB σε χαμηλές στάθμες μέχρι -8.5 dB σε κορεσμό, όταν η έξοδος του υπό δοκιμή ενισχυτή «φορτίστηκε» με κατάλληλη συνθήκη αντιστοίχισης μέσω των ζευκτών. Σε δοκιμή διαδοχικής λειτουργίας με το 20 στάδιο, επιβεβαιώθηκε ότι η απαιτούμενη ισχύς ανά κλάδο για το σύστημα μπορεί να επιτευχθεί με ισχύ εισόδου 16 dBm, παρέχοντας λειτουργικό περιθώριο. Παρατηρήθηκαν ωστόσο φαινόμενα πτώσης παλμού λόγω αύξησης του κέρδους του δεύτερου σταδίου εντός παλμού, καθώς και έντονα ίχνη ενδοδιαμόρφωσης γύρω στα 13-14 dBm εισόδου που χρήζουν στοχευμένης βελτιστοποίησης στην προσαρμογή και στο φιλτράρισμα των αρμονικών.

Παρακάτω ο συνολικός πίνακας με τις τεχνικές προδιαγραφές του ενισχυτή και αντίστοιχη τιμή της μέτρησης για την  $2^{\eta}$  εκδοχή του ενισχυτή:

| Parameter                                | Specification per                                                                    | Specification per                                                                            | Measurement                  |

|------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------|

|                                          | 2024-02-12                                                                           | 2024-08-12                                                                                   | For PCB#2                    |

| Operating frequency                      | 352.21 MHz                                                                           | 352.21 MHz                                                                                   | 352.21 MHz                   |

| -1 dB bandwidth                          | ≥±1 MHz                                                                              | ≥±1 MHz                                                                                      | 50MHz                        |

| Peak output<br>power                     | 30 W (or higher)                                                                     | 50 W                                                                                         | 58W                          |

| RF pulse width                           | Up to 3.5 ms                                                                         | Up to 3.5 ms                                                                                 | 3.5 ms                       |

| Repetition rate                          | Up to 14 Hz                                                                          | Up to 14 Hz                                                                                  | 14 Hz                        |

| Gain                                     | 23 dB min                                                                            | 27 dB at 20dBm input                                                                         | 26.85 dB                     |

| Efficiency                               | > 50 %                                                                               | > 50 %                                                                                       | 68%                          |

| Maximum no-<br>damage RF drive<br>input  | 26 dBm                                                                               | 26 dBm                                                                                       | 26 dBm                       |

| Harmonic content at output power         | <-30 dBc                                                                             | <-30 dBc                                                                                     | -20 dBc, -27dBc              |

| Spurious and sideband levels in ± 20 MHz | <-60 dBc                                                                             | < -60 dBc                                                                                    | No spurious                  |

| RF Input<br>Connector                    | N type, 50 Ω,<br>Female                                                              | N type, 50 Ω, Female                                                                         | N type, $50 \Omega$ , Female |

| RF Output<br>Connector                   | N type, 50 Ω,<br>Female                                                              | N type, 50 Ω, Female                                                                         | N type, 50 Ω,<br>Female      |

| Input/output impedance                   | 50 Ω                                                                                 | 50 Ω                                                                                         | 50 Ω                         |

| Input VSWR                               | ≤ 1.2:1 (if possible)                                                                | ≤ 1.12:1 or -25dB (if possible)                                                              | 1.5:1                        |

| output VSWR                              | ≤ 1.2:1 (if possible)                                                                | ≤ 1.12:1 or -25dB (if possible)                                                              | 2.3:1                        |

| Load VSWR                                | Infinity                                                                             | Infinity                                                                                     |                              |

| Gain flatness                            | $\Delta G \le \pm 0.5 \text{ dB}$<br>(over 10dB dynamic)                             | $\Delta G \le \pm 0.5 \text{ dB (over}$<br>10dB dynamic)                                     | 2.95 dB                      |

| Phase flatness                           | ≤2°(over 10dB dynamic)                                                               | ≤2° (over 10dB<br>dynamic)                                                                   | 0.2°                         |

| RF Power Drop across the pulse           | ≤ 5% p-p (or Max 0,21dB) (power) (Within 3.5ms RF pulse excluding first 100μs of the | ≤ 10% p-p (or Max 0,21dB) (power) (Within 3.5ms RF pulse excluding first 100μs of the pulse) | 0.05 dB drop                 |

|                                                                  | pulse)                                                                 |                                                                                   |           |

|------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------|

| Power ripple across pulse                                        | ≤ 0.25% rms (Within 3.5ms RF pulse excluding first 100µs of the pulse) | ≤ 0.25% rms (Within 3.5ms RF pulse excluding first 100μs of the pulse)            | No        |

| Phase shift across the pulse                                     | ≤ 5° (Within 3.5ms RF pulse excluding first 100μs of the pulse)        | ≤ 10° (Within 3.5ms<br>RF pulse excluding<br>first 100µs of the<br>pulse)         | 0.2°      |

| Phase ripple across pulse                                        | ≤ 0.25° rms (Within 3.5ms RF pulse excluding first 100µs of the pulse) | ≤ 0.25° rms (Within<br>3.5ms RF pulse ex-<br>cluding first 100µs of<br>the pulse) | No        |

| Pulse-to-pulse power stability                                   | ≤ 2%                                                                   | ≤ 2%                                                                              | 0%        |

| Pulse-to-pulse<br>phase stability<br>(repeatability)             | ≤ 2°                                                                   | ≤ 2°                                                                              | 0°        |

| RF Pulse Rise/<br>Fall Time                                      | ≤ 1 μs                                                                 | ≤1 μs                                                                             |           |

| compression point @ 0,1dB                                        | 54 W                                                                   | 54 W                                                                              | 2 W       |

| Total Group De-<br>lay (not sure we<br>need this param-<br>eter) | ≤ 50 ns                                                                | ≤ 50 ns                                                                           | 6ns       |

| Size                                                             | Max size of the PCB 20x10 cm                                           | Max size of the PCB 20x10 cm                                                      | 10.6x6 cm |

Για πληρότητα, η πρώτη επανάληψη του PCB έδειξε συντονισμό περί τα 295 MHz. Ο έλεγχος της ταινιογραμμής με προσωρινό τερματισμό 50 Ω επιβεβαίωσε σωστή χαρακτηριστική εμπέδηση, άρα το θέμα εντοπίστηκε στο σημείο αναφοράς του μοντέλου συσκευασίας στο εργαλείο προσομοίωσης και διορθώθηκε στη δεύτερη επανάληψη. Η πέμπτη επανάληψη προσέφερε έως ~68–70 W με βελτιωμένη θερμική συμπεριφορά και χαμηλότερη κατανάλωση, χάρη σε πιο βελτιωμένη γεωμετρία εξόδου με ευρεία επιφάνεια σύνδεσης, μικρότερες αποστάσεις και περιορισμός επιρροής του κυκλώματος τροφοδοσίας.

Συνοψίζοντας, η εργασία ανέδειξε έναν ολοκληρωμένο κύκλο σχεδίασης—υλοποίησης—μέτρησης για έναν ενισχυτή ισχύος στερεάς κατάστασης που ανταποκρίνεται

στις λειτουργικές απαιτήσεις του ESS, επιτυγχάνοντας υψηλή αποδοτικότητα, επαναληψιμότητα σε παλμική λειτουργία και συμβατότητα με τα συστήματα του ESS. Η μεθοδική επιλογή υλικών και τοπολογιών, ο στοχευμένος σχεδιασμός και οι μετρήσεις στον πάγκο οδήγησαν σε τεκμηριωμένες βελτιστοποιήσεις, από διάταξη και προσαρμογή έως διαδικασίες συναρμολόγησης/γείωσης, ενώ ανέδειξαν σαφή περιθώρια περαιτέρω ωρίμανσης σε παραμέτρους όπως των S-παραμέτρων εξόδου, την θωράκιση και την έξυπνη πόλωση. Πέρα από το συγκεκριμένο πρωτότυπο, η παρούσα εργασία θέτει μια σταθερή βάση πάνω στην οποία μπορούν να αναπτυχθούν μελλοντικές βελτιώσεις και επεκτάσεις, οδηγώντας στην κατασκευή ακόμη πιο αποδοτικών ενισχυτών και συμβάλλοντας περαιτέρω στην εδραίωση της βιωσιμότητας ως βασικού χαρακτηριστικού του ESS.

## **Chapter 1: Introduction**

#### 1 Introduction

This chapter introduces the scope, background, motivation, and objectives of the thesis. It summarizes the design and validation work carried out during a six-month internship at the European Spallation Source (ESS) Radio Frequency (RF) group, provides an overview of the ESS and its applications, explains the motivation for adopting Solid-State Power Amplifier (SSPA) technology, and outlines the objectives focused on the design, simulation, manufacturing, and testing of a driver amplifier.

#### 1.1 Scope

The purpose of this thesis is to document the design and validation work carried out during a six-month internship at ESS RF group. The focus of the internship was the design, development, and validation of an RF amplifier to serve as the 1st stage driver for a new Solid-State Power Amplifier system. The internship aimed to contribute to ESS's project of using SSPA technology to power spoke cavities, with each cavity requiring up to 400kW. This thesis highlights key deliverables, technical challenges, design optimizations and lessons learned.

#### 1.2 The European Spallation Source